OpenEdgePMU: An Open PMU Architecture with Edge Processing for Future Resilient Smart Grids

Abstract

1. Introduction

1.1. A Brief Review of Recent PMU Designs

1.2. Motivation for the OpenEdgePMU Initiative

1.3. Challenges and Requirements for Distribution Grid PMUs

1.4. Novelty of the OpenEdgePMU Initiative

- Soft real-time edge/fog processing;

- Hard real-time processing of phasors;

- Local storage of all acquired data;

- Distributed storage management;

- Ability to support several different functionalities in a single processing system (e.g., typical PMU, fault detection and analysis, power quality analysis, state estimation, fast protection, smart grid automation, etc.);

- Phasors measurement accuracy adequate for distribution grids (0.0x%, millidegrees for phase);

- Compact size;

- Low cost;

- Open source (both regarding software and hardware design);

- Adequate project documentation to support adoption from the research and scientific community.

- Vast amounts of locally generated data are processed by artificial intelligence agents running locally.

- The edge system generates only events to remote cloud software backends/frontends, thus reducing the necessity of extensive communication bandwidth and the relevant cost of transmission.

- The edge system stores the generated data timeseries locally, in case of a potential end-user’s request for further detailed analysis. This distributed database may also vastly reduce the costs for cloud services.

- The edge system that processes the acquired data can communicate with minimum delays with other edge systems that are able to execute actions and control (e.g., protection, automation, etc.). The 5G infrastructure comes together to minimize communication latency and provide time-critical solutions.

2. Materials and Methods

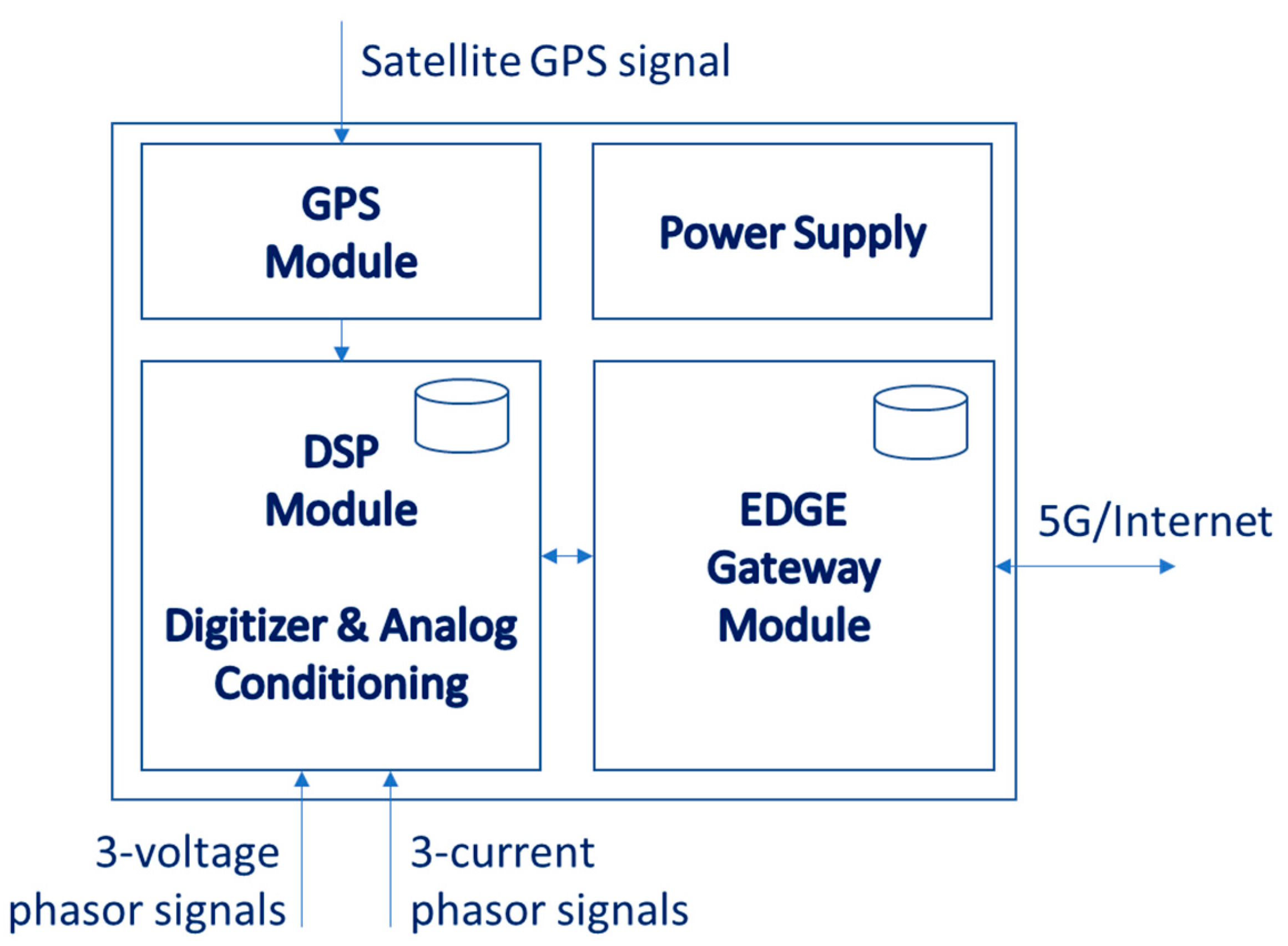

2.1. System Architecture

- The digital signal processor (DSP) module which is responsible for all hard real-time processing of the digitized phasor signals. It also contains the digitizer and analog conditioning electronic circuits that are responsible for interfacing with the external sensors of the phasor signals, as well as filtering and amplification suitable for the digitizer, which is responsible for the analog-to-digital conversion of the acquired phasor signals.

- The edge gateway module, which is responsible for all soft real-time processing, such as artificial intelligence, communication protocols, etc.

- The GPS module which is responsible for interfacing the satellite GPS signals, keeping absolute timing, and generating the time resynchronization signal for the digitizer.

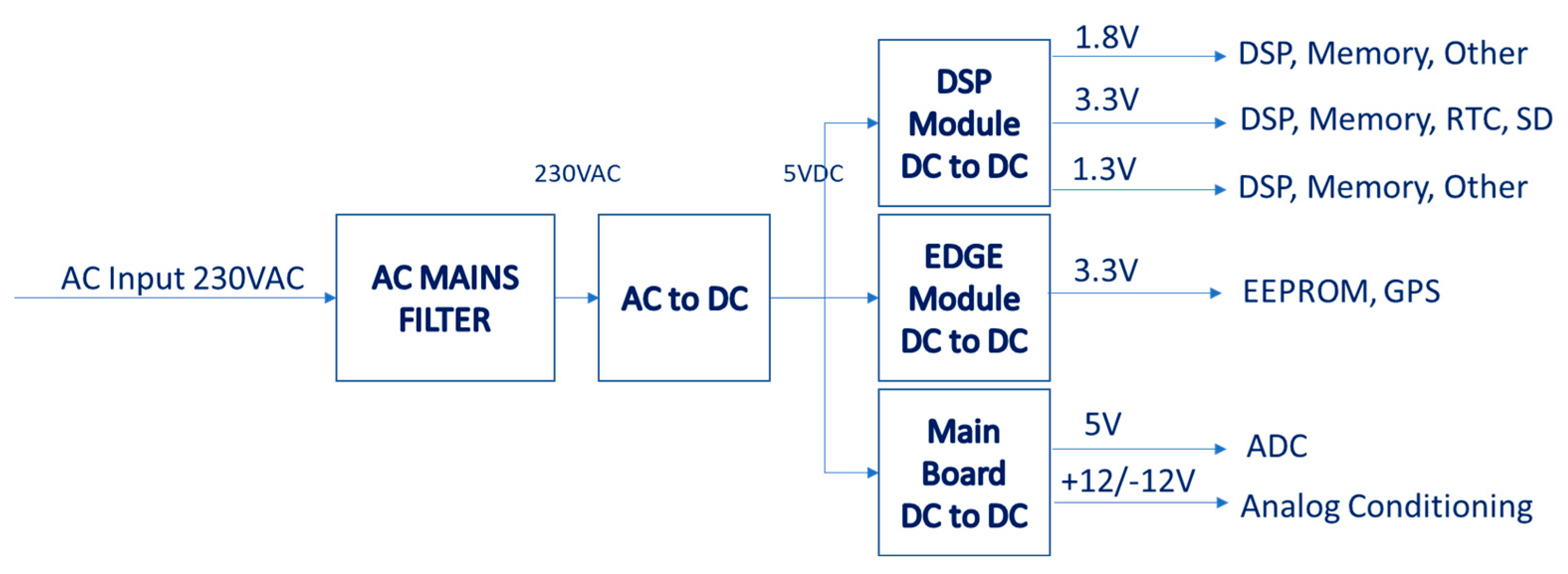

- The power supply module which is responsible for the AC-to-DC conversion of one of the voltage phasors, to suitable low voltages for powering all electronic components.

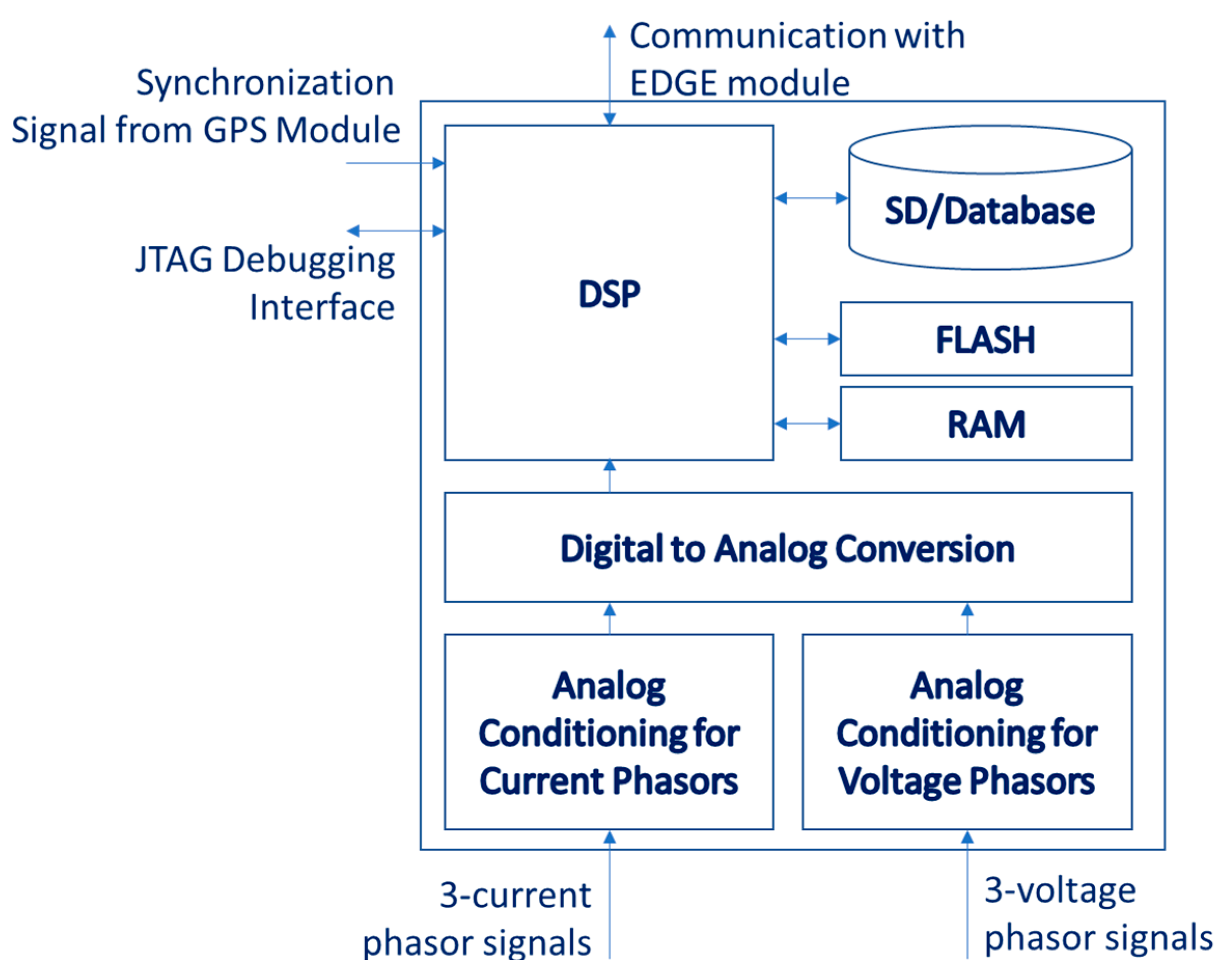

2.2. DSP Module

- DSP TMS320c5517 (Texas Instruments, Dallas, TX, USA) [42] is the brain of the module running a firmware that handles all operations related to data acquisition, storage, processing synchronization, communication, and configuration. This is a high-performance, low-power, fixed-point digital signal processor from Texas Instruments, with the following specifications:

- 200 MHz clock rate, 5 ns instruction cycle time, one or two instructions executed per cycle, dual multiply-and-accumulate units, two arithmetic and logic units (ALUs);

- 320 KB on-chip RAM, zero wait state (64 kB dual-access RAM, 256 KB single access);

- 128 KB on-chip ROM zero wait state;

- Tightly coupled FFT hardware accelerator;

- Peripherals: McSPI, McBSP, UHPI, EMIF, UART, USB, DMA, eMMC, SPI, I2C, and I2S.

- SDRAM (external) (Micron MT48H32M16LF) [43] is useful for firmware execution. The size of the SDRAM is 64 MB.

- Nonvolatile flash memory (external) (Infineon S29GL128S11DHIV20) [44] for storing the firmware of the DSP module. The size of the FLASH memory is 16 MΒ. The memory is in-system programmable; therefore, the developer can change and upload the DSP module’s firmware.

- Nonvolatile SD memory (SD Card) [45] for storing the acquired data and other parameters for configuring the device. The default storage size is 64 GB and, depending on the sampling frequency, the storage period can last from some hours to several days.

- Analog-to-digital converter (ADS8586S, Texas Instruments) [46] for digitizing the analogue input signal. This is a 6-channel, high-speed, simultaneous-sampling ADC, with 16-bit resolution and fully differential bipolar inputs on a single supply, with the following key performance specifications:

- 250 kSPS max throughput per channel;

- Two selectable input ranges, ±10 V and ±5 V;

- Antialiasing low-pass filter to 24 kHz for ±10 V range and to 16 kHz for ±5 V range;

- DNL, ±0.35 LSB;

- INL, ±0.45 LSB;

- SNR, 96.4 dB

- THD, −114 dB.

- Analog conditioning electronic circuit for isolating the voltage input, reducing it to an acceptable level suitable for acquisition, and for amplifying the current input from the current sensors. The analog conditioning circuit consists of a total of six channels (three for voltage and three for current). The voltage input includes a differential isolation amplifier in combination with a voltage divider to reduce the input voltage and to isolate it from the digital circuit. The current input includes simple amplifier circuitry to amplify the input signal. The specifications of the voltage inputs are:

- Number of inputs, 3, one per phase;

- Input range, 230 VAC nominal;

- Isolation, optical isolation;

- Isolation voltage 4000 Vpeak;

- Transient immunity, 10 kV/us minimum;

- Input sensor type, Rogowski coil;

- Range, 100 mV/1000 A typical, but configurable for different sensors.

- Voltage analog input interface, to connect the external voltage phasor (230VAC nominal);

- Current analog input interface, to connect the external Rogowski coil;

- Full-duplex UART serial interface with the MCU/edge processing module, providing bandwidth 921,600 bps;

- GPS-PPS input signal interface, used for immediate external interrupt to the DSP, in order to resynchronize the internal sampling frequency timer;

- JTAG interface, used for connecting an external JTAG board to interconnect the DSP module with Texas Instruments Code Composer Studio environments, useful for firmware development and debugging;

- Full Duplex UART serial interface at 921,600 bps for direct debugging using a common terminal (common interface with MCU/edge processing module).

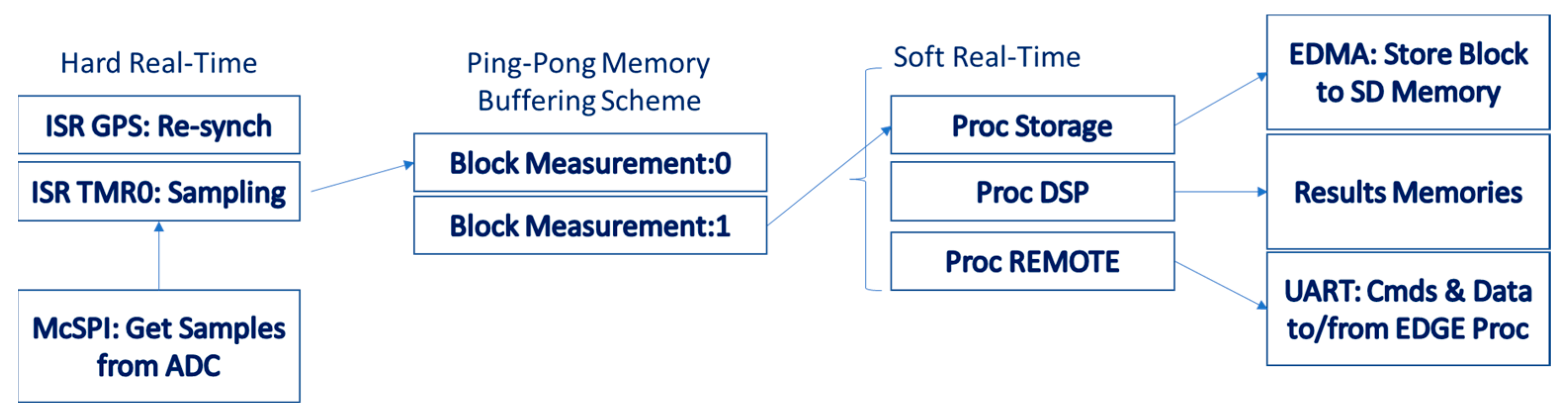

- Hard real-time functionalities:

- Sampling of six (6) channels and conversion to digital signals;

- Storage of digital signals to the nonvolatile SD memory using EDMA transfers;

- Processing of the digital signals;

- Timing resynchronization with GPS.

- Soft real-time functionalities:

- Communication with the edge processing module;

- Measurements de-calibration.

- System support functionalities:

- Configuration via remote terminal;

- Measurement calibration;

- Debugging via JTAG and Texas Instruments CCS;

- In-system programming.

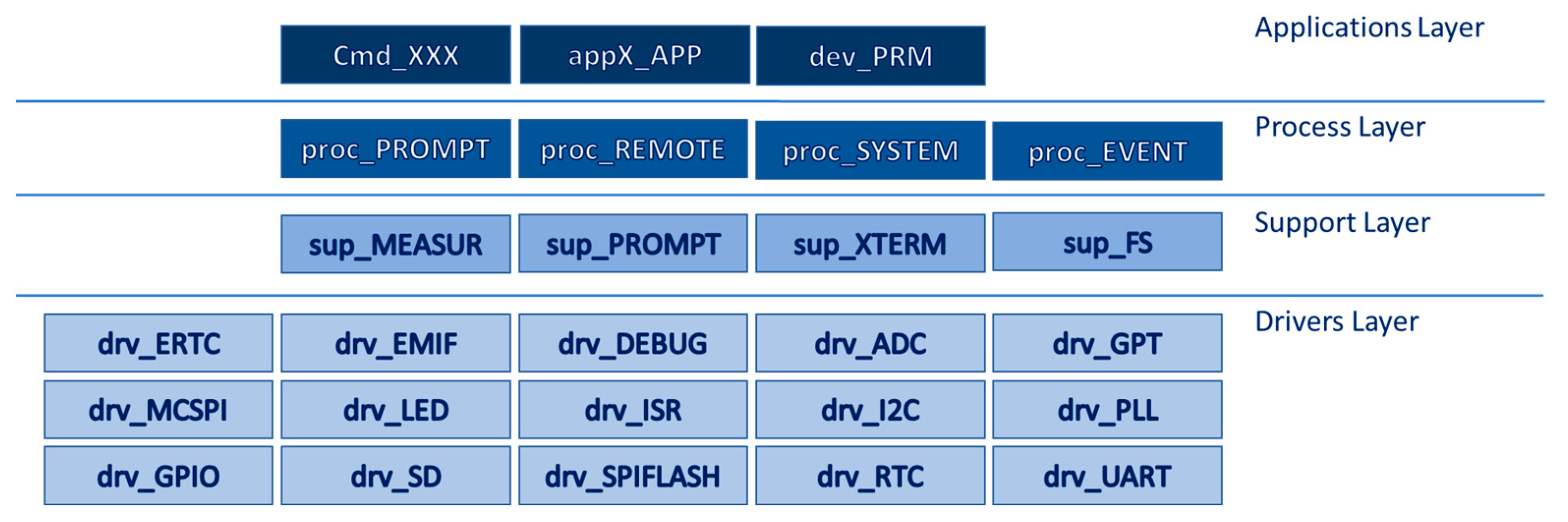

- The drivers layer is responsible for low-level driver implementation regarding certain internal DSP peripherals and external peripherals. The DSP internal peripherals are McSPI, I2C, UART, SD/MMC, EMIF, EDMA, GPIO, and ISR. The external peripherals are the ADC, NOR flash, and SDRAM memories.

- The support layer provides the application programming interface (API) to be used by processes to access low-level functionalities. This includes the terminal prompt interface, the file system, and the XTERM support library, which is an implementation of the XMODEM protocol [47] used in In-System-Programming (ISP) to support future firmware updates, as well as potential file/data transfers.

- The process layer contains high and low priority processes related to device operation, including data acquisition (ACQ), data handling (DH), communication with the GW module (REMOTE), and the command prompt.

- The application Layer refers to the top-level application related to the actual functional operation of the DSP module regarding measurement. Essentially, this is a single entity that combines different processes to accomplish a certain task.

| Algorithm 1. Code Snippet-1 |

| #define BLOCK_SIZE_MEASUREMENT 1363 #define NUMBER_BOCKS_MEASUREMENT 2 #define NUMBER_OF_CHNNELS_MEASUREMENT 6 struct Block_MEASUREMENT { Uint16 date_time [12];//ddmmyyhhmmssmmm Int16 raw[BLOCK_SIZE_MEASUREMENT][NUMBER_OF_CHNNELS_MEASUREMENT]; Uint32 cs;//Check sum of the total FILE DataBlock structure }; … struct Block_MEASUREMENT block[NUMBER_BOCKS_MEASUREMENT]; |

- System configuration parameters, 8 kBytes;

- Events, 512 events × 64 Bytes = 32 kBytes;

- Signal data, 3.000.000 Blocks × 16.384 Bytes = 49,152 Gbytes;

- Extra, almost 14 GBytes for future use.

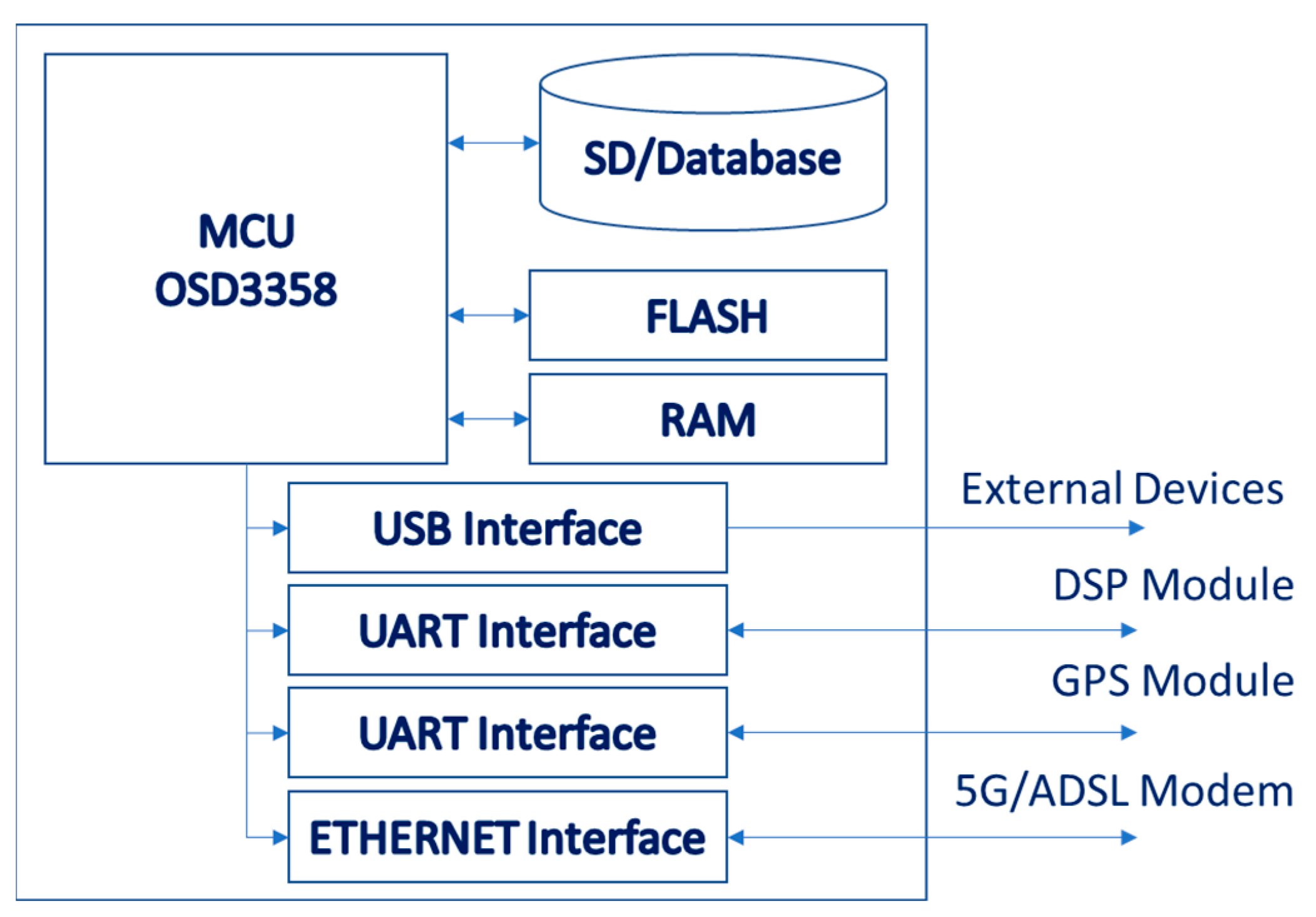

2.3. Edge Processing Module

- Texas Instruments Sitara™ AM335x ARM® Cortex® A8 Processor running at 1 GHz;

- Ethernet controller and interface (supports 10/100/1000 Mbps communication rates);

- Nonvolatile storage controller for MMC, SD, and SDIO;

- Supports up to 1 GB DDR3L memory.

- On-chip peripherals: CAN, SPI, I2C, UART, GPIO, etc.

- MMC to interface with the SD memory card storing the OS and all the data;

- I2C to interface with the on-board EEPROM memory;

- UART to interface with the PMU and other external modules;

- Ethernet to provide an Ethernet interface to connect to the local network.

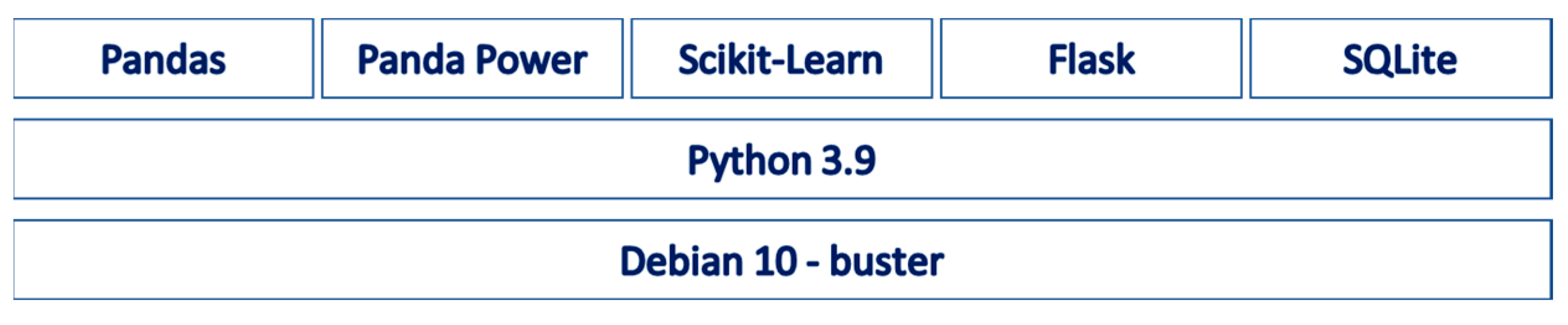

- PandaPower [49], a library used for power system modeling;

- Pandas [50], a numerical and data analysis library;

- Scikit-learn [51], an AI construction and execution library;

- Flask [52], a library for the development of HTTP-REST interfaces;

- SQLite [53], a library for the interaction with the local SQLite database.

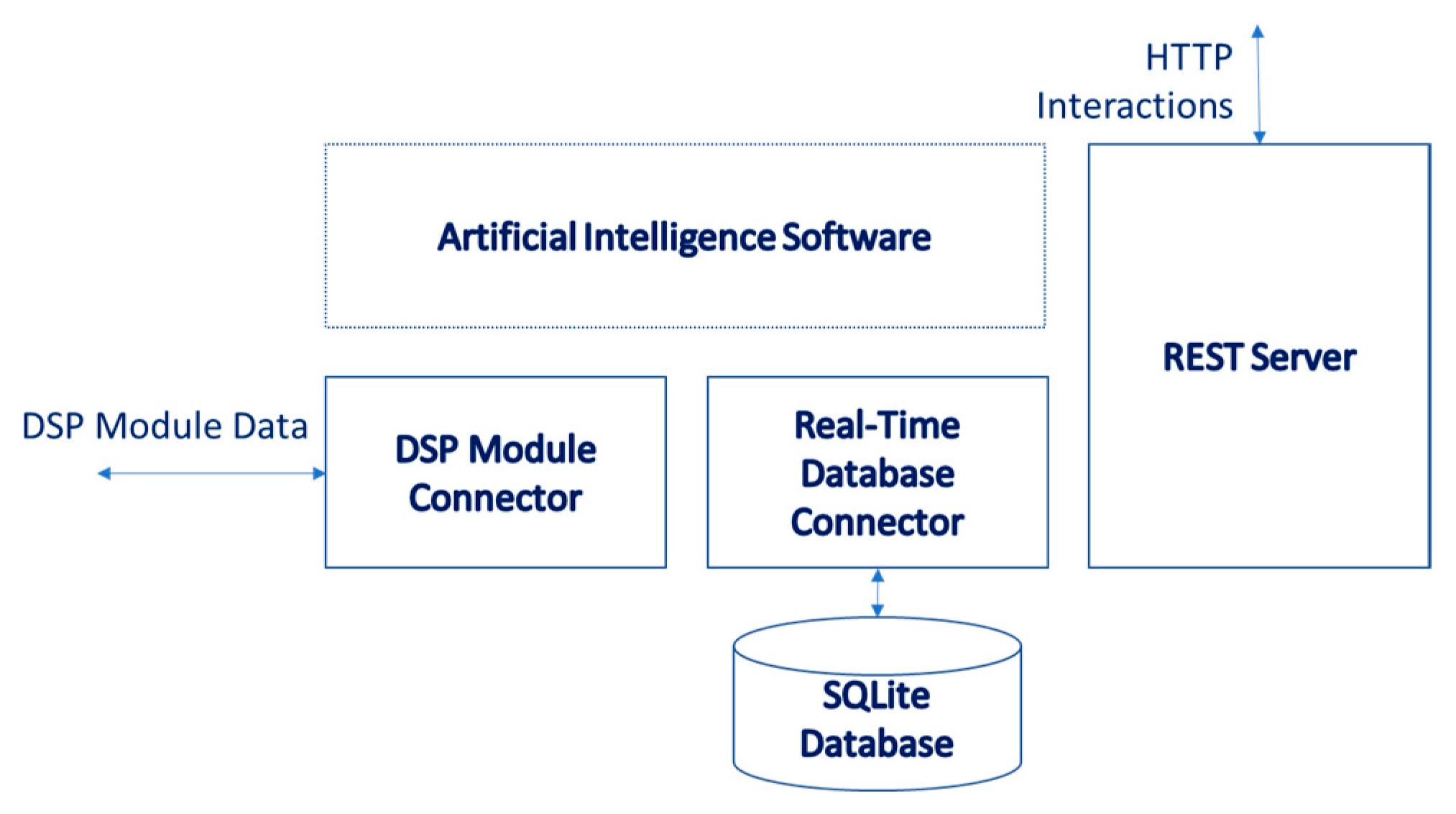

- Command and control of the PMU, including commands for the DSP module;

- Acquisition of data generated by the DSP module;

- Local database;

- Communication with backend/frontend applications;

- Communication with other OpenEdgePMUs;

- Execution of artificial intelligence functionalities.

- The DSP module connector is responsible for connecting the edge processing module application with the DSP module via the serial port. After a successful connection, it can retrieve the current measurement of the DSP module. Additionally, it is responsible for periodically retrieving the latest measurements of the DSP module. It also stores the measurements to the database after successful retrieval.

- The REST server is a stand-alone service, based on the Flask framework, and is responsible for deploying a RESTful API on the edge processing module application, to serve HTTP requests. Such requests can refer to the latest measurements retrieved from the DSP module, historic measurements, or the status of the device (e.g., connection status, free storage space, MAC address, etc.). For the first two types of requests, the REST server connects directly to the database and retrieves the requested data, while for the third type of request, the REST server obtains the relevant information directly from the OS, by executing certain Linux commands. In all cases, the REST server will reply to the client with a REST protocol HTTP response, containing either the requested data upon success, or an error message upon failure.

- The real-time database component acts as a bridge between the edge processing module application and the database. Any measurements that must be stored are first sent to this agent, who is then responsible for storing them properly. Additionally, this agent handles write errors (e.g., duplicate values), database connectivity issues, and provides the state fetcher agent any measurements that might be requested. The latter functionality is crucial when storing rows across multiple tables, which must link their data by utilizing foreign keys.

- The SQLite database application, after retrieving the measurements, takes care of storing the measurements in the database that the device has in its storage disk. Since this database is installed on each device, it is important to consider some basic parameters, such as the storage frequency and the size of the tables. A fine balance between collecting adequate data samples for future analysis and properly utilizing the limited storage space is found in one-minute sampling of the real-time DSP module measurements. Regarding the storage frequency, the storage (by the gateway application) and the retrieval (by the main application) can differ. In addition, the database used is relational and is based on SQLite technology. It is noted that the database already has a predetermined structure that allows the continuous storage of PMU and RTU data.

2.4. GPS Module

2.5. Power Supply Module

- Input range, 90–305 VACl;

- Isolation, 4000 VAC;

- Consumption, 5 Watt max;

- Other, option to power from phase A and neutral.

3. Results and Discussion

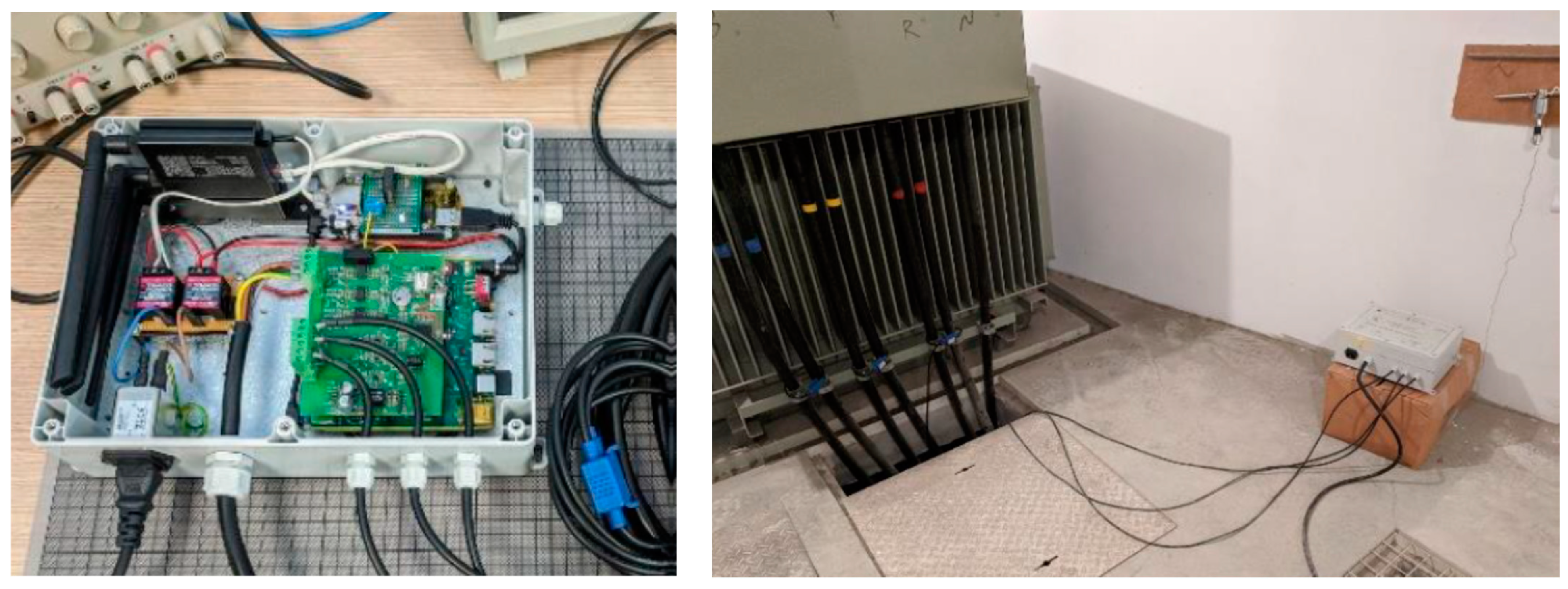

3.1. Hardware Implementation

- The DSP board is one of the key components in the OpenEdgePMU system. To simplify the overall design and utilization of the DSP in different devices, the DSP board is segregated by having its own design. In this way, a separate board was designed to include all the necessary components required for the DSP to operate with the aim to keep the digital high-speed electronics section segregated and to expose all the necessary interfaces via a common board-to-board mezzanine connector. The idea is that the DSP board is mounted onto the main board of the PMU module, which has a simpler design and uses only the necessary interfaces required. Figure 9 shows the top side of the DSP board, depicting its main components (DSP, external memory modules, power regulator, crystal etc.). The DSP Board has:

- Dimensions, 67 mm × 52 mm;

- Number of components, 203;

- PCB layers, 8;

- Schematic sheets, 12;

- Estimated cost, €120.

- Regarding the edge board, as shown in Figure 10, the edge processing module is also segregated from the OpenEdgePMU system; it is essentially a separate board that is connected to the OpenEdgePMU base board. This board includes the most essential elements to make the MCU OSD3358 SoC operate properly, and all the interfaces are exposed to two mezzanine connectors to be used in other designs depending on the application. This is done to simplify the design process and to easily accommodate different designs utilized in different devices. Figure 10 depicts the top side of the edge board. The edge board has:

- Dimensions, 60 mm × 44 mm;

- Number of components, 144;

- PCB layers, 6;

- Schematic sheets, 7;

- Estimated cost, €200.

- The main board includes all other electronic components of the OpenEdgePMU system, such as the power supply, the analog conditioning and ADC part of the DSP module, input/output connectors, etc., as well as all other sockets suitable to attach the rest of the circuits, such as the DSP board, the edge board, and the GPS. Figure 12 shows the board without and with system add-on components. The main board has:

- Dimensions, 135 mm × 150 mm;

- Number of components, 201;

- PCB layers, 2;

- Schematic sheets, 10;

- Estimated cost, €150.

3.2. Current Funded Projects Using the OpenEdgePMU System

3.2.1. eBalance+ Project (European Union H2020)

3.2.2. TEXNOREYMETA Project (Greek National Funded)

- Real-time power quality analysis based on EN50160;

- Energy meter for secondary distribution substation;

- Phasor measurement unit.

3.3. AI and Optimization Application Examples Using the OpenEdgePMU System

3.3.1. Power Flow (PF)

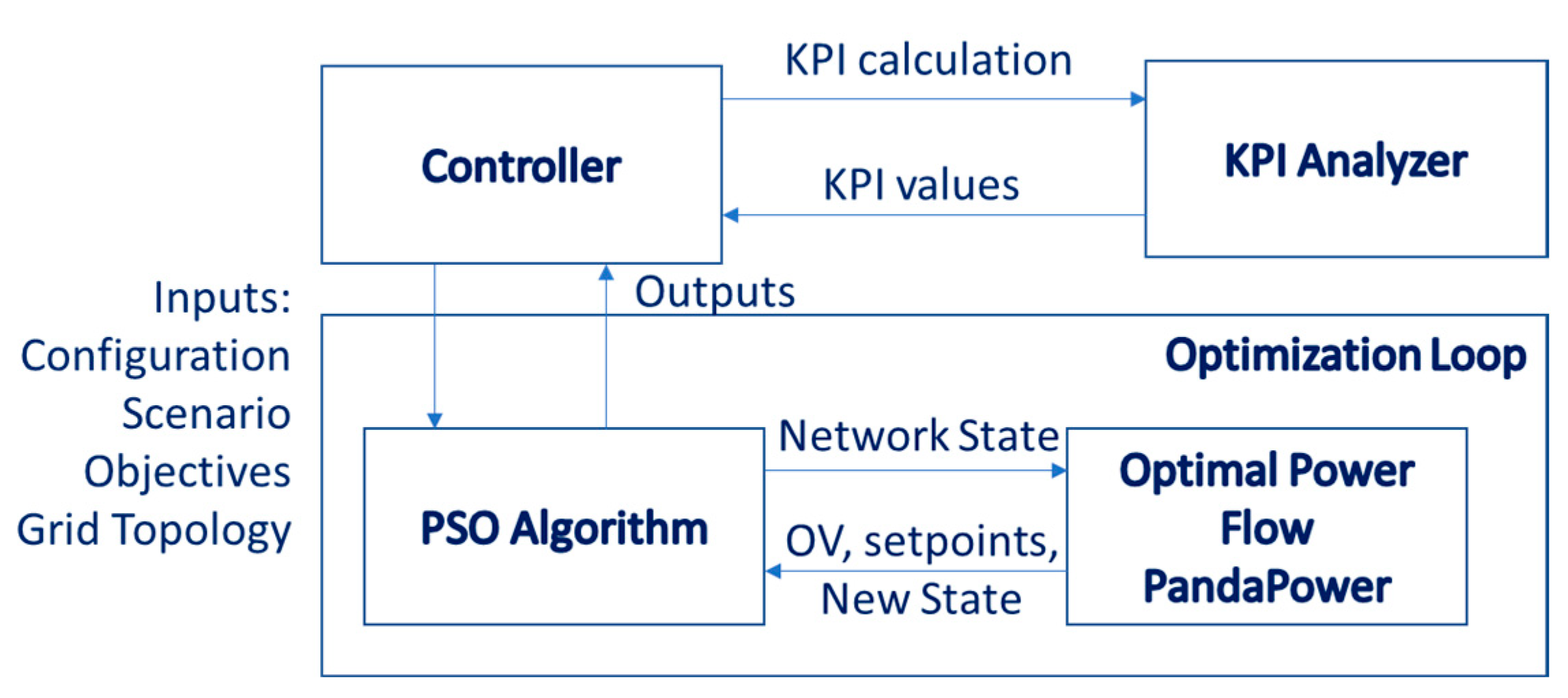

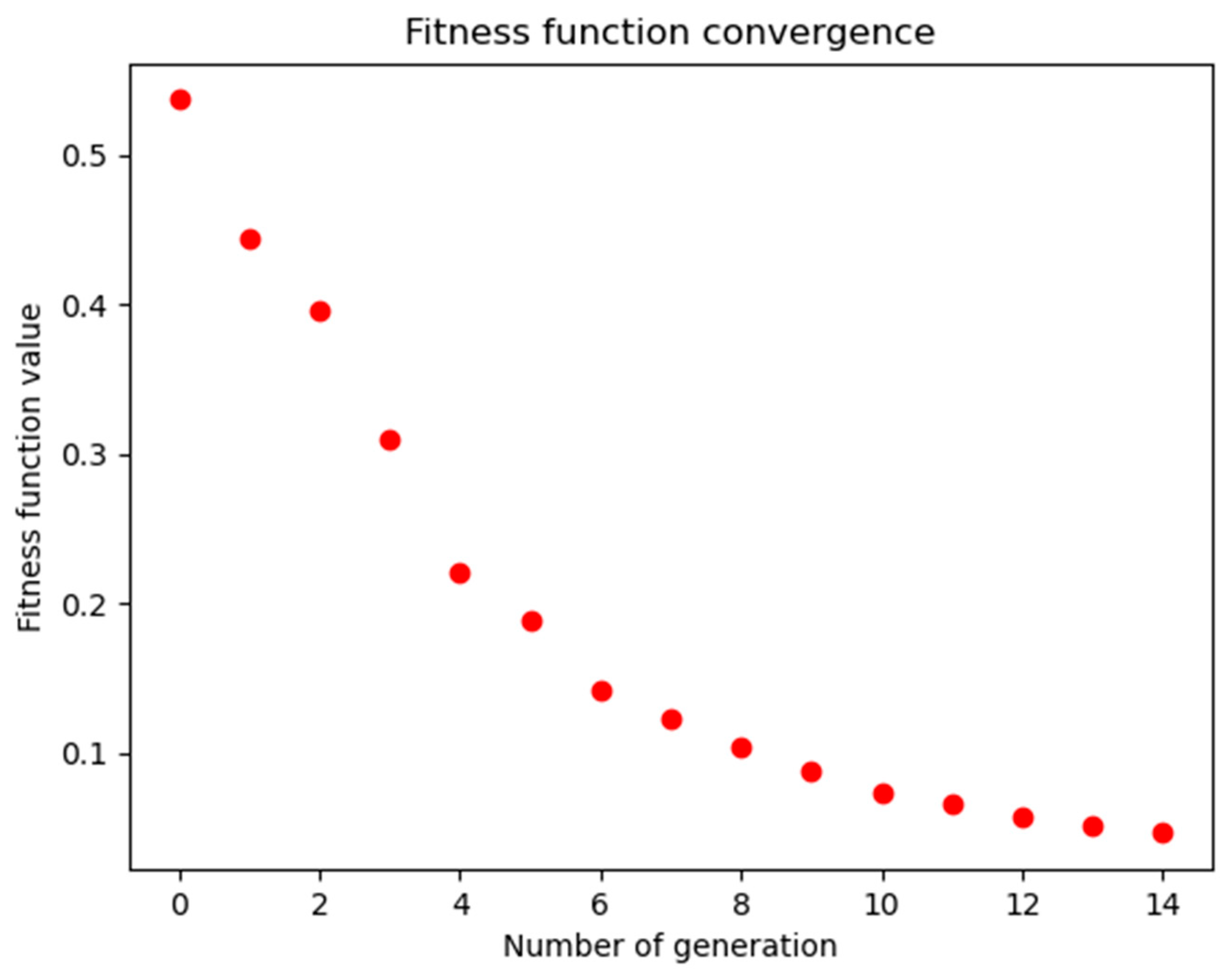

3.3.2. Optimal Power Flow (OPF)

- Voltage limits of node

- Generation limits of generation nodes

- Tap limits on branch

- Loading limit of branch

- External grid active and reactive power injection limits

- Upper and lower limits of the curtailed power of each RES unit

- Active and reactive power balance at nodewhere and are the active and reactive load, and and are the incoming or outgoing active and reactive power. Similar to PF, OPF is also executed with the help of PandaPower. The inputs of the algorithm consist of (a) the grid’s topology and (b) the real-time state of the grid. The desired target objective must also be determined which may differ among:

- real power losseswhere is the total active power losses in the distribution network, is the number of branches, is the resistance in the branch , and is the current in the branch .

- voltage deviation minimizationwhere is the prespecified reference voltage value at -th load bus, which is usually set at the value of 1.0 p.u. and N is the number of load buses,

- RES curtailment minimizationwhere is a weight factor of the curtailed power of the -th RES unit, with .

3.3.3. Load Prediction Based on AI

- sc001, weekdays of one year;

- sc011, daylight hours of one year;

- sc013, daylight hours of weekdays only of one year;

- sc034, spring days of one year;

- sc035, summer days of one year.

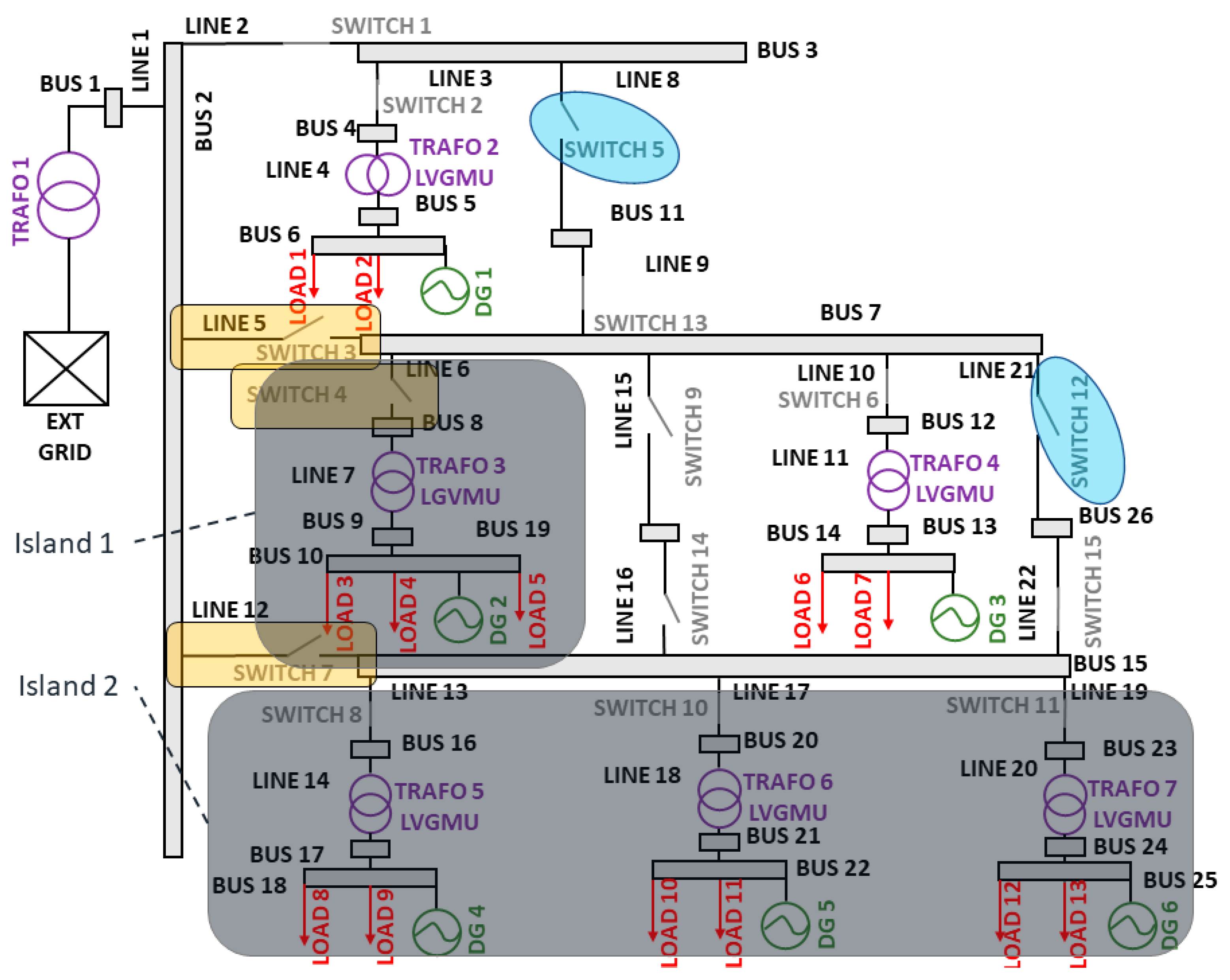

3.3.4. Islanding

- Assume that failures are detected on Lines 5, 6, 12, and 16 of the grid topology shown in Figure 17.

- Assume also that, initially, all switches are closed except for Switches 5, 9, 12, and 14.

- The aforementioned failures lead to opening Switches 3, 4, and 7. Then, two possible islanding setups are obtained:

- Setup (a), closing Switch 5, Islands 1 and 2 are formed;

- Setup (b), closing Switches 5, and 15, Island 1 is formed.

- For each islanding setup, OPF is conducted, and the respective objective value is obtained, as shown in Table 3. Islanding setup (a) is selected as it achieves the minimum objective value.

- Islanding setup (a) is applied, and then load shedding is conducted to maintain power supply to as many consumers as possible, as presented in Table 4. In this case, no load shedding is taking place, as the required demand does not exceed the available energy produced. The islanding algorithm is completed by solving the OPF problem for each island to ensure that power losses are minimized.

3.4. Discussion and Remarks

4. Conclusions

- Provide state-of-the art, low-cost hardware and software that can process future edge processing requirements in energy smart grids;

- Lower technology entry barriers, specially regarding academic and SMEs/startups;

- Fuse cross-disciplinary knowledge that potentially may come from further contributors;

- Investigate alternative business models and market opportunities in future resilient smart distribution grids;

- Promote open innovation with collaboration between SMEs and academia.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wache, M.; Murray, D.C. Application of Synchrophasor Measurements for distribution networks. In Proceedings of the 2011 IEEE Power and Energy Society General Meeting, Detroit, MI, USA, 24–29 July 2011. [Google Scholar]

- Hojabri, M.; Dersch, U.; Papaemmanouil, A.; Bosshart, P. A Comprehensive Survey on Phasor Measurement Unit Applications in Distribution Systems. Energies 2019, 12, 4552. [Google Scholar] [CrossRef]

- Stewart, E.M.; Kiliccote, S.; Shand, C.M.; McMorran, A.W.; Arghandeh, R.; von Meier, A. Addressing the challenges for integrating micro-synchrophasor data with operational system applications. In Proceedings of the 2014 IEEE PES General Meeting, Conference & Exposition, National Harbor, MD, USA, 27–31 July 2014. [Google Scholar]

- Dusabimana, E.; Yoon, S.-G. A Survey on the Micro-Phasor Measurement Unit in Distribution Networks. Electronics 2020, 9, 305. [Google Scholar] [CrossRef]

- Phadke, A.G.; Thorp, J.S. History and applications of phasor measurements. In Proceedings of the 2006 IEEE PES Power Systems Conference and Exposition, Atlanta, GA, USA, 29 October–1 November 2006; pp. 331–335. [Google Scholar]

- von Meier, A.; Culler, D.; McEachern, A.; Arghandeh, R. Microsynchrophasors for distribution system. In Proceedings of the 5th IEEE PES Innovative Smart Grid Technologies (ISGT) European 2014 Conference, Washington, DC, USA, 19–22 February February 2014; pp. 1–5. [Google Scholar]

- Rietveld, G.; Jongepier, A.; Seters, J.V.; Visser, M.; Liu, P.; Acanski, M.; Hoogenboom, D.; Brom, H.E.V.D. Application of PMUs for Monitoring a 50 kV Distribution Grid. In Proceedings of the CIRED Conference, Lyon, France, 15–18 June 2015; pp. 1–5. [Google Scholar]

- Carta, A.; Locci, N.; Muscas, C.; Sulis, S. A flexible GPS-based system for synchronized phasor measurement in electric distribution networks. IEEE Trans. Instrum. Meas. 2008, 57, 2450–2456. [Google Scholar] [CrossRef]

- Laverty, D.M.; Best, R.J.; Brogan, P.; Al Khatib, I.; Vanfretti, L.; Morrow, D.J. The OpenPMU Platform for Open-Source Phasor Measurements. IEEE Trans. Instrum. Meas. 2013, 62, 701–709. [Google Scholar] [CrossRef]

- IEEE Std C37.118.1-2011 (Revision of IEEE Std C37.118-2005); IEEE Standard for Synchrophasor Measurements for Power Systems. IEEE Standards Association: New York, NY, USA, 2011; pp. 1–61.

- IEEE Std C37.118.1a-2014 (Amendment to IEEE Std C37.118.1-2011); IEEE Standard for Synchrophasor Measurements for Power Systems—Amendment 1: Modification of Selected Performance Requirements. IEEE Standards Association: New York, NY, USA, 2014; pp. 1–25.

- The Open Source Initiative OSI—The BSE License. Available online: http://www.opensource.orge/licenses/bsd-license.php (accessed on 12 February 2023).

- GNU General Public License. Available online: http://www.opensource.org/licenses/bsd-license.php (accessed on 12 February 2023).

- Open Hardware Licenses, The Foundation for P2P Alternatives. Available online: http://p2pfoundation.net/Open_Hadware_licenses (accessed on 12 February 2023).

- The TAPR Open Hardware License. Available online: http://www.tapr.org/ohl.html (accessed on 12 February 2023).

- GridTrak—Home Page. Available online: http://www.gridtrak.com (accessed on 12 February 2023).

- He, Z.; Liao, Y. The design of analog acquisition system in distribution automation. In Proceedings of the 2012 China International Conference on Electricity Distribution, Venice, Italy, 9–12 September 2012; pp. 1–4. [Google Scholar]

- Du, L.; Huang, J.K.; Liu, Q.Y. A realisation of measurement unit for phasor measurement unit based on DSP. In Proceedings of the Asia-Pacific Power and Energy Engineering Conference (APPEEC), Shanghai, China, 27–29 March 2012. [Google Scholar]

- Romano, P.; Paolone, M.; Chau, T.; Jeppesen, B.; Ahmed, E.A. A high-performance, low-cost PMU prototype for distribution networks based on FPGA. In Proceedings of the 2017 IEEE Manchester PowerTech, Manchester, UK, 18–22 June 2017. [Google Scholar]

- Pinte, B.; Quinlan, M.; Reinhard, K. Low voltage micro-phasor measurement unit (μPMU). In Proceedings of the 2015 IEEE Power and Energy Conference at Illinois (PECI), 20–21 February 2015. [Google Scholar]

- Rodrigues, R.N.; Cavalcante, L.H.; Zatta, J.K.; Schlichting, L.C.M. A Phasor Measurement Unit based on discrete fourier transform using digital signal processor. In Proceedings of the 2016 12th IEEE International Conference on Industry Applications (INDUSCON), Curitiba, Brazil, 20–23 November 2016; pp. 1–6. [Google Scholar]

- Discovery Ket with STM32F407VG MCU. Available online: http://www.st.com/en/evaluation-tools/stm32f4discovery.html (accessed on 12 February 2023).

- Das, H.P.; Pradhan, A.K. Development of a micro-phasor measurement unit for distribution system applications. In Proceedings of the National Power Systems Conference (NPSC), Bhubaneswar, India, 19–21 December 2016; pp. 1–5. [Google Scholar]

- Bhatti, T.A.; Raheem, A.; Alam, T.; Malik, M.O.; Munir, A. Implementation of low cost non-DFT based Phasor Measurement Unit for 50 Hz power system. In Proceedings of the 2016 International Conference on Computing, Electronic and Electrical Engineering (ICE Cube), Quetta, Pakistan, 11–12 April 2016; pp. 120–125. [Google Scholar]

- Angioni, A.; Lipari, G.; Pau, M.; Ponci, F.; Monti, A. A Low Cost PMU to Monitor Distribution Grids. In Proceedings of the AMPS 2017—IEEE International Workshop on Applied Measurements for Power Systems, Liverpool, UK, 20–22 September 2017. [Google Scholar]

- Zhao, X.; Laverty, D.M.; McKernan, A.; Morrow, D.J.; McLaughlin, K.; Sezer, S. GPS-Disciplined Analog-to-Digital Converter for Phasor Measurement Applications. IEEE Trans. Instrum. Meas. 2017, 66, 2349–2357. [Google Scholar] [CrossRef]

- Cetina, R.Q.; Roscoe, A.J.; Atoche, A.C. Low-cost power systems metrology laboratory based on raspberry Pi. In Proceedings of the 1st International Colloquium on Smart Grid Metrology (SmaGriMet), Split, Croatia, 24–27 April 2018; pp. 1–2. [Google Scholar]

- Schofield, D.; Gonzalez-Longatt, F.; Bogdanov, D. Design and Implementation of a Low-Cost Phasor Measurement Unit: A Comprehensive Review. In Proceedings of the 2018 Seventh Balkan Conference on Lighting (BalkanLight), Varna, Bulgaria, 20–22 September 2018; pp. 1–6. [Google Scholar]

- Bucci, G.; Ciancetta, F.; D’Innocenzo, F.; Fiorucci, E.; Ometto, A. Development of a low cost power meter based on a digital signal controller. Int. J. Emerg. Electr. Power Syst. 2018, 19, 20170280. [Google Scholar] [CrossRef]

- Femine, A.D.; Gallo, D.; Landi, C.; Luiso, M. A design approach for a low cost phasor measurement unit. In Proceedings of the I2MTC 2019—2019 IEEE International Instrumentation and Measurement Technology Conference, Auckland, New Zealand, 20–23 May 2019. [Google Scholar]

- Seger, P.V.H.; Moreto, M.; Grando, F.L.; Lazzaretti, A.E.; Denardin, G.W.; Pastro, C.R. Monitoring Low Voltage Electrical Networks Using Low Cost PMUs: A Case Study. In Proceedings of the 2020 IEEE International Conference on Environment and Electrical Engineering and 2020 IEEE Industrial and Commercial Power Systems Europe (EEEIC/I and CPS Europe), Madrid, Spain, 9–12 June 2020. [Google Scholar]

- Shankar, G.; Ray, S.; Goyal, S.R.; Srinivas, R. Development of a Low Cost Phasor Measurement Unit for Laboratory Studies. In Proceedings of the 2021 1st International Conference on Power Electronics and Energy (ICPEE), Bhubaneswar, India, 2–3 January 2021. [Google Scholar]

- Raju, V.V.R.; Shree, K.H.P.; Kumar, S.V.J. Development of cost-effective phasor measurement unit for wide area monitoring system applications. Int. J. Electr. Comput. Eng. 2021, 11, 4731–4739. [Google Scholar] [CrossRef]

- Schofield, D.; Mohapatra, D.; Chamorro, H.R.; Roldan-Fernandez, J.M.; Abdellah, K.; Gonzalez-Longatt, F. Design and Implementation of Low-Cost Phasor Measurement Unit: PhasorsCatcher. Energies 2022, 15, 3172. [Google Scholar] [CrossRef]

- Mohapatra, D. Development and Hardware Implementation of a Phasor Measurement Unit Using Microcontroller. NIT Rourkela Ed. Available online: http://ethesis.nitrkl.ac.in/7621/1/2015_MT_Development_Debasis_mohapatra.pdf (accessed on 20 March 2022).

- Sampson, O.V. Construction of a Phasor Measurement Unit (PMU) for Power System Applications. Ph.D. Thesis, University of Manitoba, Winnipeg, MB, Canada, 2015. [Google Scholar]

- Culliss, J.A. A 3rd Generation Frequency Disturbance Recorder: A Secure, Low Cost Synchophasor Measurement Device. Ph.D. Thesis, Department of Electrical Engineering and Computer Science, University of Tennessee, Knoxville, TN, USA, 2015. [Google Scholar]

- Raspberry Pi. Available online: https://www.raspberrypi.org (accessed on 12 February 2023).

- Beagle Bone Black. Available online: https://beagleboard.org/black (accessed on 12 February 2023).

- Marcus, Y.; Silverstein, A. Factors Affecting PMU Installation Costs; Tech. Rep.; Office of Electricity Delivery and Energy Reliability, U.S. Department of Energy: Houston, TX, USA, 2014.

- TMDSEVM5517—C5517 Evaluation Module (EVM). Available online: https://www.ti.com/tool/TMDSEVM5517 (accessed on 12 February 2023).

- Texas Instruments. TMS320C5517 Fixed-Point Digital Signal Processor, Data Sheet, SPRS727C. Available online: https://www.ti.com/lit/ds/symlink/tms320c5517.pdf (accessed on 12 February 2023).

- Micron SDRAM MT48H32M16LF—Data Sheet. Available online: https://media-www.micron.com/-/media/client/global/documents/products/data-sheet/dram/mobile-dram/low-power-dram/lpsdr/y67m_512mb_mobile_lpsdr_at.pdf (accessed on 12 February 2023).

- Infineon FLASH S29GL128S11DHIV20—Data Sheet. Available online: https://www.infineon.com/dgdl/Infineon-S29GL01GS_S29GL512S_S29GL256S_S29GL128S_128_Mb_256_Mb_512_Mb_1_Gb_GL-S_MIRRORBIT_TM_Flash_Parallel_3-DataSheet-v20_00-EN.pdf (accessed on 12 February 2023).

- SanDisk Extreme® microSD™ UHS-I Card, Data Sheet. Available online: https://documents.westerndigital.com/content/dam/doc-library/en_us/assets/public/sandisk/product/memory-cards/extreme-uhs-i-microsd/data-sheet-extreme-uhs-i-microsd.pdf (accessed on 12 February 2023).

- Texas Instruments. ADS8586S 16-Bit, High-Speed, 6-Channel, Simultaneous-Sampling ADC with Bipolar Inputs on a Single Supply, Data Sheet, SBAS833A. Available online: https://www.ti.com/lit/ds/symlink/ads8586s.pdf (accessed on 12 February 2023).

- Xmodem Protocol. Available online: https://en.wikipedia.org/wiki/XMODEM (accessed on 12 February 2023).

- Octavo Systems; Rev, I.N.D. 2022. Available online: https://octavosystems.com/octavosystems.com/wp-content/uploads/2017/08/OSD335x-SM-Datasheet.pdf (accessed on 12 February 2023).

- Panda Power. Available online: www.pandapower.org (accessed on 12 February 2023).

- Pandas: A Numerical and Data Analysis Library. Available online: https://pydata.org (accessed on 12 February 2023).

- Scikit-Learn: An AI Construction and Execution Library. Available online: https://scikit-learn.org/stable/index.html (accessed on 12 February 2023).

- Flask: A Library for the Development of HTTP-REST Interfaces. Available online: https://flask.palletsprojects.com/en/2.2.x/ (accessed on 12 February 2023).

- SQLite: A Library for the Interaction with the Local SQLite Database. Available online: https://www.sqlite.org/index.html (accessed on 12 February 2023).

- Lantronix, GPS/GLONASS Receiver Module A5100-A, Data Sheet. Available online: https://cdn.lantronix.com/wp-content/uploads/pdf/A5100_UG.pdf (accessed on 12 February 2023).

- Adafruit Ultimate GPS, Data Sheet. Available online: https://cdn-shop.adafruit.com/datasheets/PA6B-Datasheet-A07.pdf (accessed on 12 February 2023).

- eBalance+ European Union Project. Available online: https://www.ebalanceplus.eu (accessed on 12 February 2023).

- Techoreymeta Greek National Project. Available online: https://tehnorevmeta.emtech.global/ (accessed on 12 February 2023).

- Vaccaro, A.; Canizares, C. A knowledge-based framework for power flow and optimal power flow analyses. In Proceedings of the 2017 IEEE Power & Energy Society General Meeting, Chicago, IL, USA, 16–20 July 2017; p. 1. [Google Scholar] [CrossRef]

- Thurner, L.; Scheidler, A.; Probst, A.; Braun, M. Heuristic optimization for network restoration and expansion in compliance with the single contingency policy. IET Gener. Transm. Distrib. 2017, 11, 4264–4273. [Google Scholar] [CrossRef]

- Scheidler, A.; Thurner, L.; Braun, M. Heuristic optimisation for automated distribution system planning in network integration studies. IET Renew. Power Gener. 2018, 12, 530–538. [Google Scholar] [CrossRef]

- Menke, J.-H.; Hegemann, J.; Gehler, S.; Braun, M. Heuristic monitoring method for sparsely measured distribution grids. Int. J. Electr. Power Energy Syst. 2018, 95, 146–155. [Google Scholar] [CrossRef]

- Wang, H.; Kraiczy, M.; von Berg, S.W.-V.B.S.W.; Kämpf, E.; Ernst, B.; Schmidt, S.; Wirtz, F.; Braun, M. Reactive power coordination on strategies with distributed generators in distribution networks. In Proceedings of the 1st International Conference on Large-Scale Grid Integration of Renewable Energy in India, Delhi, India, 6–8 September 2017. [Google Scholar]

- Frank, S.; Steponavice, I.; Rebennack, S. Optimal power flow: A bibliographic survey I. Energy Syst. 2012, 3, 221–258. [Google Scholar] [CrossRef]

- Frank, S.; Rebennack, S. A Primer on Optimal Power Flow: Theory, Formulation, and Practical Examples; Colorado School of Mines: Golden, CO, USA, 2012; pp. 1–42. [Google Scholar]

- Abido, M.A. Optimal Power Flow Using Particle Swarm Optimization. Electr. Power Energy Syst. 2002, 24, 563–571. [Google Scholar] [CrossRef]

- Osman, M.S.; Abo-Sinna, M.A.; Mousa, A.A. A solution to the optimal power flow using genetic algorithm. Appl. Math. Comp. 2004, 155, 391–405. [Google Scholar] [CrossRef]

- Papadimitrakis, M.; Giamarelos, N.; Stogiannos, M.; Zois, E.N.; Livanos, N.A.I.; Alexandridis, A. Metaheuristic search in smart grid: A review with emphasis on planning, scheduling and power flow optimization applications. Renew. Sustain. Energy Rev. 2021, 145, 111072. [Google Scholar] [CrossRef]

- Mittal, U.; Nangia, U.; Jain, N.K. Computational Intelligence-Based Optimal Power Flow Methods-A Review. In Proceedings of the 2022 IEEE Delhi Section Conference (DELCON), New Delhi, India, 11–13 February 2022; pp. 1–8. [Google Scholar] [CrossRef]

- Maskar, M.B.; Thorat, A.R.; Korachgaon, I. A review on optimal power flow problem and solution methodologies. In Proceedings of the 2017 International Conference on Data Management, Analytics and Innovation (ICDMAI), Pune, India, 24–26 February 2017; pp. 64–70. [Google Scholar] [CrossRef]

- Theodoridis, S. Machine Learning: A Bayesian and Optimization Perspective; Academic Press: Cambridge, MA, USA, 2015. [Google Scholar]

- Mamun, A.A.; Sohel, M.; Mohammad, N.; Sunny, M.S.H.; Dipta, D.R.; Hossain, E. A Comprehensive Review of the Load Forecasting Techniques Using Single and Hybrid Predictive Models. IEEE Access 2020, 8, 134911–134939. [Google Scholar] [CrossRef]

- Sun, X.; Ouyang, Z.; Yue, D. Short-term load forecasting based on multivariate linear regression. In Proceedings of the 2017 IEEE Conference on Energy Internet and Energy System Integration (EI2), Beijing, China, 26–28 November 2017; pp. 1–5. [Google Scholar] [CrossRef]

- Azad, S.A.; Ali, A.B.M.S.; Wolfs, P. Daily average load forecasting using dynamic linear regression. In Proceedings of the Asia-Pacific World Congress on Computer Science and Engineering, Nadi, Fiji, 4–5 November 2014; pp. 1–7. [Google Scholar] [CrossRef]

- Azad, M.K.; Uddin, S.; Takruri, M. Support vector regression based electricity peak load forecasting. In Proceedings of the 11th International Symposium on Mechatronics and Its Applications (ISMA), Sharjah, United Arab Emirates, 4–6 March 2018; pp. 1–5. [Google Scholar] [CrossRef]

- Chen, W.; Chen, X.; Liao, Y.; Wang, G.; Yao, J.; Chen, K. Short-term load forecasting based on time series reconstruction and support vector regression. In Proceedings of the 2013 IEEE International Conference of IEEE Region 10 (TENCON 2013), Xi’an, China, 22–25 October 2013; pp. 1–4. [Google Scholar] [CrossRef]

- Chowdhury, D.; Sarkar, M.; Haider, M.Z.; Alam, T. Zone Wise Hourly Load Prediction Using Regression Decision Tree Model. In Proceedings of the 2018 International Conference on Innovation in Engineering and Technology (ICIET), Dhaka, Bangladesh, 27–28 December 2018; pp. 1–6. [Google Scholar] [CrossRef]

- Lahouar, A.; Slama, J.B.H. Random forests model for one day ahead load forecasting. In Proceedings of the IREC2015 the Sixth International Renewable Energy Congress, Sousse, Tunisia, 24–26 March 2015; pp. 1–6. [Google Scholar] [CrossRef]

- Singh, S.; Hussain, S.; Bazaz, M.A. Short term load forecasting using artificial neural network. In Proceedings of the 2017 Fourth International Conference on Image Information Processing (ICIIP), Shimla, India, 21–23 December 2017; pp. 1–5. [Google Scholar] [CrossRef]

- Akarslan, E.; Hocaoglu, F.O. Electricity demand forecasting of a micro grid using ANN. In Proceedings of the 2018 9th International Renewable Energy Congress (IREC), Hammamet, Tunisia, 20–22 March 2018; pp. 1–5. [Google Scholar] [CrossRef]

- Zheng, J.; Xu, C.; Zhang, Z.; Li, X. Electric load forecasting in smart grids using Long-Short-Term-Memory based Recurrent Neural Network. In Proceedings of the 2017 51st Annual Conference on Information Sciences and Systems (CISS), Baltimore, MD, USA, 22–24 March 2017; pp. 1–6. [Google Scholar] [CrossRef]

- Giamarelos, N.; Zois, E.N.; Papadimitrakis, M.; Stogiannos, M.; Livanos, N.-A.I.; Alexandridis, A. Short-Term Electric Load Forecasting With Sparse Coding Methods. IEEE Accesss 2021, 9, 102847–102861. [Google Scholar] [CrossRef]

- Deng, Z.; Wang, B.; Xu, Y.; Xu, T.; Liu, C.; Zhu, Z. Multi-Scale Convolutional Neural Network With Time-Cognition for Multi-Step Short-Term Load Forecasting. IEEE Access 2019, 7, 88058–88071. [Google Scholar] [CrossRef]

- Mi, Y.; Chen, Y.; Yuan, M.; Li, Z.; Tao, B.; Han, Y. Multi-Timescale Optimal Dispatching Strategy for Coordinated Source-Grid-Load-Storage Interaction in Active Distribution Networks Based on Second-Order Cone Planning. Energies 2023, 16, 1356. [Google Scholar] [CrossRef]

- Daneshi, H.; Daneshi, A. Price forecasting in deregulated electricity markets—A bibliographical survey. In Proceedings of the 2008 Third International Conference on Electric Utility Deregulation and Restructuring and Power Technologies, Nanjing, China, 6–9 April 2008; pp. 657–661. [Google Scholar] [CrossRef]

- Wu, L.; Shahidehpour, M.; Li, T. Stochastic Security-Constrained Unit Commitment. IEEE Trans. Power Syst. 2007, 22, 800–811. [Google Scholar] [CrossRef]

- Ooi, B.T.; Mcgillis, D.; Galiana, F.D.; Marceau, R. The Potential of Distributed Generation to Provide Ancillary Services. In Proceedings of the 2000 Power Engineering Society Summer Meeting (Cat. No.00CH37134), Seattle, WA, USA, 16–20 July 2000; pp. 1762–1767. [Google Scholar]

- Lalor, G.; Mullane, A.; O’Malley, M. Frequency control and wind turbine technologies. IEEE Trans. Power Syst. 2005, 20, 1905–1913. [Google Scholar] [CrossRef]

- Brenna, M.; Foiadelli, F.; Petroni, P.; Sapienza, G.; Zaninelli, D. Distributed generation regulation for intentional islanding in Smart Grids. In Proceedings of the 2012 IEEE PES Innovative Smart Grid Technologies (ISGT), Washington, DC, USA, 16–20 January 2012; pp. 1–6. [Google Scholar] [CrossRef]

- Corti, M.; Superti-Furga, G.; Tironi, E.; Pavan, A.M.; Sulligoi, G. Intentional islanding in medium voltage distribution grids. In Proceedings of the 2016 IEEE 16th International Conference on Environment and Electrical Engineering (EEEIC), Florence, Italy, 7–10 June 2016; pp. 1–6. [Google Scholar] [CrossRef]

- Conti, S.; Rizzo, S.A. Monte Carlo Simulation by Using a Systematic Approach to Assess Distribution System Reliability Considering Intentional Islanding. IEEE Trans. Power Deliv. 2015, 30, 64–73. [Google Scholar] [CrossRef]

- Oboudi, M.H.; Mohammadi, M.; Rastegar, M. Resilience-oriented intentional islanding of reconfigurable distribution power systems. J. Mod. Power Syst. Clean Energy 2019, 7, 741–752. [Google Scholar] [CrossRef]

- Mantas, V.; Soderquist, K.E. Open Innovation: Activating the Entrepreneurial Mindset. In Proceedings of the 5th European Conference on Innovation and Entrepreneurship, Athens, Greece, 16–17 September 2010. [Google Scholar]

- OpenEdgePMU Portal. Available online: https://oepmu.emtech.global (accessed on 12 February 2023).

- OpenEdgePMU Gitlab. Available online: https://gitlab.com/oepmu/open-edge-pmu (accessed on 12 February 2023).

- “Open Source Phasor Data Concentrator” Grid Protection Alliance. Available online: https://github.com/GridProtectionAlliance/openPDC (accessed on 12 February 2023).

- OpenIEC61850. Available online: www.openmuc.org/iec-61850 (accessed on 12 February 2023).

| Topology | IEEE 123 |

|---|---|

| Objective | Real power losses |

| KPI initial value | 3.360886005262138 |

| KPI optimized value | 0.1510907405190642 |

| Method/ Scenario | 15 Min (sc013) | 1 h (sc011) | 6 h (sc034) | 12 h (sc001) | 24 h (sc035) | |||||

|---|---|---|---|---|---|---|---|---|---|---|

| R2 | MAE | R2 | MAE | R2 | MAE | R2 | MAE | R2 | MAE | |

| LR | 0.9731 | 0.9189 | 0.8805 | 2.2507 | 0.7261 | 3.4779 | 0.7571 | 2.9458 | 0.8562 | 2.6320 |

| CART | 0.9718 | 0.9303 | 0.8945 | 2.0556 | 0.7743 | 2.9189 | 0.7803 | 2.6624 | 0.8332 | 2.8246 |

| RF | 0.9720 | 0.9272 | 0.8948 | 2.0496 | 0.7741 | 2.9117 | 0.7806 | 2.6557 | 0.8658 | 2.5198 |

| MLP | 0.9734 | 0.8959 | 0.8898 | 2.0793 | 0.7533 | 3.1473 | 0.7461 | 2.8195 | 0.8569 | 2.6001 |

| LSTM | 0.9720 | 0.9564 | 0.8814 | 2.20008 | 0.7556 | 3.1903 | 0.7719 | 2.8539 | 0.8592 | 2.6377 |

| SVR | 0.9724 | 0.9155 | 0.8751 | 2.2201 | 0.7244 | 3.3945 | 0.7379 | 2.9913 | 0.8539 | 2.5498 |

| Configuration | OPF Solution (RPL) |

|---|---|

| a | 0.007605321647110751 |

| b | 3.360886005262138 |

| Island | Generation Unit | Consumption | Load Shedding | OPF Results (OPF) |

|---|---|---|---|---|

| #1 | SGEN 2 = 0.15 | LOAD 3 = 0.01 | No | 0.00010976394887844073 |

| LOAD 4 = 0.01 | ||||

| LOAD 5 = 0.01 | ||||

| Total = 0.03 | ||||

| #2 | SGEN 4 = 0.15 SGEN 5 = 0.15 SGEN 6 = 0.15 | LOAD 8 = 0.01 | No | 0.0021422370982533434 |

| LOAD 9 = 0.01 | ||||

| LOAD 10 = 0.01 | ||||

| LOAD 11 = 0.01 | ||||

| LOAD 12 = 0.01 | ||||

| LOAD 13 = 0.01 | ||||

| Total = 0.45 | Total = 0.06 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Livanos, N.-A.I.; Hammal, S.; Giamarelos, N.; Alifragkis, V.; Psomopoulos, C.S.; Zois, E.N. OpenEdgePMU: An Open PMU Architecture with Edge Processing for Future Resilient Smart Grids. Energies 2023, 16, 2756. https://doi.org/10.3390/en16062756

Livanos N-AI, Hammal S, Giamarelos N, Alifragkis V, Psomopoulos CS, Zois EN. OpenEdgePMU: An Open PMU Architecture with Edge Processing for Future Resilient Smart Grids. Energies. 2023; 16(6):2756. https://doi.org/10.3390/en16062756

Chicago/Turabian StyleLivanos, Nikolaos-Antonios I., Sami Hammal, Nikolaos Giamarelos, Vagelis Alifragkis, Constantinos S. Psomopoulos, and Elias N. Zois. 2023. "OpenEdgePMU: An Open PMU Architecture with Edge Processing for Future Resilient Smart Grids" Energies 16, no. 6: 2756. https://doi.org/10.3390/en16062756

APA StyleLivanos, N.-A. I., Hammal, S., Giamarelos, N., Alifragkis, V., Psomopoulos, C. S., & Zois, E. N. (2023). OpenEdgePMU: An Open PMU Architecture with Edge Processing for Future Resilient Smart Grids. Energies, 16(6), 2756. https://doi.org/10.3390/en16062756