NPC Seven-Level Single-Phase Inverter with DC-Link Voltage Balancing, Input Voltage Boosting, and AC Power Decoupling

Abstract

:1. Introduction

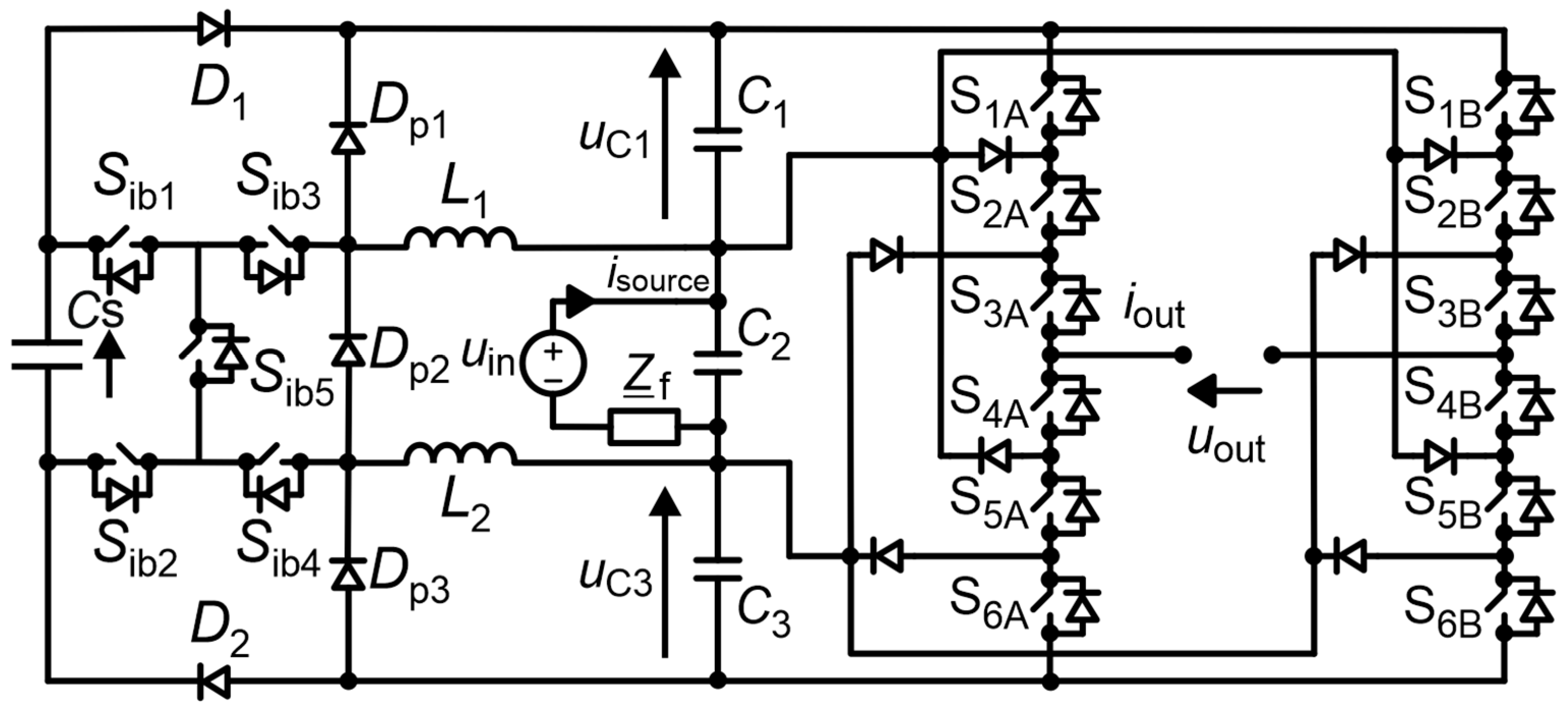

2. Concept of Operation of the System

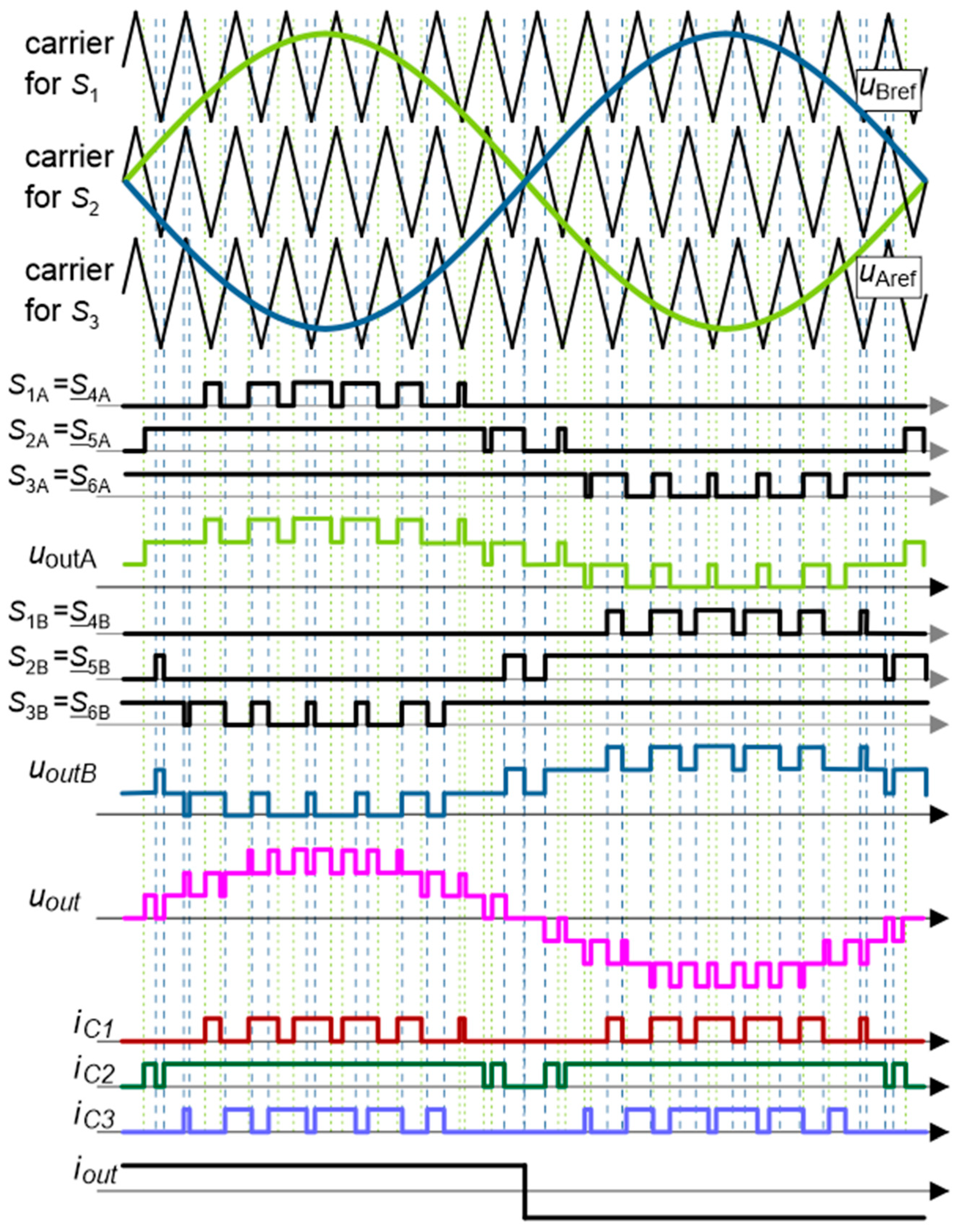

2.1. Modulation of the Inverter

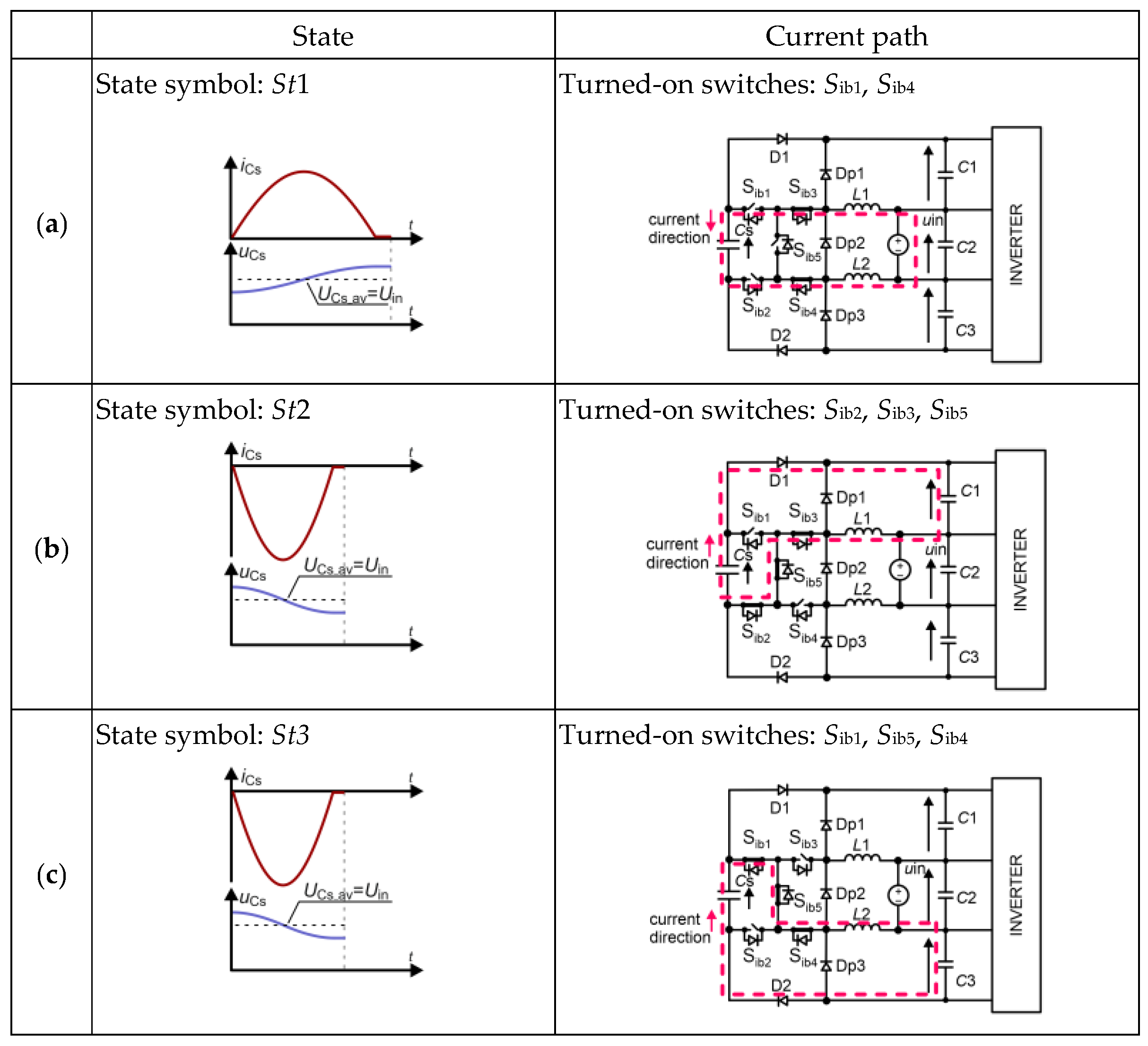

2.2. Realization of AIVB Control Concept

2.2.1. Reduction of the AC Component in the Source Voltage at the Double Frequency of the Output Voltage

2.2.2. Selection of Components

3. Simulation Results

3.1. Power of DC-Link Capacitors in Seven-Level HB Inverter

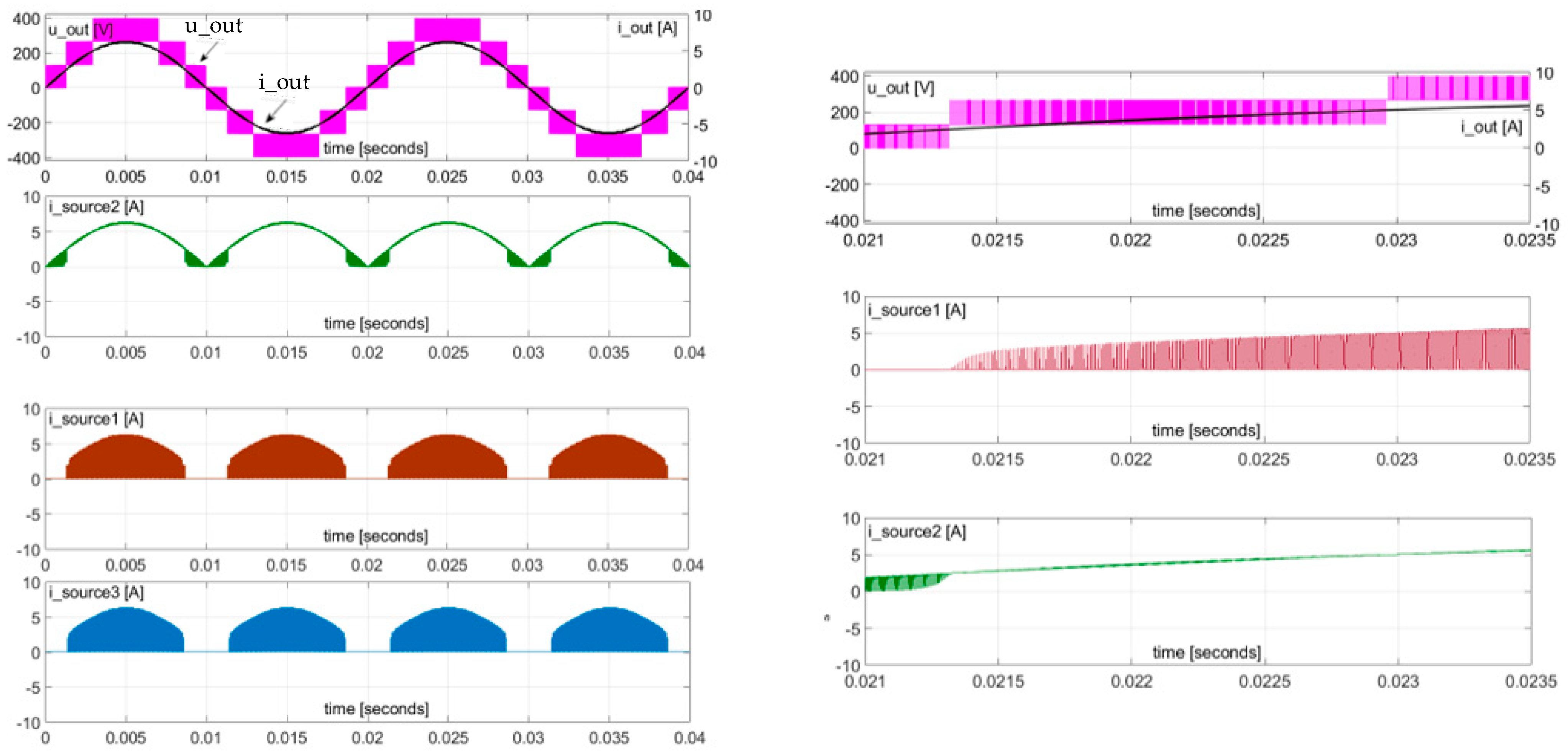

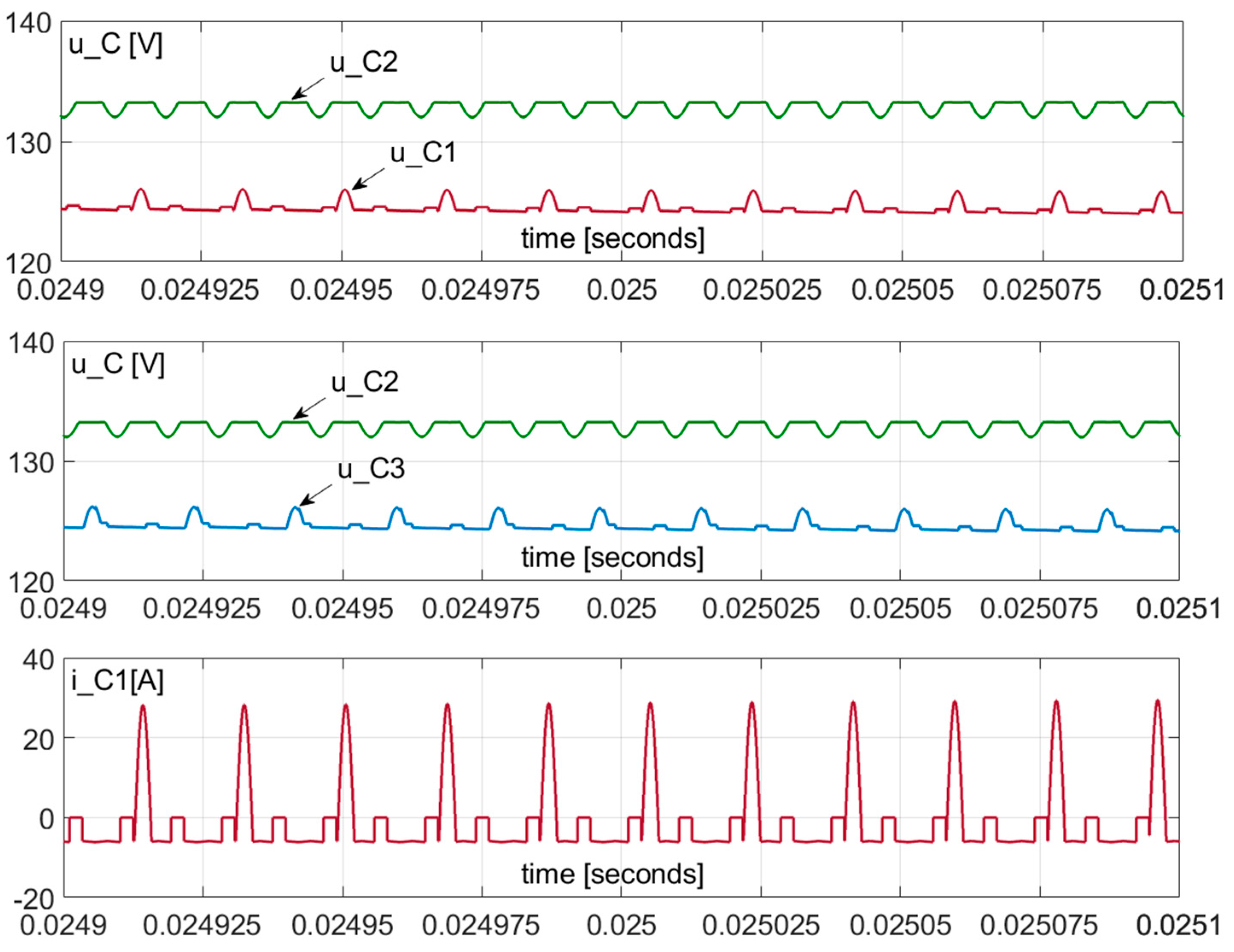

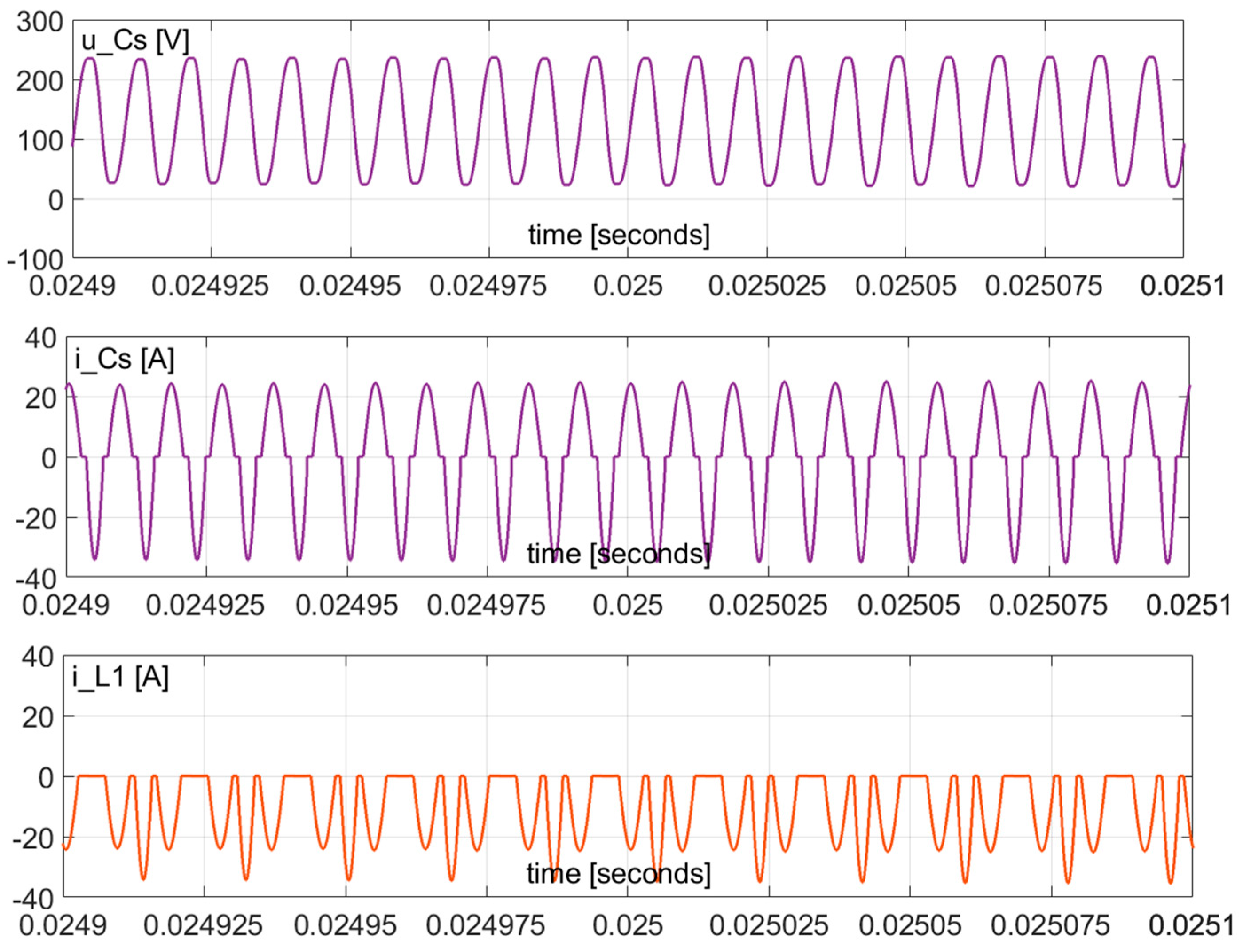

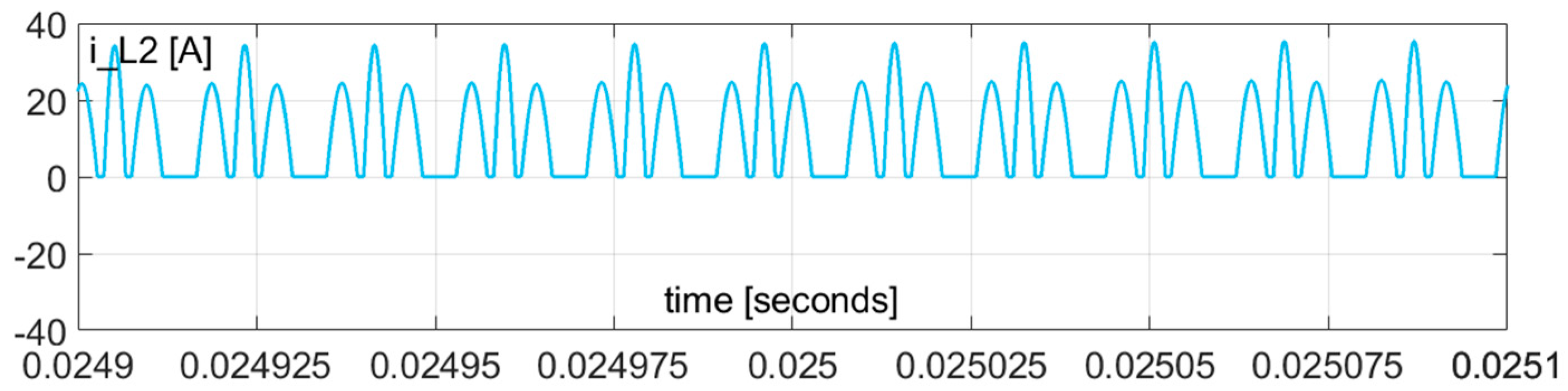

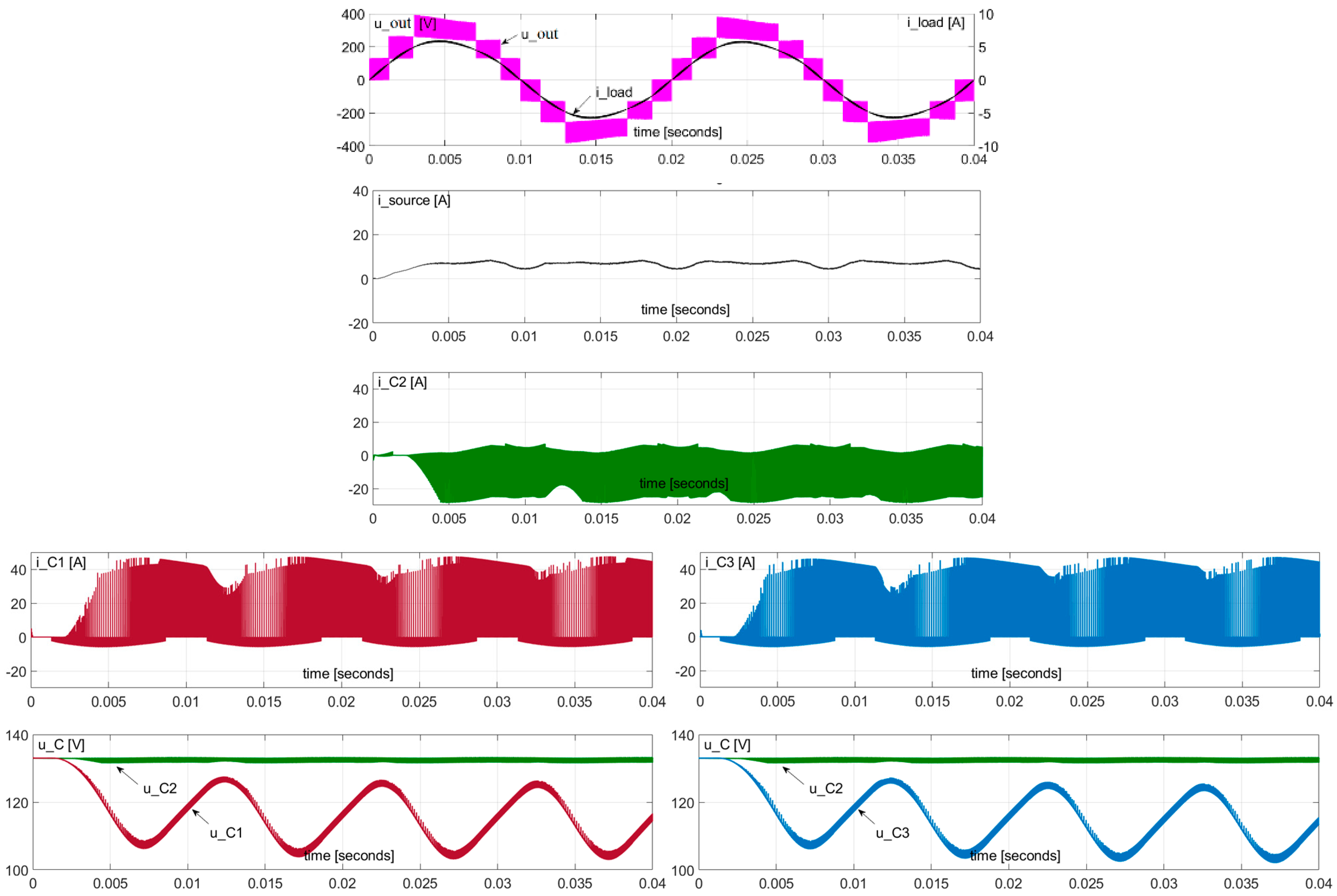

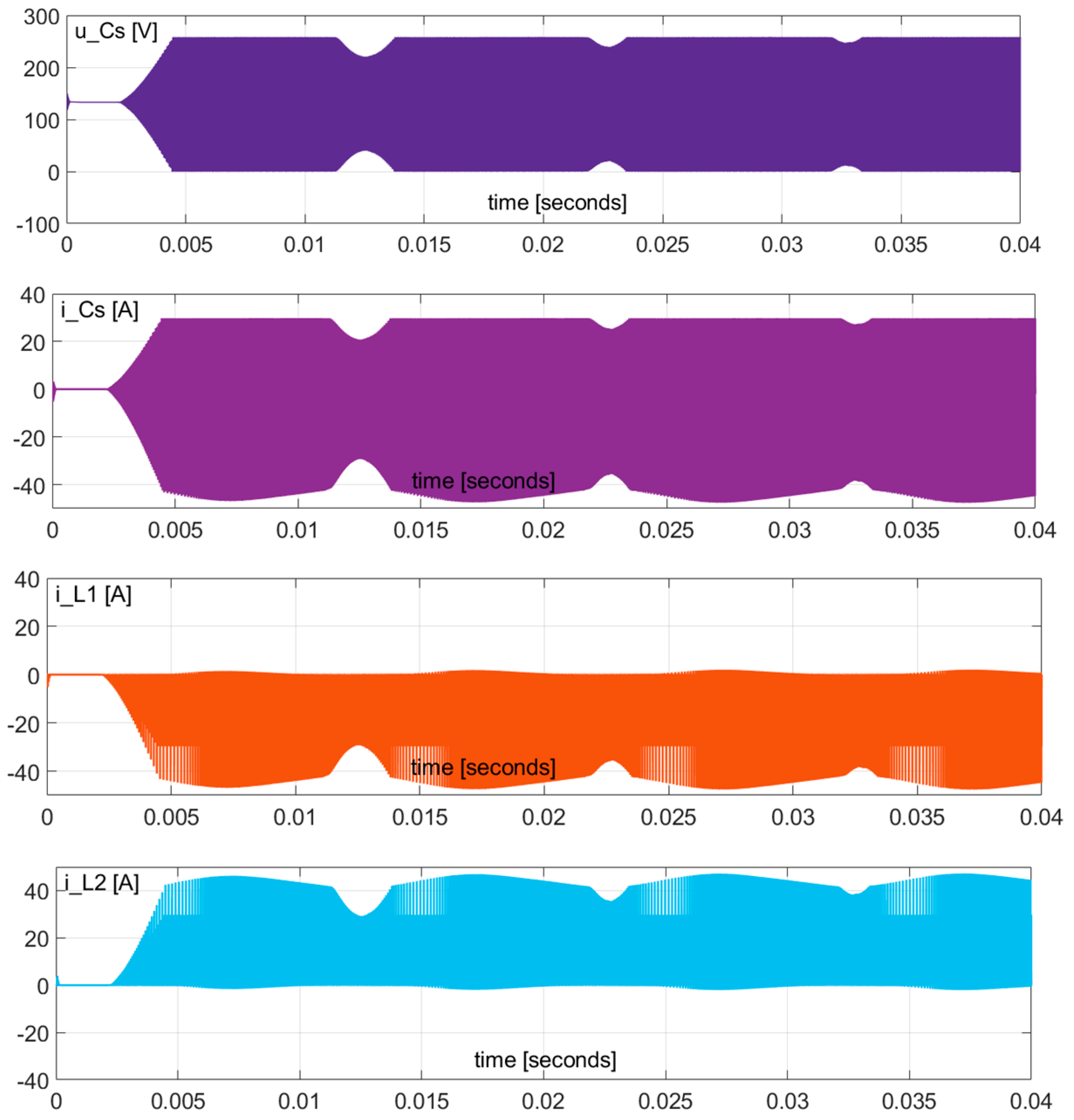

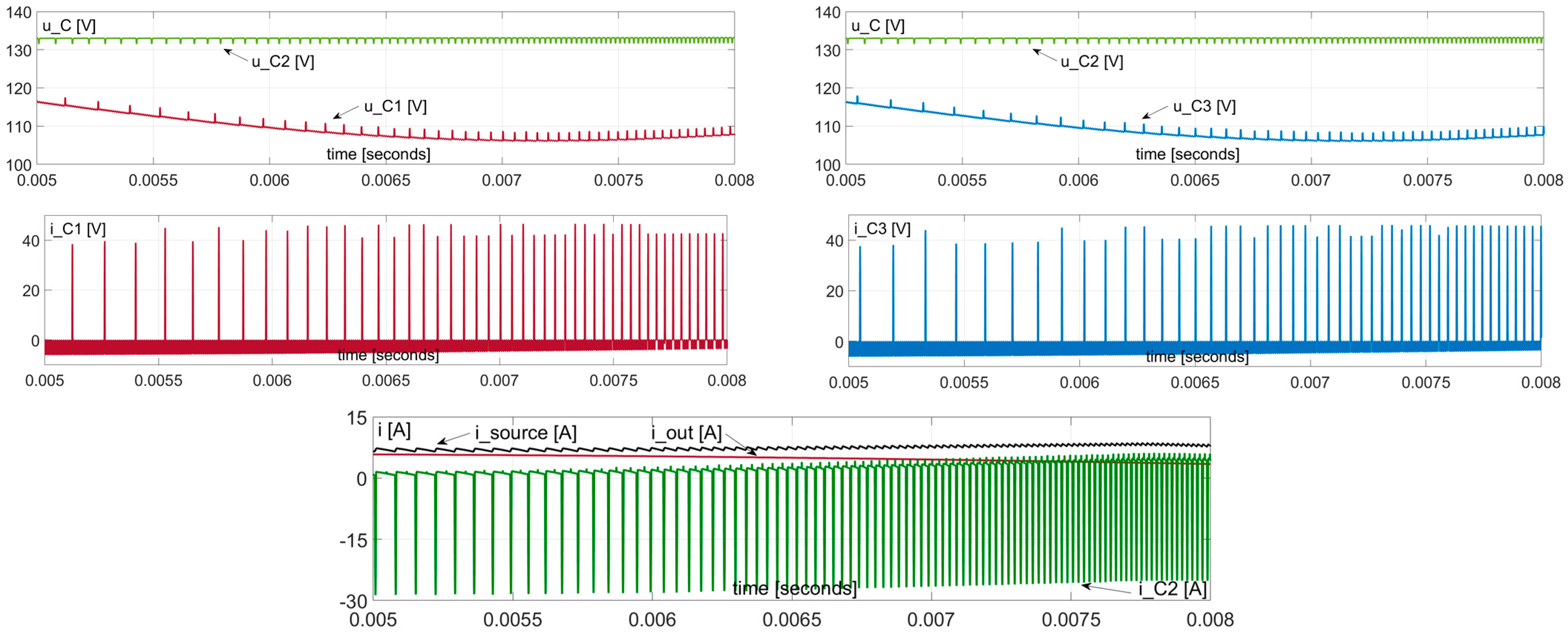

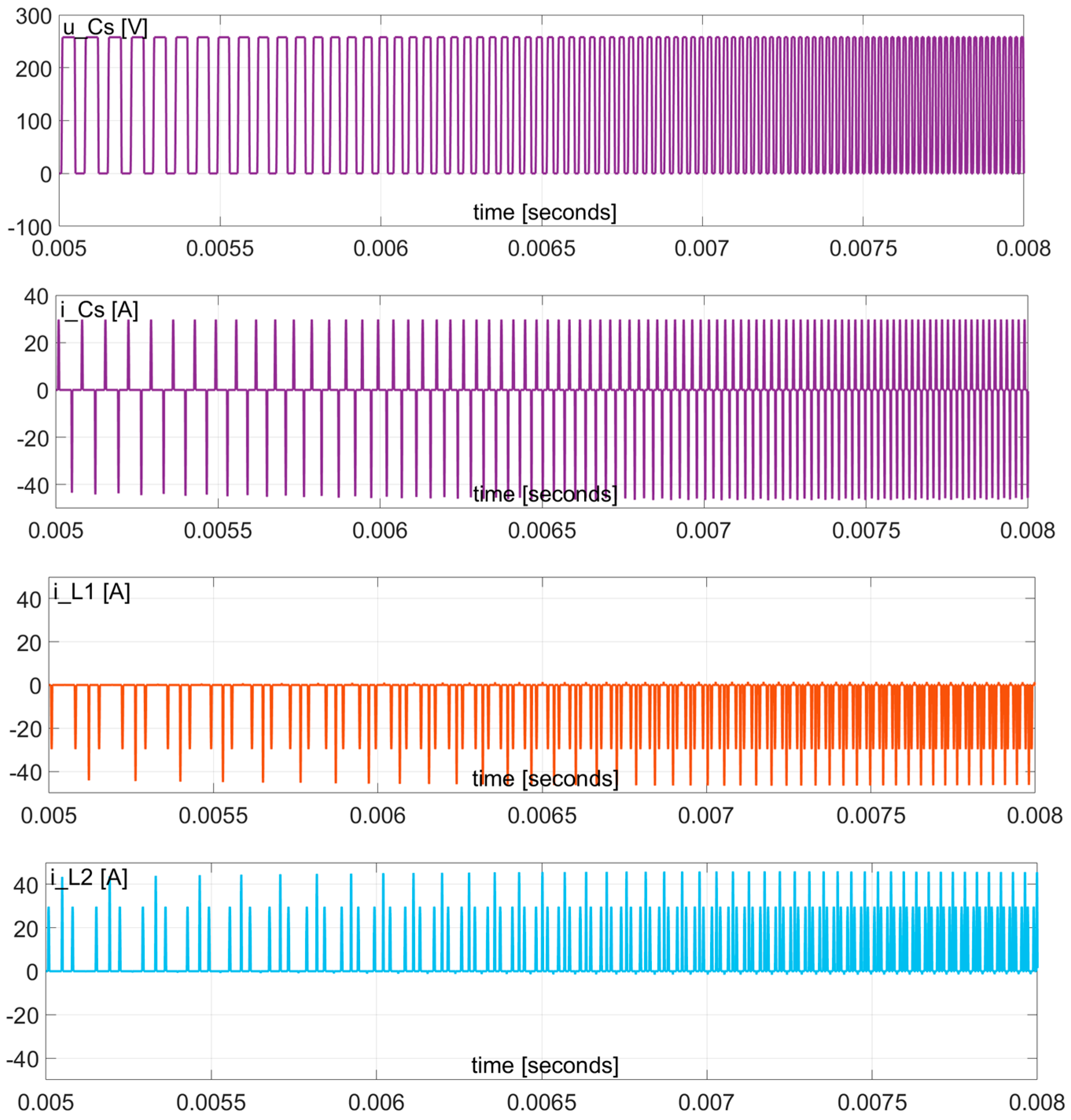

3.2. The Converter with the AIVB Operating in the Continuous Mode with Fixed Frequency

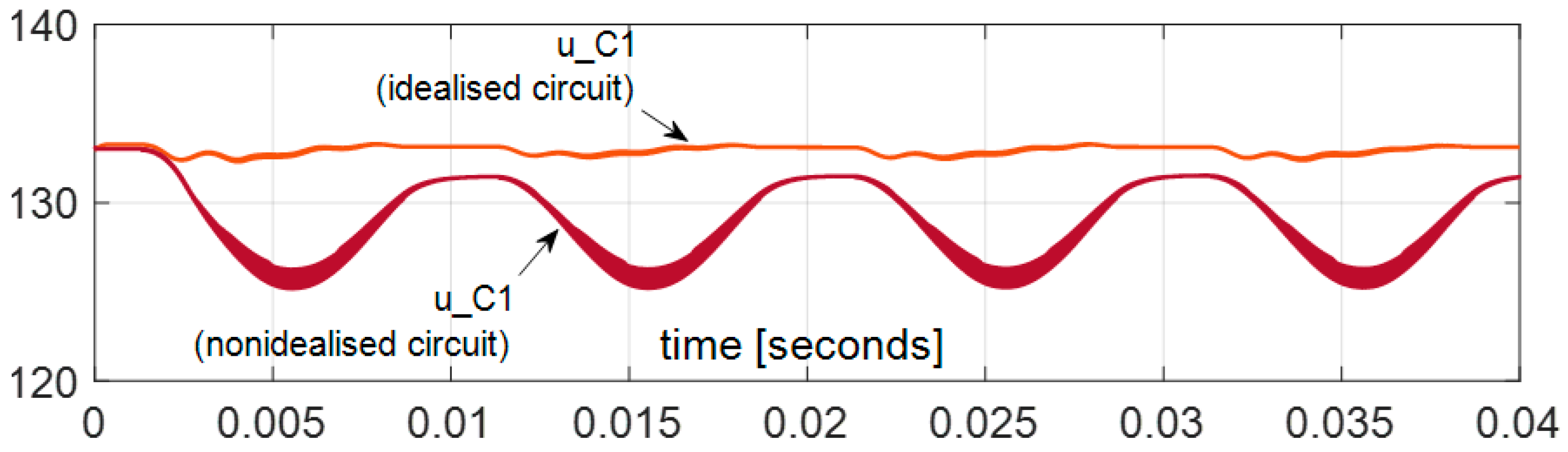

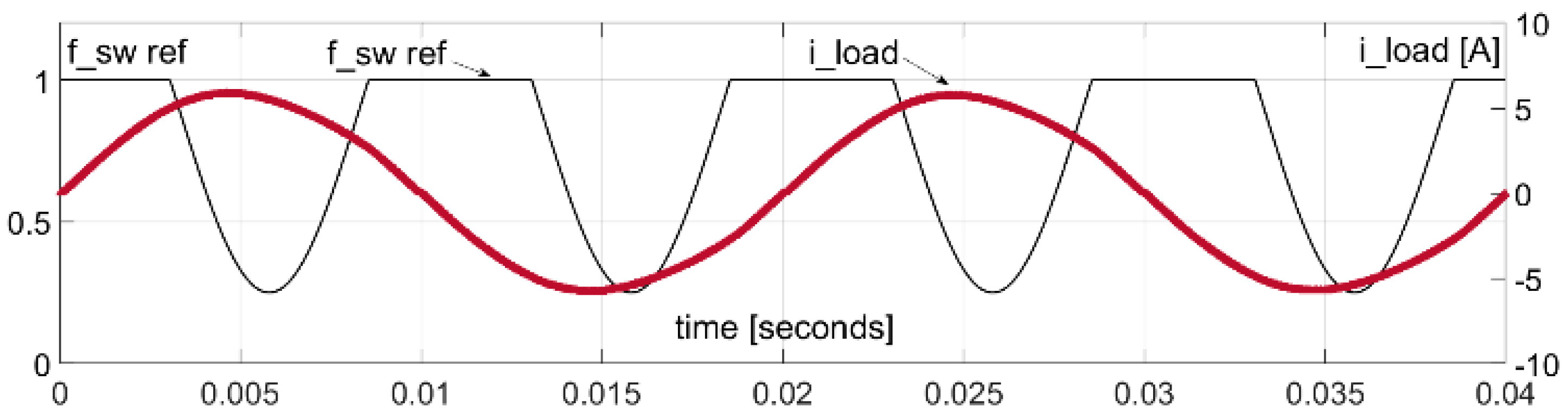

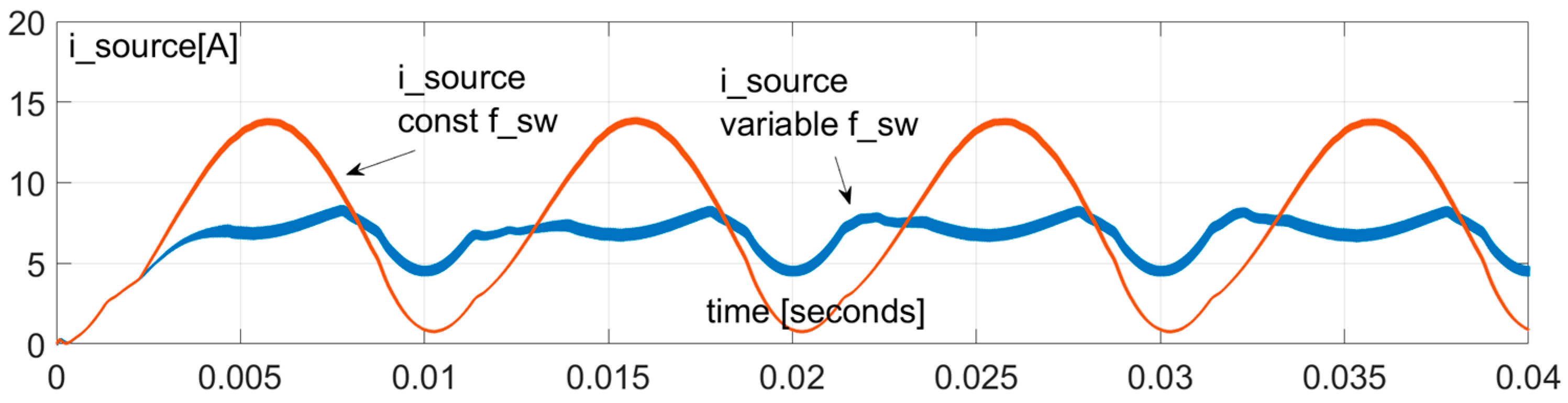

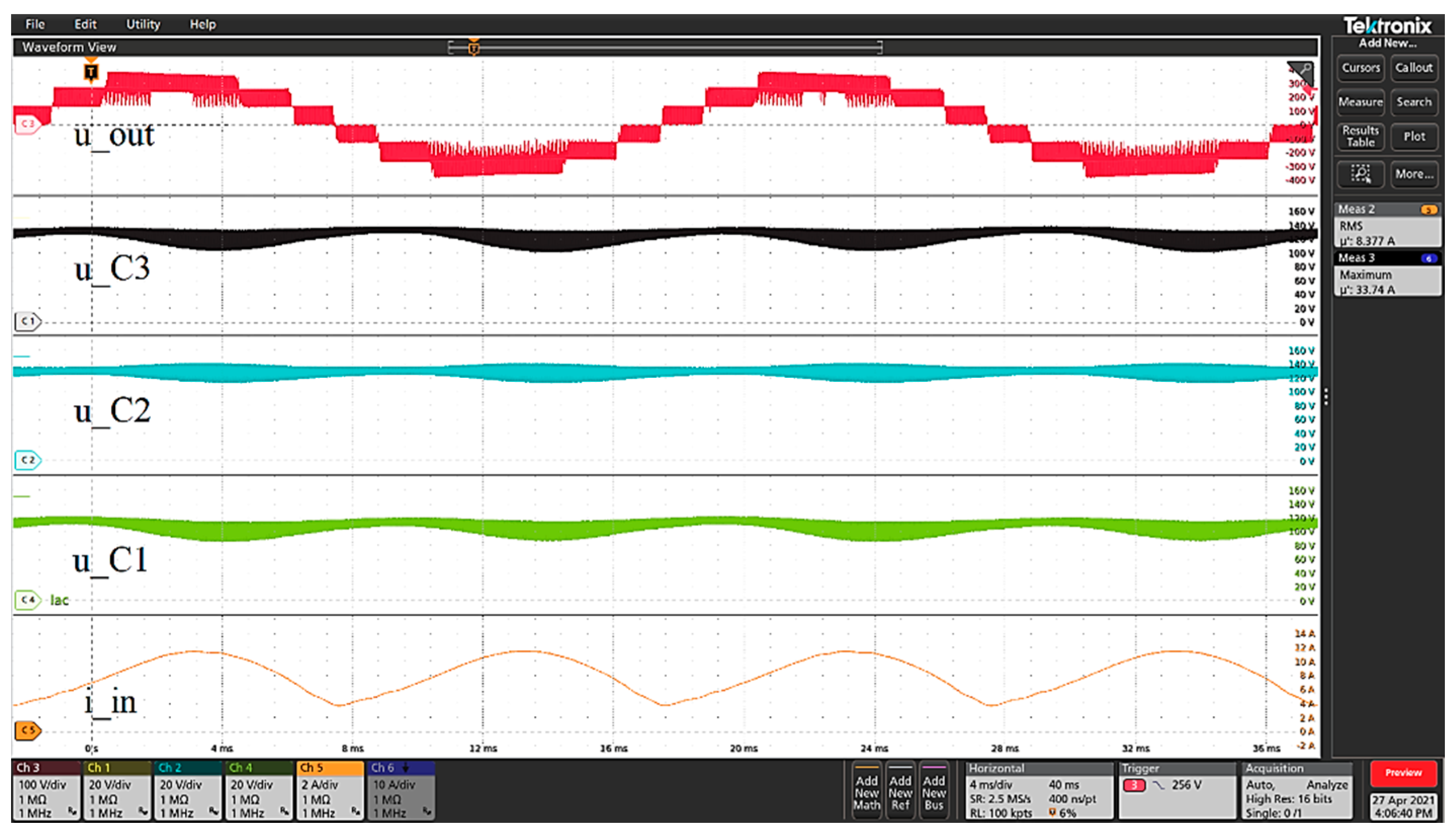

3.3. Double Frequency Reduction in the Source Current by Control of the AIVB Power

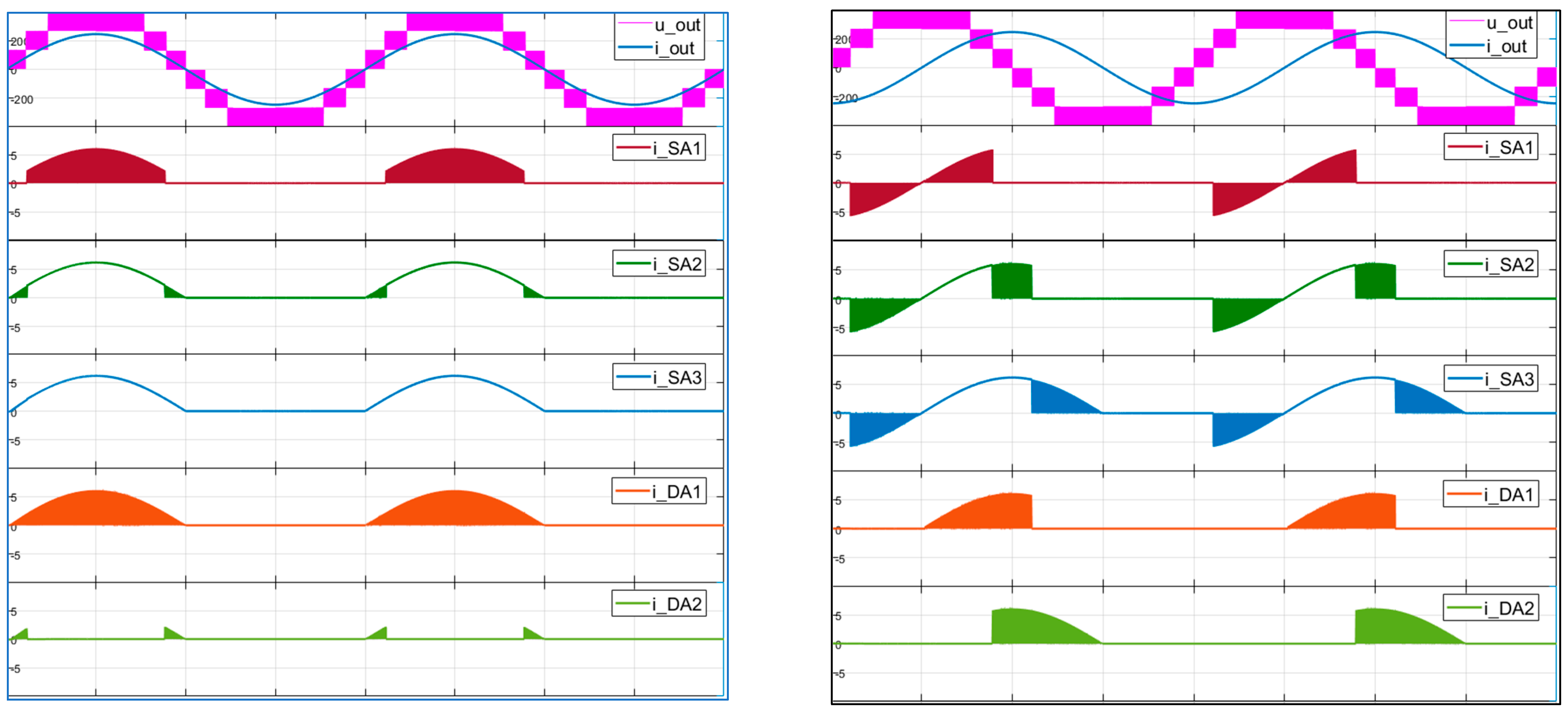

3.4. Switch Load by Currents of Converters and Conduction lLosses

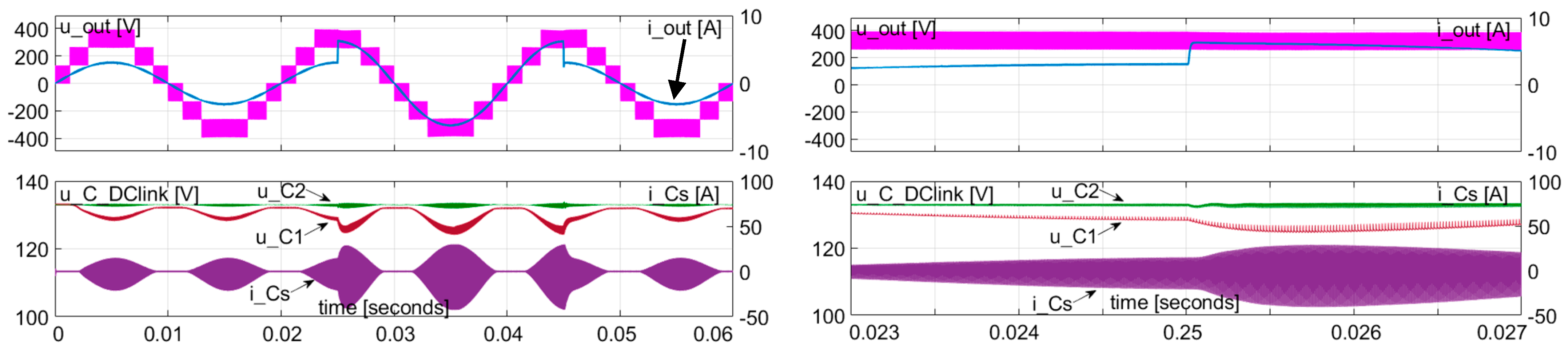

3.5. Step Change of Load

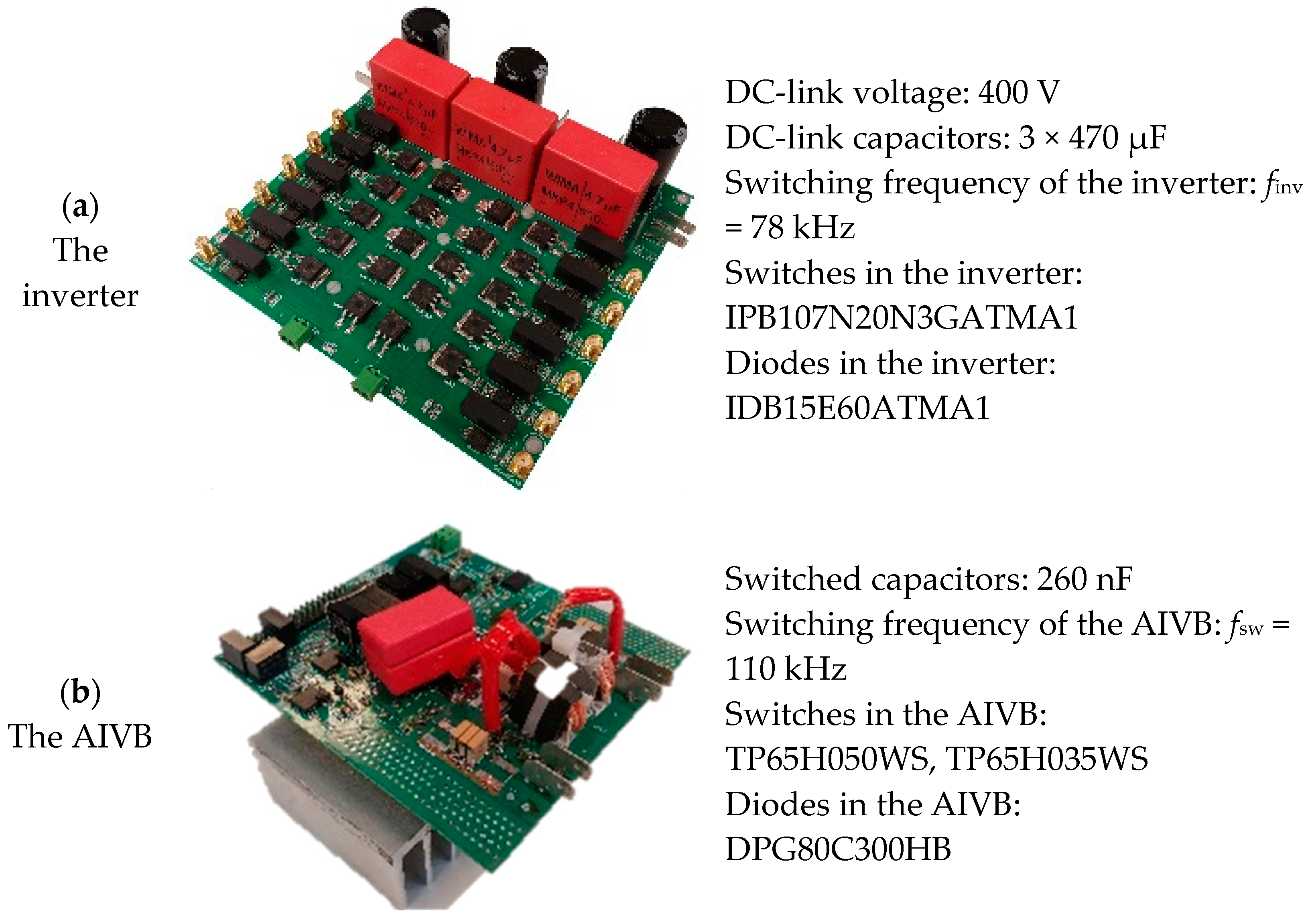

4. Experimental Results

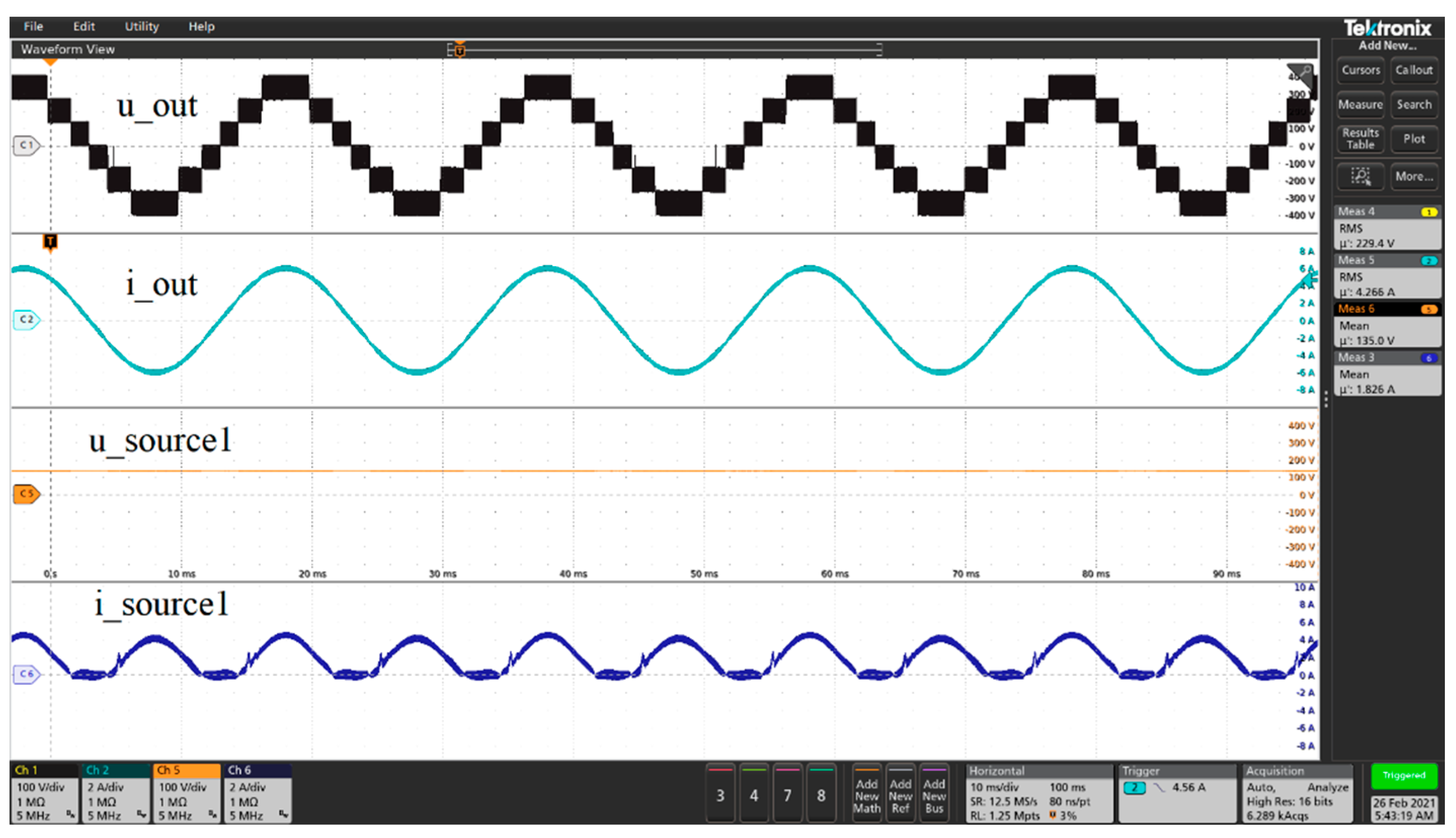

4.1. Operation of the Inverter with the PD-PWM Method and Three DC Sources

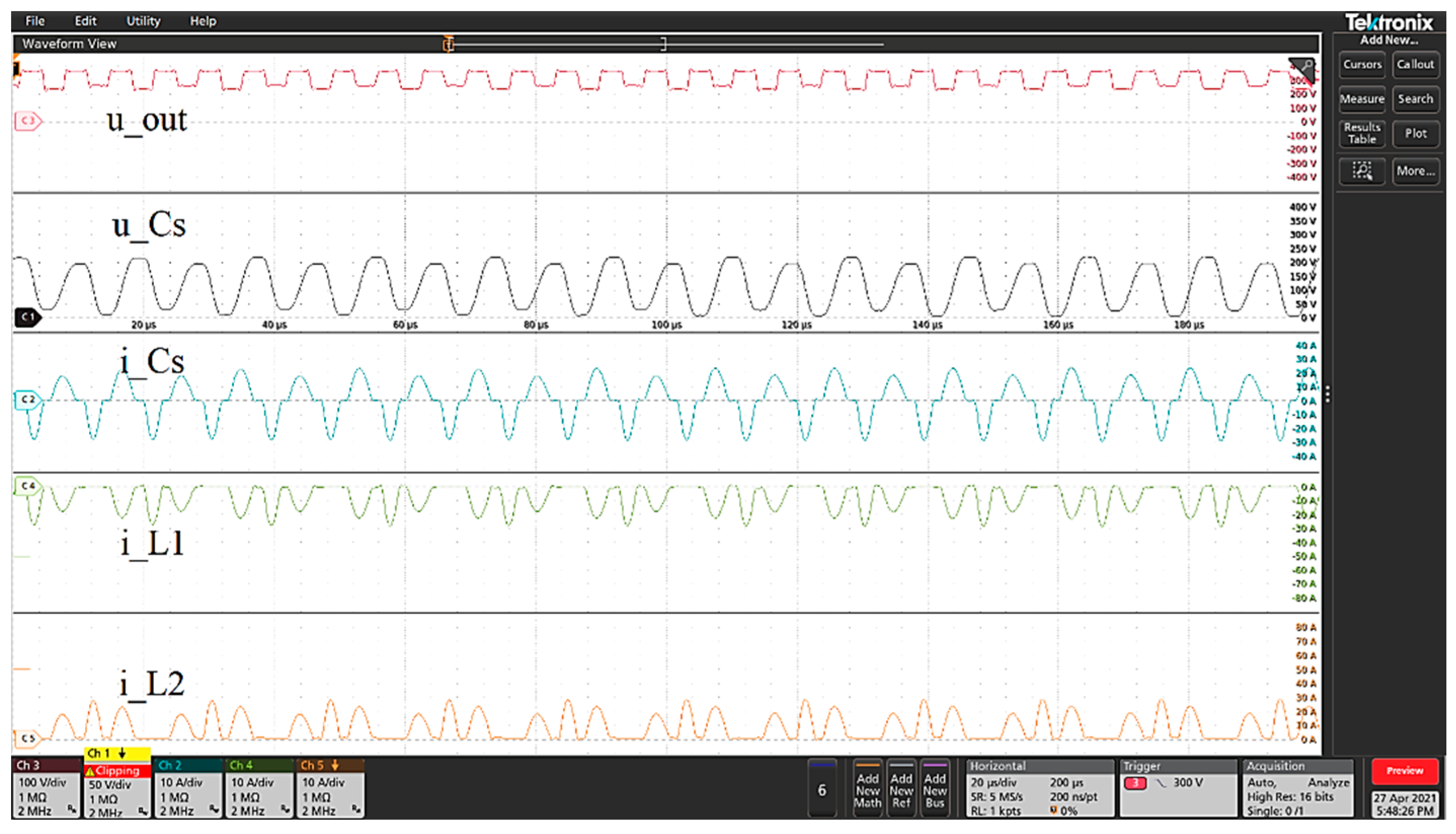

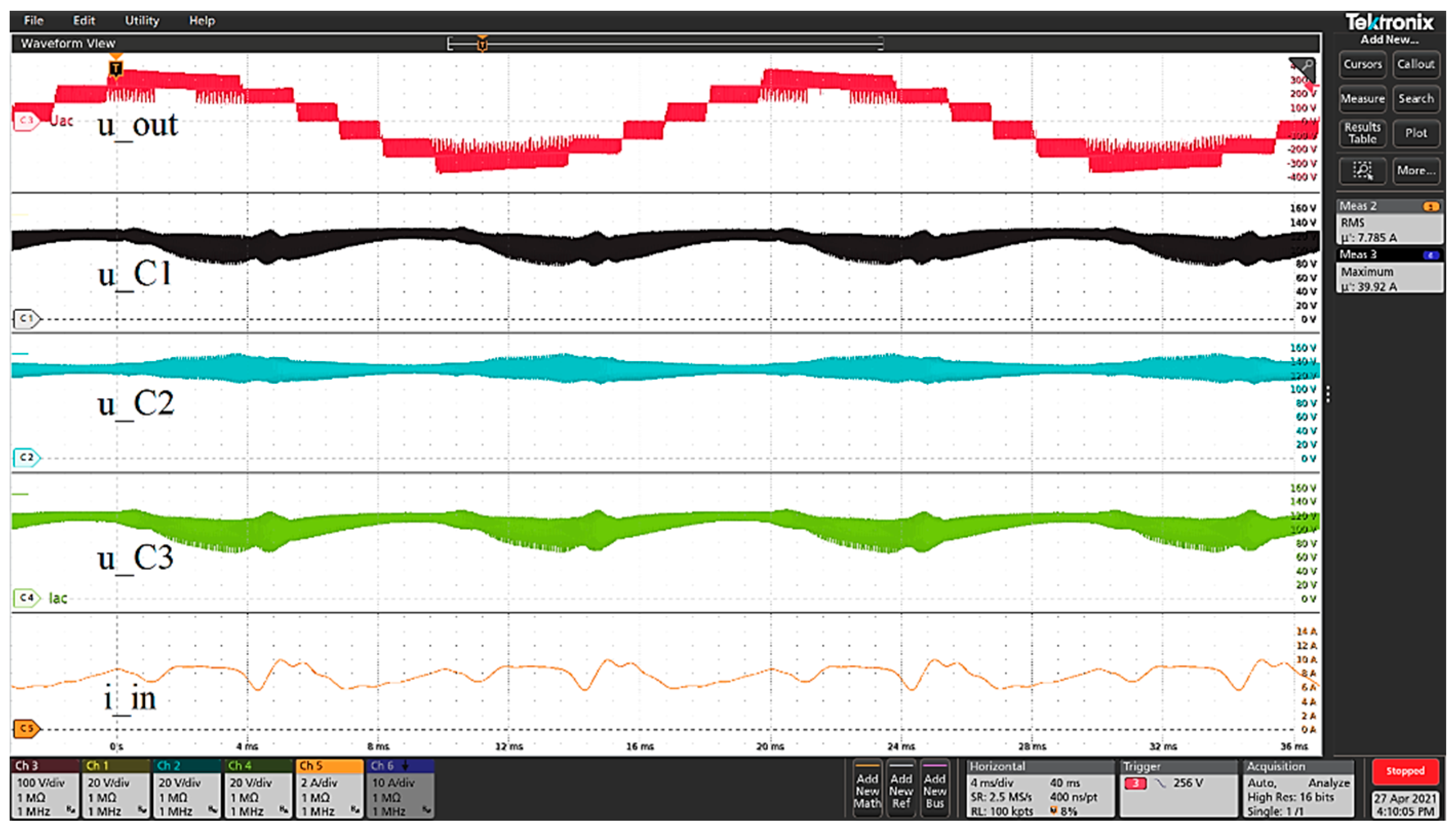

4.2. Operation of the AIVB

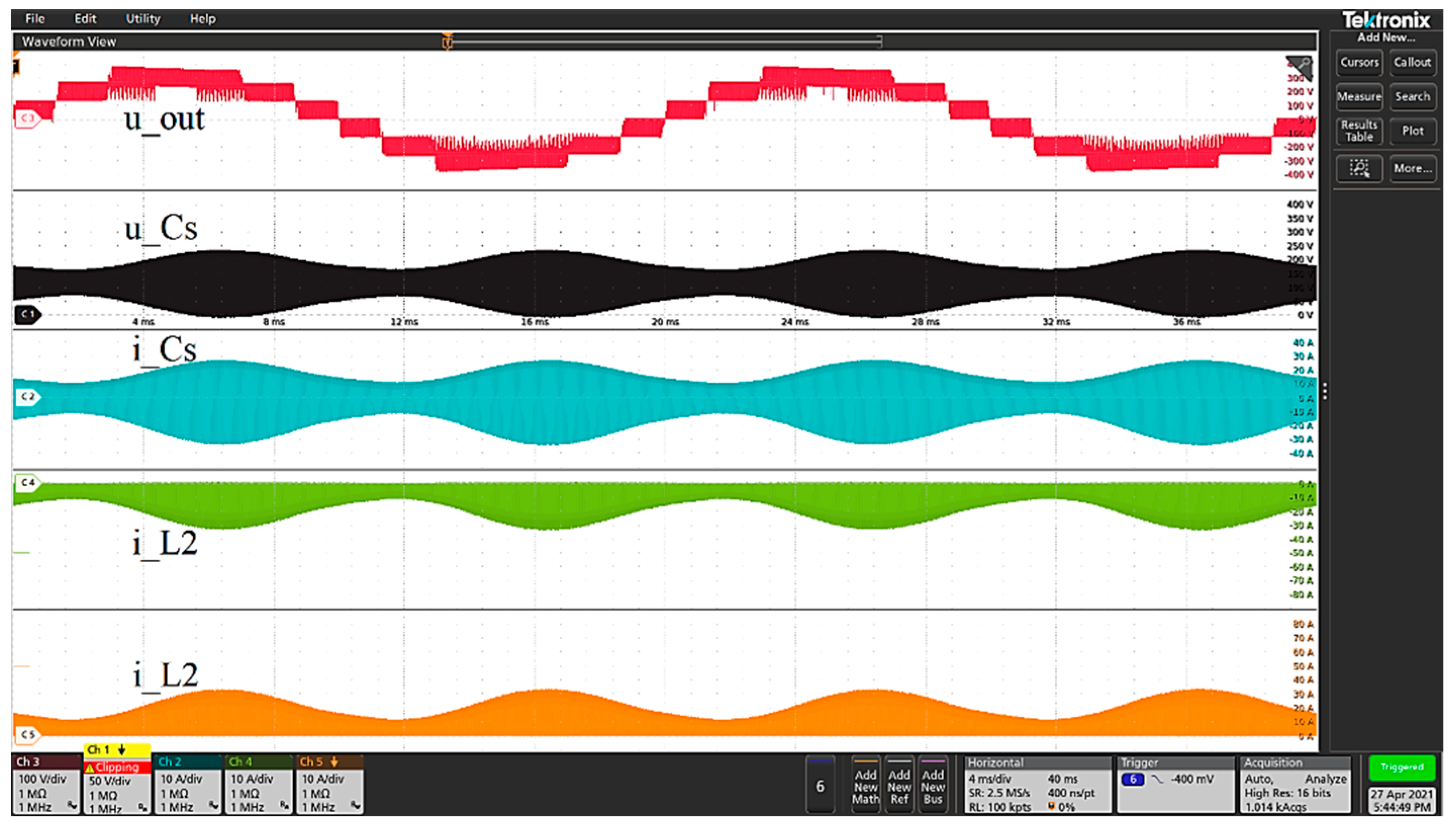

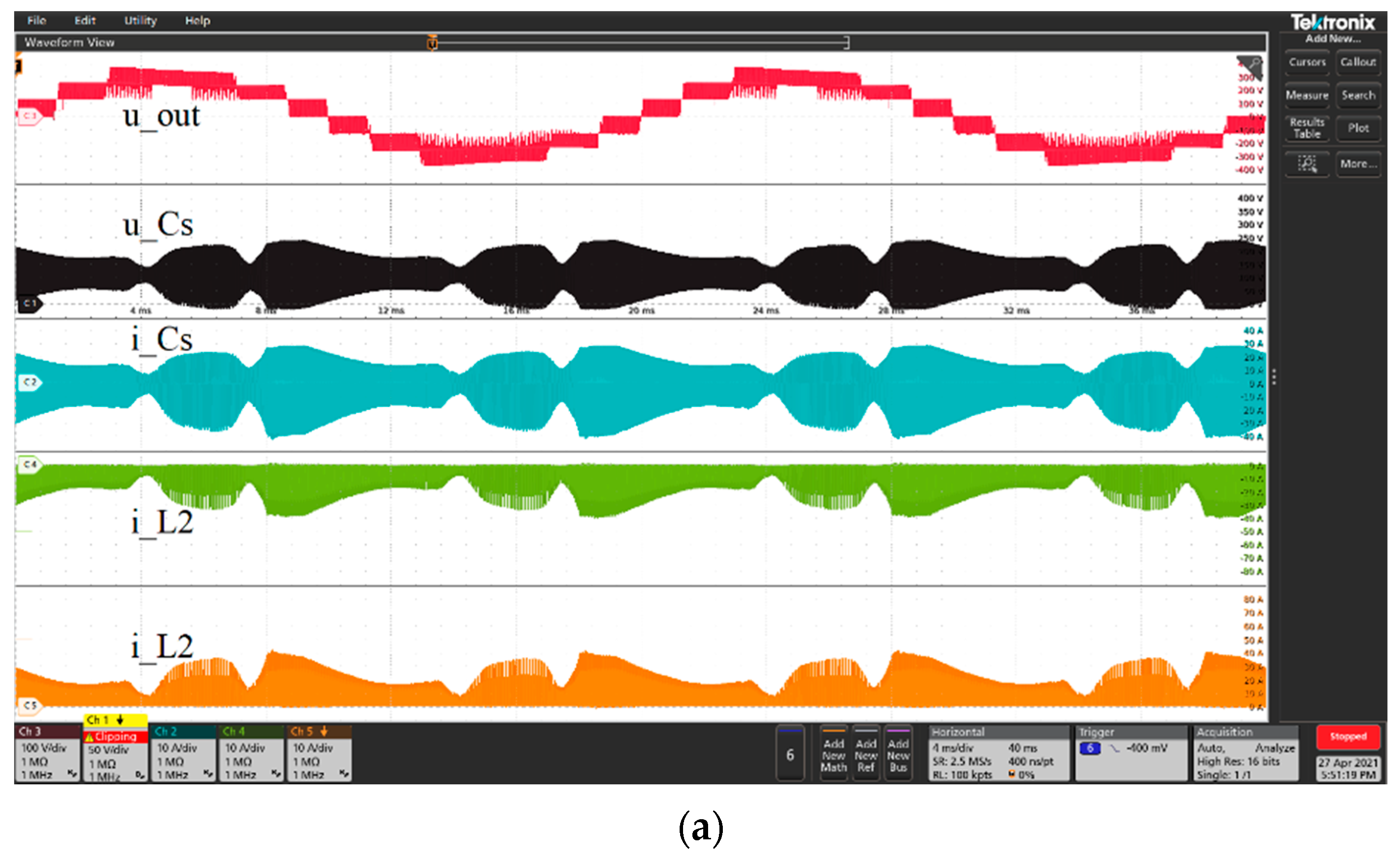

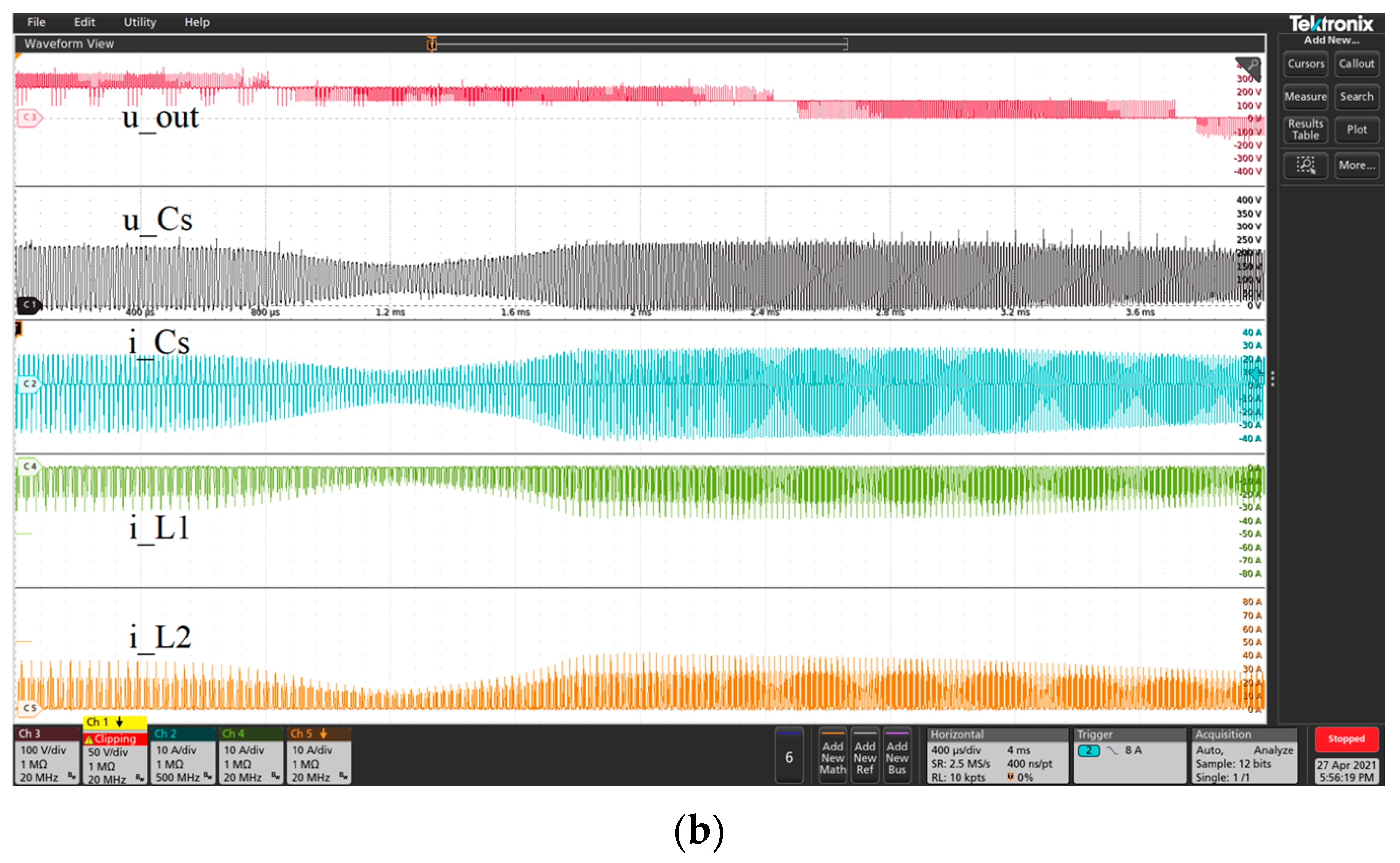

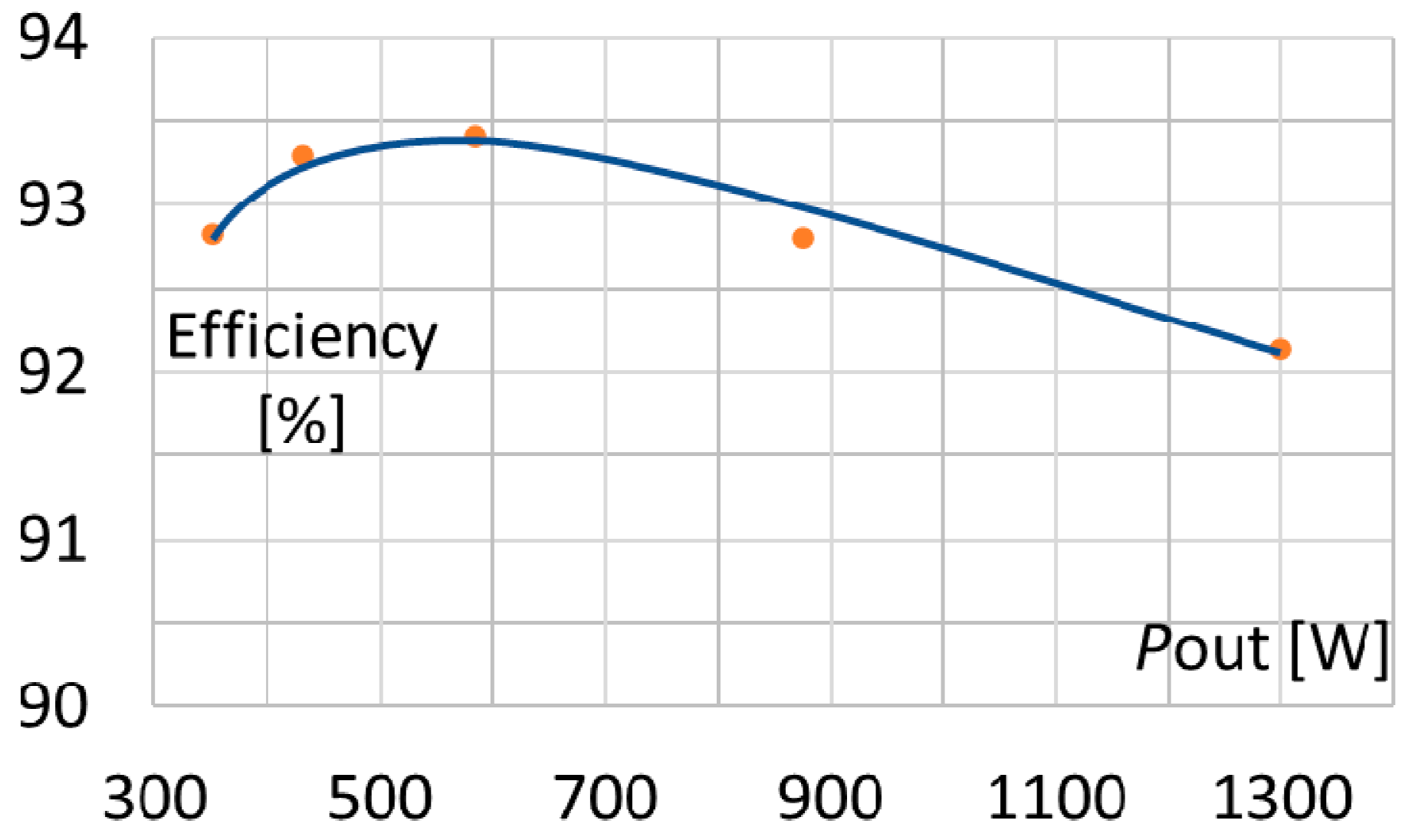

4.3. Operation of the Inverter with the AIVB Converter

5. Comparison to Existing Solutions

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Rodriguez, J.; Bernet, S.; Steimer, P.K.; Lizama, I.E. A Survey on Neutral-Point-Clamped Inverters. IEEE Trans. Ind. Electron. 2010, 57, 2219–2230. [Google Scholar] [CrossRef]

- Nabae, A.; Takahashi, I.; Akagi, H. A New Neutral-Point-Clamped PWM Inverter. IEEE Trans. Ind. Appl. 1981, IA-17, 518–523. [Google Scholar] [CrossRef]

- Zhang, L.; Sun, K.; Feng, L.; Wu, H.; Xing, Y. A Family of Neutral Point Clamped Full-Bridge Topologies for Transformerless Photovoltaic Grid-Tied Inverters. IEEE Trans. Power Electron. 2013, 28, 730–739. [Google Scholar] [CrossRef]

- Trabelsi, M.; Vahedi, H.; Abu-Rub, H. Review on Single-DC-Source Multilevel Inverters: Topologies, Challenges, Industrial Applications, and Recommendations. IEEE Open J. Ind. Electron. Soc. 2021, 2, 112–127. [Google Scholar] [CrossRef]

- Khan, M.N.H.; Forouzesh, M.; Siwakoti, Y.P.; Li, L.; Kerekes, T.; Blaabjerg, F. Transformerless Inverter Topologies for Single-Phase Photovoltaic Systems: A Comparative Review. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 805–835. [Google Scholar] [CrossRef]

- Salem, A.; Van Khang, H.; Robbersmyr, K.G.; Norambuena, M.; Rodriguez, J. Voltage Source Multilevel Inverters with Reduced Device Count: Topological Review and Novel Comparative Factors. IEEE Trans. Power Electron. 2021, 36, 2720–2747. [Google Scholar] [CrossRef]

- Zhang, Z.; Zhang, J.; Shao, S.; Zhang, J. A High-Efficiency Single-Phase T-Type BCM Microinverter. IEEE Trans. Power Electron. 2019, 34, 984–995. [Google Scholar] [CrossRef]

- Khazraei, M.; Zupancic, D. Solar Inverter Design. The Race to Design High-Efficiency, High-Power-Density Inverters. Power Syst. Des. 2020, 5, 9–12. [Google Scholar]

- Stala, R. Natural DC-link voltage balance in a single-phase NPC inverter with four-level legs and novel modulation method. IET Power Electron. 2020, 13, 3764–3776. [Google Scholar] [CrossRef]

- Strzelecki, R.; Szczepankowski, P.; Strzelecka, N. Four level diode-clamped back-to-back converter with active DC link voltage control. In Proceedings of the 2013 International Conference-Workshop Compatibility and Power Electronics, Ljubljana, Slovenia, 5–7 June 2013; pp. 182–187. [Google Scholar] [CrossRef]

- Shukla, A.; Ghosh, A.; Joshi, A. Flying-Capacitor-Based Chopper Circuit for DC Capacitor Voltage Balancing in Diode-Clamped Multilevel Inverter. IEEE Trans. Ind. Electron. 2010, 57, 2249–2261. [Google Scholar] [CrossRef] [Green Version]

- Cui, D.; Ge, Q. A Novel Hybrid Voltage Balance Method for Five-Level Diode-Clamped Converters. IEEE Trans. Ind. Electron. 2018, 65, 6020–6031. [Google Scholar] [CrossRef]

- Zhao, J.; Han, Y.; He, X.; Tan, C.; Cheng, J.; Zhao, R. Multilevel Circuit Topologies Based on the Switched-Capacitor Converter and Diode-Clamped Converter. IEEE Trans. Power Electron. 2011, 26, 2127–2136. [Google Scholar] [CrossRef]

- Shu, Z.; He, X.; Wang, Z.; Qiu, D.; Jing, Y. Voltage Balancing Approaches for Diode-Clamped Multilevel Converters Using Auxiliary Capacitor-Based Circuits. IEEE Trans. Power Electron. 2013, 28, 2111–2124. [Google Scholar] [CrossRef]

- Hachlowski, J.; Stala, R. DC-link Voltage Balancing Converter with Resonant Switched-Capacitor Circuit for Four-Level and Six-Level NPC Inverter. In Proceedings of the 2019 21st European Conference on Power Electronics and Applications (EPE 19 ECCE Europe), Genova, Italy, 3–5 September 2019. [Google Scholar] [CrossRef]

- Hachlowski, J.; Stala, R. A Novel Converter for Voltage Balance in A Series Connected Capacitors And Batteries. Power Electron. Drives 2018, 3, 65–74. [Google Scholar] [CrossRef] [Green Version]

- Taghvaie, A.; Haque, M.E.; Saha, S.; Mahmud, M.A. A New Step-Up Switched-Capacitor Voltage Balancing Converter for NPC Multilevel Inverter-Based Solar PV System. IEEE Access 2020, 8, 83940–83952. [Google Scholar] [CrossRef]

- Shimizu, T.; Koizumi, H. Modularized chain structure of switched capacitor for cell voltage equalizer with T-connected bi-directional switch. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016; pp. 1194–1197. [Google Scholar] [CrossRef]

- Liu, K.; Yang, Z.; Tang, X.; Cao, W. Automotive Battery Equalizers Based on Joint Switched-Capacitor and Buck-Boost Converters. IEEE Trans. Veh. Technol. 2020, 69, 12716–12724. [Google Scholar] [CrossRef]

- Pereda, J.; Dixon, J. High-Frequency Link: A Solution for Using Only One DC Source in Asymmetric Cascaded Multilevel Inverters. IEEE Trans. Ind. Electron. 2011, 58, 3884–3892. [Google Scholar] [CrossRef]

- Singh, J.; Dahiya, R.; Lalit Mohan, S. Recent research on transformer based single DC source multilevel inverter: A review. Renew. Sustain. Energy Rev. 2018, 82, 3207–3224. [Google Scholar] [CrossRef]

- Sun, X.; Wang, B.; Zhou, Y.; Wang, W.; Du, H.; Lu, Z. A Single DC Source Cascaded Seven-Level Inverter Integrating Switched-Capacitor Techniques. IEEE Trans. Ind. Electron. 2016, 63, 7184–7194. [Google Scholar] [CrossRef]

- Gautam, A.R.; Fulwani, D.M.; Makineni, R.R.; Rathore, A.K.; Singh, D. Control Strategies and Power Decoupling Topologies to Mitigate 2ω-Ripple in Single-Phase Inverters: A Review and Open Challenges. IEEE Access 2020, 8, 147533–147559. [Google Scholar] [CrossRef]

- Zhang, Y.; Xiong, J.; He, P.; Wang, S. Review of power decoupling methods for micro-inverters used in PV systems. Chin. J. Electr. Eng. 2018, 4, 26–32. [Google Scholar] [CrossRef]

- Vitorino, M.A.; Alves, L.F.S.; Wang, R.; de Rossiter Corrêa, M.B. Low-Frequency Power Decoupling in Single-Phase Applications: A Comprehensive Overview. IEEE Trans. Power Electron. 2017, 32, 2892–2912. [Google Scholar] [CrossRef]

- He, L.; Cheng, C. A Bridge Modular Switched-Capacitor-Based Multilevel Inverter with Optimized SPWM Control Method and Enhanced Power-Decoupling Ability. IEEE Trans. Ind. Electron. 2018, 65, 6140–6149. [Google Scholar] [CrossRef]

- Omomo, A.; Itoh, J.; Kusaka, K.; Takaoka, N.; Le, H.N. T-type NPC Inverter with Active Power Decoupling Method using Discontinuous Current Mode for Micro-Inverter. In Proceedings of the 2018 7th International Conference on Renewable Energy Research and Appl. (ICRERA), Paris, France, 14–17 October 2018; pp. 1147–1152. [Google Scholar] [CrossRef]

- Kumari, M.; Siddique, M.D.; Sarwar, A.; Tariq, M.; Mekhilef, S.; Iqbal, A. Recent trends and review on switched-capacitor-based single-stage boost multilevel inverter. Int. Trans. Elec. Energy Syst. 2021, 31, e12730. [Google Scholar] [CrossRef]

- Siddique, M.D.; Mekhilef, S.; Shah, N.M.; Ali, J.S.M.; Blaabjerg, F. A New Switched Capacitor 7L Inverter With Triple Voltage Gain and Low Voltage Stress. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 1294–1298. [Google Scholar] [CrossRef]

- Sathik, M.J.; Sandeep, N.; Siddique, M.D.; Almakhles, D.; Mekhilef, S. Compact Seven-Level Boost Type Inverter Topology. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 1358–1362. [Google Scholar] [CrossRef]

- Zeng, J.; Lin, W.; Liu, J. Switched-Capacitor-Based Active-Neutral-Point-Clamped Seven-Level Inverter with Natural Balance and Boost Ability. IEEE Access 2019, 7, 126889–126896. [Google Scholar] [CrossRef]

- Lee, S.S.; Lee, K. Dual-T-Type Seven-Level Boost Active-Neutral-Point-Clamped Inverter. IEEE Trans. Power Electron. 2019, 34, 6031–6035. [Google Scholar] [CrossRef]

| Parameter | Uin [V] | Uload [V] | Pload [kW] | UDC [V] | fsw [kHz] | C1,2,3 in DC Link [μF] | Cs [nF] | L1, L2 [uH] |

|---|---|---|---|---|---|---|---|---|

| Value | 133 | 230 | 1 | 400 | 110 | 500 | 320 | 3 |

| State | D1 | D2 | Sib1 | Sib2 | Sib3 | Sib4 | Sib5 |

|---|---|---|---|---|---|---|---|

| St1 (used 2 times) in a period | - | - | A | A | A | A | - |

| St2 | A | - | - | A | A | - | A |

| St3 | - | A | A | - | - | A | A |

| Number of active subperiods | 1 | 1 | 3 | 3 | 3 | 3 | 2 |

| Number of Components and Gain | Ref. [10] | Ref. [11] | Ref. [12] | Ref. [13] | Ref. [14] | Ref. [17] | Proposed |

|---|---|---|---|---|---|---|---|

| Switches | 8 | 8/12 | 8 | 6 | 8 | 5 | 5 |

| Diodes | 4 | 0 | 0 | 0 | 0 | 2 | 2 |

| Inductors | 2 (2 or 5 mH) | 2 (20 mH) | 2 | 0 | 0 | 0 | 2 × 3 µH |

| Capacitor | 0 | 2/4 2.2 mF | 2 9.4 mF | 2 2.2 mF | 3 470 μF | 0 | 1 260 nF |

| DC-link capacitors | 3 | 4 | 4 | 3 | 4 | 3 | 3 |

| Voltage Gain Ability | 1 | 1 | 1 | 3 | 2 or 4 * | 3 | 3 |

| Parameter | Ref. [29] | Ref. [30] | Ref. [31] | Ref. [32] | Proposed |

|---|---|---|---|---|---|

| Gain | 3 | 3 | 1.5 | 1.5 | 3 |

| Switches | 12 | 8 | 9 | 10 | 17 |

| Diodes | 11 | 1 | - | - | 10 (and 3 protection diodes) |

| Voltage stress on switches | TSVp.u. = 5.3 | TSVp.u. = 6 | TSV × Vstep = 16 | 0.5 Vdc (2 switches) Vdc (6 switches) 2 Vdc (2 switches) TSVp.u. = 11/1.5 = 7.3 | TSVp.u. = 7.3 TSV × Vstep = 22 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Stala, R.; Hachlowski, J.; Penczek, A. NPC Seven-Level Single-Phase Inverter with DC-Link Voltage Balancing, Input Voltage Boosting, and AC Power Decoupling. Energies 2022, 15, 3729. https://doi.org/10.3390/en15103729

Stala R, Hachlowski J, Penczek A. NPC Seven-Level Single-Phase Inverter with DC-Link Voltage Balancing, Input Voltage Boosting, and AC Power Decoupling. Energies. 2022; 15(10):3729. https://doi.org/10.3390/en15103729

Chicago/Turabian StyleStala, Robert, Jakub Hachlowski, and Adam Penczek. 2022. "NPC Seven-Level Single-Phase Inverter with DC-Link Voltage Balancing, Input Voltage Boosting, and AC Power Decoupling" Energies 15, no. 10: 3729. https://doi.org/10.3390/en15103729

APA StyleStala, R., Hachlowski, J., & Penczek, A. (2022). NPC Seven-Level Single-Phase Inverter with DC-Link Voltage Balancing, Input Voltage Boosting, and AC Power Decoupling. Energies, 15(10), 3729. https://doi.org/10.3390/en15103729