Real Time Hardware-in-Loop Implementation of LLC Resonant Converter at Worst Operating Point Based on Time Domain Analysis

Abstract

:1. Introduction

- FDA-based design techniques are primarily reliant on engineering practice, such as how to choose the Q and K values, which is not universal, and the outcomes differ from one situation to the next;

- Only the most basic soft switching and voltage gain needs are taken into account in the design.

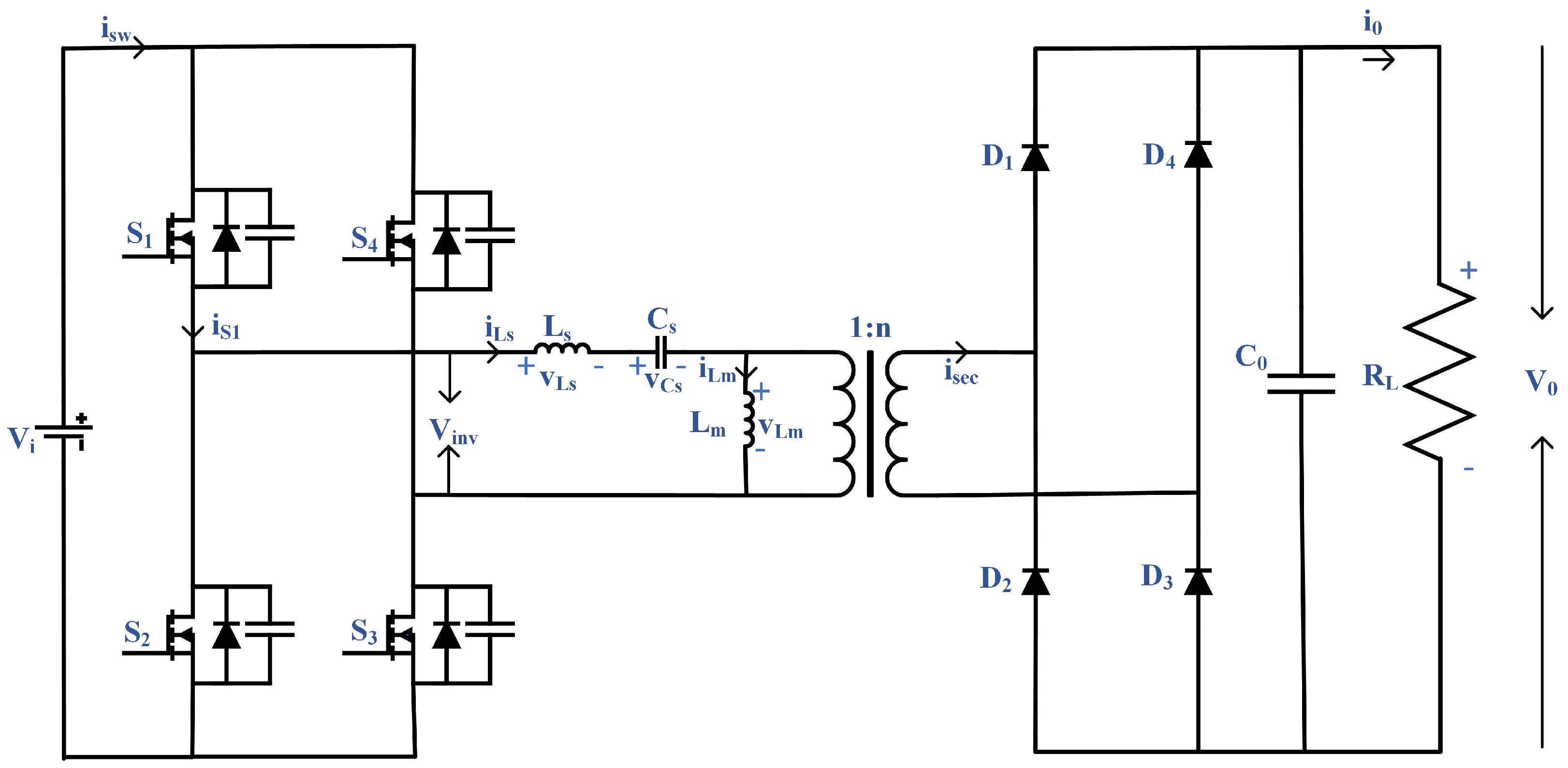

2. Time-Domain Analysis Introduction

3. Steady State Time-Domain Analysis

- The rectifier diodes, MOSFET switches and transformer are ideal;

- The filter capacitor is sufficiently big to maintain a stable voltage at the output;

- The capacitance of a MOSFET is quite small;

- The dead time between switches is not taken into account.

- The most typical mode of operation for an LLC-RC is the PO mode. Generally, the LLC-RC is intended to operate in this mode in order to attain ZVS for the primary switches and ZCS for the secondary diodes;

- The resonant tank control capabilities of an LLC converter can be increased by constructing it in the operation modes of PN or PON even when the peak gain operating point occurs in these modes [8,14]. The peak gain for the primary switch is also the barrier between ZVS and ZCS operation. When constructing an LLC-RC in PON or PN modes, the ZVS action may fail, reducing the efficiency of the converter;

- Furthermore, to obtain the ZVS operation in the PON or PN operating mode, a large dead-time is required. Excessive dead-time will have a negative impact on the converter’s efficiency. As a result, in terms of soft switching, the PO mode is favored above the PN or PON modes;

- In terms of performance, the PO mode is almost identical to the maximum gain mode. As a result, the voltage gain lost by using the worst-case PO operating mode design is negligible, and the PO mode may be utilized to estimate the peak gain as well;

- For closed-loop designs, this guarantees control stability by using negative gain–frequency curve slopes in the PO mode. Because of this, the PO mode of operation is recommended for LLC converters. A control instability problem can arise when the operating point of the gain–frequency curve varies in PN or PON mode, which is when the gain–frequency curve is operated at its boundary.

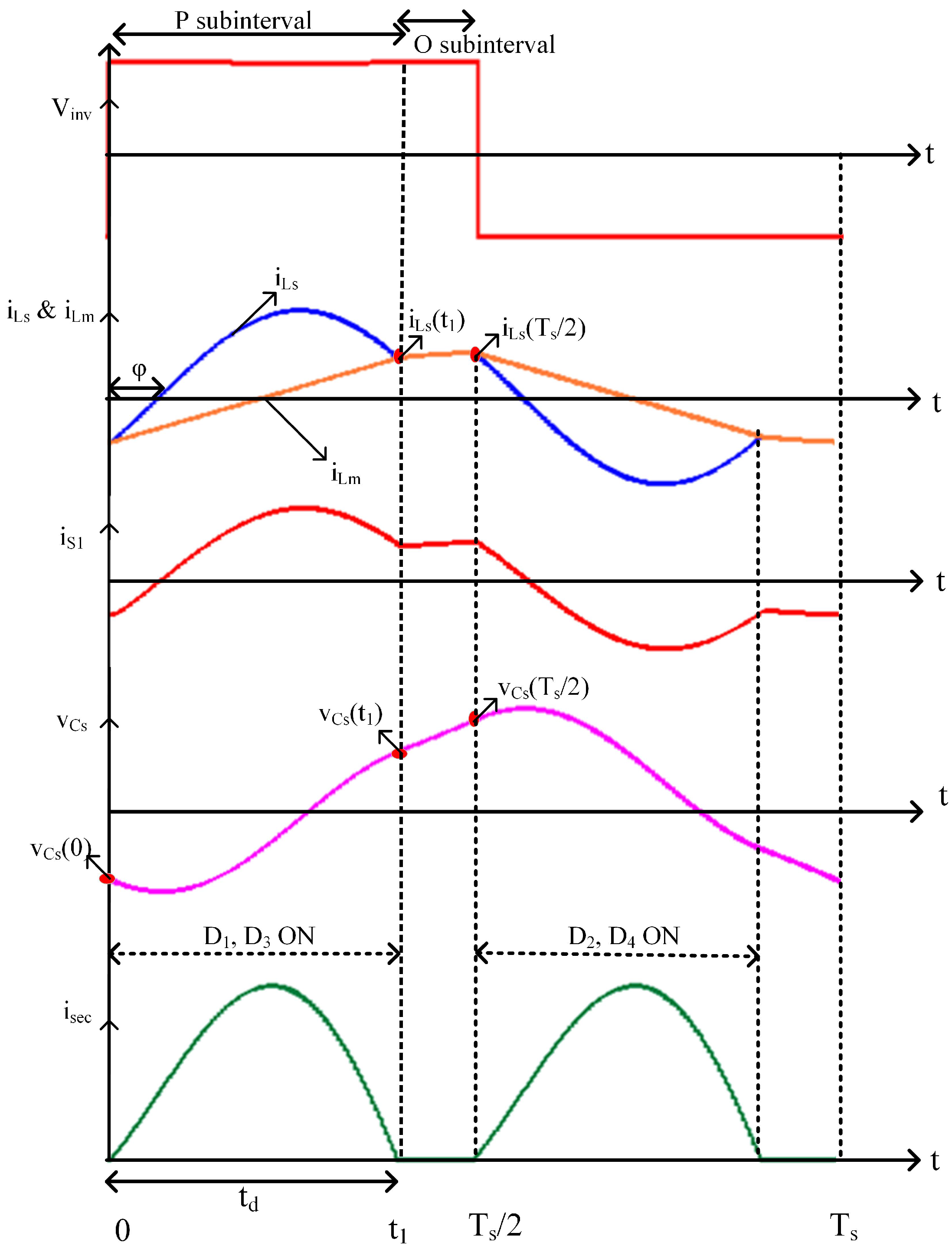

3.1. Energy Transfer Period (0 − T1)

3.2. Freewheeling Period (t1 − /2)

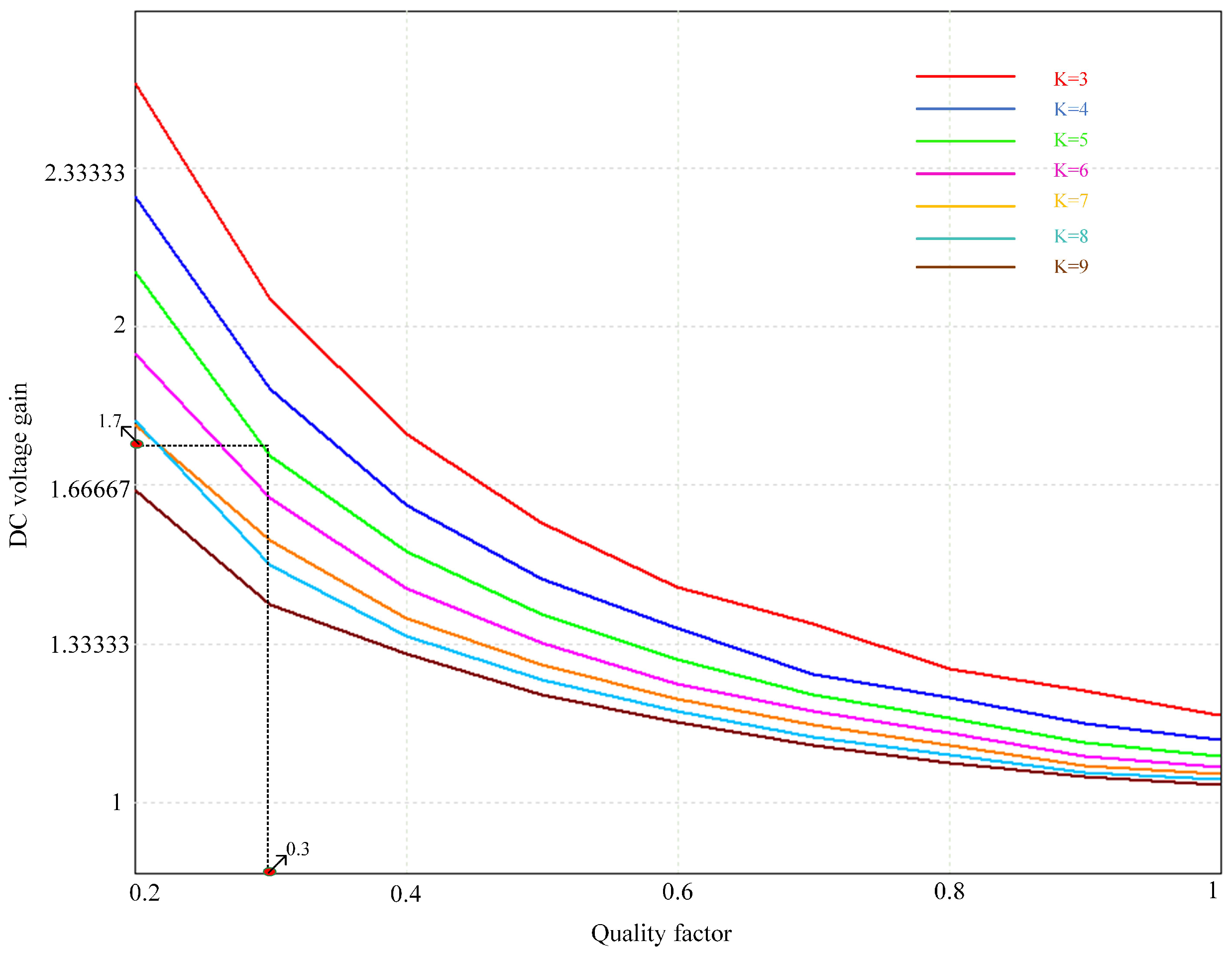

4. Complete Step-by-Step Design of an LLC-RC

- Determine the ratio of transformer turns;

- Determine the amount of DC gain required;

- Select Q and K in such a way that the output voltage gain matches the desired when the converter is working in PO mode;

- Determine the resonant components.

Loss Examination of LLC-RC

5. Simulation and Experimental Results

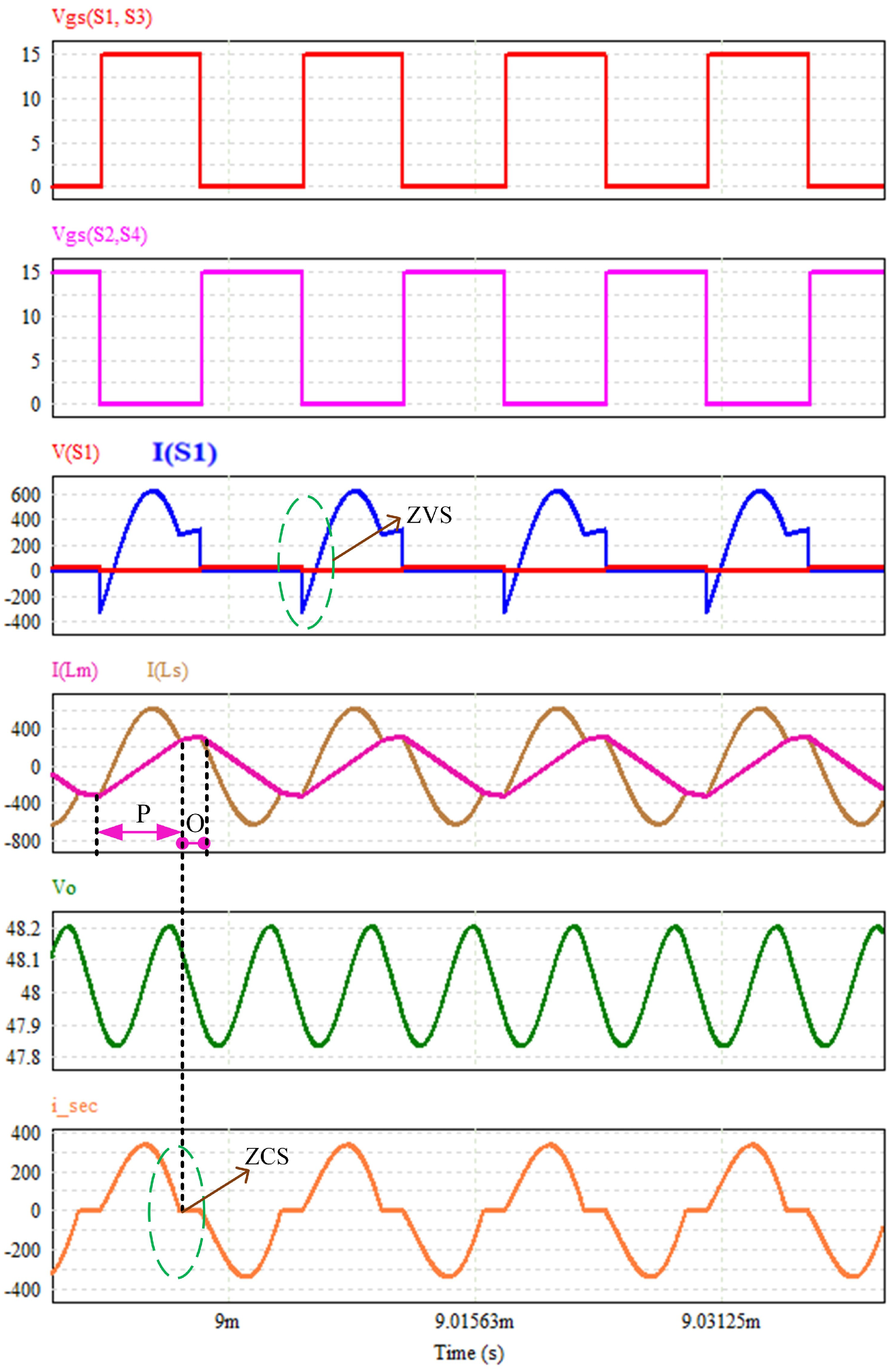

5.1. Simulation Results

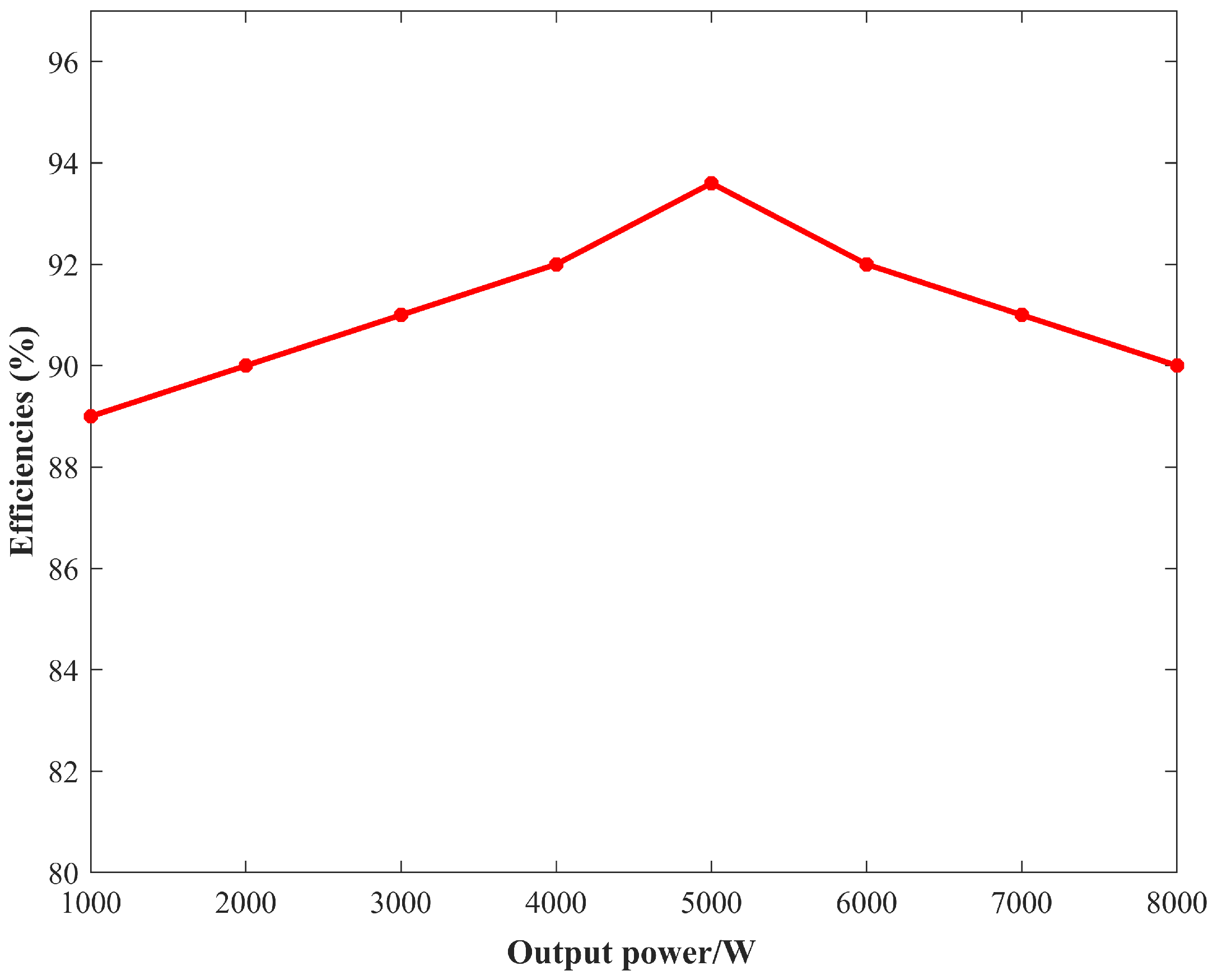

5.2. Experimental Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Zhou, Q.; Liu, Y.; Li, Z.; He, Z. A Coupled-Inductor Interleaved LLC Resonant Converter for Wide Operation Range. Energies 2022, 15, 315. [Google Scholar] [CrossRef]

- Manuel, D.; Kutschak, M.; Pulsinelli, F.; Rodriguez, N.; Morales, D.P. On the Practical Evaluation of the Switching Loss in the Secondary Side Rectifiers of LLC Converters. Energies 2021, 14, 5915. [Google Scholar]

- Tran, Y.K.; Freijedo, F.D.; Dujic, D. Open-loop power sharing characteristic of a three-port resonant LLC converter. CPSS Trans. Power Electron. Appl. 2019, 4, 171–179. [Google Scholar] [CrossRef]

- Wei, Y.; Altin, N.; Luo, Q.; Nasiri, A. A high efficiency, decoupled on-board battery charger with magnetic control. In Proceedings of the 2018 7th International Conference on Renewable Energy Research and Applications (ICRERA), Paris, France, 14–17 October 2018; pp. 920–925. [Google Scholar]

- Wei, Y.; Luo, Q.; Alonso, J.M.; Mantooth, A. A magnetically controlled single-stage AC–DC converter. IEEE Trans. Power Electron. 2020, 35, 8872–8877. [Google Scholar] [CrossRef]

- Yang, B.; Chen, R.; Lee, F.C. Integrated magnetic for LLC resonant converter. In Proceedings of the APEC. Seventeenth Annual IEEE Applied Power Electronics Conference and Exposition (Cat. No. 02CH37335), Dallas, TX, USA, 10–14 March 2002; pp. 346–351. [Google Scholar]

- Wei, Y.; Wang, Z.; Luo, Q.; Mantooth, H.A. MATLAB GUI Based Steady State Open-Loop and Closed-Loop Simulation Tools for Different LLC Converters With all Operation Modes. IEEE Open J. Ind. Appl. 2021, 2, 320–336. [Google Scholar] [CrossRef]

- Fang, X.; Hu, H.; Shen, Z.J.; Batarseh, I. Operation mode analysis and peak gain approximation of the LLC resonant converter. IEEE Trans. Power Electron. 2011, 27, 1985–1995. [Google Scholar] [CrossRef]

- Ivensky, G.; Bronshtein, S.; Abramovitz, A. Approximate analysis of resonant LLC DC-DC converter. IEEE Trans. Power Electron. 2011, 26, 3274–3284. [Google Scholar] [CrossRef]

- Liu, J.; Zhang, J.; Zheng, T.Q.; Yang, J. A modified gain model and the corresponding design method for an LLC resonant converter. IEEE Trans. Power Electron. 2016, 32, 6716–6727. [Google Scholar] [CrossRef]

- Deng, J.; Li, S.; Hu, S.; Mi, C.C.; Ma, R. Design methodology of LLC resonant converters for electric vehicle battery chargers. IEEE Trans. Veh. Technol. 2013, 63, 1581–1592. [Google Scholar] [CrossRef]

- Deng, J.; Mi, C.C.; Ma, R.; Li, S. Design of LLC resonant converters based on operation-mode analysis for level two PHEV battery chargers. IEEE/ASME Trans. Mechatron. 2014, 20, 1595–1606. [Google Scholar] [CrossRef]

- Hu, Z.; Wang, L.; Qiu, Y.; Liu, Y.F.; Sen, P.C. An accurate design algorithm for LLC resonant converters—Part I. IEEE Trans. Power Electron. 2015, 31, 5435–5447. [Google Scholar] [CrossRef]

- Hu, Z.; Wang, L.; Qiu, Y.; Liu, Y.F.; Sen, P.C. An accurate design algorithm for LLC resonant converters—Part II. IEEE Trans. Power Electron. 2015, 31, 5448–5460. [Google Scholar] [CrossRef]

- Yu, R.; Ho, G.K.Y.; Pong, B.M.H.; Ling, B.W.K.; Lam, J. Computer-aided design and optimization of high-efficiency LLC series resonant converter. IEEE Trans. Power Electron. 2011, 27, 3243–3256. [Google Scholar] [CrossRef] [Green Version]

- Xu, H.; Yin, Z.; Zhao, Y.; Huang, Y. Accurate design of high-efficiency LLC resonant converter with wide output voltage. IEEE Acess 2017, 5, 26653–26665. [Google Scholar] [CrossRef]

- Bhat, A.S. Analysis and design of LCL-type series resonant converter. IEEE Trans. Ind. Electron. 1994, 41, 118–124. [Google Scholar] [CrossRef]

- Steigerwald, R.L. A comparison of half-bridge resonant converter topologies. IEEE Trans. Power Electron. 1988, 3, 174–182. [Google Scholar] [CrossRef]

- Bhat, A.S. A generalized steady-state analysis of resonant converters using two-port model and Fourier-series approach. IEEE Trans. Power Electron. 1998, 13, 142–151. [Google Scholar] [CrossRef]

- Forsyth, A.J.; Ward, G.A.; Mollov, S.V. Extended fundamental frequency analysis of the LCC resonant converter. IEEE Trans. Power Electron. 2003, 18, 1286–1292. [Google Scholar] [CrossRef]

- Lee, B.H.; Kim, M.Y.; Kim, C.E.; Park, K.B.; Moon, G.W. Analysis of LLC resonant converter considering effects of parasitic components. In Proceedings of the INTELEC 2009-31st International Telecommunications Energy Conference, Incheon, Korea, 18–22 October 2009; pp. 1–6. [Google Scholar]

- Lin, R.L.; Lin, C.W. Design criteria for resonant tank of LLC DC-DC resonant converter. In Proceedings of the IECON 2010-36th Annual Conference on IEEE Industrial Electronics Society Conference, Glendale, CA, USA, 7–10 November 2010; pp. 427–432. [Google Scholar]

- Jung, J.H.; Kwon, J.G. Theoretical analysis and optimal design of LLC resonant converter. In Proceedings of the 2007 European Conference on Power Electronics and Applications, Aalborg, Denmark, 2–5 September 2007; pp. 1–10. [Google Scholar]

- Batarseh, I.; Liu, R.; Ortiz-Conde, A.; Yacoub, A.; Siri, K. Steady state analysis and performance characteristics of the LLC-type parallel resonant converter. In Proceedings of the 1994 Power Electronics Specialist Conference-PESC’94, Taipei, Taiwan, 20–25 June 1994; pp. 597–606. [Google Scholar]

- Vukšić, M.; Beroxsx, S.M.; Mihoković, L. The multiresonant converter steady-state analysis based on dominant resonant process. IEEE Trans. Power Electron. 2010, 26, 1452–1468. [Google Scholar] [CrossRef]

- Lazar, J.F.; Martinelli, R. Steady-state analysis of the LLC series resonant converter. In Proceedings of the APEC 2001 Sixteenth Annual IEEE Applied Power Electronics Conference and Exposition (Cat. No. 01CH37181), Anaheim, CA, USA, 4–8 March 2001; pp. 728–735. [Google Scholar]

- Oeder, C.; Bucher, A.; Stahl, J.; Duerbaum, T. A comparison of different design methods for the multiresonant LLC converter with capacitive output filter. In Proceedings of the 2010 IEEE 12th Workshop on Control and Modeling for Power Electronics (COMPEL), Boulder, CO, USA, 28–30 June 2010; pp. 1–7. [Google Scholar]

- Costa, V.S.; Perdigao, M.S.; Mendes, A.S.; Alonso, J.M. Evaluation of a variable-inductor-controlled LLC resonant converter for battery charging applications. In Proceedings of the IECON 2016-42nd Annual Conference of the IEEE Industrial Electronics Society, Piazza Adua, Firenze, Italy, 24–27 October 2016; pp. 5633–5638. [Google Scholar]

- Fang, Z.; Cai, T.; Duan, S.; Chen, C. Optimal design methodology for LLC resonant converter in battery charging applications based on time-weighted average efficiency. IEEE Trans. Power Electron. 2014, 30, 5469–5483. [Google Scholar] [CrossRef]

- Yang, C.H.; Liang, T.J.; Chen, K.H.; Li, J.S.; Lee, J.S. Loss analysis of half-bridge LLC resonant converter. In Proceedings of the 2013 1st International Future Energy Electronics Conference (IFEEC), Tainan, Taiwan, 3–6 November 2013; pp. 155–160. [Google Scholar]

| Parameter | Designator | Value |

|---|---|---|

| Input voltage range | – | 24–32 V |

| Input nominal voltage | 28 V | |

| Output voltage | – | 48 V |

| Rated output power | 8000 W | |

| Series resonant frequency | 100 kHz |

| Q | K | - | Normalized Frequency | (KHz) | (KHz) | _ (A) | _ (A) | _ (V) | _ (A) | _ (A) | _ (A) | _ (A) | _ (V) | (µH) | C (µF) | (µH) |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0.3 | 3 | 0.87 | 1.18 | 118 | 100 | 170.83 | 499.75 | 32 | 62.83 | 206.80 | 318.64 | 341.66 | 11.80 | 0.0468 | 54.134 | 0.14 |

| 0.3 | 3 | 1.67 | 0.85 | 85 | 100 | 254.83 | 718.98 | 32 | 83.96 | 323.76 | 541.90 | 509.66 | 55.86 | 0.0468 | 54.134 | 0.14 |

| 0.3 | 4 | 0.87 | 1.23 | 123 | 100 | 151.110 | 438.460 | 32 | 62.75 | 198.84 | 228.96 | 302.220 | 9.975 | 0.0468 | 54.134 | 0.187 |

| 0.3 | 4 | 1.67 | 0.81 | 81 | 100 | 224.47 | 653.42 | 32 | 83.94 | 330.063 | 411.17 | 448.95 | 51.03 | 0.0468 | 54.134 | 0.187 |

| 0.3 | 5 | 0.87 | 1.27 | 127 | 100 | 141.24 | 406.28 | 32 | 62.71 | 194.390 | 177.290 | 282.49 | 9.015 | 0.0468 | 54.134 | 0.234 |

| 0.3 | 5 | 1.66 | 0.78 | 78 | 100 | 208.490 | 626.14 | 32 | 83.39 | 336.37 | 329.79 | 416.98 | 22.38 | 0.0468 | 54.134 | 0.234 |

| 0.3 | 6 | 0.87 | 1.3 | 130 | 100 | 135.69 | 387.15 | 32 | 62.73 | 191.74 | 144.39 | 271.39 | 8.46 | 0.0468 | 54.134 | 0.281 |

| 0.3 | 6 | 1.67 | 0.74 | 74 | 100 | 204.63 | 636.74 | 32 | 83.94 | 354.88 | 276.15 | 409.27 | 45.480 | 0.0468 | 54.134 | 0.281 |

| 0.3 | 7 | 0.87 | 1.33 | 133 | 100 | 131.89 | 374.22 | 32 | 62.62 | 189.66 | 120.75 | 263.78 | 8.043 | 0.0468 | 54.134 | 0.328 |

| 0.3 | 7 | 1.67 | 0.71 | 71 | 100 | 202.39 | 648.97 | 32 | 83.89 | 368.91 | 236.090 | 404.78 | 43.63 | 0.0468 | 54.134 | 0.328 |

| 0.3 | 8 | 0.87 | 1.35 | 135 | 100 | 129.52 | 365.46 | 32 | 62.64 | 188.450 | 104.12 | 259.049 | 7.79 | 0.0468 | 54.134 | 0.374 |

| 0.3 | 8 | 1.66 | 0.69 | 69 | 100 | 199.90 | 655.56 | 32 | 83.34 | 376.83 | 205.27 | 399.80 | 42.10 | 0.0468 | 54.134 | 0.374 |

| 0.3 | 9 | 0.87 | 1.37 | 137 | 100 | 127.68 | 358.87 | 32 | 62.58 | 187.42 | 91.11 | 255.37 | 7.57 | 0.0468 | 54.134 | 0.421 |

| 0.3 | 9 | 1.67 | 0.66 | 66 | 100 | 202.79 | 683.98 | 32 | 83.62 | 395.59 | 181.28 | 405.58 | 40.85 | 0.0468 | 54.134 | 0.421 |

| 0.3 | 10 | 0.87 | 1.38 | 138 | 100 | 126.58 | 354.1 | 32 | 62.68 | 186.92 | 81.53 | 253.16 | 7.47 | 0.0468 | 54.134 | 0.468 |

| 0.3 | 10 | 1.66 | 0.64 | 64 | 100 | 203.75 | 701.41 | 32 | 83.38 | 407.05 | 161.79 | 407.50 | 39.77 | 0.0468 | 54.134 | 0.468 |

| Name of the Device | Loss Calculation |

|---|---|

| MOSFET | Gate-Driving loss = |

| Turn-off loss = | |

| Conduction loss in MOSFET = loss in MOSFET+ loss in | |

| antiparallel diode = | |

| Transformer | Core loss = |

| Copper loss = | |

| Diode | Conduction loss of diodes = |

| Name of the Device | OP5700 Simulator |

|---|---|

| FPGA | Xilinx® Virtex® 7 FPGA on VC707 board |

| Processing speed: 200 ns–20 s | |

| I/O Lines | 256 lines, routed to eight analog or digital, |

| 16 or 32 channels | |

| High-speed communication ports | 16SFP sockets, up to 5 GBps |

| I/O connectors | Four panels of four DB37 connectors |

| Monitoring connectors | Four panels of RJ45 connectors |

| PC interface | Standard PC connectors |

| Power rating | Input: 100–240 VAC, 50–60 Hz, 10/5 A, Power: 600 W |

| Name of the Component | Parameter |

|---|---|

| Primary MOSFET (–) | VISHAY SQJQ140E |

| Rectifier diodes (–) | VISHAY VS-403CNQ100PbF |

| Turns ratio () | 1:1.72 |

| Resonant capacitor () | 54.134 µF |

| Resonant inductor () | 0.04679 µH |

| Magnetizing inductor () | 0.23395 µH |

| Design Parameter | Simulation Value | Experimental Value |

|---|---|---|

| Q | 0.3 | 0.3 |

| K | 5 | 5 |

| (KHz) | 78 | 77 |

| (KHz) | 100 | 98.61 |

| _ (A) | 208.49 | 206.2 |

| _ (A) | 626.14 | 619.3 |

| _ (V) | 32 | 24 |

| _ (A) | 83.39 | 80.5 |

| _ (A) | 336.37 | 331 |

| _ (A) | 329.79 | 325.1 |

| _ (A) | 416.98 | 409.5 |

| _ (V) | 22.38 | 22 |

| (µH) | 0.0468 | 0.0468 |

| (µF) | 54.134 | 54.134 |

| (µH) | 0.23396 | 0.23396 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Geddam, K.K.; Devaraj, E. Real Time Hardware-in-Loop Implementation of LLC Resonant Converter at Worst Operating Point Based on Time Domain Analysis. Energies 2022, 15, 3634. https://doi.org/10.3390/en15103634

Geddam KK, Devaraj E. Real Time Hardware-in-Loop Implementation of LLC Resonant Converter at Worst Operating Point Based on Time Domain Analysis. Energies. 2022; 15(10):3634. https://doi.org/10.3390/en15103634

Chicago/Turabian StyleGeddam, Kiran Kumar, and Elangovan Devaraj. 2022. "Real Time Hardware-in-Loop Implementation of LLC Resonant Converter at Worst Operating Point Based on Time Domain Analysis" Energies 15, no. 10: 3634. https://doi.org/10.3390/en15103634

APA StyleGeddam, K. K., & Devaraj, E. (2022). Real Time Hardware-in-Loop Implementation of LLC Resonant Converter at Worst Operating Point Based on Time Domain Analysis. Energies, 15(10), 3634. https://doi.org/10.3390/en15103634