Prediction of DC-Link Voltage Switching Ripple in Three-Phase Four-Leg PWM Inverters

Abstract

1. Introduction

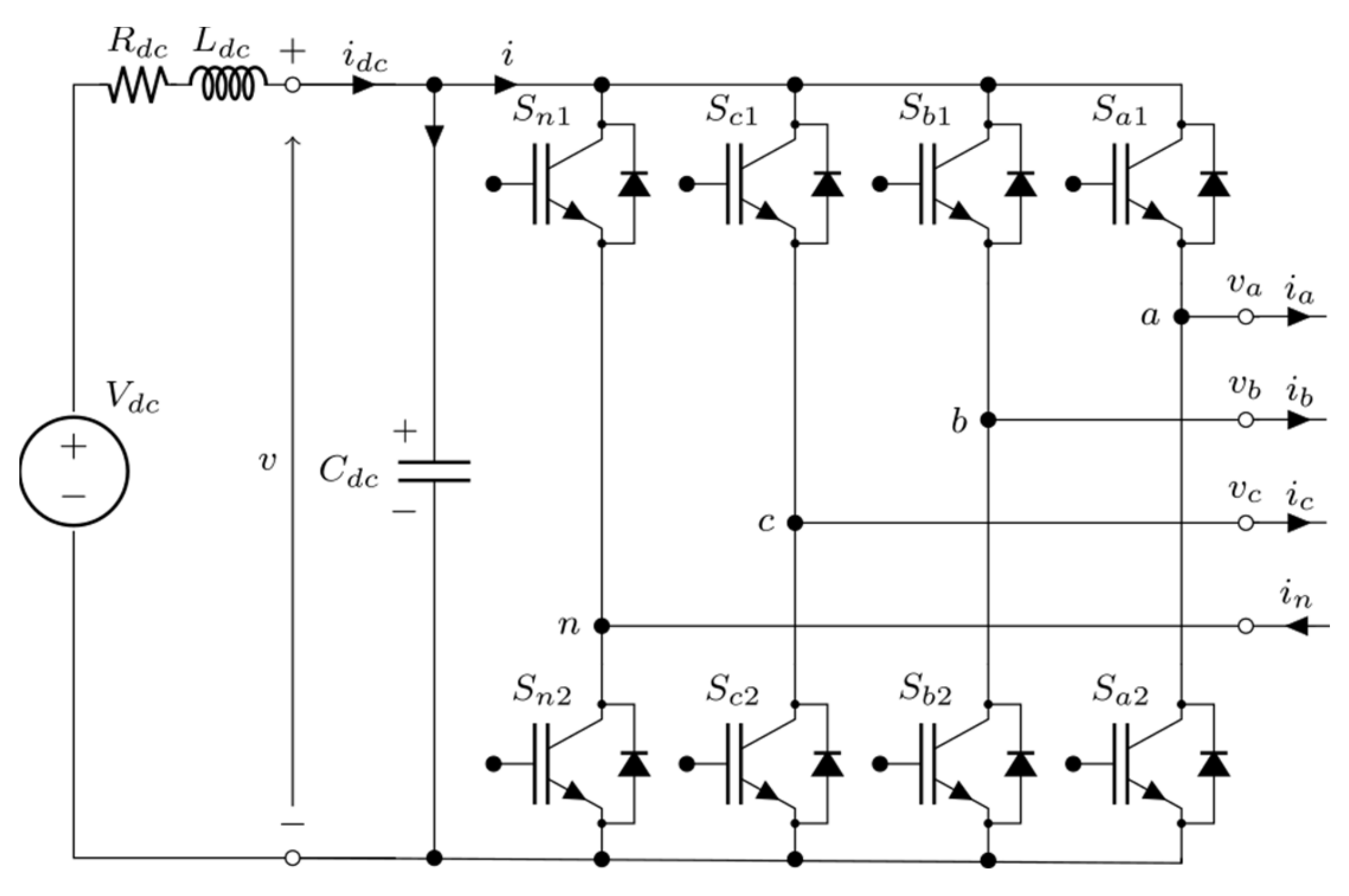

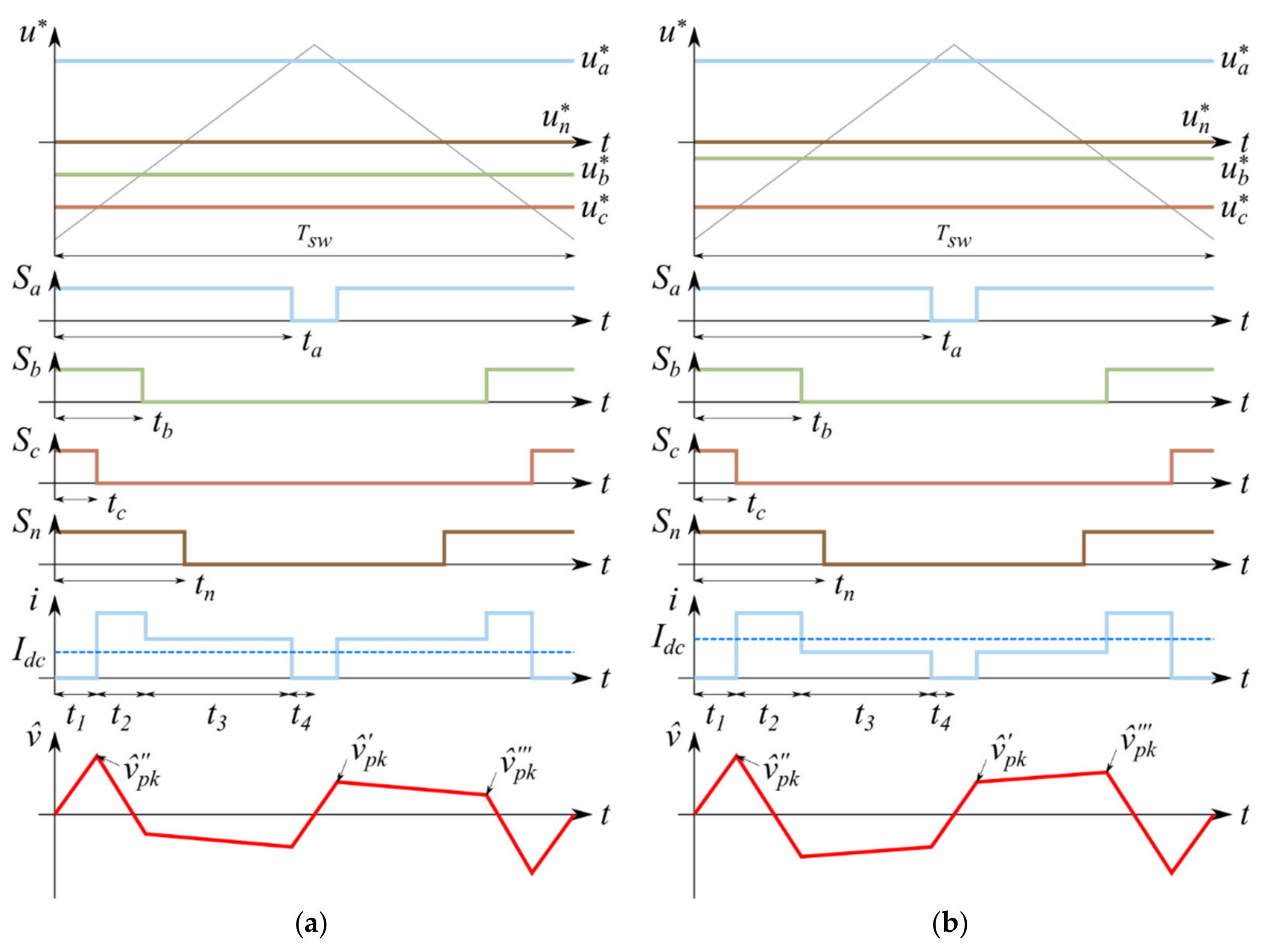

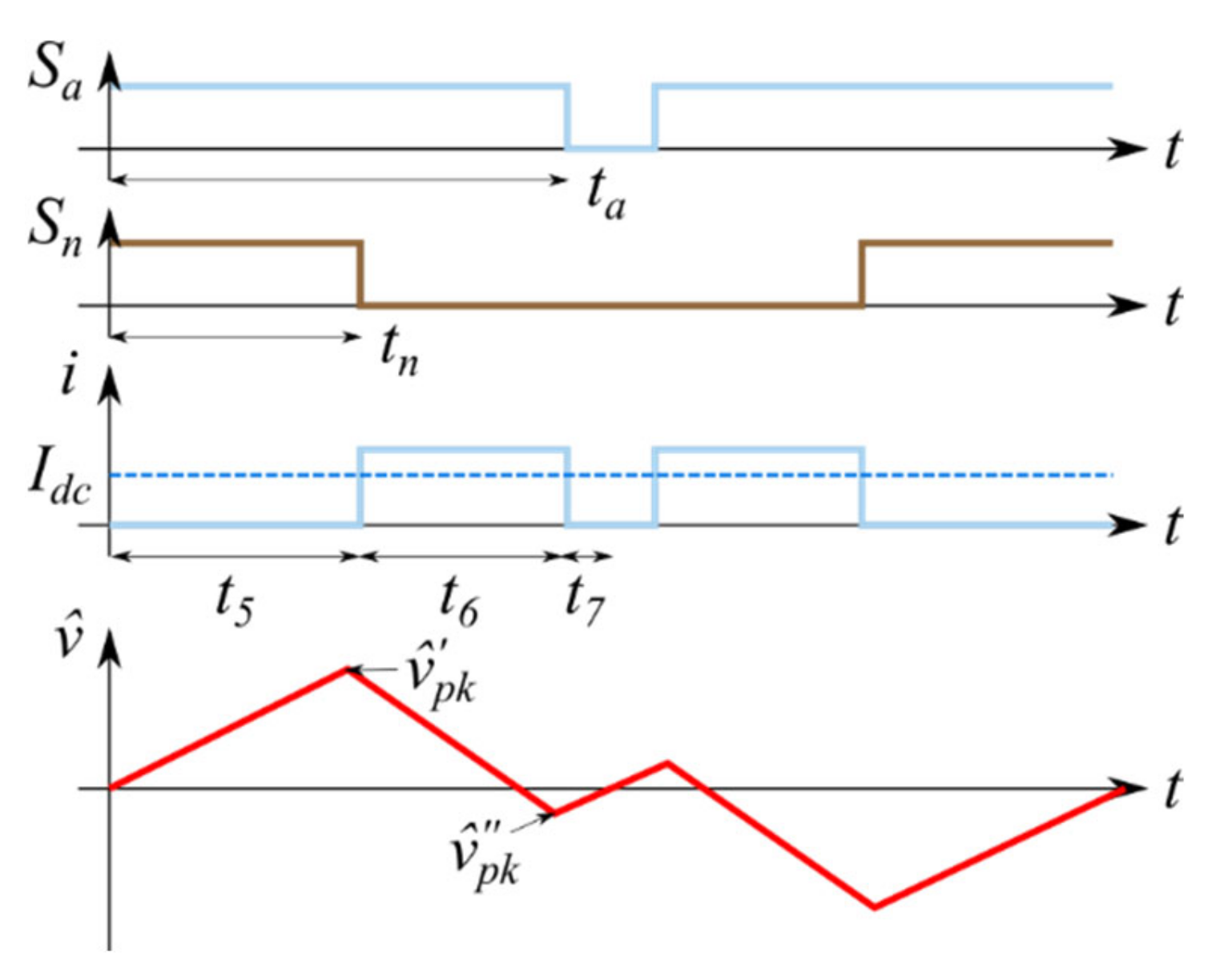

2. System Configuration and Modulation Principle

3. Converter DC-Link Current in Case of Balanced and Unbalanced Currents

3.1. Balanced Currents

3.2. Unbalanced Currents

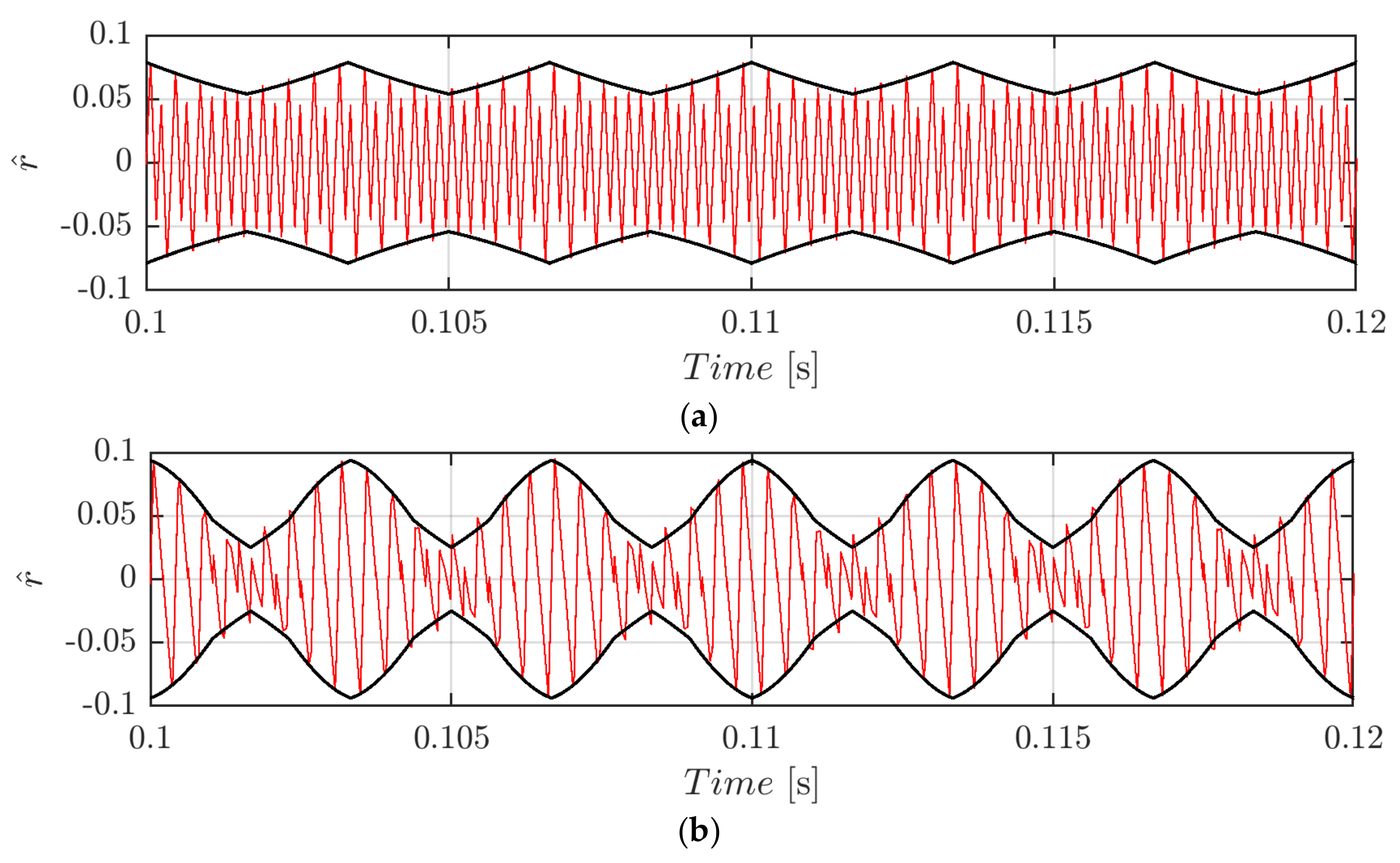

4. Evaluation of DC-Link Voltage Ripple

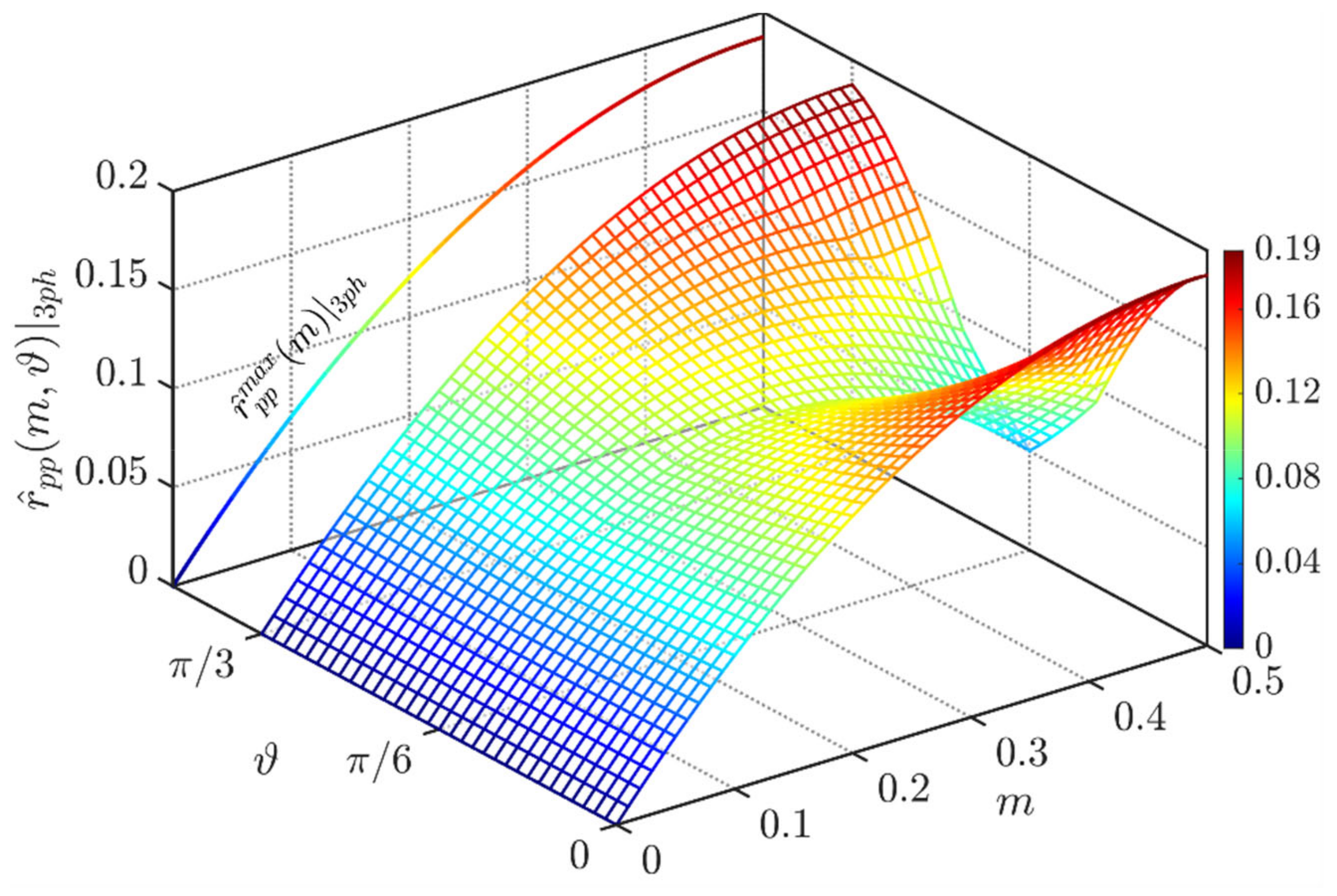

4.1. Peak-to-Peak Voltage Ripple—Balanced Currents

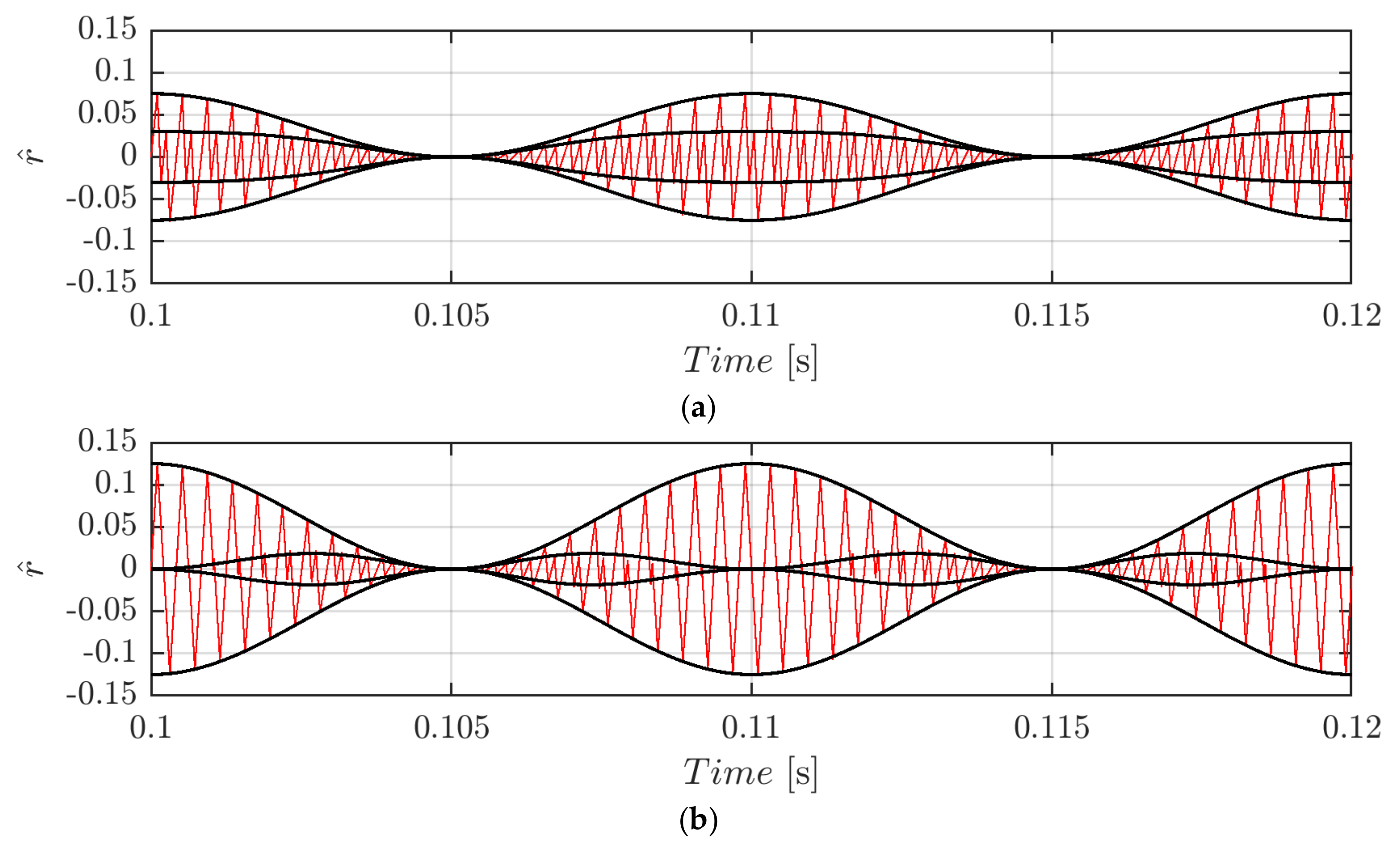

4.1.1. Sinusoidal PWM

4.1.2. Centered PWM (SVM)

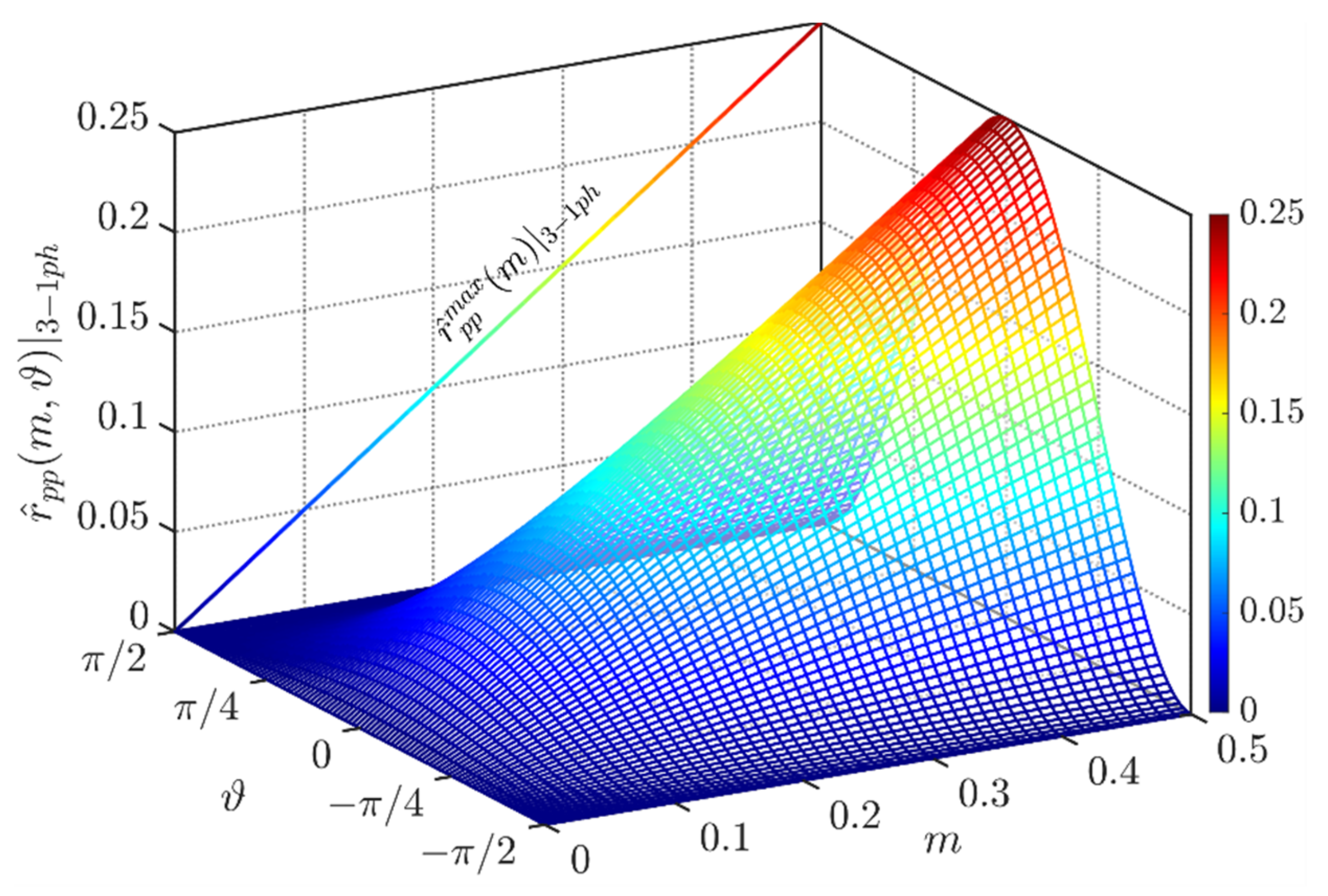

4.2. Peak-to-Peak Voltage Ripple—Unbalanced Currents

4.2.1. Sinusoidal PWM

4.2.2. Centered PWM (SVM)

4.2.3. Single-Phase Modulation

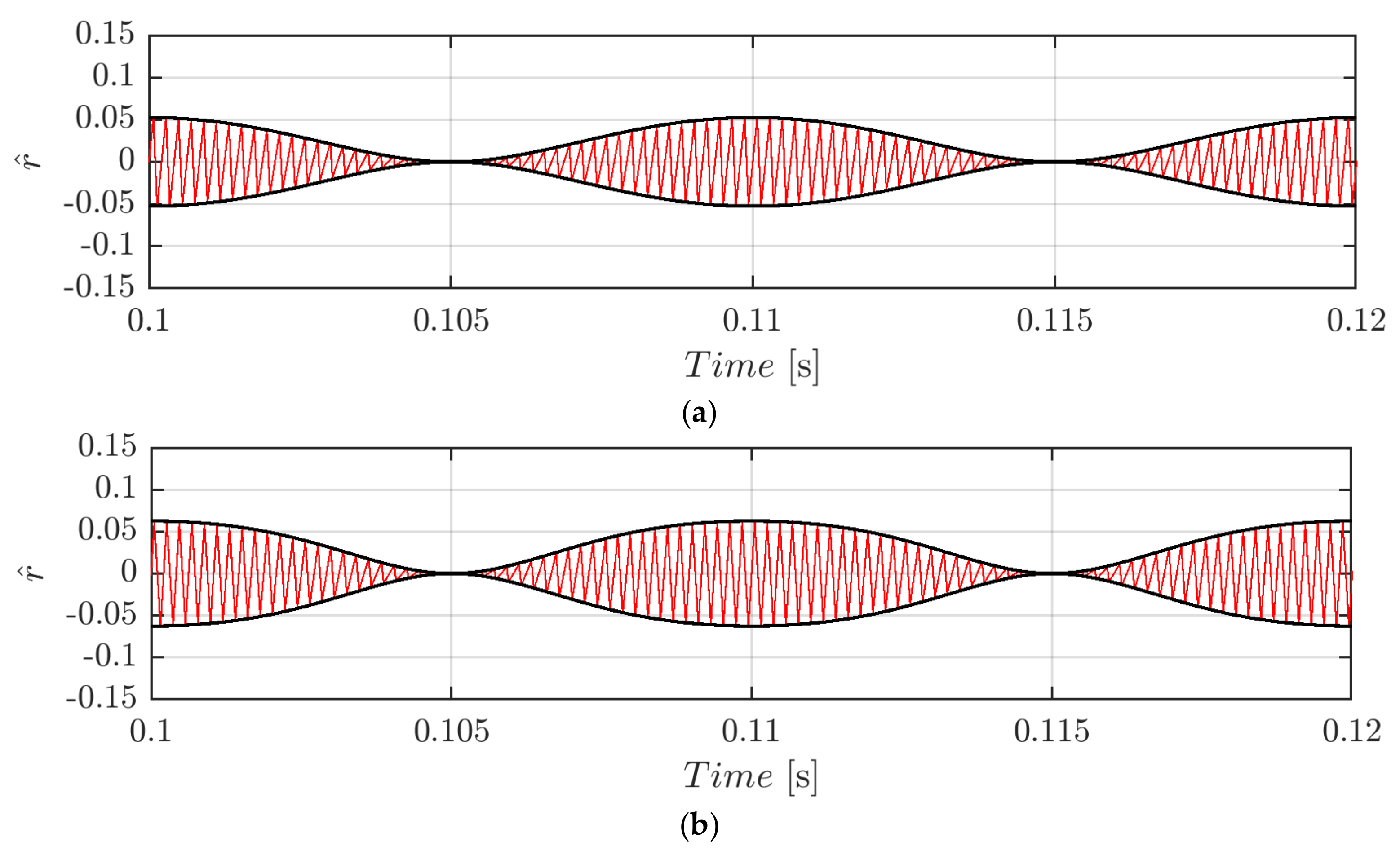

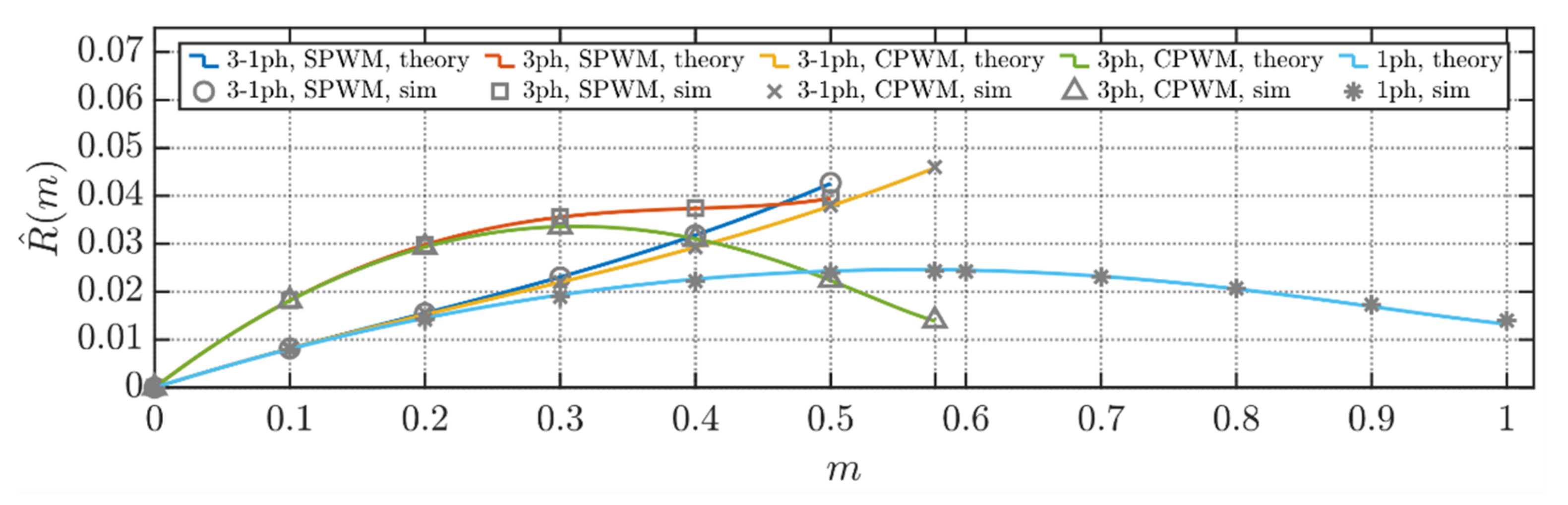

4.3. Voltage Ripple RMS-Balanced Currents

4.3.1. Sinusoidal PWM

4.3.2. Centered PWM (SVM)

4.4. Voltage Ripple RMS—Unbalanced Currents

4.4.1. Sinusoidal PWM

4.4.2. Centered PWM (SVM)

4.4.3. Single-Phase Modulation

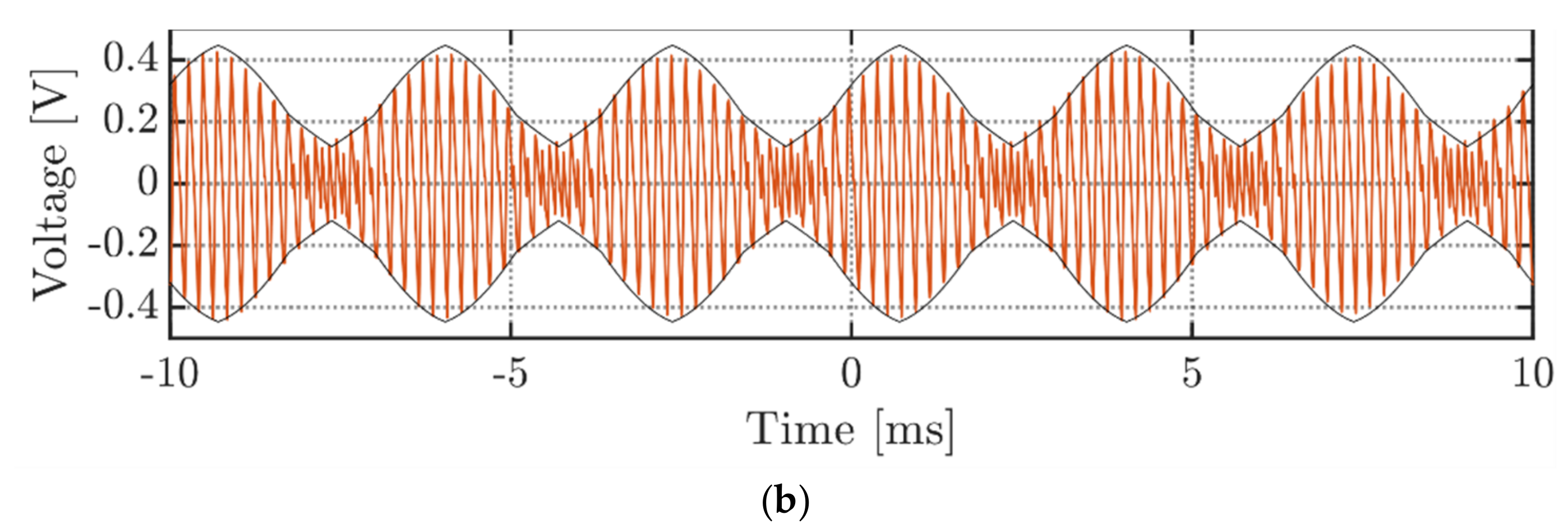

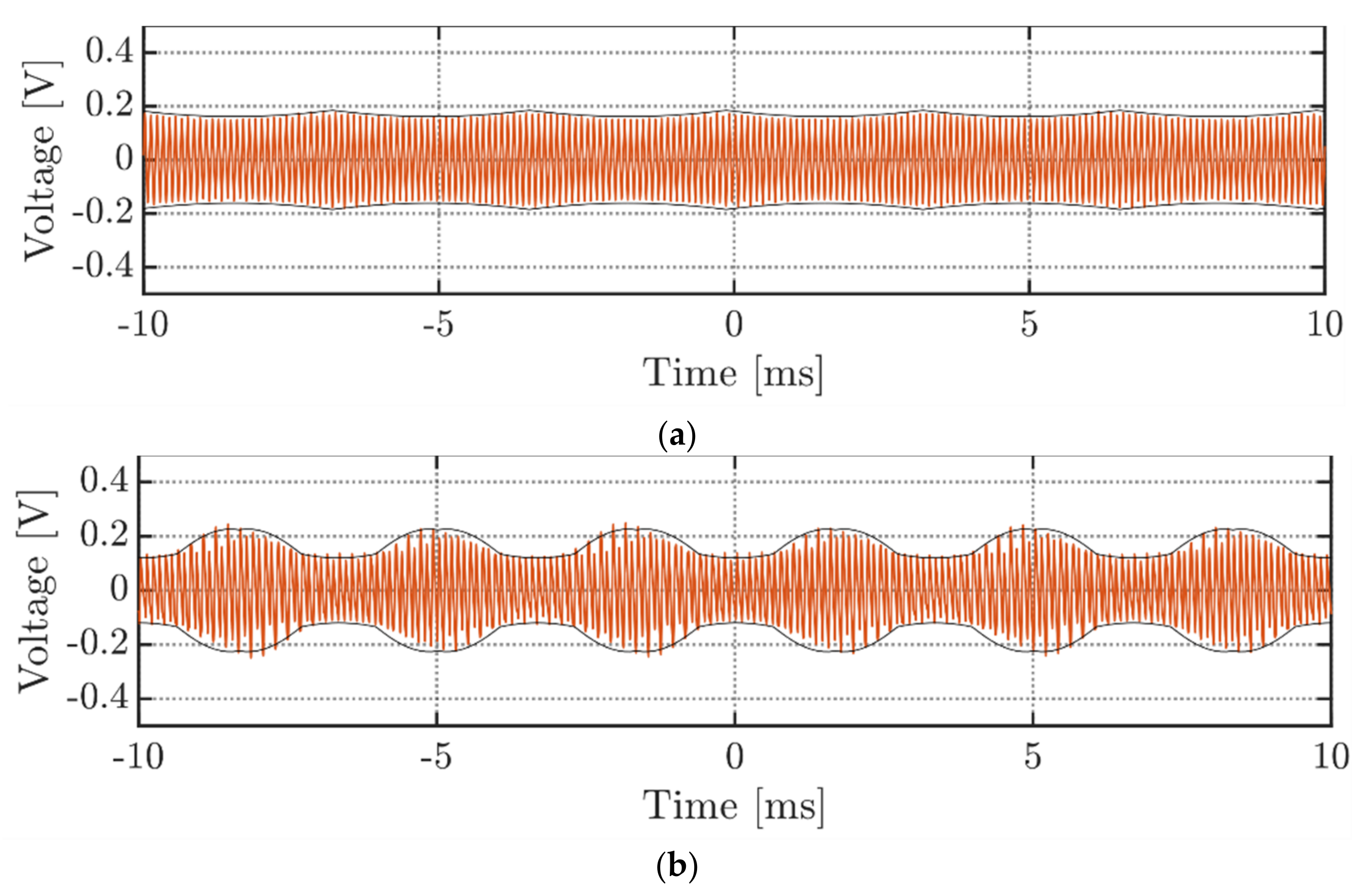

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Nomenclature

| x | Index for phases a, b, c, and neutral n, used as a subscript |

| , | Converter’s instantaneous phase current and its amplitude |

| ,,,, | Converter’s input current instantaneous value, high-frequency component, low-frequency component, averaged component, and mean value |

| ,,,, | Converter’s DC-link voltage instantaneous value, high-frequency component, low-frequency component, averaged component, and mean value |

| , | Modulating signals and sinusoidal modulating signal |

| γ | Common-mode injection |

| mx, m | Modulation index (normalized by DC-link voltage Vdc) |

| ϑ, t | Phase angle and time |

| Sx1 | Legs’ switching functions |

| , | Peak (pk) and peak-to-peak (pp) voltage ripple wrapping envelopes |

| , | Normalized peak (pk) and peak-to-peak (pp) voltage ripple wrapping envelopes |

| , | Maximum peak-to-peak input voltage ripple and its normalization |

| , | DC-link voltage switching ripple RMS and its normalization |

References

- Zhao, W.; Ruan, X.; Yang, D.; Chen, X.; Jia, L. Neutral Point Voltage Ripple Suppression for a Three-Phase Four-Wire Inverter With an Independently Controlled Neutral Module. IEEE Trans. Ind. Electron. 2017, 64, 2608–2619. [Google Scholar] [CrossRef]

- Nascimento, C.F.; Diene, O.; Watanabe, E.H. Analytical Model of Three-Phase Four-Wire VSC Operating as Grid Forming Power Converter under Unbalanced Load Conditions. In Proceedings of the 2017 IEEE 12th International Conference on Power Electronics and Drive Systems (PEDS), Honolulu, HI, USA, 12–15 December 2017; pp. 1219–1224. [Google Scholar]

- Carrasco, G.; Silva, C.A.; Peña, R.; Cárdenas, R. Control of a Four-Leg Converter for the Operation of a DFIG Feeding Stand-Alone Unbalanced Loads. IEEE Trans. Ind. Electron. 2015, 62, 4630–4640. [Google Scholar] [CrossRef]

- Khadkikar, V.; Chandra, A.; Singh, B. Digital signal processor implementation and performance evaluation of split capacitor, four-leg and three H-bridge-based three-phase four-wire shunt active filters. IET Power Electron. 2011, 4, 463–470. [Google Scholar] [CrossRef]

- Aredes, M.; Hafner, J.; Heumann, K. Three-Phase Four-Wire Shunt Active Filter Control Strategies. IEEE Trans. Power Electron. 1997, 12, 311–318. [Google Scholar] [CrossRef]

- Yaramasu, V.; Rivera, M.; Wu, B.; Rodriguez, J. Model Predictive Current Control of Two-Level Four-Leg Inverters—Part I: Concept, Algorithm, and Simulation Analysis. IEEE Trans. Power Electron. 2013, 28, 3459–3468. [Google Scholar] [CrossRef]

- Rivera, M.; Yaramasu, V.; Rodriguez, J.; Wu, B. Model Predictive Current Control of Two-Level Four-Leg Inverters—Part II: Experimental Implementation and Validation. IEEE Trans. Power Electron. 2013, 28, 3469–3478. [Google Scholar] [CrossRef]

- Mandrioli, R.; Viatkin, A.; Hammami, M.; Ricco, M.; Grandi, G. A Comprehensive AC Current Ripple Analysis and Performance Enhancement via Discontinuous PWM in Three-Phase Four-Leg Grid-Connected Inverters. Energies 2020, 13, 4352. [Google Scholar] [CrossRef]

- Dorf, R.C.; Bishop, R.H. Modern Control Systems, 11th ed.; Prentice Hall: Upper Saddle River, NJ, USA, 2008. [Google Scholar]

- Ghosh, R.; Narayanan, G. Control of Three-Phase, Four-Wire PWM Rectifier. IEEE Trans. Power Electron. 2008, 23, 96–106. [Google Scholar] [CrossRef]

- Li, A.; Jiang, D.; Kong, W.; Qu, R. Four-Leg Converter for Reluctance Machine With DC-Biased Sinusoidal Winding Current. IEEE Trans. Power Electron. 2019, 34, 4569–4580. [Google Scholar] [CrossRef]

- Fu, Y.; Li, Y.; Huang, Y.; Lu, X.; Zou, K.; Chen, C.; Bai, H. Imbalanced Load Regulation Based on Virtual Resistance of A Three-Phase Four-Wire Inverter for EV Vehicle-to-Home Applications. IEEE Trans. Transp. Electrif. 2019, 5, 162–173. [Google Scholar] [CrossRef]

- Viatkin, A.; Mandrioli, R.; Hammami, M.; Ricco, M.; Grandi, G. AC Current Ripple Harmonic Pollution in Three-Phase Four-Leg Active Front-End AC/DC Converter for On-Board EV Chargers. Electronics 2021, 10, 116. [Google Scholar] [CrossRef]

- Fu, Y.; Li, Y.; Huang, Y.; Bai, H.; Zou, K.; Lu, X.; Chen, C. Design Methodology of a Three-Phase Four-Wire EV Charger Operated at the Autonomous Mode. IEEE Trans. Transp. Electrif. 2019, 5, 1169–1181. [Google Scholar] [CrossRef]

- Hintz, A.; Prasanna, R.; Rajashekara, K. Comparative Study of Three-phase Grid Connected Inverter Sharing Unbalanced Three-phase and/or Single-phase systems. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 6491–6496. [Google Scholar]

- Hintz, A.; Prasanna, U.R.; Rajashekara, K. Comparative Study of the Three-Phase Grid-Connected Inverter Sharing Unbalanced Three-Phase and/or Single-Phase systems. IEEE Trans. Ind. Appl. 2016, 52, 5156–5164. [Google Scholar] [CrossRef]

- Kim, J.-H.; Sul, S.-K. A Carrier-Based PWM Method for Three-Phase Four-Leg Voltage Source Converters. IEEE Trans. Power Electron. 2004, 19, 66–75. [Google Scholar] [CrossRef]

- Lin, Z.; Ruan, X.; Jia, L.; Zhao, W.; Liu, H.; Rao, P. Optimized Design of the Neutral Inductor and Filter Inductors in Three-Phase Four-Wire Inverter With Split DC-Link Capacitors. IEEE Trans. Power Electron. 2019, 34, 247–262. [Google Scholar] [CrossRef]

- Hammami, M.; Mandrioli, R.; Viatkin, A.; Ricco, M.; Grandi, G. Analysis of Input Voltage Switching Ripple in Three-Phase Four-Wire Split Capacitor PWM Inverters. Energies 2020, 13, 5076. [Google Scholar] [CrossRef]

- Hava, A.M.; Kerkman, R.J.; Lipo, T.A. Carrier-based PWM-VSI overmodulation strategies: Analysis, comparison, and design. IEEE Trans. Power Electron. 1998, 13, 674–689. [Google Scholar] [CrossRef]

- Vujacic, M.; Hammami, M.; Srndovic, M.; Grandi, G. Theoretical and Experimental Investigation of Switching Ripple in the DC-Link Voltage of Single-Phase H-Bridge PWM Inverters. Energies 2017, 10, 1189. [Google Scholar] [CrossRef]

- Vujacic, M.; Hammami, M.; Srndovic, M.; Grandi, G. Analysis of dc-link voltage switching ripple in three-phase PWM inverters. Energies 2018, 11, 471. [Google Scholar] [CrossRef]

- Hammami, M.; Rizzoli, G.; Mandrioli, R.; Grandi, G. Capacitors Voltage Switching Ripple in Three-Phase Three-Level Neutral Point Clamped Inverters with Self-Balancing Carrier-Based Modulation. Energies 2018, 11, 3244. [Google Scholar] [CrossRef]

- Gopalakrishnan, K.S.; Das, S.; Narayanan, G. Analytical expression for RMS DC link capacitor current in a three-level inverter. In Proceedings of the Centenary Conference Electrical Engineering, Indian Institute of Science, Bangalore, India, 15–17 December 2011; pp. 1–6. [Google Scholar]

- Chen, T.; Li, S.; Fahimi, B. Analysis of DC-Link Voltage Ripple in Voltage Source Inverters without Electrolytic Capacitor. In Proceedings of the IECON 2018—44th Annual Conference of the IEEE Industrial Electronics Society, Washington, DC, USA, 21–23 October 2018; pp. 1041–1048. [Google Scholar]

- Srndovic, M.; Fišer, R.; Grandi, G. Analysis of Equivalent Inductance of Three-phase Induction Motors in the Switching Frequency Range. Electronics 2019, 8, 120. [Google Scholar] [CrossRef]

| Parameter | Symbol | Value | Unit |

|---|---|---|---|

| DC-link voltage | Vdc | 100 | V |

| DC-link capacitor: —balanced currents —single-phase modulation | Cdc | 100 1000 | μF μF |

| RL input circuit | Rdc | 8.1 | Ω |

| Ldc | 10.6 | mH | |

| RL load circuit | R | 5.9 | Ω |

| L @f | 25 | mH | |

| L @fsw | 16.5 | mH | |

| RC load circuit | Ro | 17.8 | Ω |

| Co | 111 | μF | |

| Power factor | PF @f | 1 | - |

| Fundamental frequency | f | 50 | Hz |

| Switching frequency | fsw | 4.8 | kHz |

| m | 0 | 0.1 | 0.2 | 0.3 | 0.4 | 0.5 | 0.5774 | |

|---|---|---|---|---|---|---|---|---|

| SPWM, theory | [mV] | 0 | 17.43 | 59.16 | 106.4 | 146.3 | 188.1 | - |

| SPWM, exp | [mV] | 1.791 | 19.07 | 60.05 | 105.7 | 146.5 | 187.7 | - |

| SPWM, error | [mV] | +1.79 | +1.64 | +0.89 | −0.70 | +0.20 | −0.40 | - |

| SPWM, error | % | - | +9.41 | +1.50 | −0.66 | +0.14 | −0.21 | - |

| CPWM, theory | [mV] | 0 | 17.35 | 58.25 | 100.3 | 121.6 | 106.5 | 74.41 |

| CPWM, exp | [mV] | 1.686 | 19.19 | 59.29 | 100.0 | 120.7 | 105.8 | 74.33 |

| CPWM, error | [mV] | +1.70 | +1.85 | +1.05 | −0.30 | −0.90 | −0.70 | −0.11 |

| CPWM, error | % | - | +10.7 | +1.80 | −0.30 | −0.74 | −0.66 | −0.15 |

| m | 0 | 0.1 | 0.2 | 0.3 | 0.4 | 0.5 | 0.6 | 0.7 | 0.8 | 0.9 | 1 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 1ph, theory | [mV] | 0 | 0.6758 | 2.695 | 5.618 | 8.875 | 11.97 | 14.38 | 15.78 | 15.77 | 14.26 | 12.17 |

| 1ph, exp | [mV] | 2.757 | 2.163 | 4.288 | 6.239 | 9.632 | 12.47 | 14.51 | 16.50 | 15.76 | 14.81 | 13.16 |

| 1ph, error | [mV] | +2.76 | +1.49 | +1.59 | +0.62 | +0.76 | +0.50 | +0.13 | +0.72 | −0.01 | +0.55 | +0.99 |

| 1ph, error | % | - | +220 | +59.1 | +11.1 | +8.53 | +4.18 | +0.90 | +4.56 | −0.06 | +3.86 | +8.13 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mandrioli, R.; Viatkin, A.; Hammami, M.; Ricco, M.; Grandi, G. Prediction of DC-Link Voltage Switching Ripple in Three-Phase Four-Leg PWM Inverters. Energies 2021, 14, 1434. https://doi.org/10.3390/en14051434

Mandrioli R, Viatkin A, Hammami M, Ricco M, Grandi G. Prediction of DC-Link Voltage Switching Ripple in Three-Phase Four-Leg PWM Inverters. Energies. 2021; 14(5):1434. https://doi.org/10.3390/en14051434

Chicago/Turabian StyleMandrioli, Riccardo, Aleksandr Viatkin, Manel Hammami, Mattia Ricco, and Gabriele Grandi. 2021. "Prediction of DC-Link Voltage Switching Ripple in Three-Phase Four-Leg PWM Inverters" Energies 14, no. 5: 1434. https://doi.org/10.3390/en14051434

APA StyleMandrioli, R., Viatkin, A., Hammami, M., Ricco, M., & Grandi, G. (2021). Prediction of DC-Link Voltage Switching Ripple in Three-Phase Four-Leg PWM Inverters. Energies, 14(5), 1434. https://doi.org/10.3390/en14051434