Reliability Enhancement of Power IGBTs under Short-Circuit Fault Condition Using Short-Circuit Current Limiting-Based Technique

Abstract

:1. Introduction

- The junction temperature rise is much less than the case without current limiting.

- The converter operation is not interrupted due to the temporary faults.

- The IGBT failure modes in SCF relevant to the peak current can be more easily handled.

2. Proposed Method

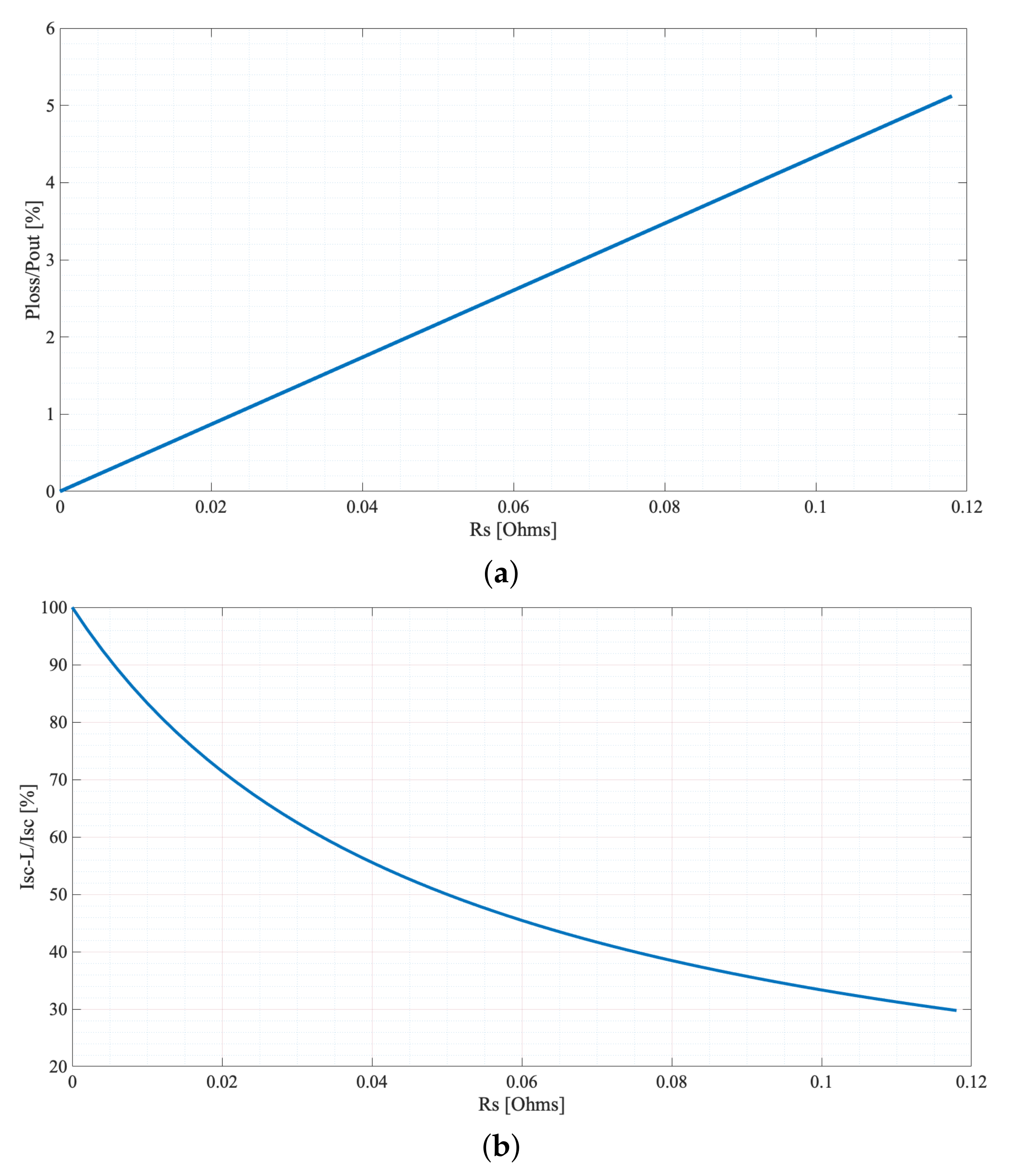

2.1. Limiting SCF Current

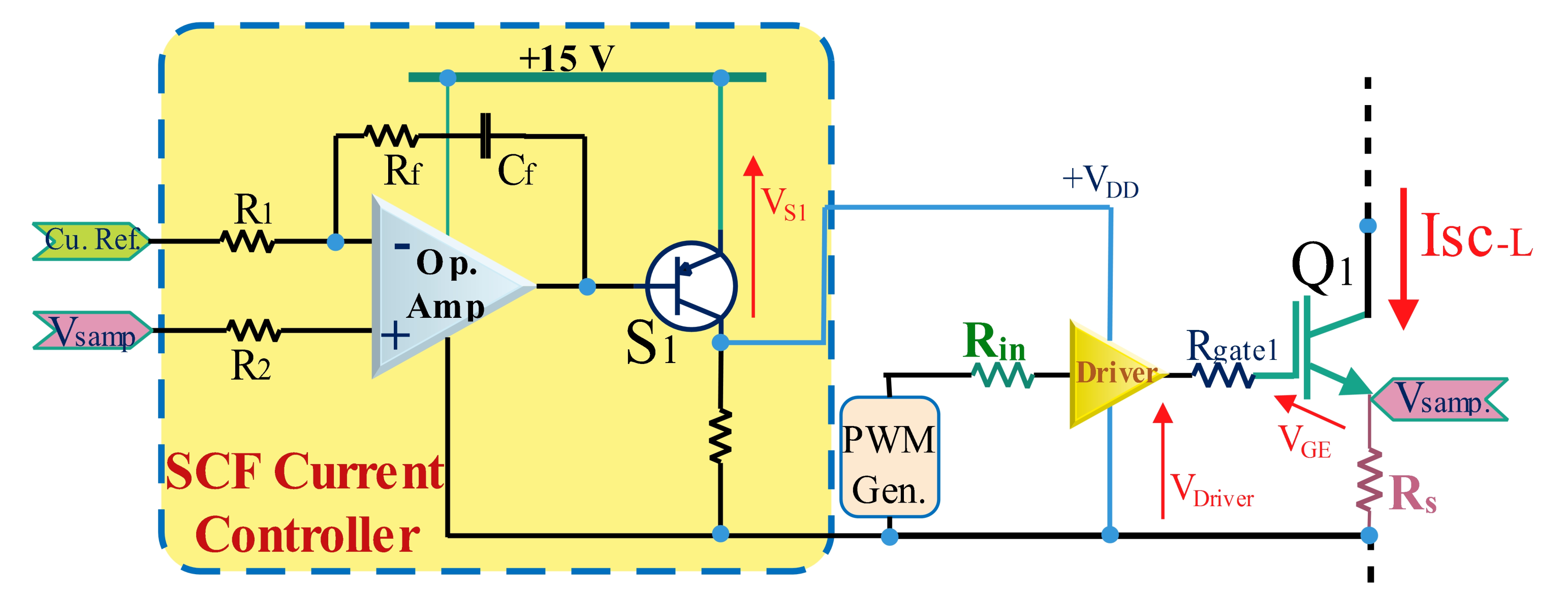

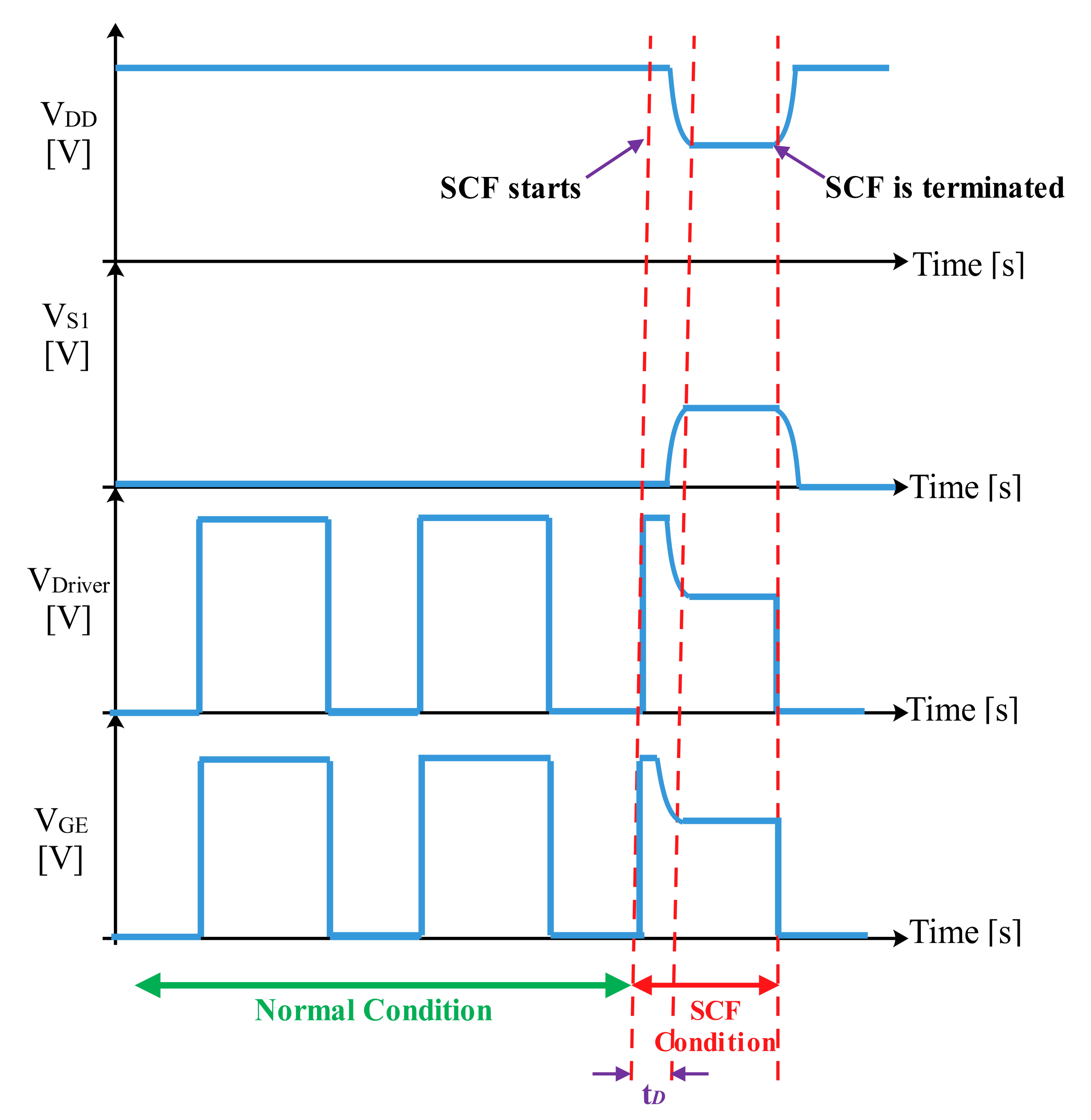

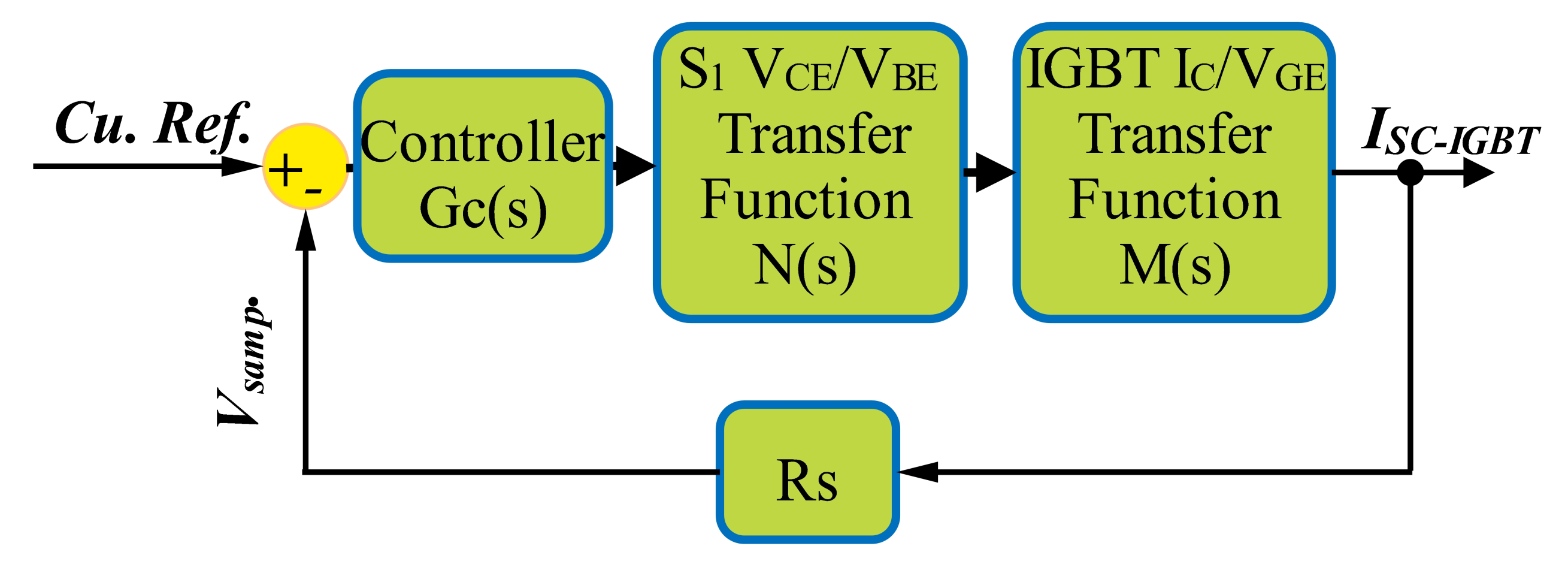

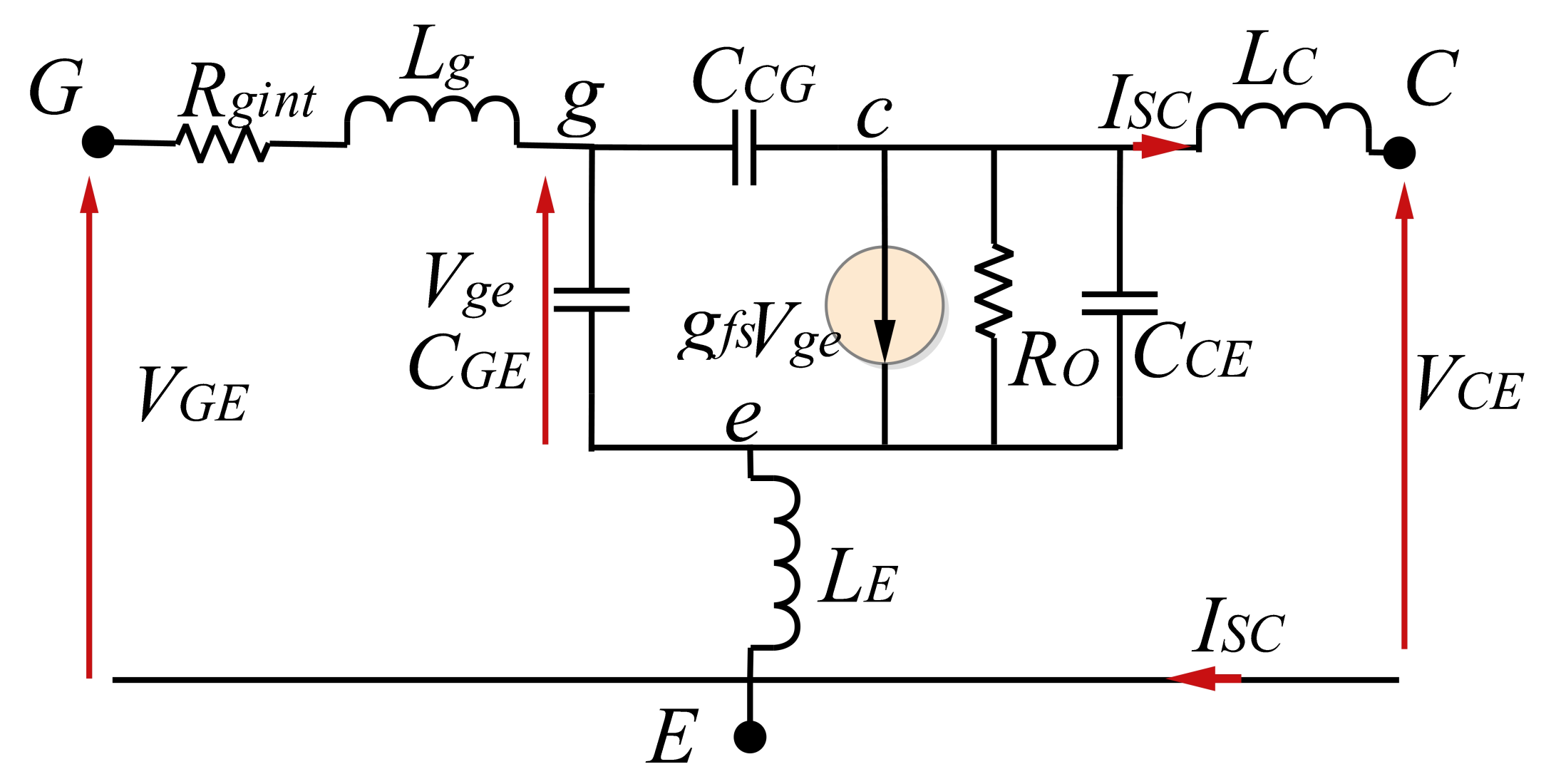

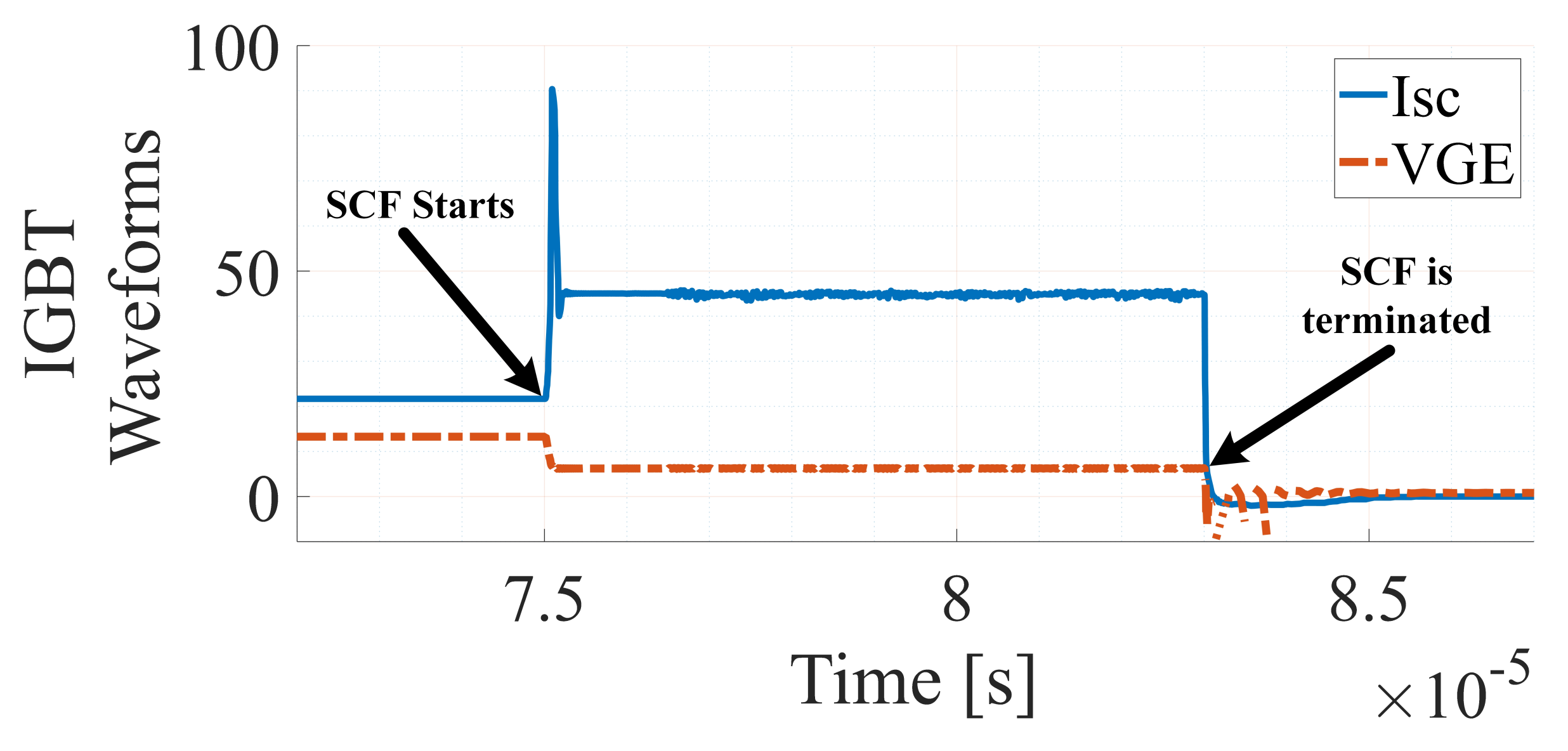

2.2. Controlling SCF Current

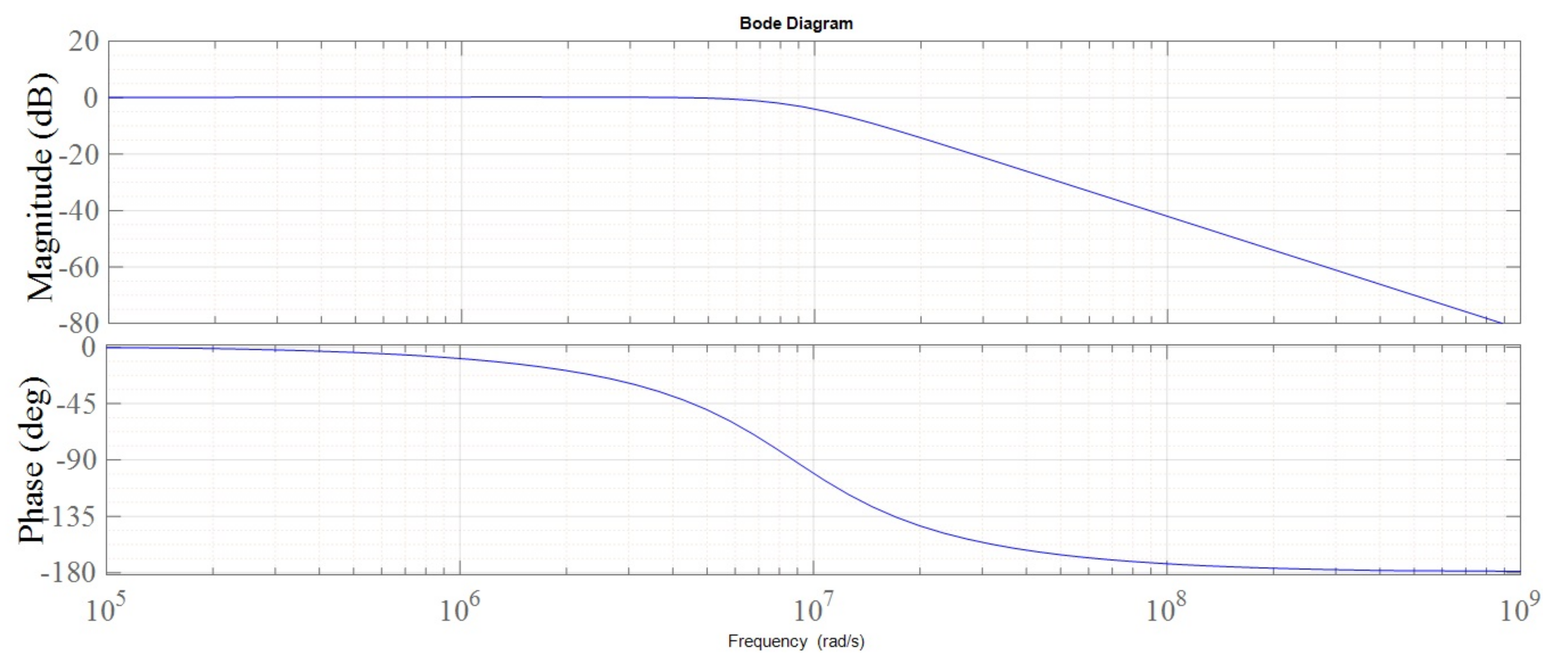

2.3. Stability Analysis

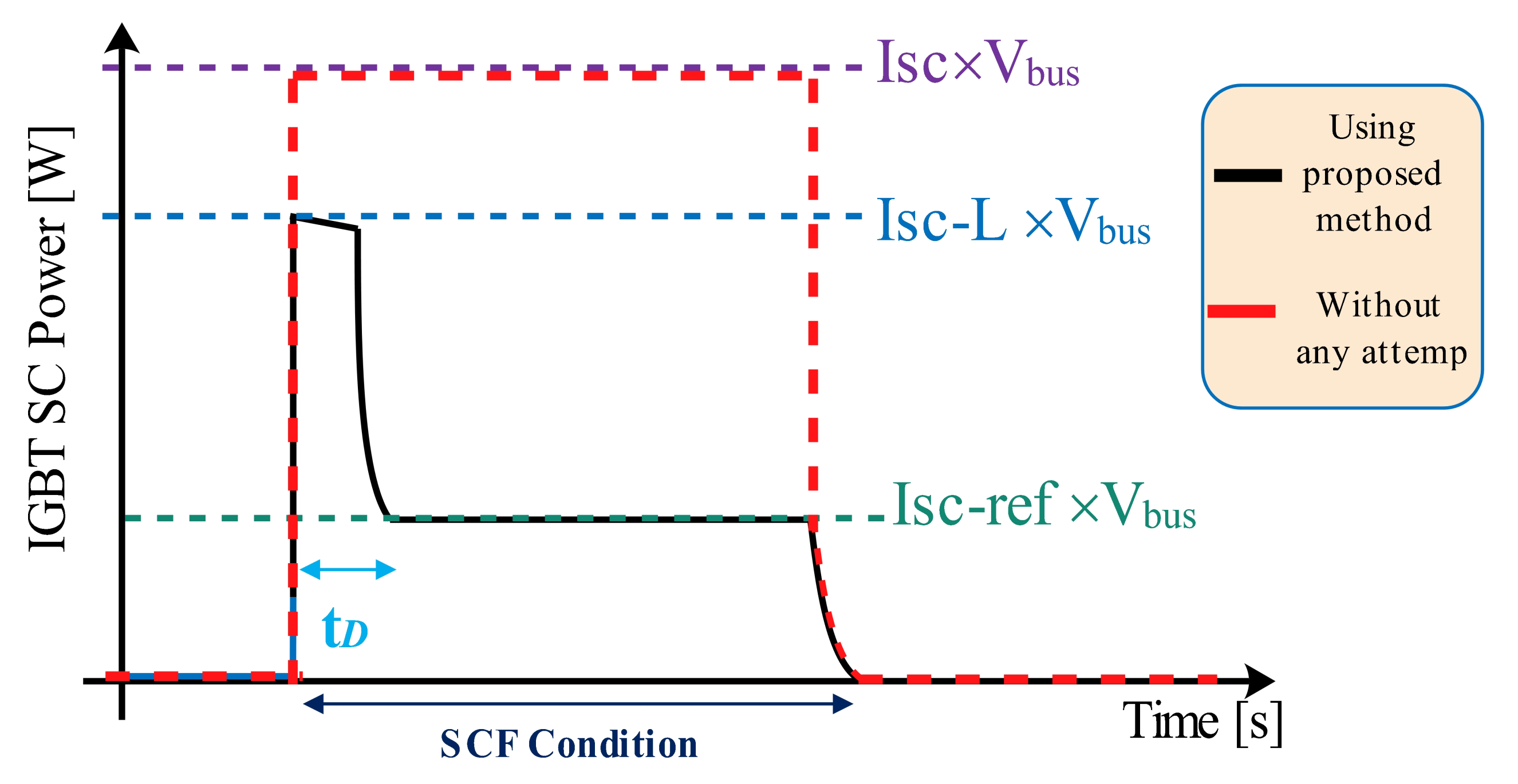

2.4. Short Circuit Energy

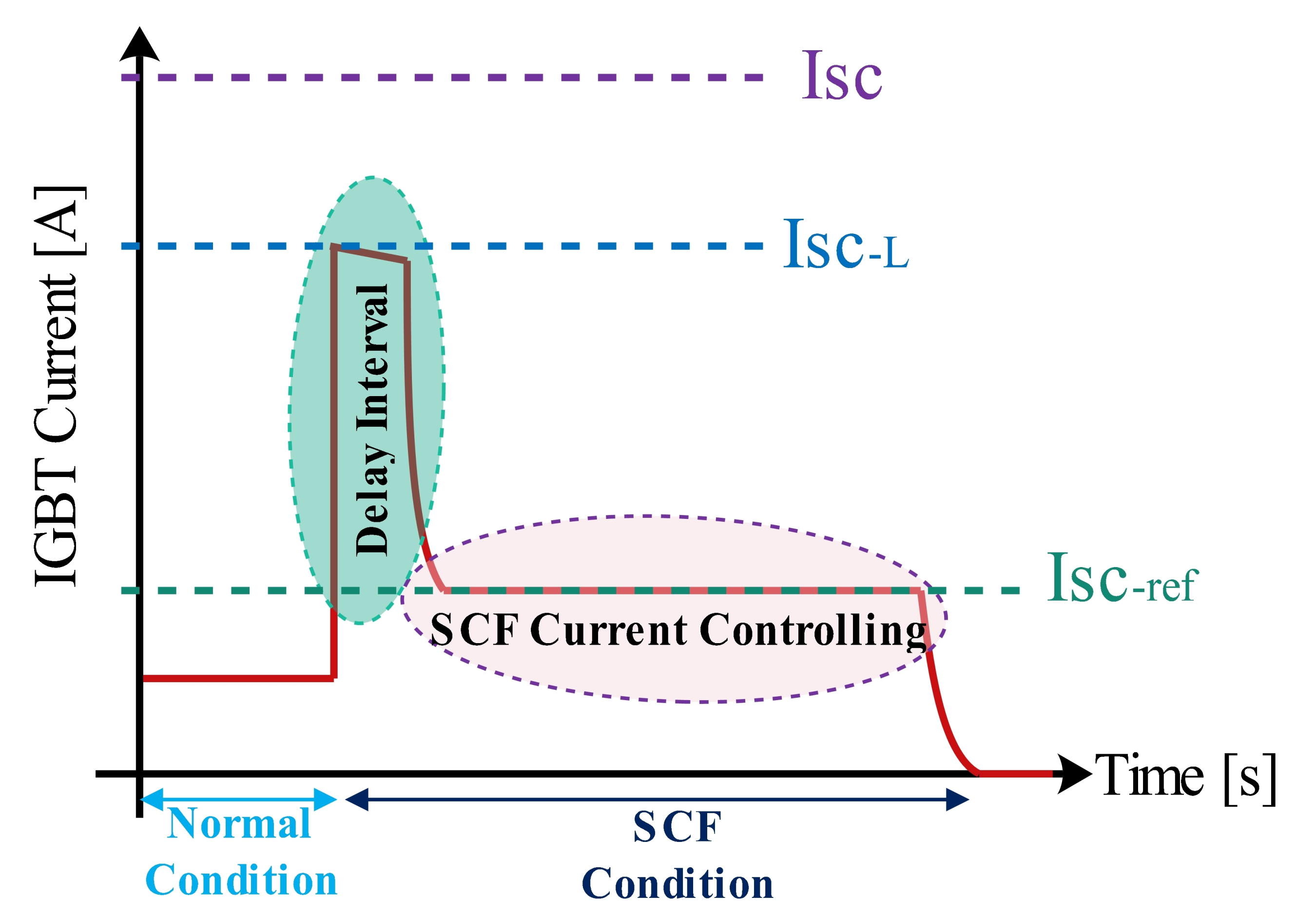

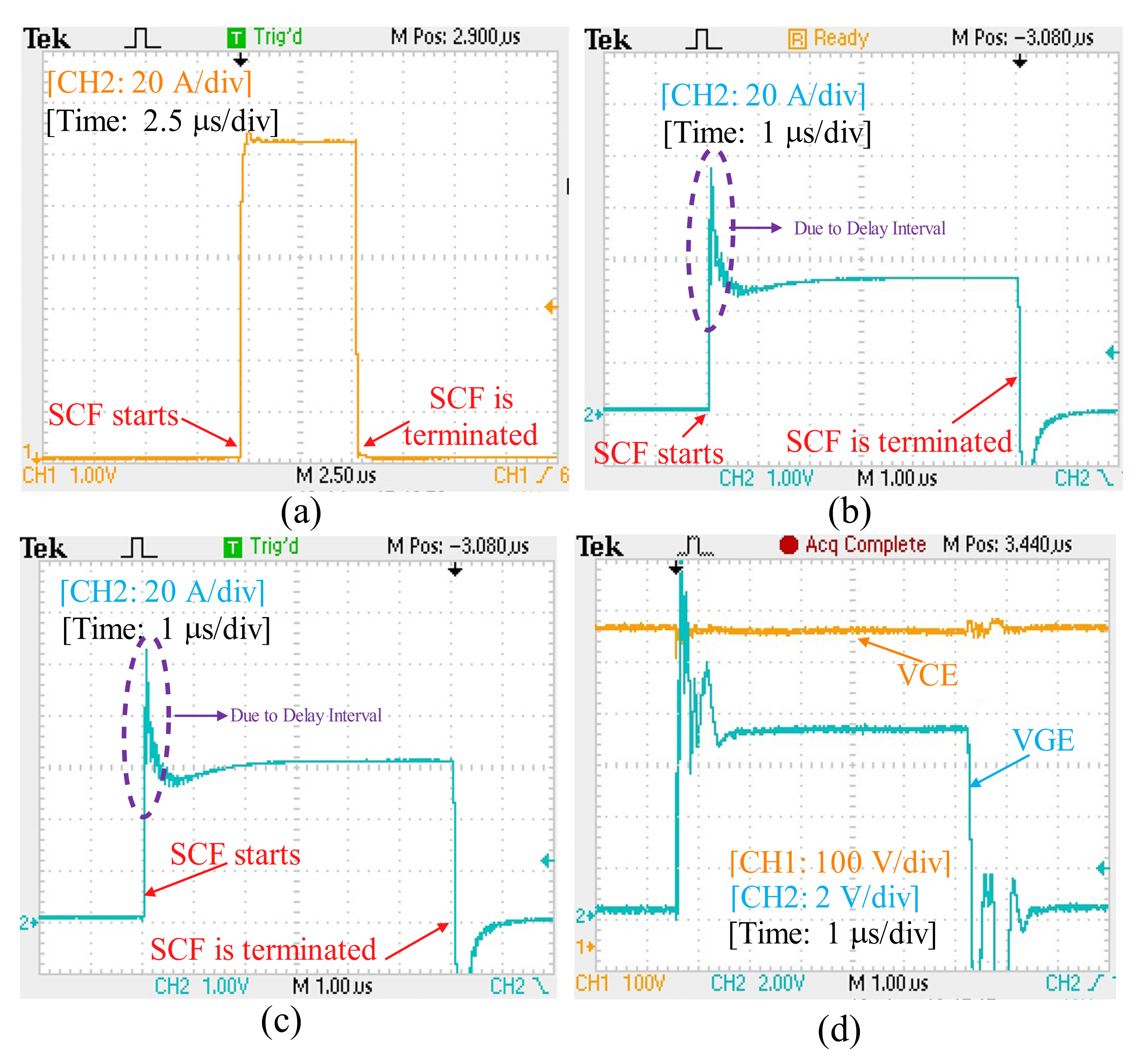

- the first interval is called delay interval (), during which the SCF current is limited to ,

- the second interval is the time duration in which the SCF current is controlled to the value of SCF current controller ().

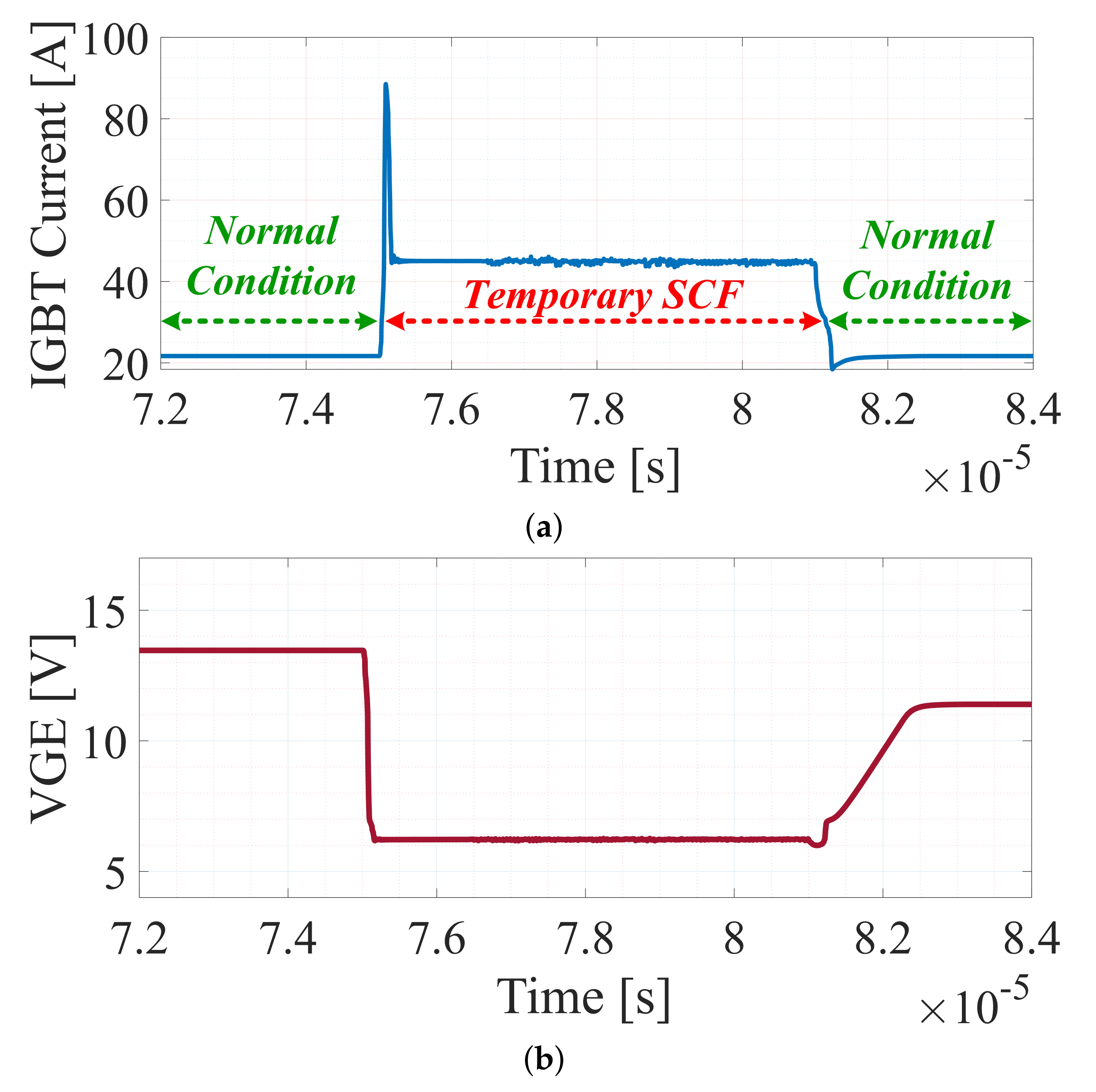

3. Simulation Results

3.1. PSPICE Simulation

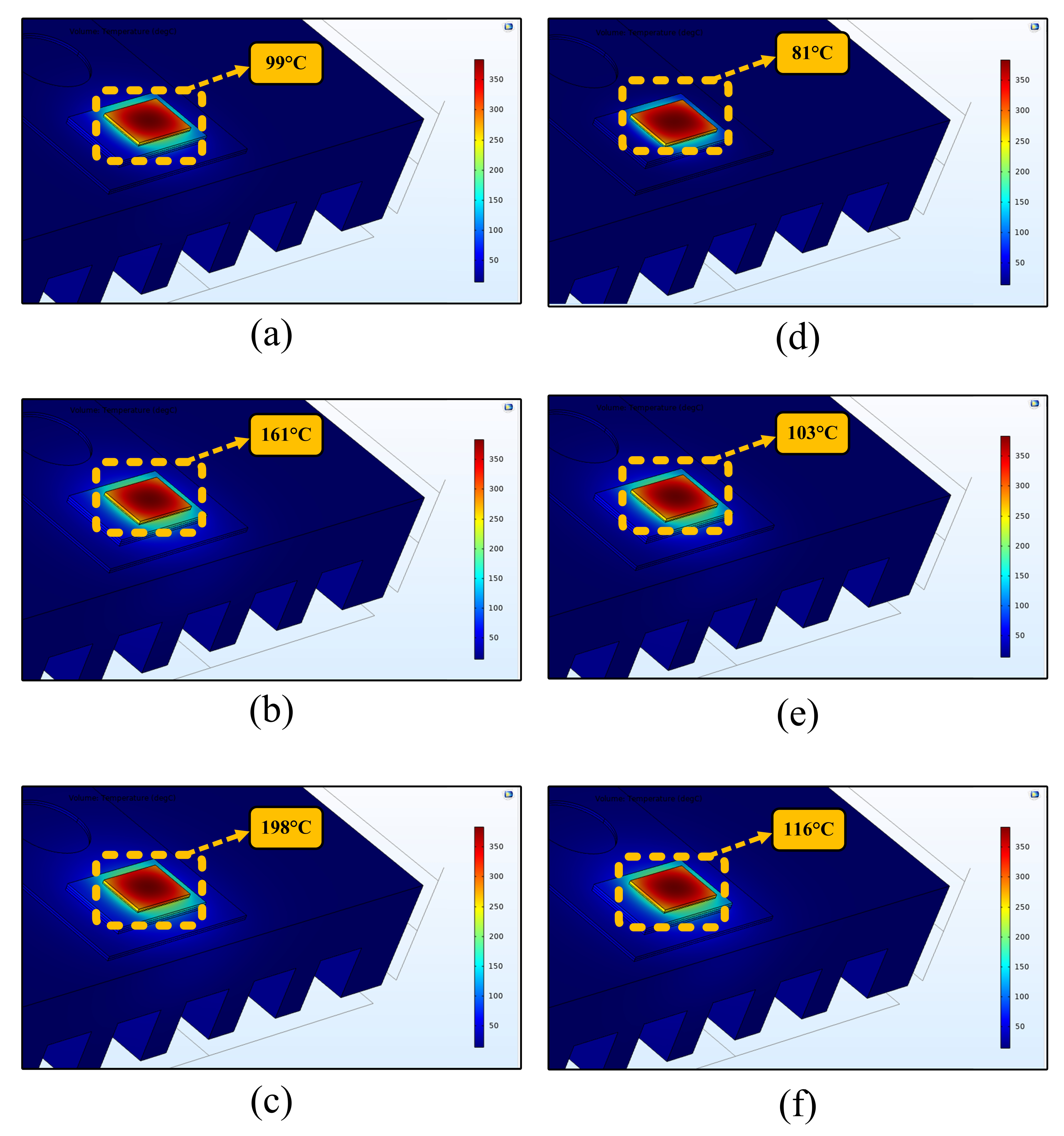

3.2. FEM Simulation

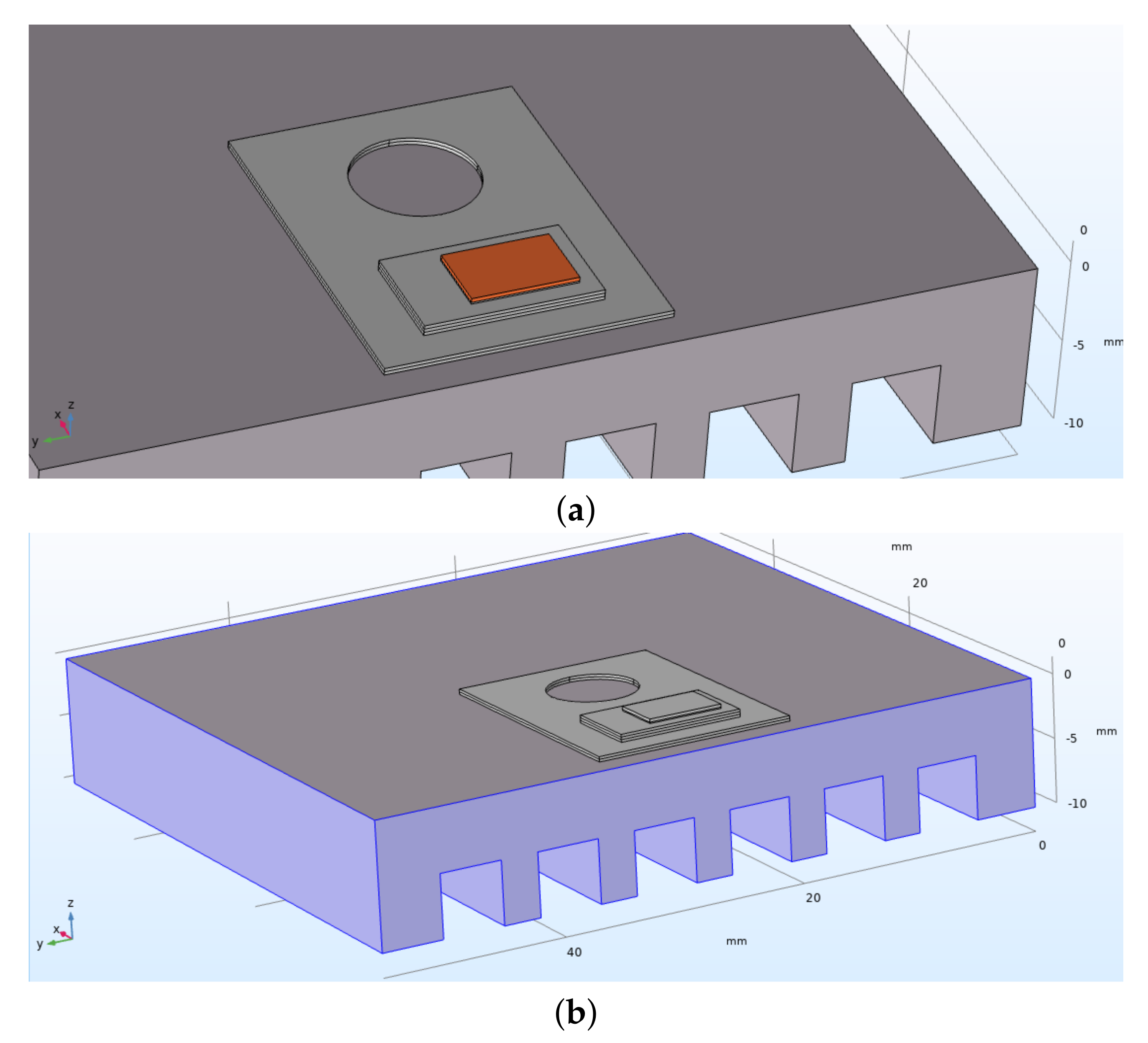

- Boundary Heat Source: The chip area of the switch is considered as a heat source in short circuit condition (see Figure 13a). The value of the heat source is based on short circuit instantaneous power value ().

- Heat flux: The simulated heat-sink on the bottom area of the switch is considered as the area from which the produced heat can be dissipated to the environment (see Figure 13b). Considering the employed heatsink in experimental implementation, the convective heat flux with heat transfer coefficient of 10,000 W/(m) is considered for the heatsink.

- Initial Values: The initial temperature value of the IGBT is considered 75 C. This is the normal operation temperature of the IGBT in the pre-fault condition.

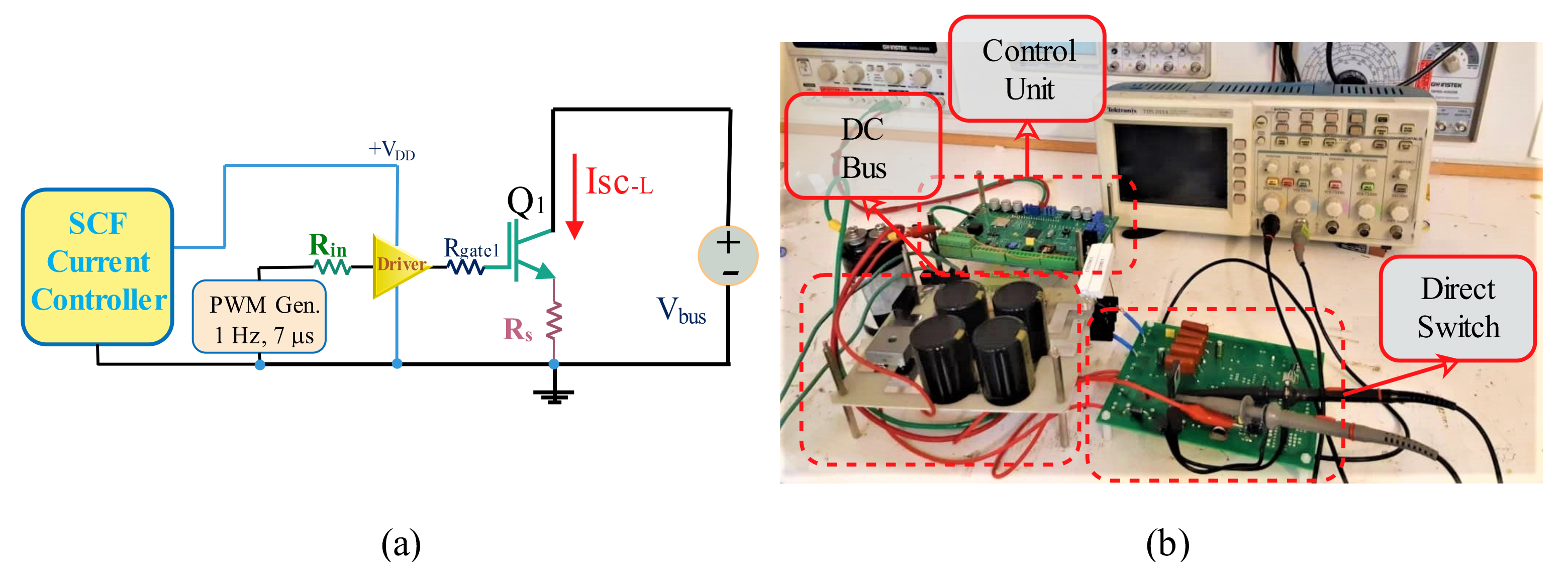

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Dieckerhoff, S.; Bernet, S.; Krug, D. Power loss-oriented evaluation of high voltage IGBTs and multilevel converters in transformerless traction applications. IEEE Trans. Power Electron. 2005, 20, 1328–1336. [Google Scholar]

- Xu, Z.; Li, M.; Wang, F.; Liang, Z. Investigation of Si IGBT Operation at 200∘ C for Traction Applications. IEEE Trans. Power Electron. 2013, 28, 2604–2615. [Google Scholar] [CrossRef]

- Mohsenzade, S.; Zarghani, M.; Kaboli, S. A high-voltage series-stacked IGBT switch with active energy recovery feature for pulsed power applications. IEEE Trans. Ind. Electron. 2019, 67, 3650–3661. [Google Scholar] [CrossRef]

- Zarghani, M.; Mohsenzade, S.; Kaboli, S. A series stacked IGBT switch based on a concentrated clamp mode snubber for pulsed power applications. IEEE Trans. Power Electron. 2019, 34, 9573–9584. [Google Scholar]

- Nasab, J.N.; Hadizade, A.; Mohsenzade, S.; Zarghany, M.; Kaboli, S. A Marx-based generator with adjustable FWHM using a controllable magnetic switch. IEEE Trans. Dielectr. Electr. Insul. 2019, 26, 324–331. [Google Scholar]

- Mohsenzade, S.; Zarghani, M.; Kaboli, S. A Series Stacked IGBT Switch to Be Used as a Fault Current Limiter in HV High Power Supplies. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 6300–6314. [Google Scholar] [CrossRef]

- Mohsenzade, S.; Zarghani, M.; Kaboli, S. A Voltage Balancing Method for Series-Connected IGBTs Operating as a Fault Current Limiter in High-Voltage DC Power Supplies. IEEE Trans. Ind. Electron. 2020, 68, 7895–7907. [Google Scholar] [CrossRef]

- Deng, E.; Wenzel, O.; Zhao, Z.; Zhang, Y.; Ying, X.; Li, J.; Huang, Y. Research on the Multi-Physics Field-Circuit Coupling Model of Press Pack IGBT Considering the Application of Hybrid HVDC Breakers. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 4854–4864. [Google Scholar] [CrossRef]

- Zhang, J.; Liu, J.; Zhong, S.; Yang, J.; Zhao, N.; Zheng, T.Q. A power electronic traction transformer configuration with low-voltage IGBTs for onboard traction application. IEEE Trans. Power Electron. 2018, 34, 8453–8467. [Google Scholar] [CrossRef]

- Zhao, X.; Li, B.; Fu, Q.; Mao, S.; Xu, D.; Leon, J.I.; Franquelo, L.G. DC solid state transformer based on three-level power module for interconnecting MV and LV DC distribution systems. IEEE Trans. Power Electron. 2020, 36, 1563–1577. [Google Scholar] [CrossRef]

- Choi, U.M.; Blaabjerg, F.; Lee, K.B. Study and handling methods of power IGBT module failures in power electronic converter systems. IEEE Trans. Power Electron. 2014, 30, 2517–2533. [Google Scholar] [CrossRef]

- Naghibi, J.; Mehran, K.; Foster, M.P. An Online Failure Assessment Approach for SiC-based MOSFET Power Modules Using Iterative Condition Monitoring Technique. In Proceedings of the 2020 IEEE 21st Workshop on Control and Modeling for Power Electronics (COMPEL), Aalborg, Denmark, 9–12 November 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Harikumaran, J.; Buticchi, G.; Migliazza, G.; Madonna, V.; Giangrande, P.; Costabeber, A.; Wheeler, P.; Galea, M. Failure Modes and Reliability Oriented System Design for Aerospace Power Electronic Converters. IEEE Open J. Ind. Electron. Soc. 2021, 2, 53–64. [Google Scholar] [CrossRef]

- Chokhawala, R.S.; Catt, J.; Kiraly, L. A discussion on IGBT short-circuit behavior and fault protection schemes. IEEE Trans. Ind. Appl. 1995, 31, 256–263. [Google Scholar]

- Mohsenzade, S.; Zarghany, M.; Kaboli, S. A series stacked IGBT switch with robustness against short-circuit fault for pulsed power applications. IEEE Trans. Power Electron. 2017, 33, 3779–3790. [Google Scholar]

- Wu, R.; Blaabjerg, F.; Wang, H.; Liserre, M.; Iannuzzo, F. Catastrophic failure and fault-tolerant design of IGBT power electronic converters-an overview. In Proceedings of the IECON 2013—39th Annual Conference of the IEEE Industrial Electronics Society, Vienna, Austria, 10–13 November 2013; pp. 507–513. [Google Scholar]

- Reigosa, P.D.; Iannuzzo, F.; Rahimo, M.; Corvasce, C.; Blaabjerg, F. Improving the short-circuit reliability in IGBTs: How to mitigate oscillations. IEEE Trans. Power Electron. 2017, 33, 5603–5612. [Google Scholar] [CrossRef] [Green Version]

- Abbate, C.; Busatto, G.; Sanseverino, A.; Velardi, F.; Ronsisvalle, C. Analysis of low-and high-frequency oscillations in IGBTs during turn-on short circuit. IEEE Trans. Electron Devices 2015, 62, 2952–2958. [Google Scholar] [CrossRef]

- Lutz, J.; Basler, T. Short-circuit ruggedness of high-voltage IGBTs. In Proceedings of the 2012 28th International Conference on Microelectronics Proceedings, Nis, Serbia, 13–16 May 2012; pp. 243–250. [Google Scholar]

- Otsuki, M.; Onozawa, Y.; Kanemaru, H.; Seki, Y.; Matsumoto, T. A study on the short-circuit capability of field-stop IGBTs. IEEE Trans. Electron Devices 2003, 50, 1525–1531. [Google Scholar] [CrossRef]

- Yang, F.; Tan, J.; Lu, S.; Zhu, Y. Investigation on the robustness during short-circuit turn-off and its tradeoff characteristics with performance in IGBTs. IEEE Trans. Electron Devices 2017, 64, 3293–3297. [Google Scholar]

- Basler, T.; Bhojani, R.; Lutz, J.; Jakob, R. Measurement of a complete HV IGBT IV-characteristic up to the breakdown point. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–9. [Google Scholar]

- Basler, T.; Bhojani, R.; Lutz, J.; Jakob, R. Dynamic self-clamping at short-circuit turn-off of high-voltage IGBTs. In Proceedings of the 2013 25th International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Kanazawa, Japan, 26–30 May 2013; pp. 277–280. [Google Scholar]

- Kopta, A.; Rahimo, M.; Schlapbach, U.; Kaminski, N.; Silber, D. Limitation of the short-circuit ruggedness of high-voltage IGBTs. Proceeding of the 2009 21st International Symposium on Power Semiconductor Devices & IC’s, Barcelona, Spain, 14–18 June 2009; pp. 33–36. [Google Scholar]

- Muller, A.; Pfirsch, F.; Silber, D. Trench IGBT behaviour near to latch-up conditions. In Proceedings of the ISPSD’05—the 17th International Symposium on Power Semiconductor Devices and ICs, Santa Barbara, CA, USA, 23–26 May 2005; pp. 255–258. [Google Scholar]

- Reigosa, P.D.; Iannuzzo, F.; Corvasce, C.; Rahimo, M. Modeling of IGBT With High Bipolar Gain for Mitigating Gate Voltage Oscillations During Short Circuit. IEEE J. Emerg. Sel. Top. Power Electron. 2019, 7, 1584–1592. [Google Scholar]

- Spirito, P.; Maresca, L.; Riccio, M.; Breglio, G.; Irace, A.; Napoli, E. Effect of the collector design on the IGBT avalanche ruggedness: A comparative analysis between punch-through and field-stop devices. IEEE Trans. Electron Devices 2015, 62, 2535–2541. [Google Scholar] [CrossRef] [Green Version]

- Voss, S.; Schulze, H.J.; Niedernostheide, F.J. Optimization of the temperature dependence of the anode-side current gain of IGBTs by field-stop design. In Proceedings of the 2010 22nd International Symposium on Power Semiconductor Devices & IC’s (ISPSD), Hiroshima, Japan, 6–10 June 2010; pp. 141–144. [Google Scholar]

- Chen, Y.; Li, W.; Iannuzzo, F.; Luo, H.; He, X.; Blaabjerg, F. Investigation and classification of short-circuit failure modes based on three-dimensional safe operating area for high-power IGBT modules. IEEE Trans. Power Electron. 2017, 33, 1075–1086. [Google Scholar]

- John, V.; Suh, B.S.; Lipo, T.A. Fast-clamped short-circuit protection of IGBT’s. IEEE Trans. Ind. Appl. 1999, 35, 477–486. [Google Scholar] [CrossRef]

- Chen, M.; Xu, D.; Zhang, X.; Zhu, N.; Wu, J.; Rajashekara, K. An improved IGBT short-circuit protection method with self-adaptive blanking circuit based on V CE measurement. IEEE Trans. Power Electron. 2017, 33, 6126–6136. [Google Scholar] [CrossRef]

- Sathik, M.H.M.; Sundararajan, P.; Sasongko, F.; Pou, J.; Vaiyapuri, V. Short Circuit Detection and Fault Current Limiting Method for IGBTs. IEEE Trans. Device Mater. Reliab. 2020, 20, 686–693. [Google Scholar] [CrossRef]

- Wang, Z.; Shi, X.; Tolbert, L.M.; Wang, F.; Blalock, B.J. A di/dt feedback-based active gate driver for smart switching and fast overcurrent protection of IGBT modules. IEEE Trans. Power Electron. 2013, 29, 3720–3732. [Google Scholar] [CrossRef]

- Oinonen, M.; Laitinen, M.; Kyyrä, J. Current measurement and short-circuit protection of an IGBT based on module parasitics. In Proceedings of the 2014 16th European Conference on Power Electronics and Applications, Lappeenranta, Finland, 26–28 August 2014; pp. 1–9. [Google Scholar]

- Radun, A. An alternative low-cost current-sensing scheme for high-current power electronics circuits. IEEE Trans. Ind. Electron. 1995, 42, 78–84. [Google Scholar]

- Ammous, A.; Allard, B.; Morel, H. Transient temperature measurements and modeling of IGBT’s under short circuit. IEEE Trans. Power Electron. 1998, 13, 12–25. [Google Scholar]

- Lobsiger, Y.; Kolar, J.W. Closed-Loop di/dt and dv/dt IGBT Gate Driver. IEEE Trans. Power Electron. 2014, 30, 3402–3417. [Google Scholar] [CrossRef]

- Yang, X.; Yuan, Y.; Long, Z.; Goncalves, J.; Palmer, P.R. Robust stability analysis of active voltage control for high-power IGBT switching by Kharitonov’s theorem. IEEE Trans. Power Electron. 2015, 31, 2584–2595. [Google Scholar] [CrossRef]

- Infineon Technologies. Highspeed Duo-Pack IGBT, IKW40N120H3, 1200 V, 40 A, PG-TO247-3 Package. 2014. Available online: https://www.infineon.com/cms/en/product/power/igbt/igbt-discretes/ikw40n120h3/ (accessed on 30 July 2021).

| Parameter | Value |

|---|---|

| IGBT Part Number | IKW40N120H3 |

| Nominal Current | 30 A |

| 20 S | |

| 5.5 V | |

| 15 V | |

| Maximum SC Current | 160 A |

| 1000 W |

| Parameter | Value |

|---|---|

| 20 S | |

| 0.05 | |

| 55 pF | |

| 72 pF | |

| 3.8 pF | |

| 15 | |

| 55 | |

| 30 nH | |

| 20 nH | |

| 15 nH |

| IGBT part number | IKW40N120H3 |

| Gate driver IC | LM5111 |

| Op. Amp IC | LM7171 |

| Nominal Current | 22 A |

| Blocking Voltage | 600 V |

| 15 V | |

| 0.05 |

| Material | Thermal Conductivity | Heat Capacity | Density |

|---|---|---|---|

| [] | [] | [] | |

| Aluminium (Al) | 239 | 910 | 2699 |

| Copper (Cu) | 385 | 380 | 180 |

| Silicon (Si) | 131 | 700 | 2330 |

| Solder (SnAgCu) | 60 | 160 | 7400 |

| Ceramic (AlO) | 27 | 776 | 3900 |

| Epoxy Mold | 0.3 | 900 | 1250 |

| Parameter | Value |

|---|---|

| 200 ns | |

| 600 V | |

| 160 A | |

| 95 A | |

| 45 A | |

| 7 s |

| Feature/Item | [15] | [30,31] | [33,34] | [6] | [7] | Proposed Method |

|---|---|---|---|---|---|---|

| Delay | 200 ns | 1∼5 s | Less than 100 ns | 200 ns | 300 ns | 200 ns |

| SC Current limiting | Yes | No | No | Yes | Yes | Yes |

| SC Current controlling | No | No | No | No | Yes | Yes |

| Effects on normal operation | No | No | No | No | Yes | No |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mohsenzade, S.; Naghibi, J.; Mehran, K. Reliability Enhancement of Power IGBTs under Short-Circuit Fault Condition Using Short-Circuit Current Limiting-Based Technique. Energies 2021, 14, 7397. https://doi.org/10.3390/en14217397

Mohsenzade S, Naghibi J, Mehran K. Reliability Enhancement of Power IGBTs under Short-Circuit Fault Condition Using Short-Circuit Current Limiting-Based Technique. Energies. 2021; 14(21):7397. https://doi.org/10.3390/en14217397

Chicago/Turabian StyleMohsenzade, Sadegh, Javad Naghibi, and Kamyar Mehran. 2021. "Reliability Enhancement of Power IGBTs under Short-Circuit Fault Condition Using Short-Circuit Current Limiting-Based Technique" Energies 14, no. 21: 7397. https://doi.org/10.3390/en14217397

APA StyleMohsenzade, S., Naghibi, J., & Mehran, K. (2021). Reliability Enhancement of Power IGBTs under Short-Circuit Fault Condition Using Short-Circuit Current Limiting-Based Technique. Energies, 14(21), 7397. https://doi.org/10.3390/en14217397