Transformer-Less Switched-Capacitor Quasi-Switched Boost DC-DC Converter

Abstract

:1. Introduction

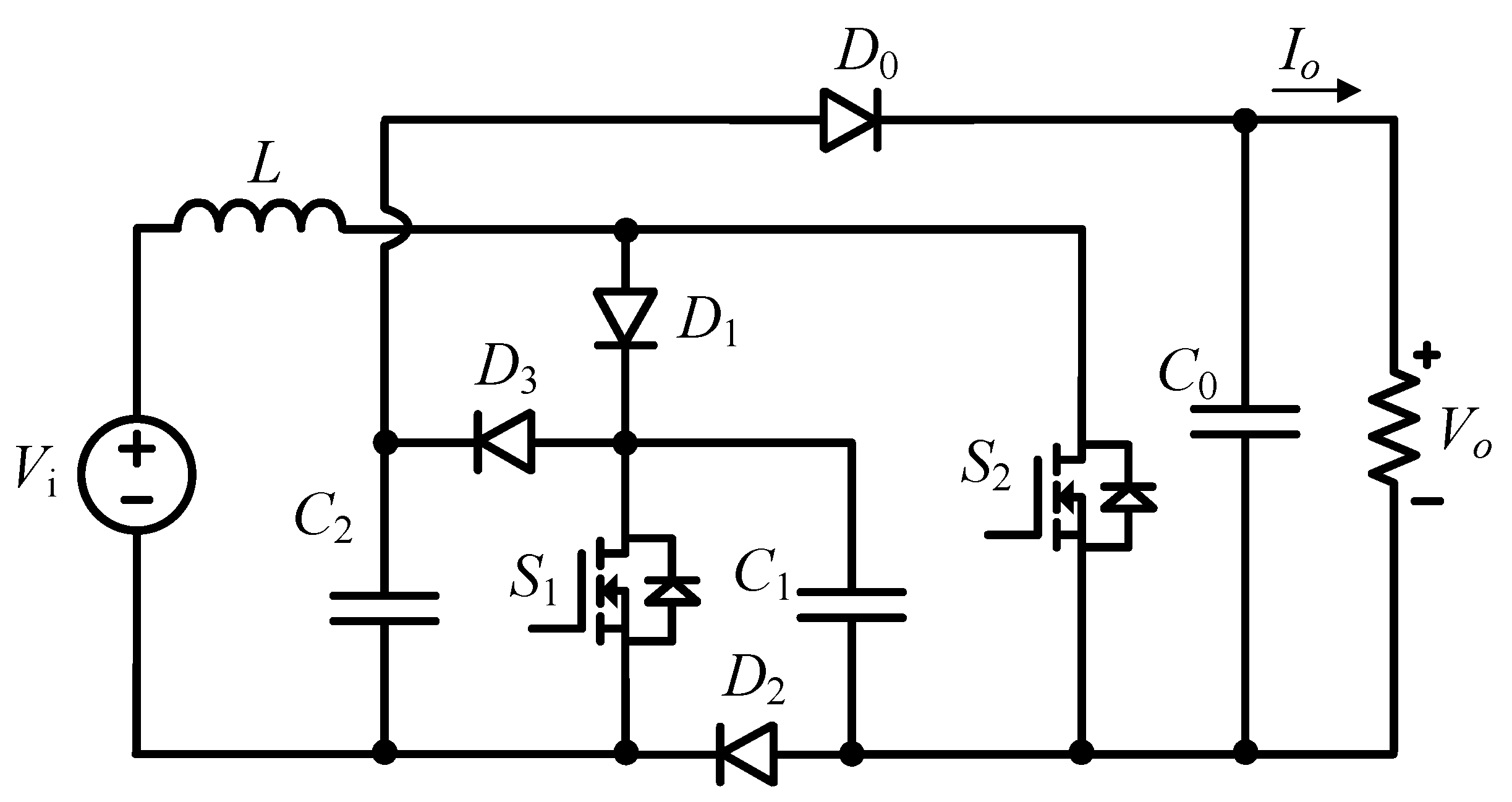

2. Operating Principle of Proposed SCQSBC

2.1. Power Circuit

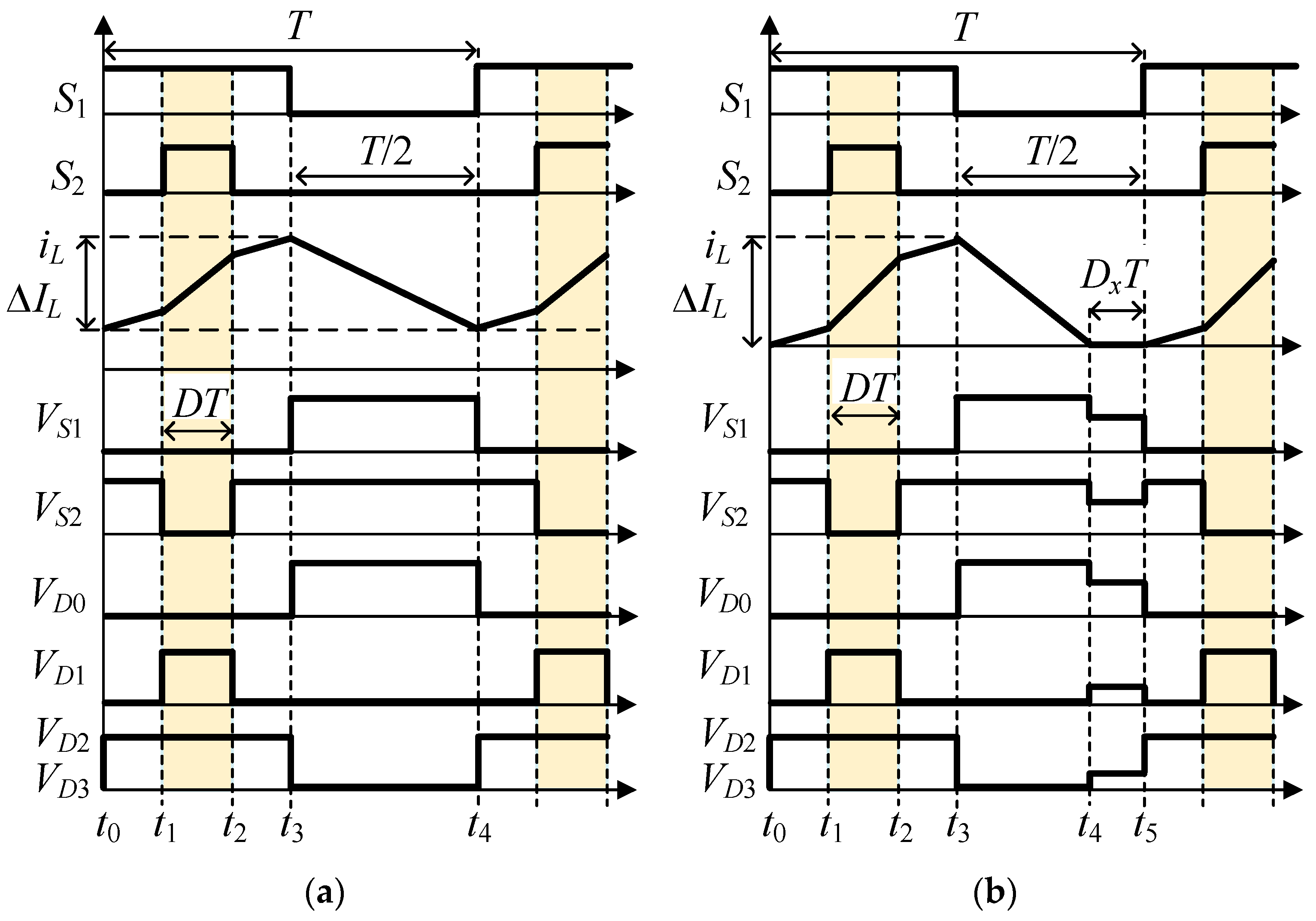

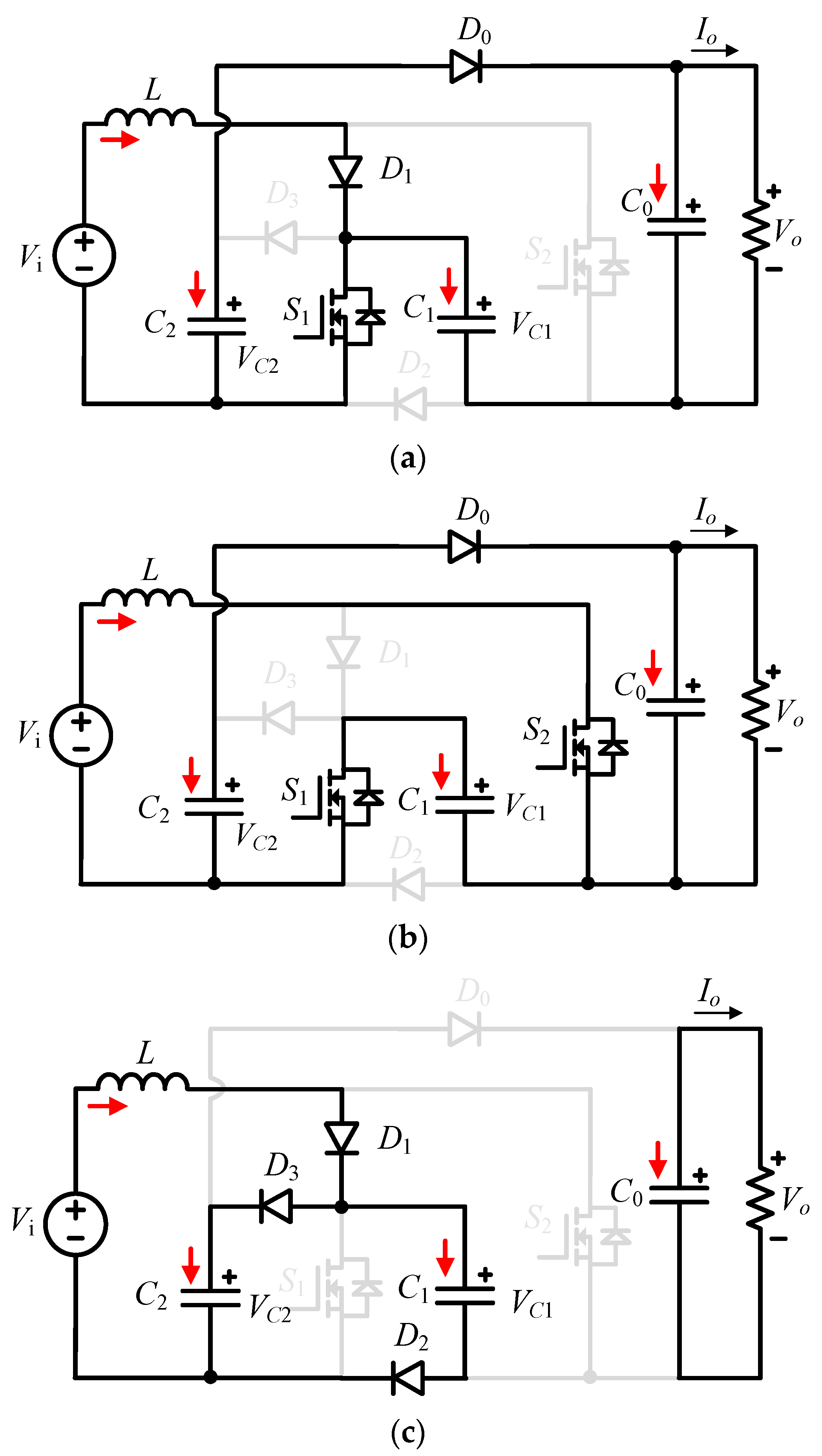

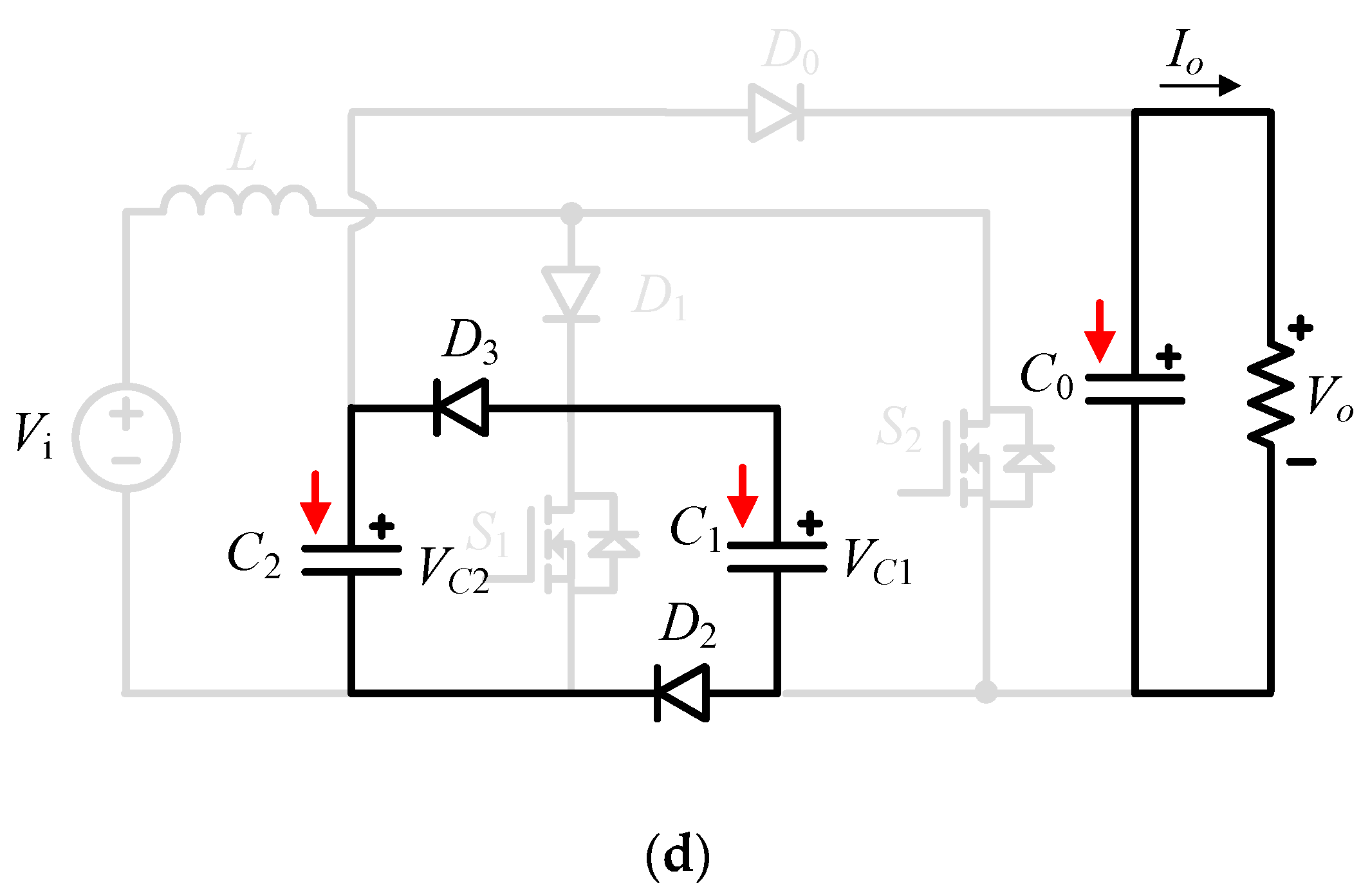

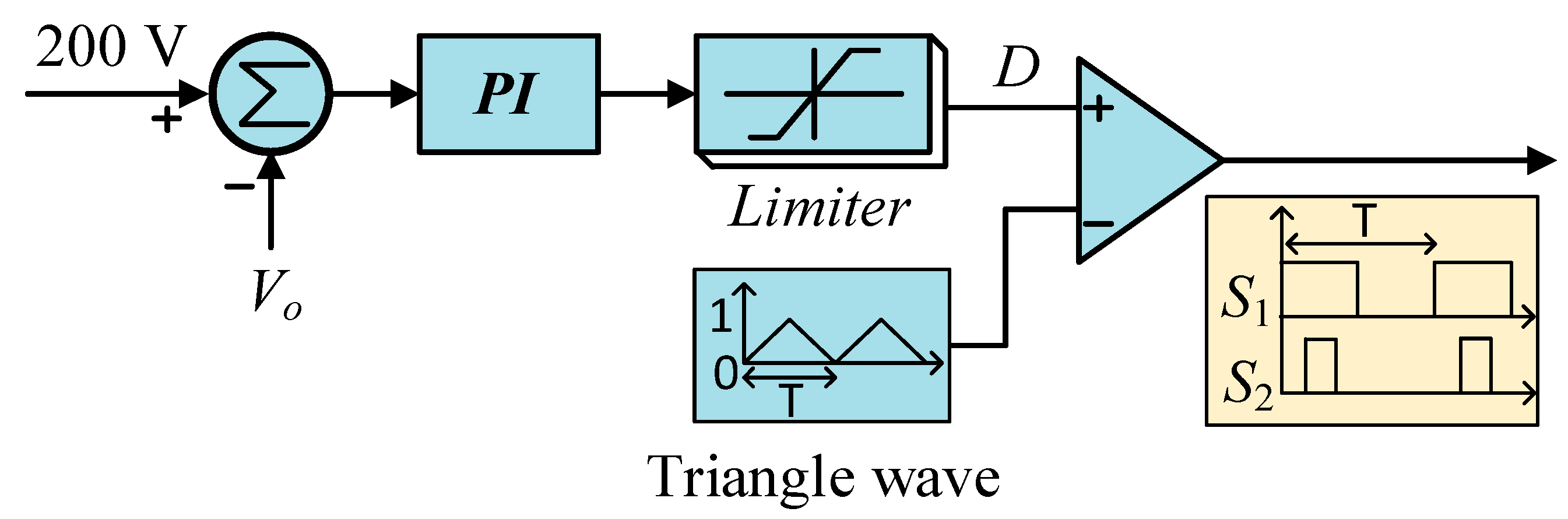

2.2. Circuit Analysis in CCM

2.3. Circuit Analysis in DCM

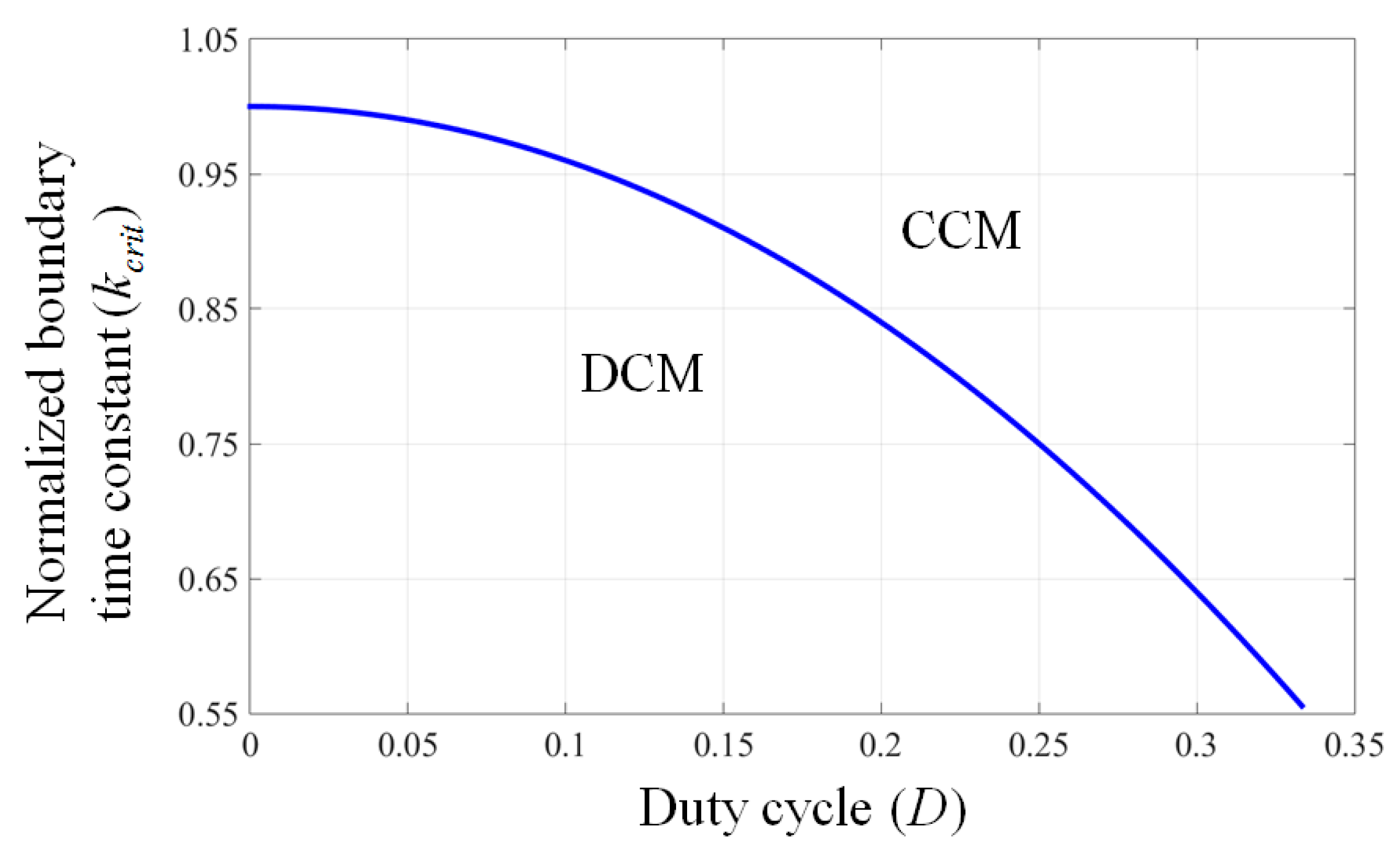

3. Designed Guideline

3.1. Selection of Inductor

3.2. Selection of Capacitors

3.3. Selection of Switching Components

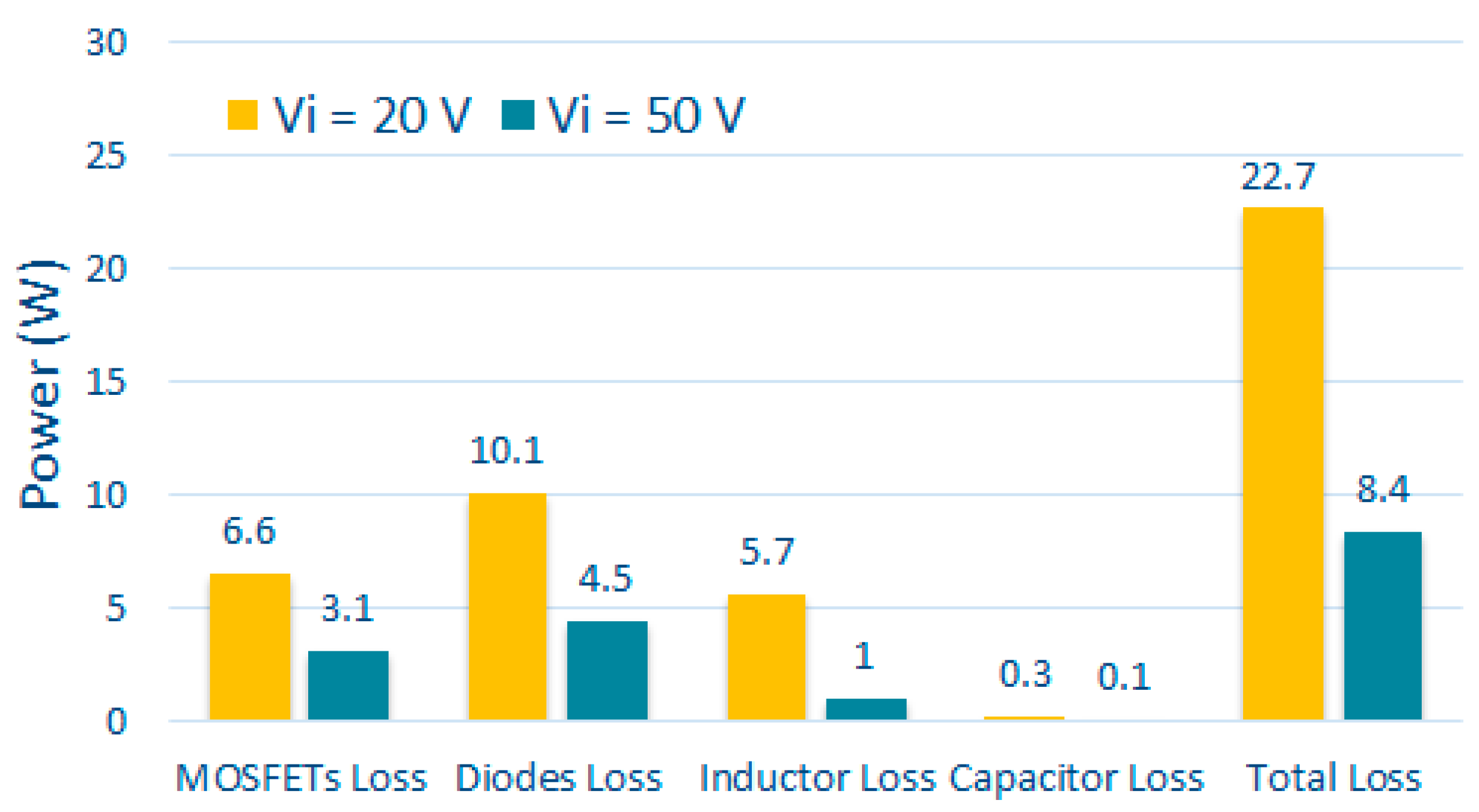

3.4. Power Loss Analysis

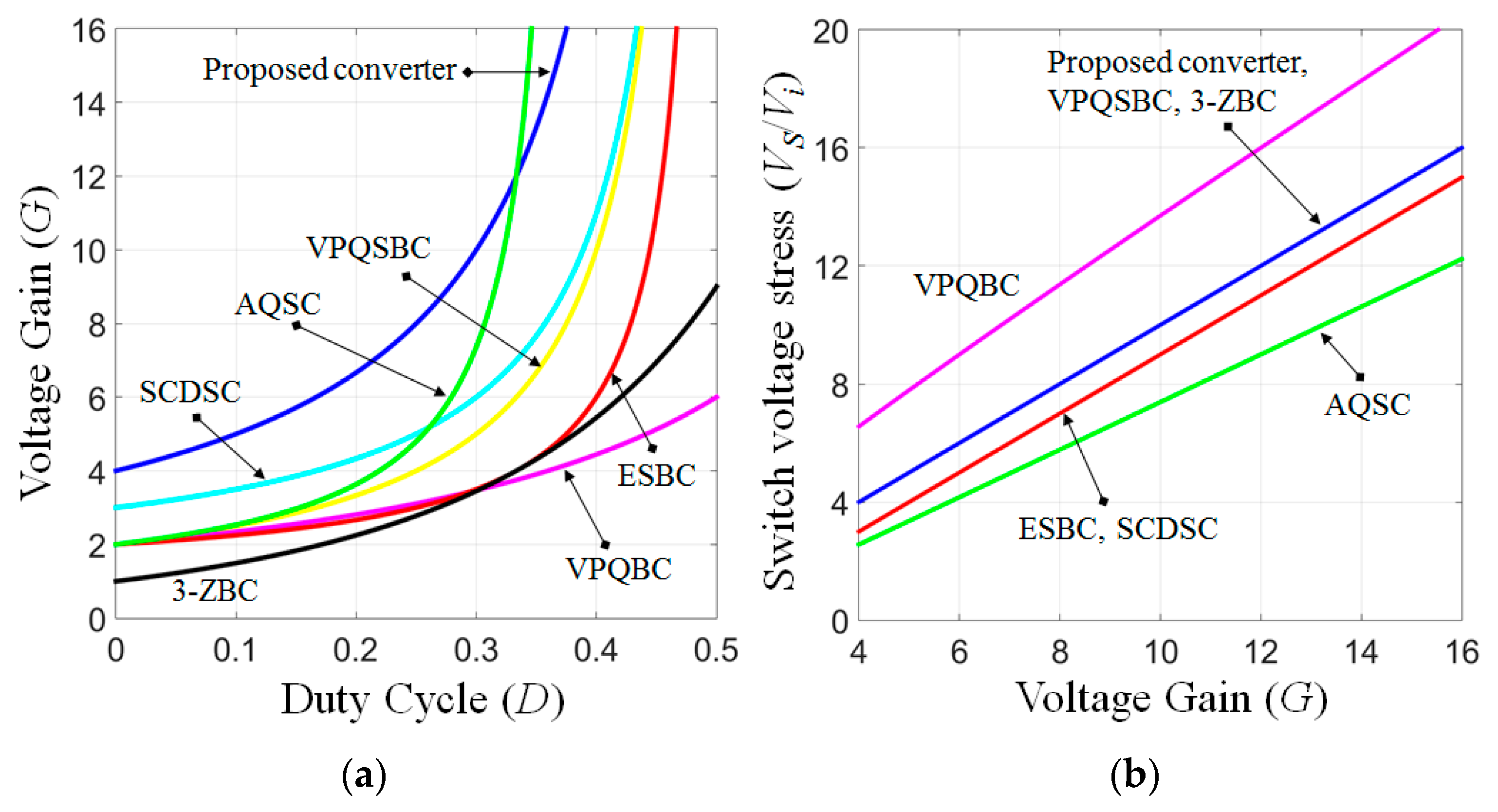

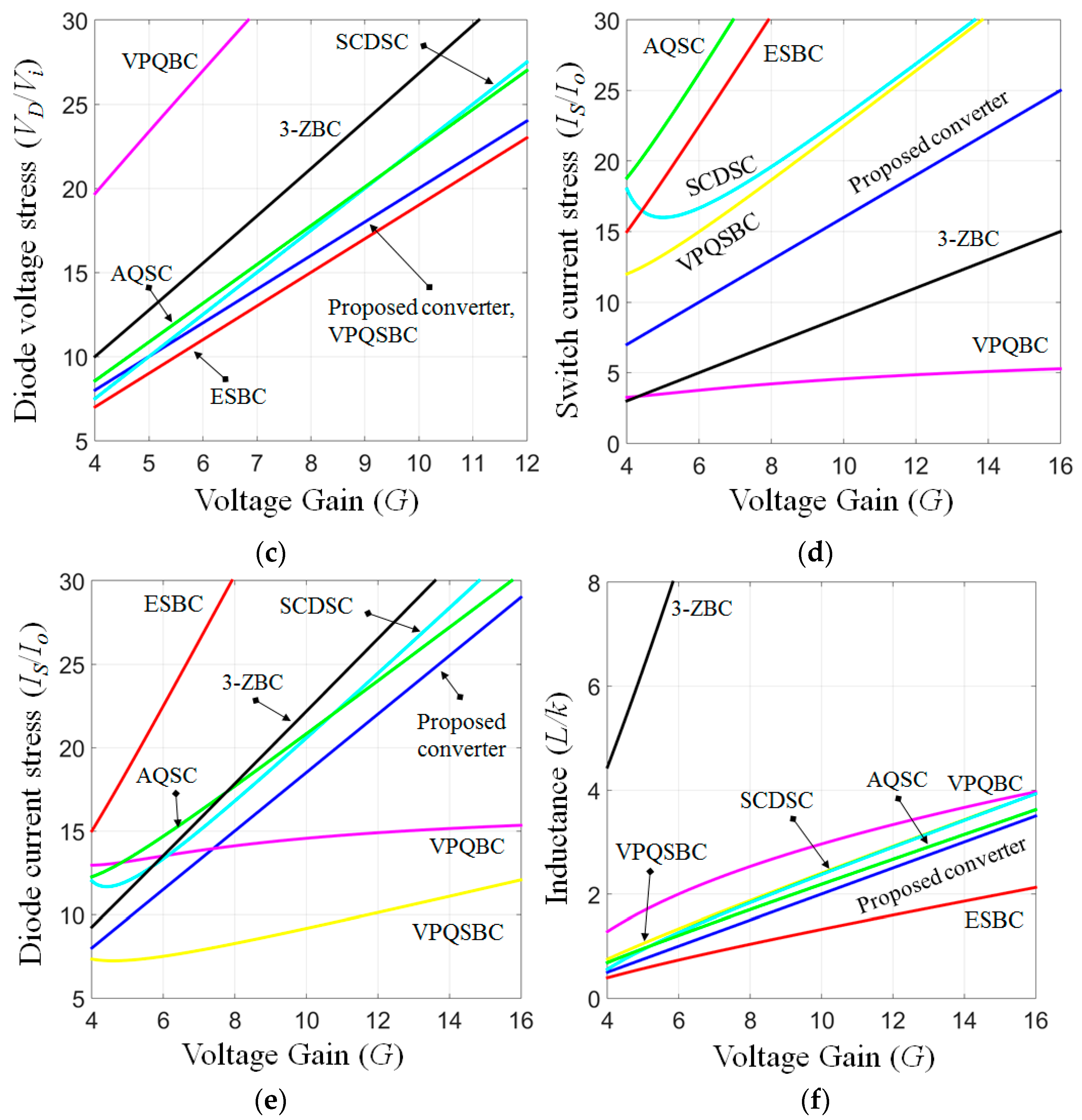

4. Comparison with Other High Gain DC-DC Converter

4.1. Voltage Gain and Count of Device Comparison

4.2. Voltage and Current Stress Comparison

4.3. Input Current and Inductor Current Ripple Comparison

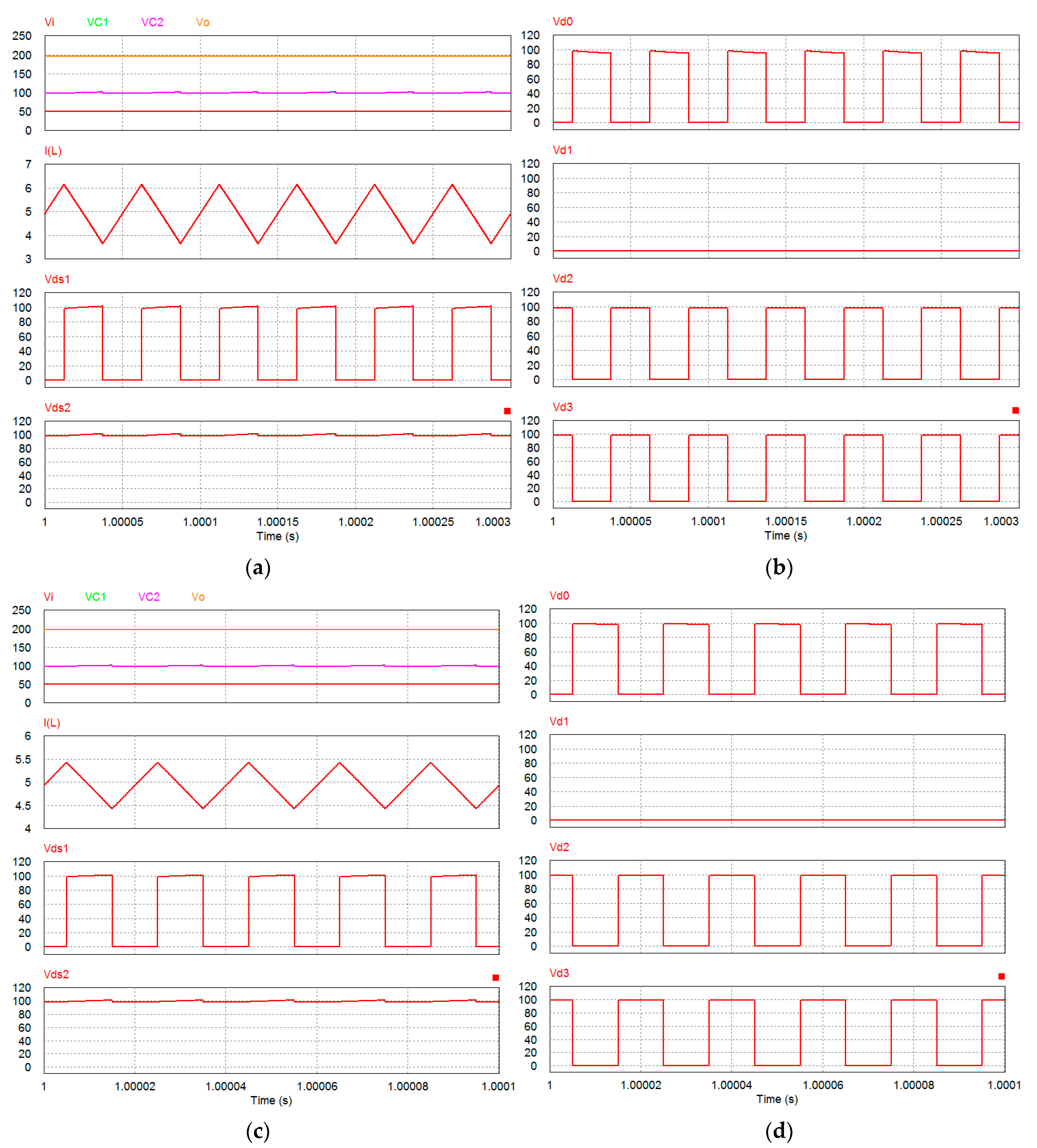

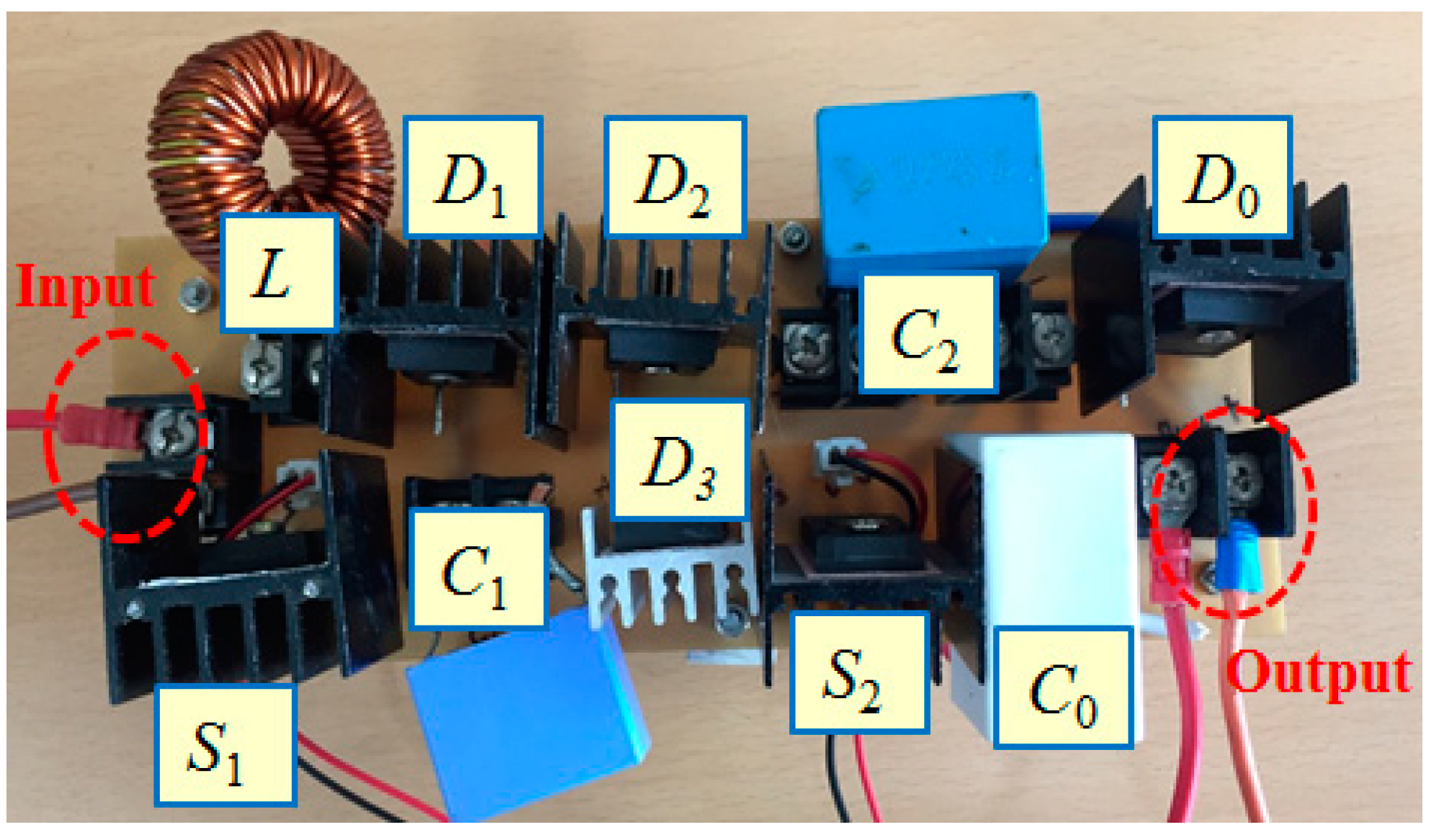

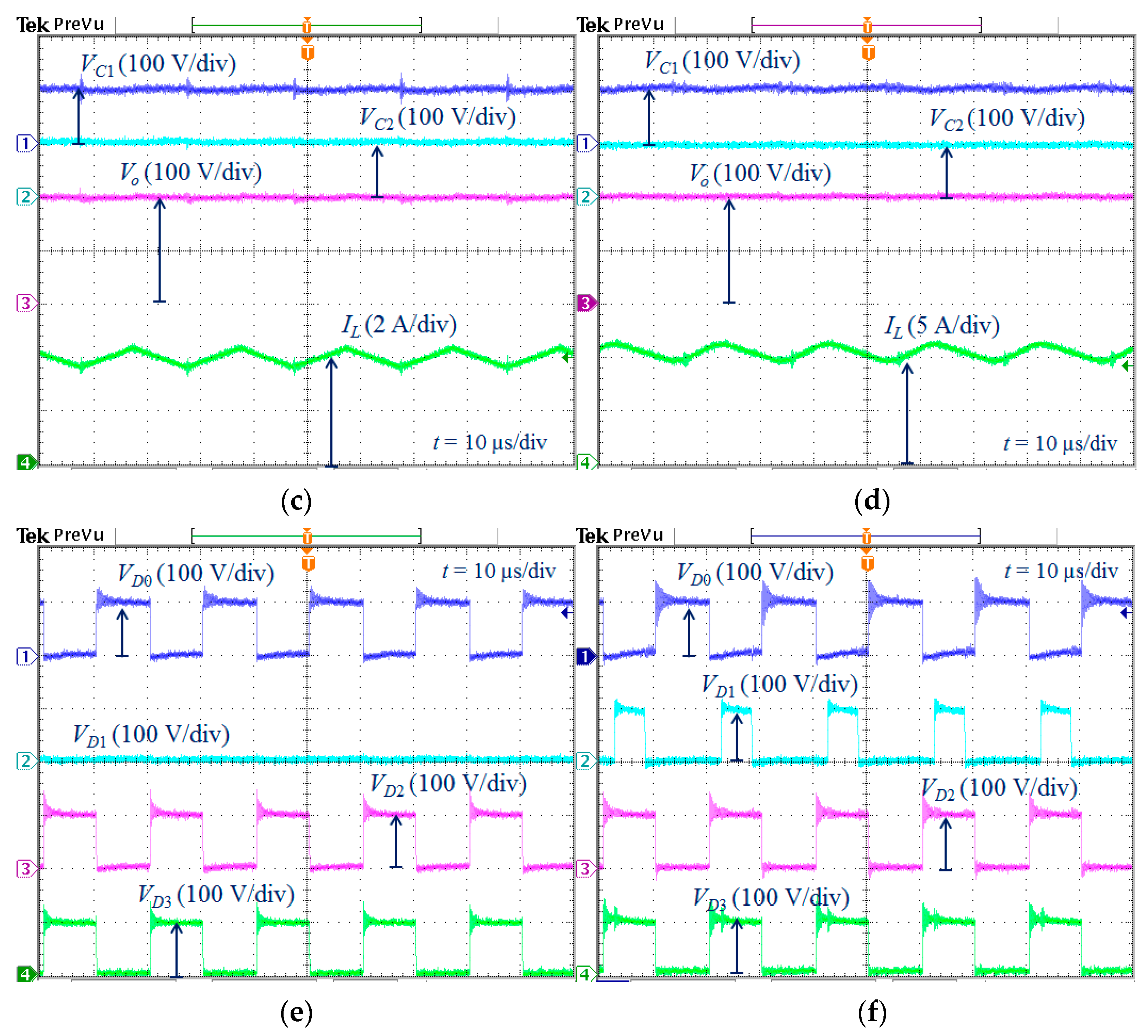

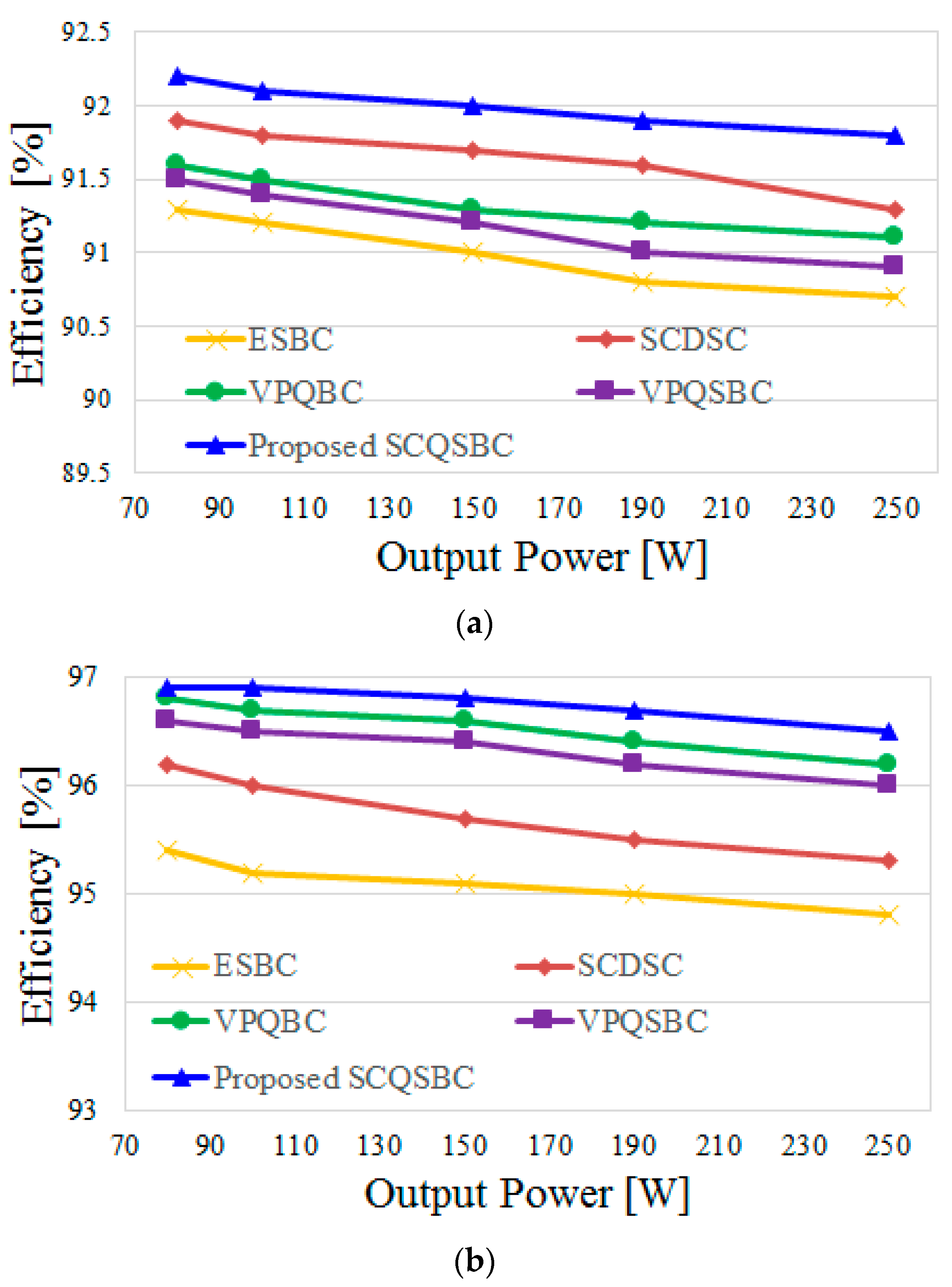

5. Simulation and Experimental Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Loana, M.P.C.; Septimiu, L.; Sorin, P.; Dan, L.; Loan, L.; Radu, M. A New Hybrid Inductor-Based Boost DC-DC Converter Suitable for Applications in Photovoltaic Systems. Energies 2019, 12, 252. [Google Scholar]

- Abdulaziz, A.; Khairy, S.; Naif, A.; Ahmed, G.A.K.; Hedra, S. Multi-Port PWM DC-DC Power Converter for Renewable Energy Applications. Energies 2021, 14, 3490. [Google Scholar]

- Nguyen, M.K.; Duong, T.D.; Lim, Y.C.; Kim, Y.J. Isolated boost DC-DC converter with three switches. IEEE Trans. Power Electron. 2018, 33, 1389–1398. [Google Scholar]

- Bin, G.; Jason, D.; Lai, J.S.; Zheng, Z.; Chuang, L. High boost ratio hybrid transformer DC–DC converter for photovoltaic module applications. IEEE Trans. Power Electron. 2013, 28, 2048–2058. [Google Scholar]

- Nguyen, M.K.; Lim, Y.C.; Choi, J.H.; Cho, G.B. Isolated High Step-up DC-DC Converter Based on Quasi-Switched-Boost Network. IEEE Trans. Ind. Electron. 2016, 63, 7553–7562. [Google Scholar] [CrossRef]

- Francois, F.; Thiery, A.M.; Eric, L.; Bertrand, G.; Jean, J.H.; Julia, C.B. An isolated multicell intercell transformer converter for applications with a high step-up ratio. IEEE Trans. Power Electron. 2013, 28, 1107–1119. [Google Scholar]

- Gang, W.; Xinbo, R.; Zhihong, Y. High step-up DC-DC converter based on switched capacitor and couple inductor. IEEE Trans. Ind. Electron. 2018, 65, 5572–5579. [Google Scholar]

- Yam, P.S.; Frede, B.; Poh, C.L. Quasi-Y-source boost DC-DC converter. IEEE Trans. Power Electron. 2015, 30, 6514–6519. [Google Scholar]

- Hossein, G.; Reza, S.S.; Mir, R.H.; Ebrahim, A.; Gorji, S.A. Design and Implementation a Single-Switch Step-Up DC-DC Converter Based on Cascaded Boost and Luo Converters. Energies 2021, 14, 3584. [Google Scholar]

- Lee, S.W.; Do, H.L. Quadratic Boost DC-DC Converter with High Voltage Gain and Reduced Voltage Stresses. IEEE Trans. Power Electron. 2019, 34, 2397–2404. [Google Scholar] [CrossRef]

- Javed, A.; Mohammad, Z.; Adil, S.; Lin, C.H.; Mohammed, A.; Raj, K.Y.; Mohd, T.; Kuntal, S.; Basem, A. A New High-Gain DC-DC Converter with Continuous Input Current for DC Microgrid Applications. Energies 2021, 14, 3629. [Google Scholar]

- Ahmad, A.; Pourya, S.; Mehdi, F. Interleaved Multistage Step-Up Topologies with Voltage Multiplier Cells. Energies 2020, 13, 5990. [Google Scholar]

- Ebrahim, B.; Hamed, M.M.; Mehran, S.; Seyed, H.H. Extendable Nonisolated High Gain DC-DC Converter Based on Active–Passive Inductor Cells. IEEE Trans. Ind. Electron. 2018, 65, 9478–9487. [Google Scholar]

- Sajad, R.; Vahid, A.; Frede, B. Implementation of a common grounded Z-source dc-dc converter with improved operation factors. IET Power Electron. 2019, 12, 2245–2255. [Google Scholar]

- Veda, P.G.; Marian, K.K. Analysis of PWM Z-source dc-dc converter in CCM for steady state. IEEE Trans. Circuits Syst. I Reg. Pap. 2012, 59, 854–863. [Google Scholar]

- Punit, K.; Mummadi, V. Z-network plus switched-capacitor boost dc-dc converters. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 791–803. [Google Scholar]

- Guidong, Z.; Bo, Z.; Zhong, L.; Dongyuan, Q.; Liqiang, Y.; Wolfgang, A.H. A 3-Z-network boost converter. IEEE Trans. Ind. Electron. 2015, 62, 278–288. [Google Scholar]

- Santanu, M.; Ravindranath, A.; Avinash, J. Inverse Watkins-Johnson topology based inverter. IEEE Trans. Power Electron. 2012, 27, 1066–1070. [Google Scholar]

- Nguyen, M.K.; Le, T.V.; Park, S.J.; Lim, Y.C. A class of quasi-switched boost inverters. IEEE Trans. Ind. Electron. 2015, 62, 1526–1536. [Google Scholar] [CrossRef]

- Alencar, F.D.S.; Fernanđo, L.T.; Enio, R.R. Switched Capacitor DC-DC Converters: A Survey on the Main Topologies, Design Characteristics, and Applications. Energies 2021, 14, 2231. [Google Scholar]

- Xiaoquan, Z.; Bo, Z.; Ke, J. Hybrid nonisolated active quasi-switched DC-DC converter for high step-up voltage conversion applications. IEEE Access 2020, 8, 222584–222598. [Google Scholar]

- Xiaoquan, Z.; Bo, Z.; Zhong, L.; Hong, L.; Li, R. Extended switched-boost DC-DC converters adopting switched-capacitor cells for high step-up conversion. IEEE J. Emerg. Sel. Topics Power Electron. 2017, 5, 1020–1030. [Google Scholar]

- Nguyen, M.K.; Duong, T.D.; Lim, L.C. Switched-capacitor-based dual-switch high-boost dc-dc converter. IEEE Trans. Power Electron. 2018, 33, 4181–4189. [Google Scholar] [CrossRef]

- Guidong, Z.; Zhiyang, W.; Samson, S.Y.; Si, Z.C.; Bo, Z.; Herbert, H.C.I.; Yun, Z. A generalized additional voltage pumping solution (GAVPS) for high-step-up converters. IEEE Trans. Power Electron. 2019, 34, 6456–6467. [Google Scholar]

| Components | Conducting Current | Conducting Period |

|---|---|---|

| S1 | 0.5 × T | |

| S2 | D × T | |

| D0 | Io | 0.5 × T |

| D1 | (1 − D) × T | |

| D2 | 0.5 × T | |

| D3 | 2Io | 0.5 × T |

| L | T | |

| C1 | D × T | |

| (1 − D) × T | ||

| C2 | (0.5 − D) × T | |

| D × T | ||

| 0.5 × T | ||

| Co | −Io | (0.5 − D) × T |

| D × T | ||

| 2Io | 0.5 × T |

| 3-ZBC [17] | AQSC [21] | ESBC [22] | SCDSC [23] | VPQBC [24] | VP-QSBC [24] | Proposed SCQSBC | |

|---|---|---|---|---|---|---|---|

| Inductor/Capacitor | 4/2 | 2/4 | 1/3 | 1/3 | 2/3 | 1/3 | 1/3 |

| Switch/Diode | 1/9 | 2/4 | 2/4 | 2/4 | 1/4 | 2/4 | 2/4 |

| Total of Devices | 16 | 12 | 10 | 10 | 10 | 10 | 10 |

| Voltage gain | |||||||

| Normalized capacitor voltage stress (VC/Vi) | |||||||

| Normalized switch voltage stress (VS/Vi) | |||||||

| Normalized diode voltage stress (VD/Vi) | D/(1 − D) 1 2D(1 + D)/(1 − D)2 (1 + D)/(1 − D) D(1 + D)/(1 − D)2 (1 + D)2/(1 − D)2 | ||||||

| Switch current stress (IS/Io) | |||||||

| Diode current stress (ID/Io) | D(1 + D)/(1 − D)2 (1 + D)/(1 − D) 2D(1 + D)/(1 − D)2 D/(1 − D) 1 | 1/D | 1/D | 1/D | 1/D | 1/D | 1 2 |

| Inductances | |||||||

| Input current ripple | High | Low | High | High | Low | Low | Very low |

| Parameter | Values |

|---|---|

| Input voltage range | 20 V to 50 V |

| Output voltage | 200 V |

| Power rating | 250 W |

| Inductor (L) | 0.5 mH |

| Capacitors | 10 µF/160 V for C1, C2 |

| 110 µF/450 V for C0 | |

| Switching frequency | 50 kHz |

| MOSFETs | IRFP4668PbF |

| Diodes | STPS60SM200C |

| Parameters | Values | |

|---|---|---|

| Inductor | Core | CM777125 (142 nH/N2) |

| Copper-wire | 0.04 Ω | |

| Capacitors | C1, C2 | 3.2 mΩ |

| Co | 4 mΩ | |

| Power switches | IRFP4668PbF (200 V, 130 A, RDSon = 8 mΩ) | |

| Power diodes | STPS60SM200C (200V, 30A, UD = 0.7 V) | |

| Converter | VPQBC | VPQSBC | Proposed SCQSBC |

|---|---|---|---|

| ΔIin | 1.3 A | 1.2 A | 0.8 A |

| Efficiency | 91.1% | 90.9% | 91.8% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Duong, T.-D.; Nguyen, M.-K.; Tran, T.-T.; Lim, Y.-C.; Choi, J.-H. Transformer-Less Switched-Capacitor Quasi-Switched Boost DC-DC Converter. Energies 2021, 14, 6591. https://doi.org/10.3390/en14206591

Duong T-D, Nguyen M-K, Tran T-T, Lim Y-C, Choi J-H. Transformer-Less Switched-Capacitor Quasi-Switched Boost DC-DC Converter. Energies. 2021; 14(20):6591. https://doi.org/10.3390/en14206591

Chicago/Turabian StyleDuong, Truong-Duy, Minh-Khai Nguyen, Tan-Tai Tran, Young-Cheol Lim, and Joon-Ho Choi. 2021. "Transformer-Less Switched-Capacitor Quasi-Switched Boost DC-DC Converter" Energies 14, no. 20: 6591. https://doi.org/10.3390/en14206591

APA StyleDuong, T.-D., Nguyen, M.-K., Tran, T.-T., Lim, Y.-C., & Choi, J.-H. (2021). Transformer-Less Switched-Capacitor Quasi-Switched Boost DC-DC Converter. Energies, 14(20), 6591. https://doi.org/10.3390/en14206591