An Analytical Approach for Design of a Cross-Connected Fibonacci Switched Capacitor Converter

Abstract

1. Introduction

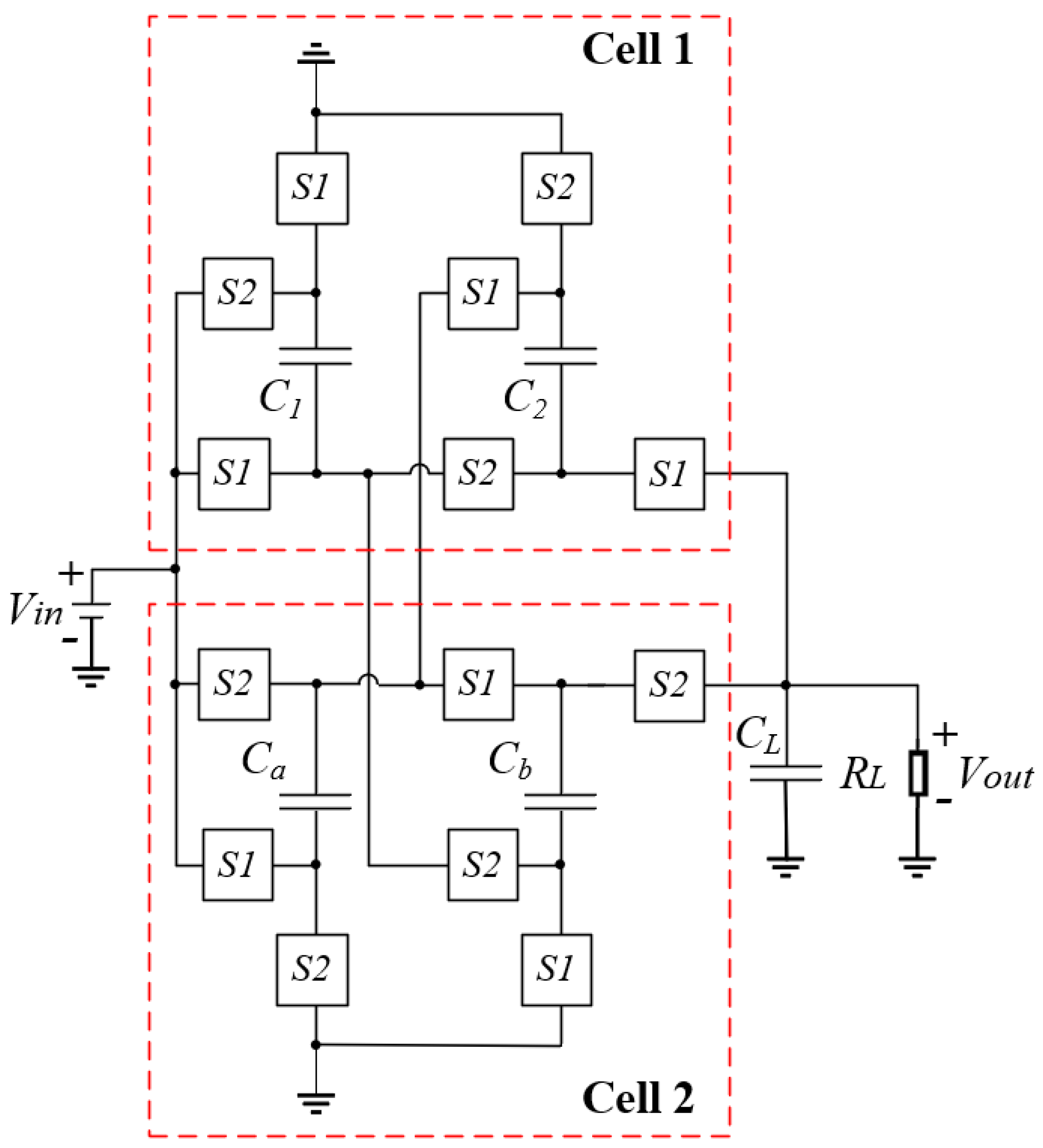

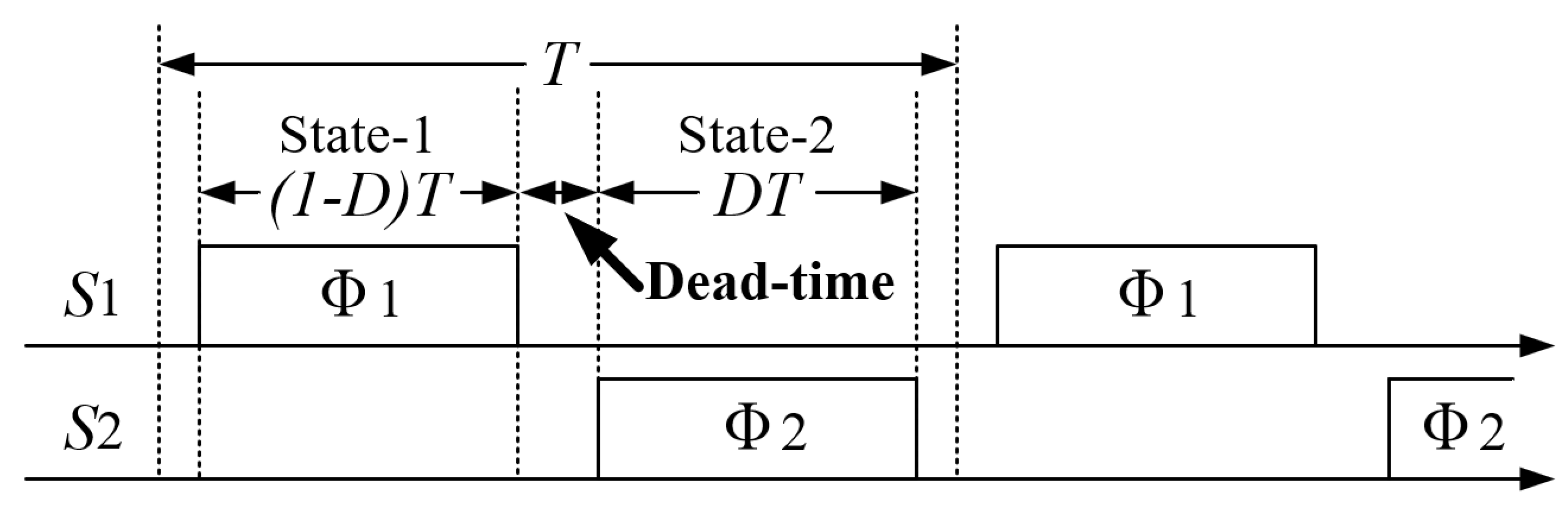

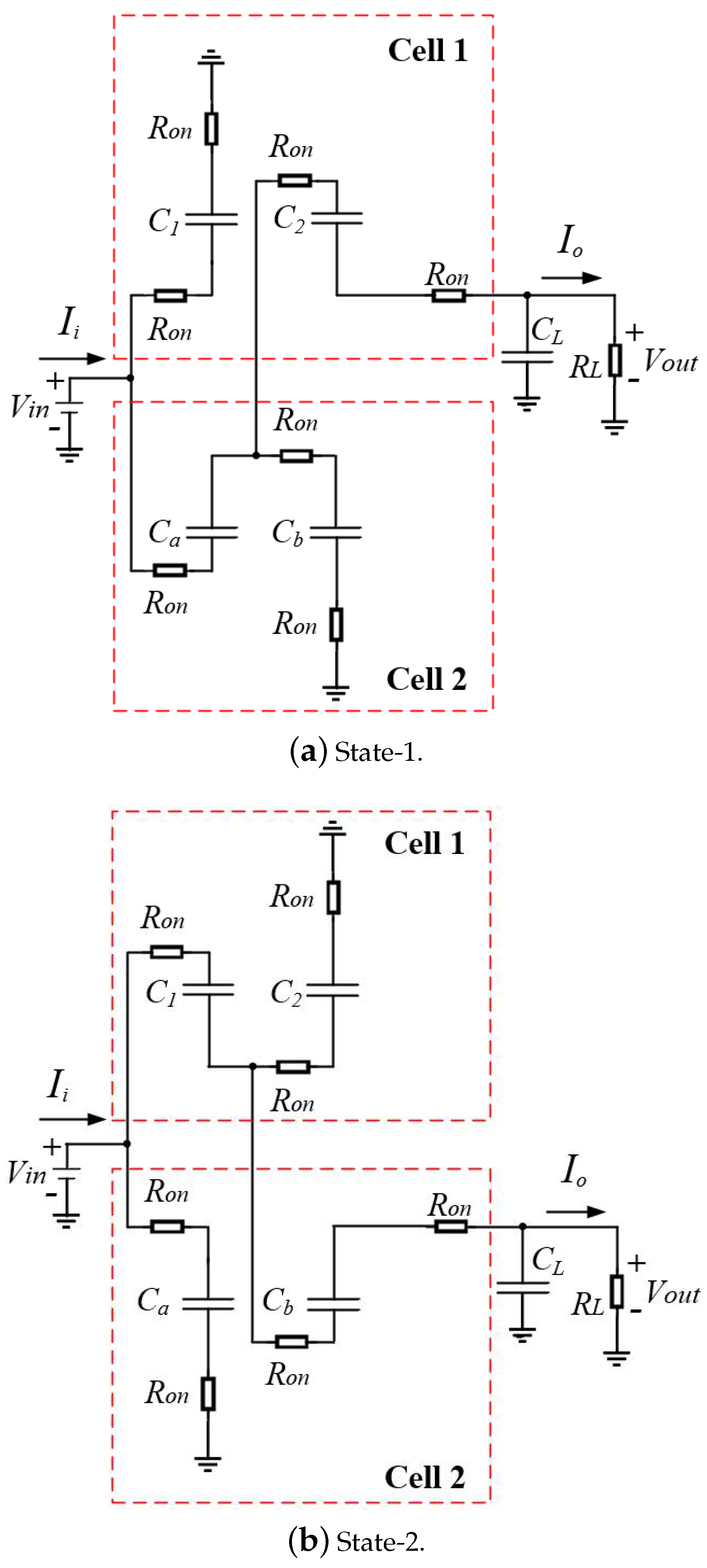

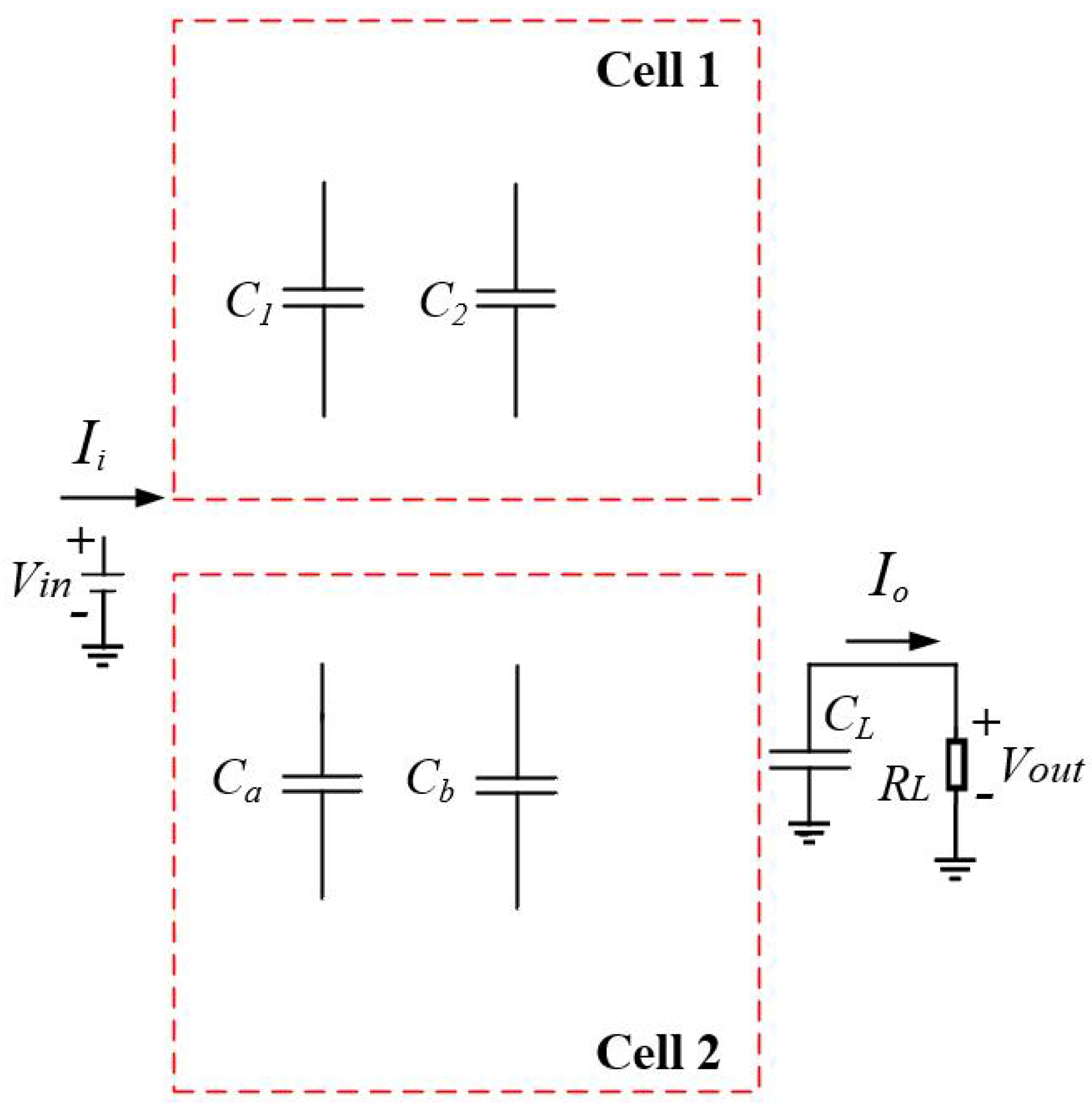

2. Circuit Configuration

3. Theoretical Analysis

3.1. Voltage Gain Function

3.2. Optimization

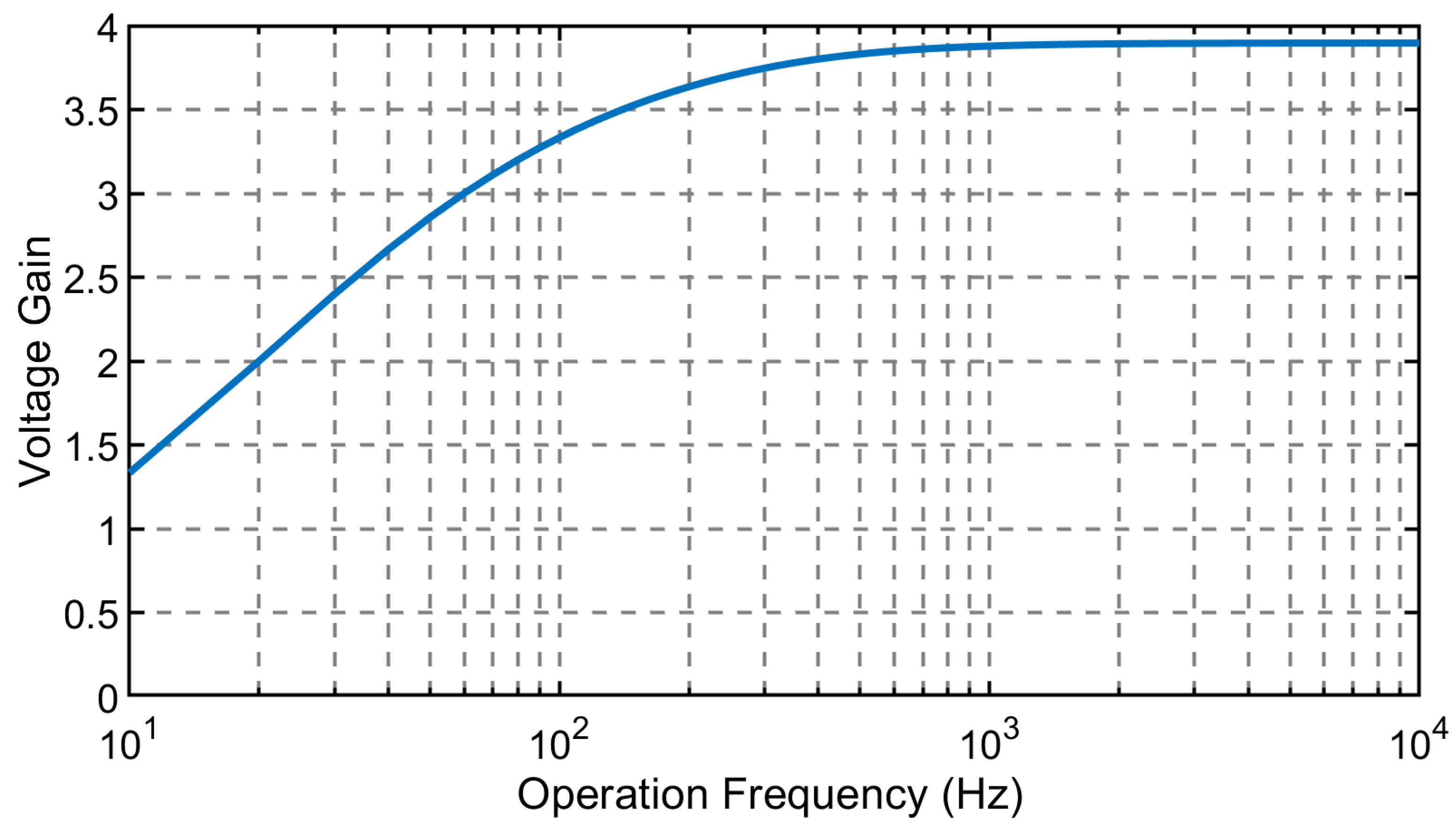

3.2.1. Operation Frequency

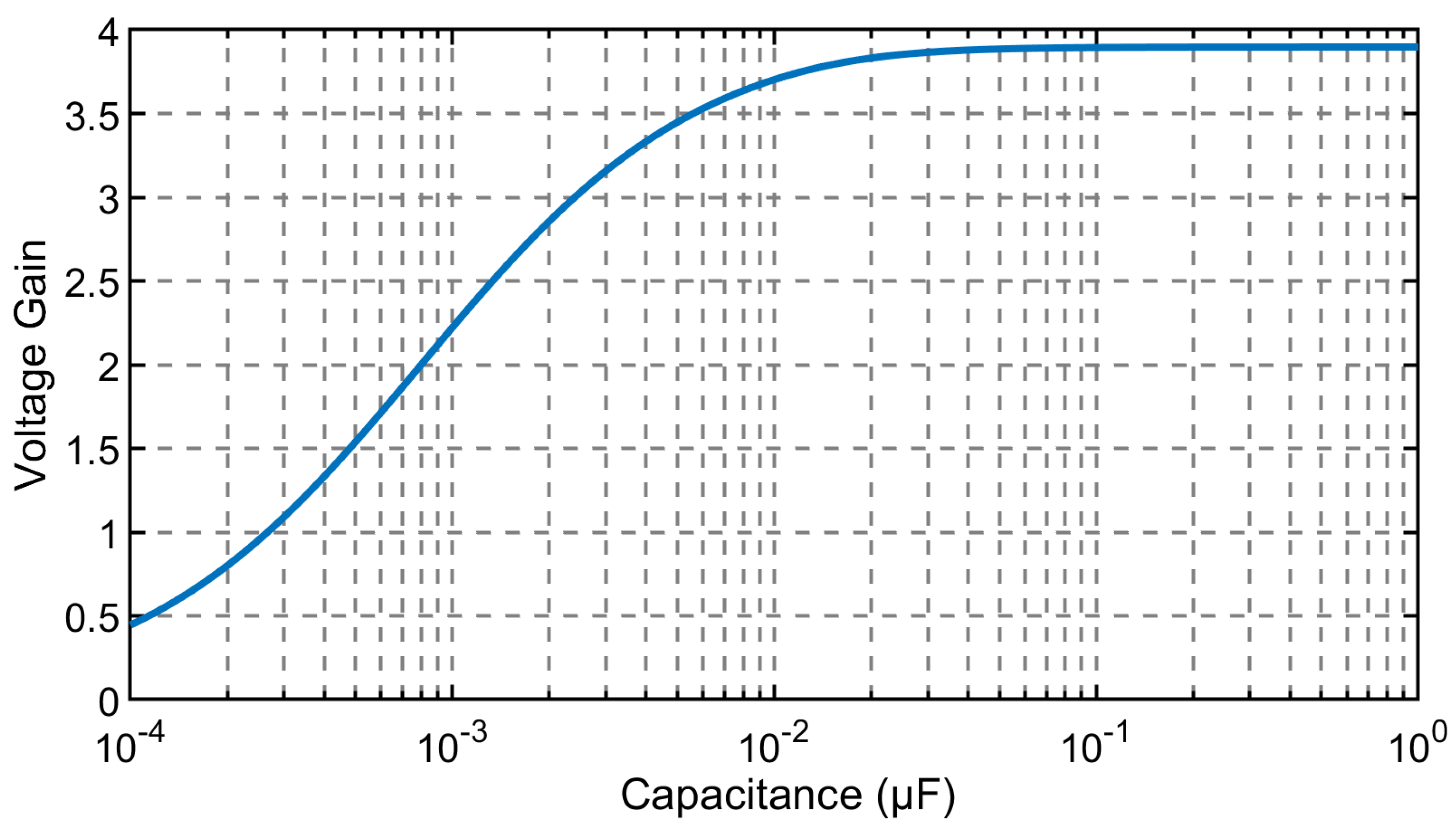

3.2.2. Flying Capacitors Capacitance

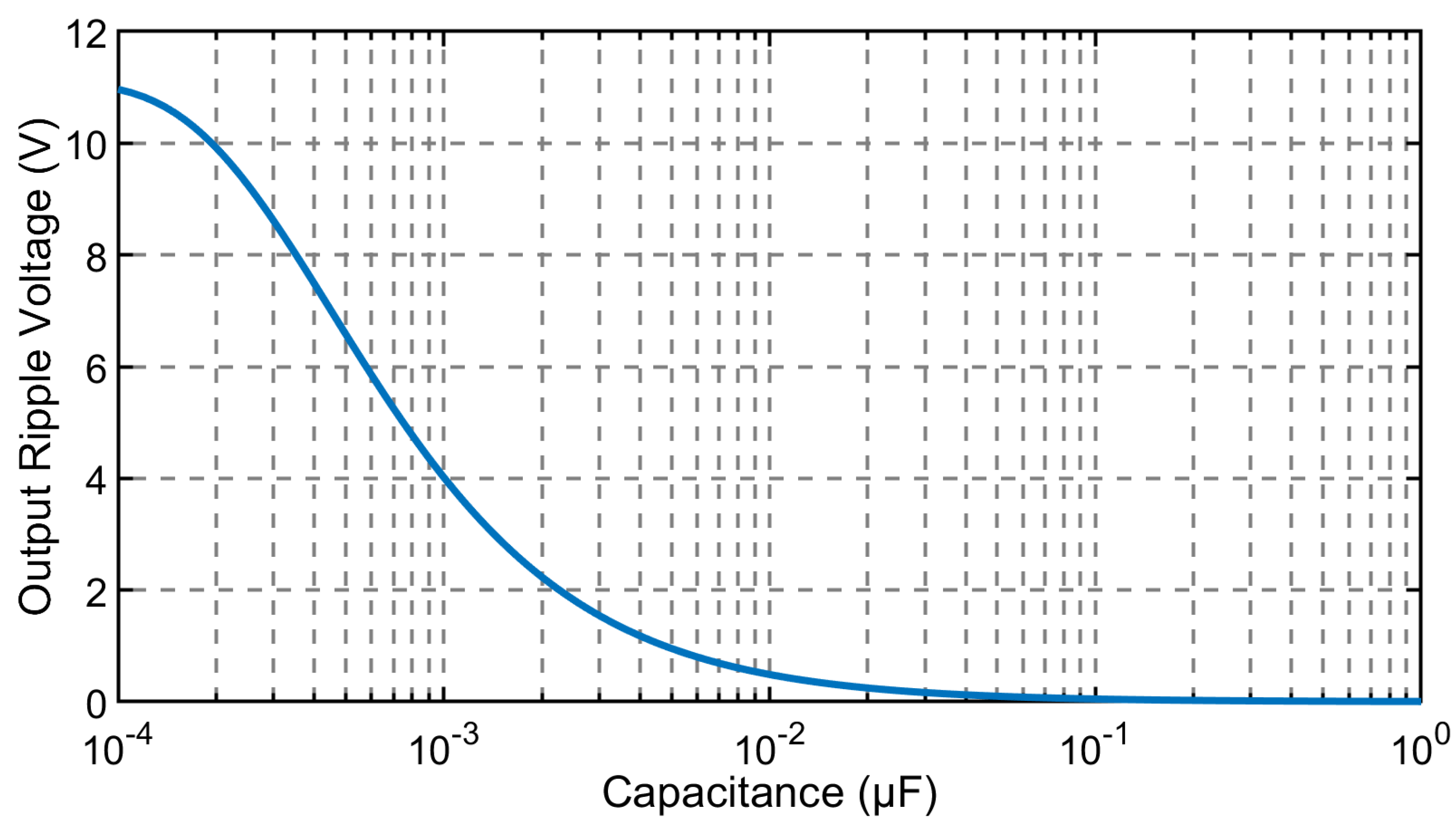

3.2.3. Output Capacitor Capacitance

3.3. Power Stage Transfer Function

4. Simulation, Experiment and Comparison

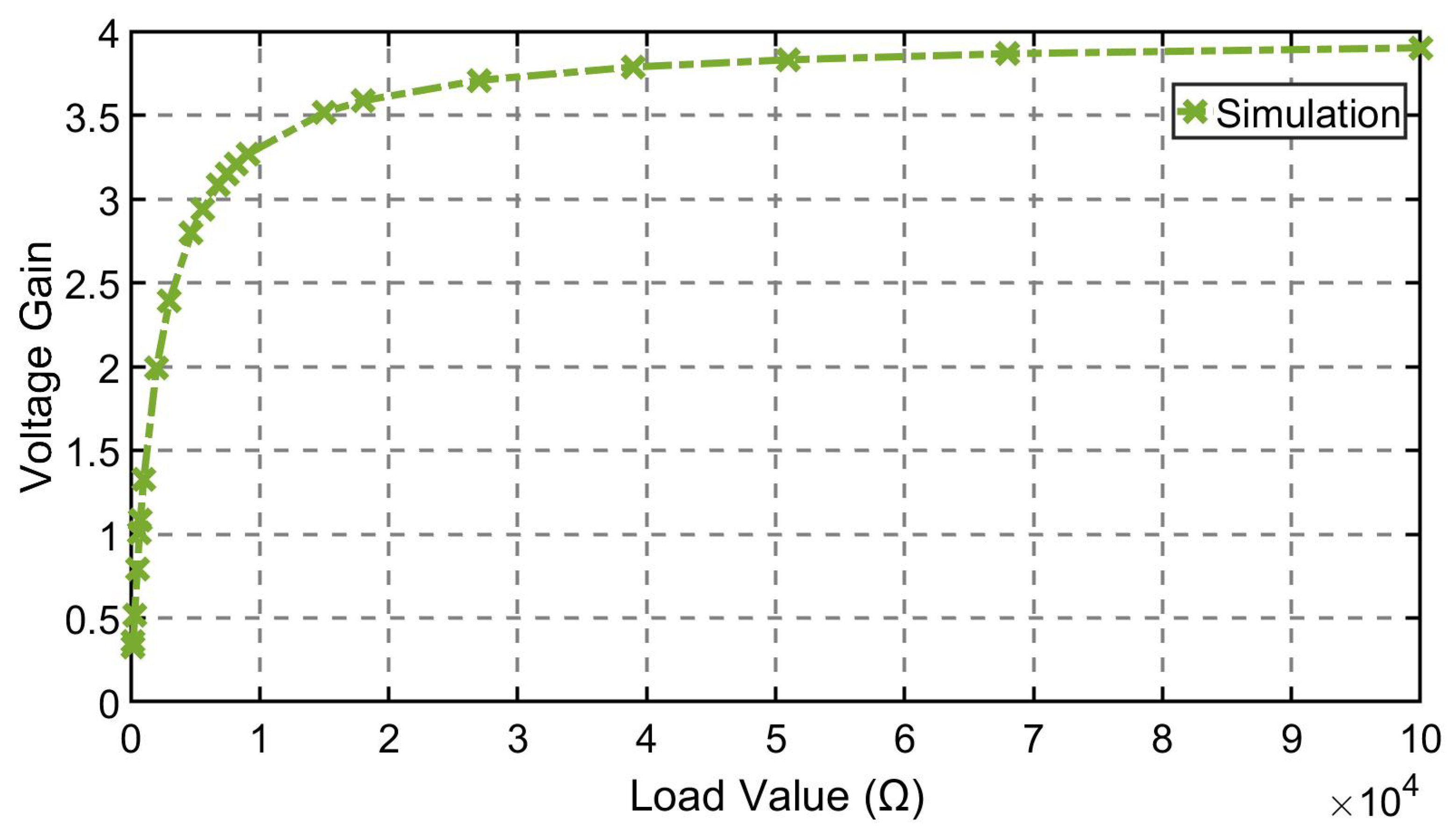

4.1. Simulation Result

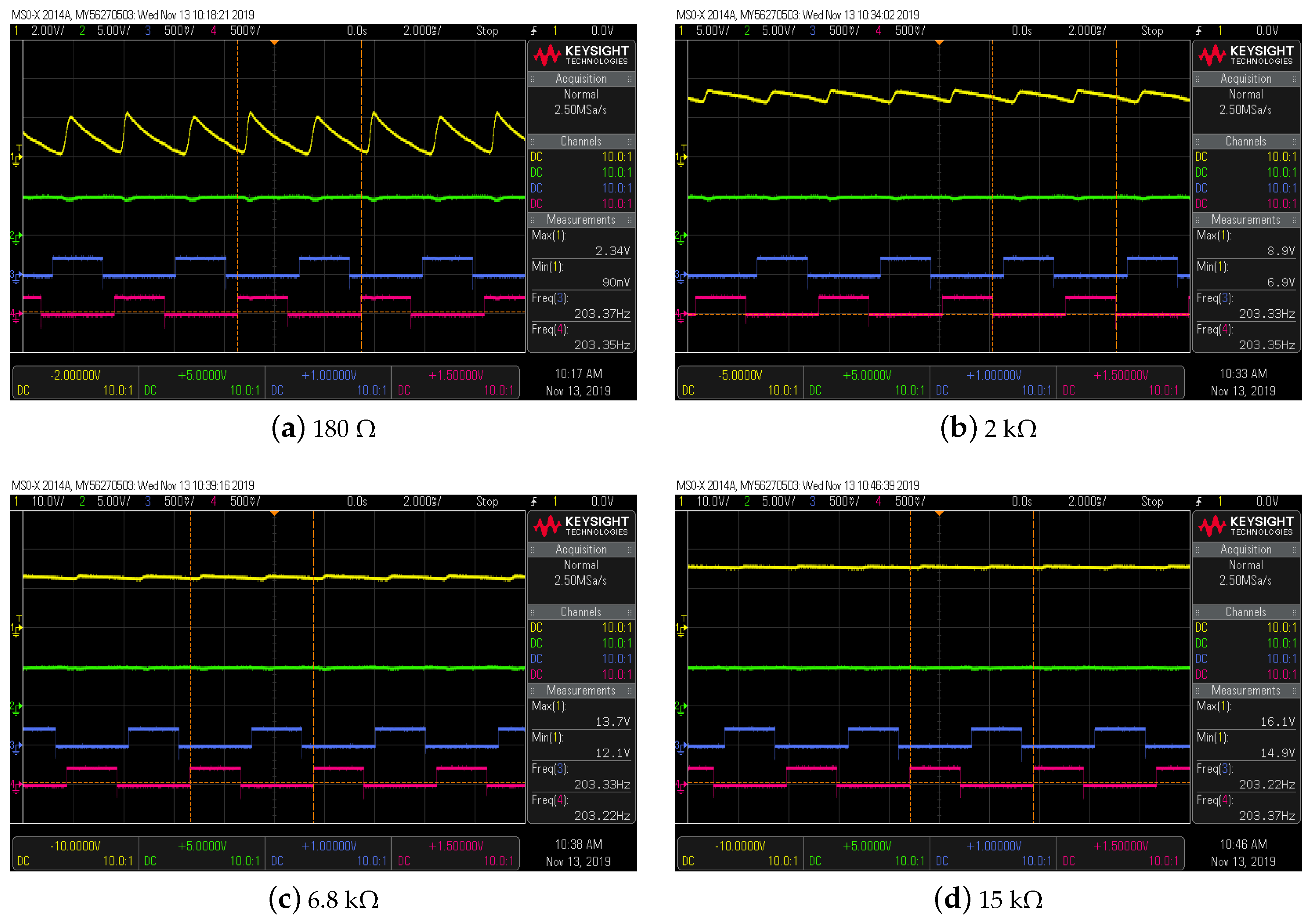

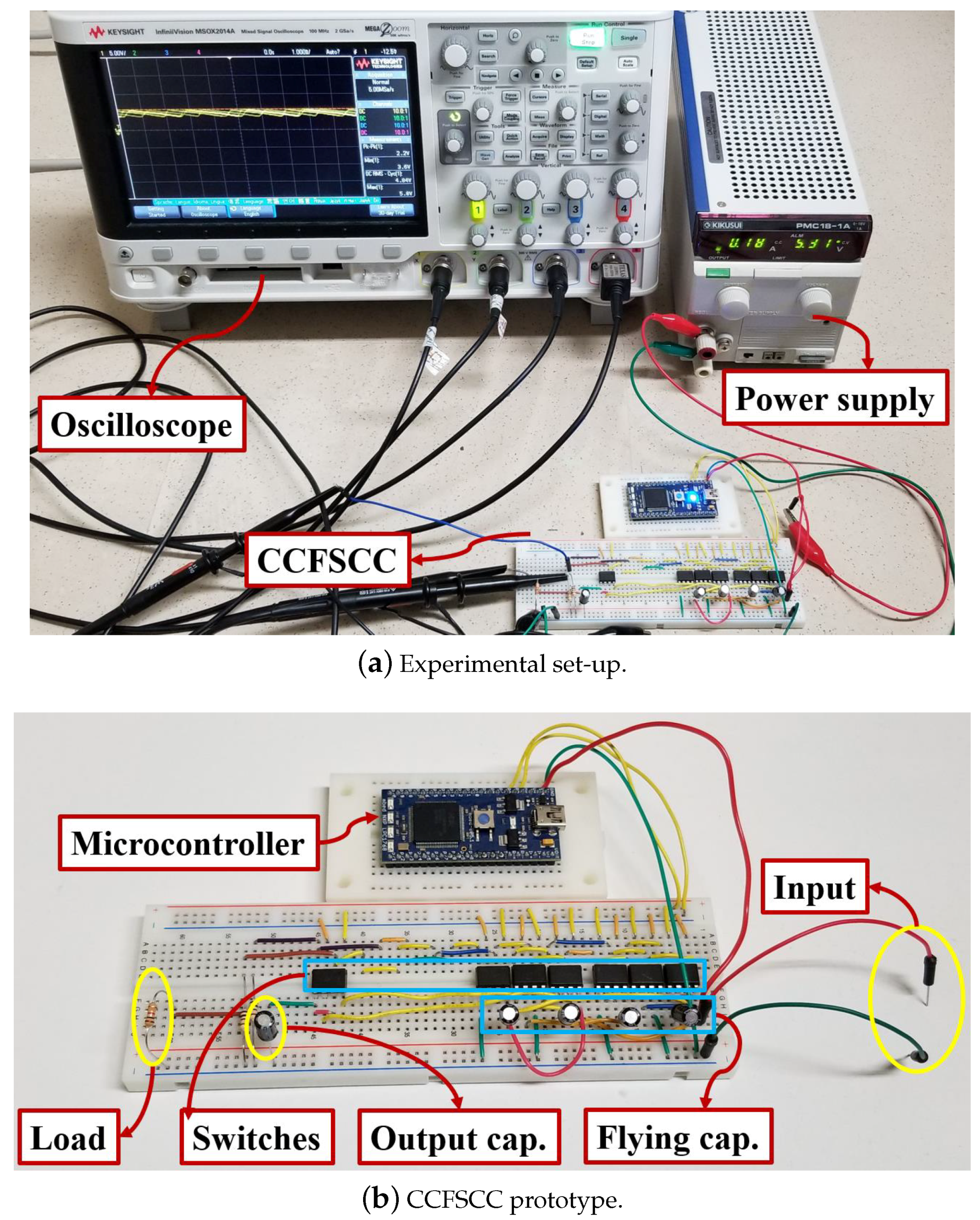

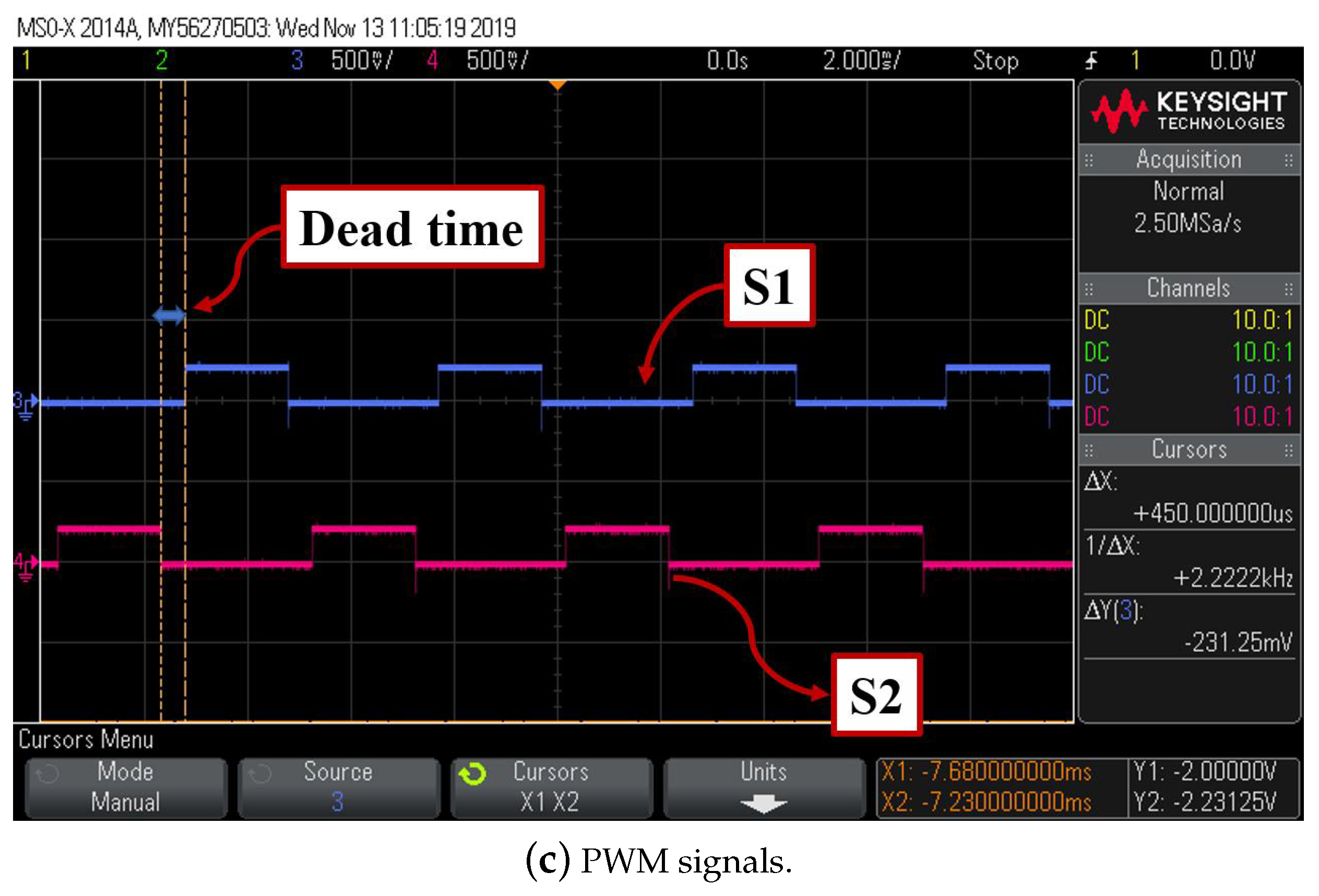

4.2. Experimental Result

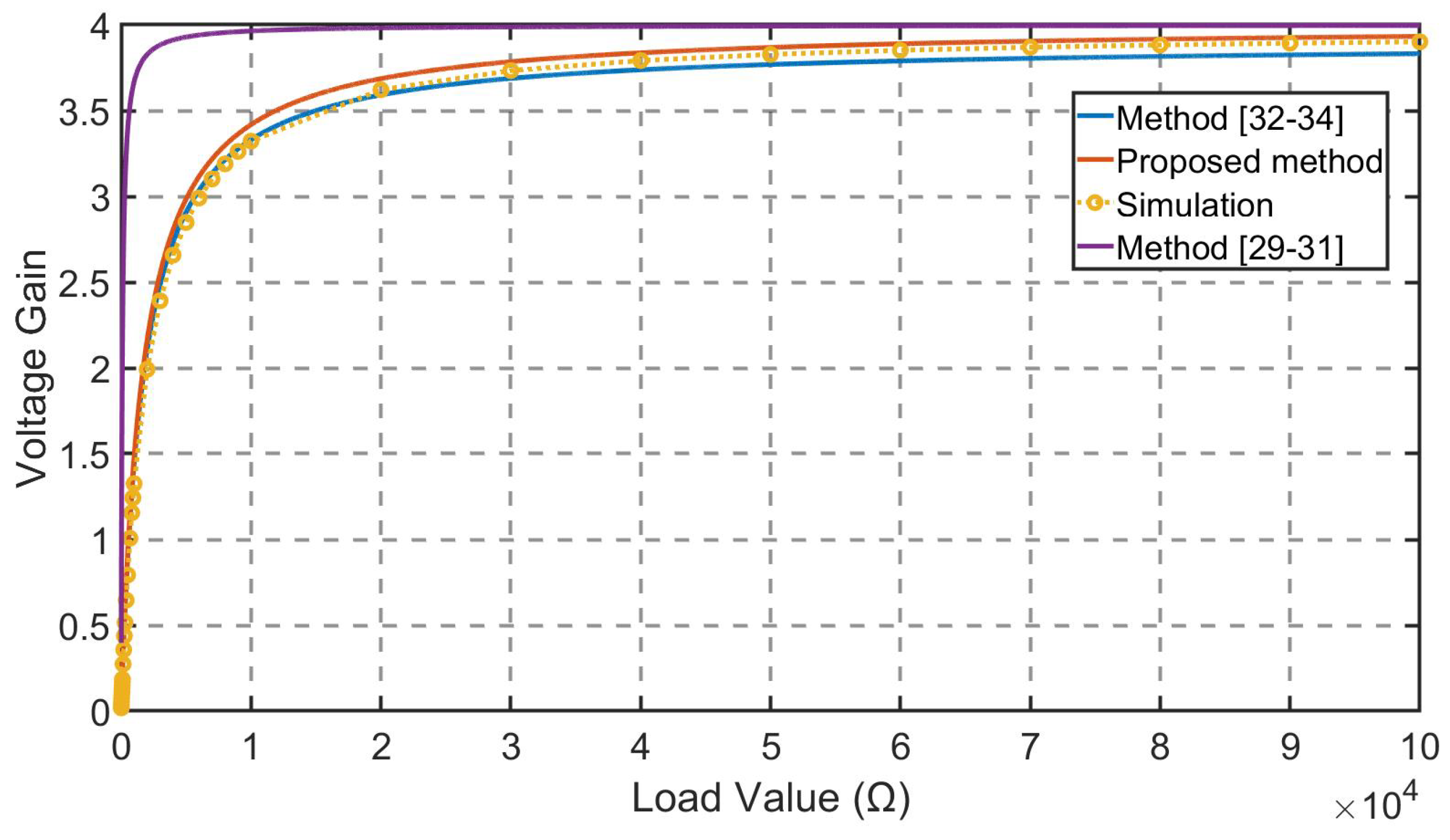

4.3. Comparison of Calculation, Simulation and Experimental Results

4.4. Comparison with Existing Methods

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

Appendix A

References

- Htet, K.O.; Fan, H.; Heidari, H. Switched Capacitor DC-DC Converter for Miniaturised Wearable Systems. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–5. [Google Scholar]

- Kilani, D.; Mohammad, B.; Alhawari, M.; Saleh, H.; Ismail, M. A Dual-Output Switched Capacitor DC–DC Buck Converter Using Adaptive Time Multiplexing Technique in 65-nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 4007–4016. [Google Scholar] [CrossRef]

- Grasso, A.D.; Palumbo, G.; Pennisi, S. Switched-Capacitor Power Management Integrated Circuit for Autonomous Internet of Things Node. IEEE Trans. Circuits Syst. II Express Briefs 2018, 65, 1455–1459. [Google Scholar] [CrossRef]

- Shah, N.; Lajevardi, P.; Wojciechowski, K.; Lang, C.; Murmann, B. An Energy Harvester Using Image Sensor Pixels With Cold Start and Over 96% MPPT Efficiency. IEEE Solid State Circuits Lett. 2019, 2, 207–210. [Google Scholar] [CrossRef]

- Wu, X.; Shi, Y.; Jeloka, S.; Yang, K.; Lee, I.; Lee, Y.; Sylvester, D.; Blaauw, D. A 20-pW Discontinuous Switched-Capacitor Energy Harvester for Smart Sensor Applications. IEEE J. Solid-State Circuits 2017, 52, 972–984. [Google Scholar] [CrossRef]

- Alhawari, M.; Kilani, D.; Mohammad, B.; Saleh, H.; Ismail, M. An efficient thermal energy harvesting and power management for μWatt wearable BioChips. In Proceedings of the 2016 IEEE International Symposium on Circuits and Systems (ISCAS), Montreal, QC, Canada, 22–25 May 2016; pp. 2258–2261. [Google Scholar]

- Liu, X.; Ravichandran, K.; Sánchez-Sinencio, E. A Switched Capacitor Energy Harvester Based on a Single-Cycle Criterion for MPPT to Eliminate Storage Capacitor. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 793–803. [Google Scholar] [CrossRef]

- Nielsen-Lónn, M.; Angelov, P.; Wikner, J.J.; Alvandpour, A. Self-oscillating multilevel switched-capacitor DC/DC converter for energy harvesting. In Proceedings of the 2017 IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC), Linkoping, Sweden, 23–25 October 2017; pp. 1–5. [Google Scholar]

- Mohey, A.M.; Ibrahim, S.A.; Hafez, I.M.; Kim, H. Design Optimization for Low-Power Reconfigurable Switched-Capacitor DC-DC Voltage Converter. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 4079–4092. [Google Scholar] [CrossRef]

- Lee, H.; Jang, E.; Saif, H.; Lee, Y.; Kim, M.; Khan, M.B.; Lee, Y. A Sub-nW Fully Integrated Switched-Capacitor Energy Harvester for Implantable Applications. In Proceedings of the IEEE 44th European Solid State Circuits Conference (ESSCIRC), Dresden, Germany, 3–6 September 2018; pp. 50–53. [Google Scholar]

- Forouzesh, M.; Siwakoti, Y.P.; Gorji, S.A.; Blaabjerg, F.; Lehman, B. Step-Up DC–DC Converters: A Comprehensive Review of Voltage-Boosting Techniques, Topologies, and Applications. IEEE Trans. Power Electron. 2017, 32, 9143–9178. [Google Scholar] [CrossRef]

- Dickson, J.F. On-chip high-voltage generation in mnos integrated circuits using an improved voltage multiplier technique. IEEE J. Solid-State Circuits 1976, 32, 374–378. [Google Scholar] [CrossRef]

- Mahmoud, A.; Alhawari, M.; Mohammad, B.; Saleh, H.; Ismail, M. A Gain-Controlled, Low-Leakage Dickson Charge Pump for Energy-Harvesting Applications. IEEE Trans. VLSI Syst. 2019, 27, 1114–1123. [Google Scholar] [CrossRef]

- Schaef, C.; Stauth, J.T. A Highly Integrated Series–Parallel Switched-Capacitor Converter With 12 V Input and Quasi-Resonant Voltage-Mode Regulation. IEEE J. Emerg. Sel. Top Power Electron. 2018, 6, 456–464. [Google Scholar] [CrossRef]

- Beck, Y.; Singer, S. General transposed series-parallel switched capacitor converter topologies. In Proceedings of the 2017 IEEE AFRICON, Cape Town, South Africa, 18–20 September 2017; pp. 1351–1356. [Google Scholar]

- Abraham, C.; Jose, B.R.; Mathew, J.; Evzelman, M. Modelling, simulation and experimental investigation of a new two input, series-parallel switched capacitor converter. IET Power Electron. 2017, 10, 368–376. [Google Scholar] [CrossRef]

- Cao, D.; Peng, F.Z. Zero-current-switching multilevel modular switched-capacitor DC–DC converter. In Proceedings of the IEEE Energy Conversion Congress and Exposition (ECCE), San Jose, CA, USA, 20–24 September 2009; pp. 3516–3522. [Google Scholar]

- Cao, D.; Jiang, S.; Peng, F.Z. Optimal design of multilevel modular switched-capacitor DC-DC converter. In Proceedings of the IEEE Energy Conversion Congress and Exposition, Phoenix, AZ, USA, 17–22 September 2011; pp. 537–544. [Google Scholar]

- Cao, D.; Peng, F.Z. Multiphase multilevel modular DC–DC converter for high-current high-gain TEG application. IEEE Trans. Ind. Appl. 2011, 47, 1400–1408. [Google Scholar]

- Zanwar, M.; Sen, S. Design of CMOS programmable output binary and fibonacci switched capacitor step-down DC-DC converter. In Proceedings of the 2016 International Conference on VLSI Systems, Architectures, Technology and Applications (VLSI-SATA), Bangalore, India, 10–12 January 2016; pp. 1–6. [Google Scholar]

- Subburaj, V.; Jena, D.; Kumar, R.; Deshmukh, A.V.; Nayak, B.; Bansal, H. Design of series, Fi=Fi-1+Fi-3 for the denominators (1, 2,.. 6) of switched capacitor converter. In Proceedings of the 2016 IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES), Delhi, India, 4–6 July 2016; pp. 1–5. [Google Scholar]

- Junussov, A.; Ruderman, A. Analysis of a reconfigurable Fibonacci switched capacitor converter with a multiphase balanced switching. In Proceedings of the 2015 IEEE 5th International Conference on Power Engineering, Energy and Electrical Drives (POWERENG), Riga, Latvia, 11–13 May 2015; pp. 164–169. [Google Scholar]

- Sanders, S.R.; Alon, E.; Le, H.; Seeman, M.D.; John, M.; Ng, V.W. The Road to Fully Integrated DC–DC Conversion via the Switched-Capacitor Approach. IEEE Trans. Power Electron. 2013, 28, 4146–4155. [Google Scholar] [CrossRef]

- Seeman, M.D.; Ng, V.W.; Le, H.; John, M.; Alon, E.; Sanders, S.R. A comparative analysis of Switched-Capacitor and inductor-based DC-DC conversion technologies. In Proceedings of the 2010 IEEE 12th Workshop on Control and Modeling for Power Electronics (COMPEL), Boulder, CO, USA, 28–30 June 2010; pp. 1–7. [Google Scholar]

- Eguchi, K.; Hirata, S.; Shimoji, M.; Zhu, H. Design of a Step-Up/Step-Down k (=2,3,...)-Fibonacci DC-DC Converter Designed by Switched-Capacitor Techniques. In Proceedings of the 2012 Fifth International Conference on Intelligent Networks and Intelligent Systems, Tianjin, China, 1–3 November 2012; pp. 170–173. [Google Scholar]

- Do, W.; Fujisaki, H.; Asadi, F.; Eguchi, K. A Cross-Connected Charge Pump for Energy Harvesting Applications. IJICIC 2019, 15, 969–982. [Google Scholar]

- Rubpongse, R.; Asadi, F.; Do, W.; Eguchi, K. Experiment of a High Voltage Gain Switched Capacitor DC-DC Converter Based on a Cross-Connected Fibonacci-Type Converter. ICIC Express Lett. 2019, 13, 393–400. [Google Scholar]

- Eguchi, K.; Julsereewong, P.; Julsereewong, A.; Fujimoto, K.; Sasaki, H. A Dickson-type adder/subtractor DC-DC converter realizing step-up/step-down conversion. IJICIC 2013, 9, 123–138. [Google Scholar]

- Seeman, M.D.; Sanders, S.R. Analysis and Optimization of Switched-Capacitor DC–DC Converters. IEEE Trans. Power Electron. 2008, 23, 841–851. [Google Scholar] [CrossRef]

- Vos, J.D.; Flandre, D.; Bol, D. A Sizing Methodology for On-Chip Switched-Capacitor DC/DC Converters. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 1597–1606. [Google Scholar] [CrossRef]

- Ng, V.W.; Sanders, S.R. A High-Efficiency Wide-Input-Voltage Range Switched Capacitor Point-of-Load DC–DC Converter. IEEE Trans. Power Electron. 2013, 28, 4335–4341. [Google Scholar] [CrossRef]

- Wu, B.; Li, S.; Smedley, K.M.; Singer, S. Analysis of High-Power Switched-Capacitor Converter Regulation Based on Charge-Balance Transient-Calculation Method. IEEE Trans. Power Electron. 2016, 31, 3482–3494. [Google Scholar] [CrossRef]

- Yang, L.; Wu, B.; Tong, X.; Smedley, K.M.; Li, G. Dynamic Capacitor Ampere-Second Balance Transient Calculation Modeling Method for Switched-Capacitor Converters. IEEE Trans. Power Electron. 2018, 33, 8916–8926. [Google Scholar] [CrossRef]

- Wu, B.; Yang, L.; Zhang, X.; Smedley, K.M.; Li, G. Modeling and Analysis of Variable Frequency One-Cycle Control on High-Power Switched-Capacitor Converters. IEEE Trans. Power Electron. 2018, 33, 5465–5475. [Google Scholar] [CrossRef]

- Wester, G.W.; Middlebrook, R.D. Low-Frequency Characterization of Switched dc-dc Converters. IEEE Trans. Aerosp. Electron. Syst. 1973, AES-9, 376–385. [Google Scholar] [CrossRef]

- Solero, L.; Lidozzi, A.; Pomilio, J.A. Design of multiple-input power converter for hybrid vehicles. IEEE Trans. Power Electron. 2005, 31, 1007–1016. [Google Scholar] [CrossRef]

- Sankaranarayanan, V.; Shirazi, M.; Gao, Y.; Ghosh, A.; Erickson, R.W.; Maksimovic, D. Controller Hardware-in-the-Loop Validation of a Modular Control Architecture for a Composite DC-DC Converter. In Proceedings of the 2019 20th Workshop on Control and Modeling for Power Electronics (COMPEL), Toronto, ON, Canada, 17–20 June 2019; pp. 1–7. [Google Scholar]

- Su, L.; Ma, D.; Brokaw, A.P. Design and Analysis of Monolithic Step-Down SC Power Converter With Subthreshold DPWM Control for Self-Powered Wireless Sensors. IEEE Trans. Circuits Syst. I Regul. Pap. 2010, 57, 280–290. [Google Scholar]

- Su, L.; Ma, D.; Brokaw, A.P. A monolithic step-down SC power converter with frequency-programmable subthreshold z-domain DPWM control for ultra-low power microsystems. In Proceedings of the ESSCIRC 2008—34th European Solid-State Circuits Conference, Edinburgh, UK, 15–19 September 2008; pp. 58–61. [Google Scholar]

- Zheng, C.; Su, L.; Ma, D. A Systematic USFG Design Approach for Integrated Reconfigurable Switched-Capacitor Power Converters. IEEE Trans. Circuits Syst. I Regul. Pap. 2011, 58, 2790–2800. [Google Scholar] [CrossRef]

| Parameters | Value |

|---|---|

| 5 V | |

| 4.7 F | |

| 4.7 F | |

| T | 4 ms |

| 11 | |

| 1k |

| Parameters | Value |

|---|---|

| 5 V | |

| 4.7 F | |

| 4.7 F | |

| T | 4 ms |

| 11 | |

| Parts and Parameters | Value |

|---|---|

| 5 V | |

| 4.7 F | |

| 4.7 F | |

| T | 4.9 ms |

| 2 ms | |

| 0.45 ms | |

| 11 | |

| Switch | AOW217 |

| Microcontroller | LPC1768 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Do, W.; Bevrani, H.; Shafiee, Q.; Eguchi, K. An Analytical Approach for Design of a Cross-Connected Fibonacci Switched Capacitor Converter. Energies 2020, 13, 431. https://doi.org/10.3390/en13020431

Do W, Bevrani H, Shafiee Q, Eguchi K. An Analytical Approach for Design of a Cross-Connected Fibonacci Switched Capacitor Converter. Energies. 2020; 13(2):431. https://doi.org/10.3390/en13020431

Chicago/Turabian StyleDo, Wanglok, Hassan Bevrani, Qobad Shafiee, and Kei Eguchi. 2020. "An Analytical Approach for Design of a Cross-Connected Fibonacci Switched Capacitor Converter" Energies 13, no. 2: 431. https://doi.org/10.3390/en13020431

APA StyleDo, W., Bevrani, H., Shafiee, Q., & Eguchi, K. (2020). An Analytical Approach for Design of a Cross-Connected Fibonacci Switched Capacitor Converter. Energies, 13(2), 431. https://doi.org/10.3390/en13020431