A Three-Level DC-Link Quasi-Switch Boost T-Type Inverter with Voltage Stress Reduction

Abstract

1. Introduction

- ▪

- The boost factor and voltage gain are improved compared to the conventional 3L-qSBT2I.

- ▪

- The modulation index is increased by adopting SVP technique.

- ▪

- The voltage stress on power devices like capacitors, diodes, and switches is decreased significantly.

- ▪

- The magnitude of CMV is reduced compared to the conventional 3L-qSBT2I.

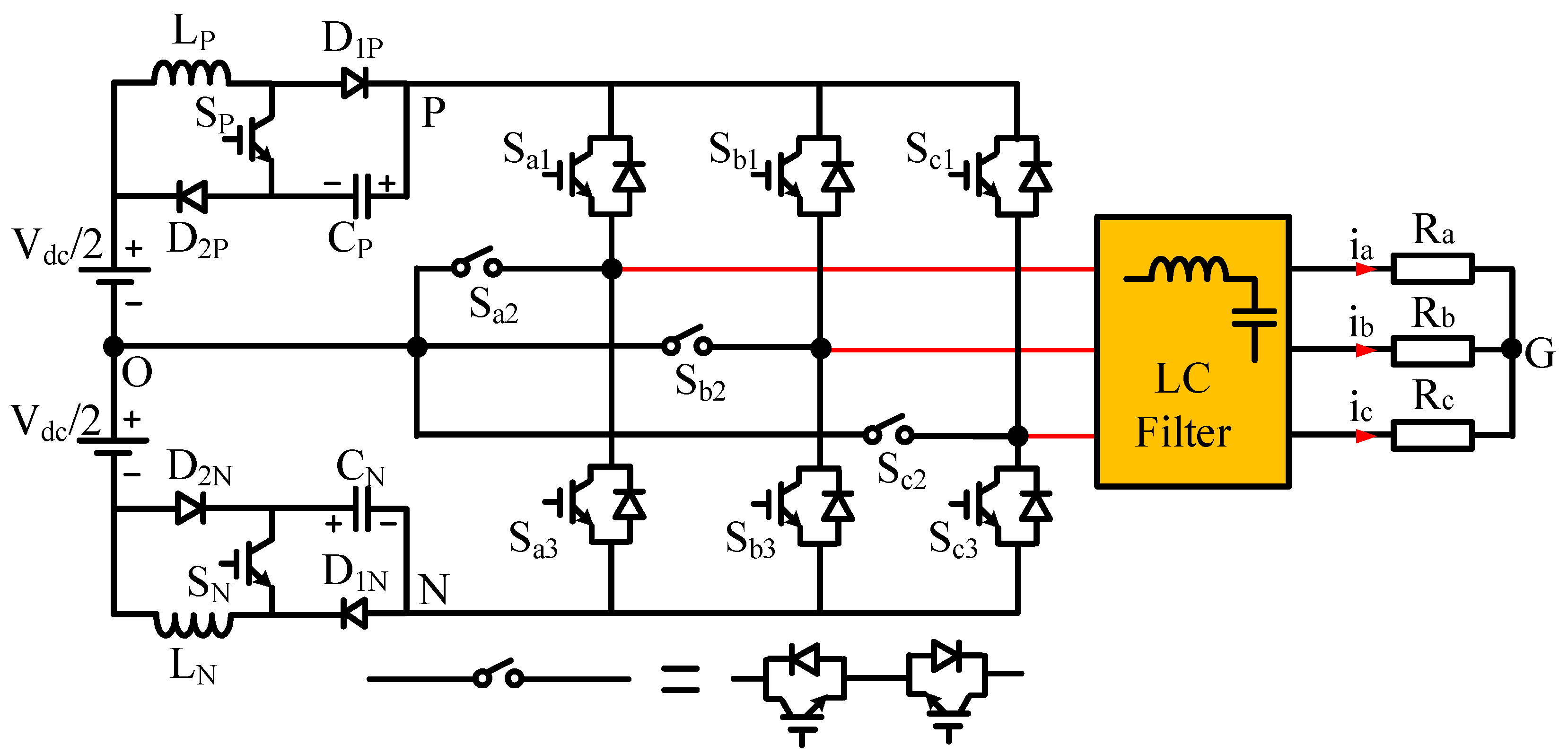

2. Three-Level DC-Link Type Quasi-Switched Boost T-Type Inverter Topology

2.1. Operating Principles

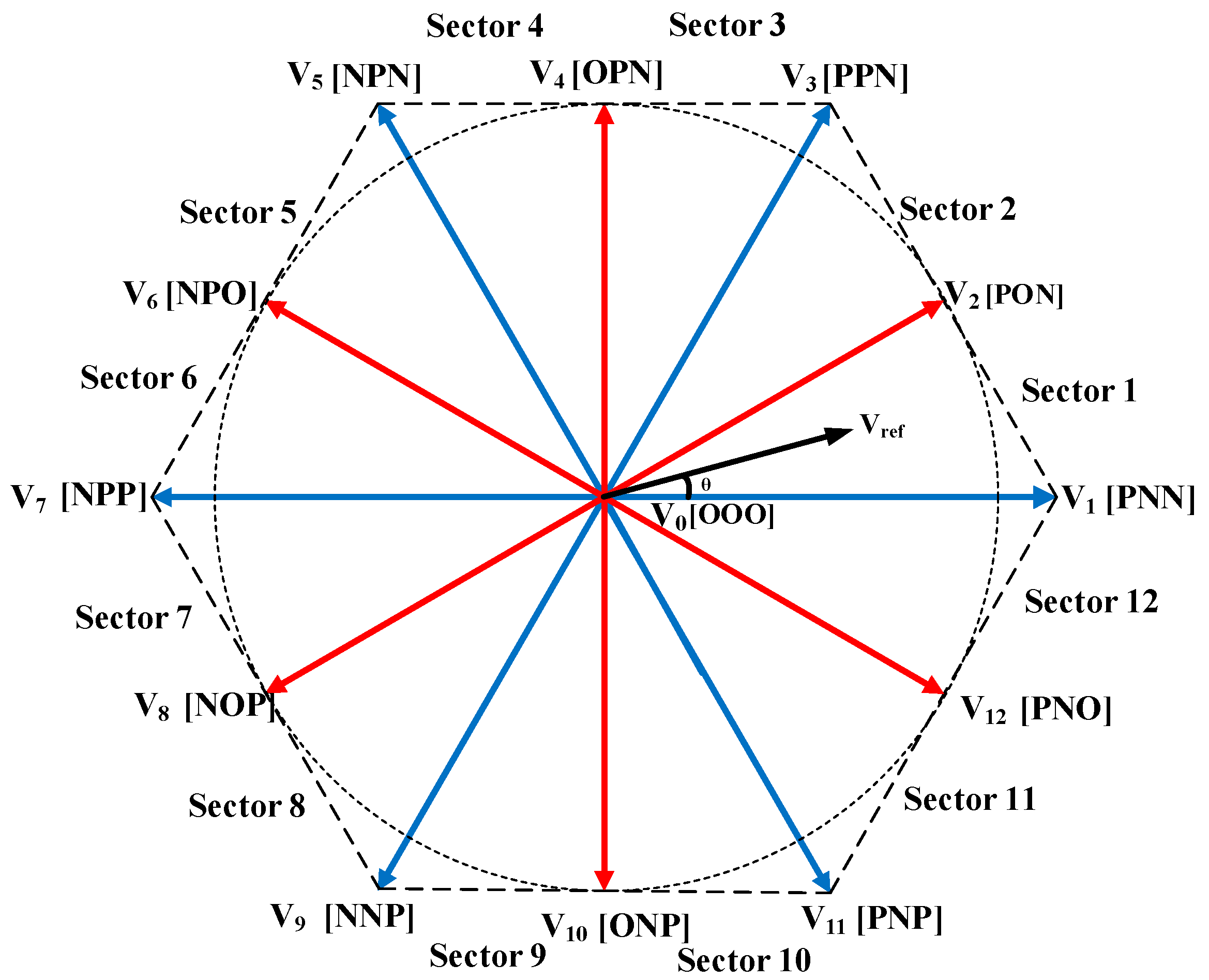

2.2. SVP Scheme to Reduce CMV

- (1)

- —reference vector,

- (2)

- —zero vector, large vector, and medium vector, respectively,

- (3)

- T—switching period of the inverter,

- (4)

- TZ, TM, TL—the on-times of , and , respectively.

2.3. Steady-State Analysis

- (1)

- —inductor current ripples of LP and LN, respectively,

- (2)

- —switching frequency of the inverter,

- (3)

- DST—ST duty ratio,

- (4)

- D0—duty cycle of SP and SN.

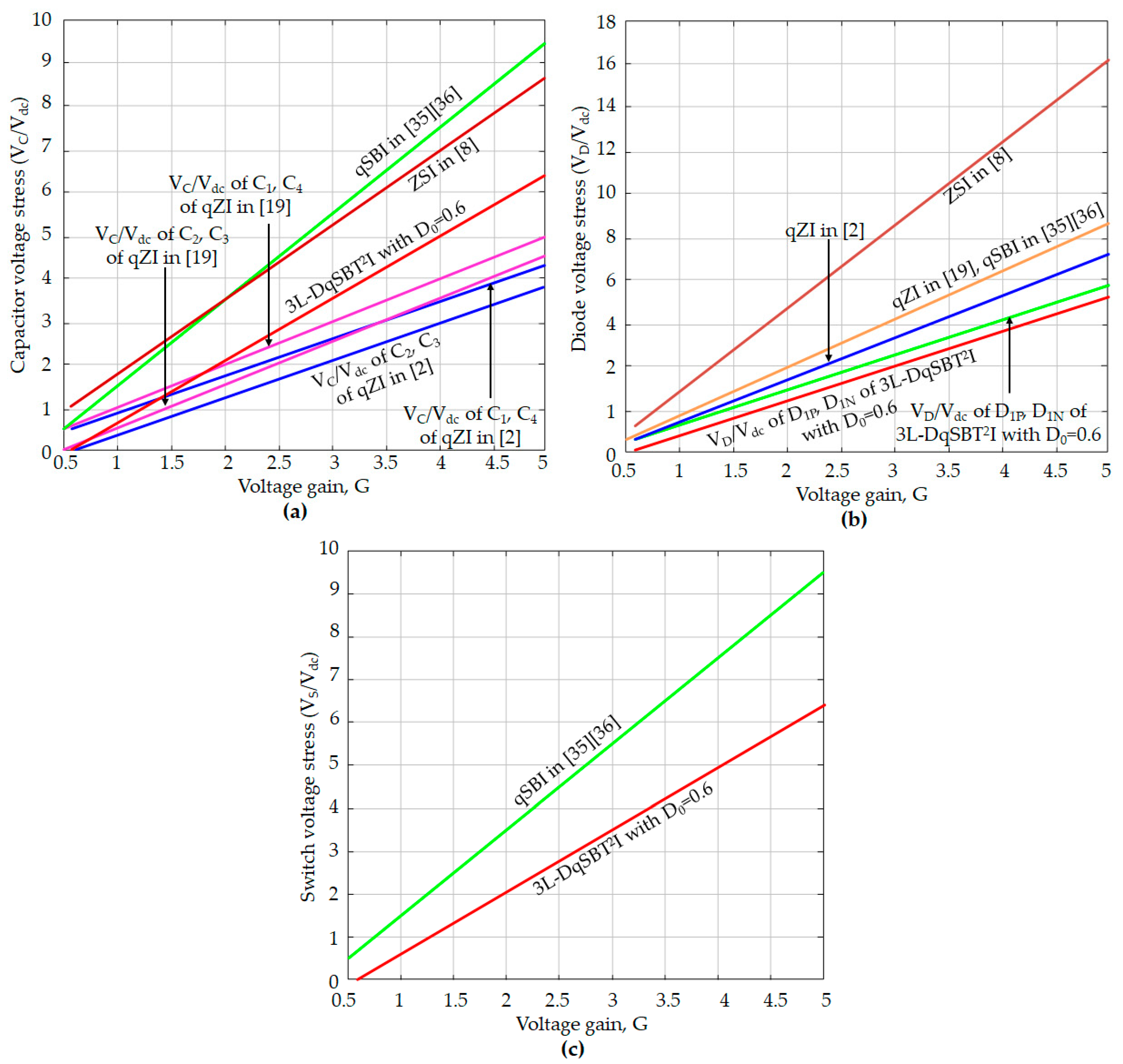

3. Comparison to Other Configurations

4. Simulation and Experimental Results

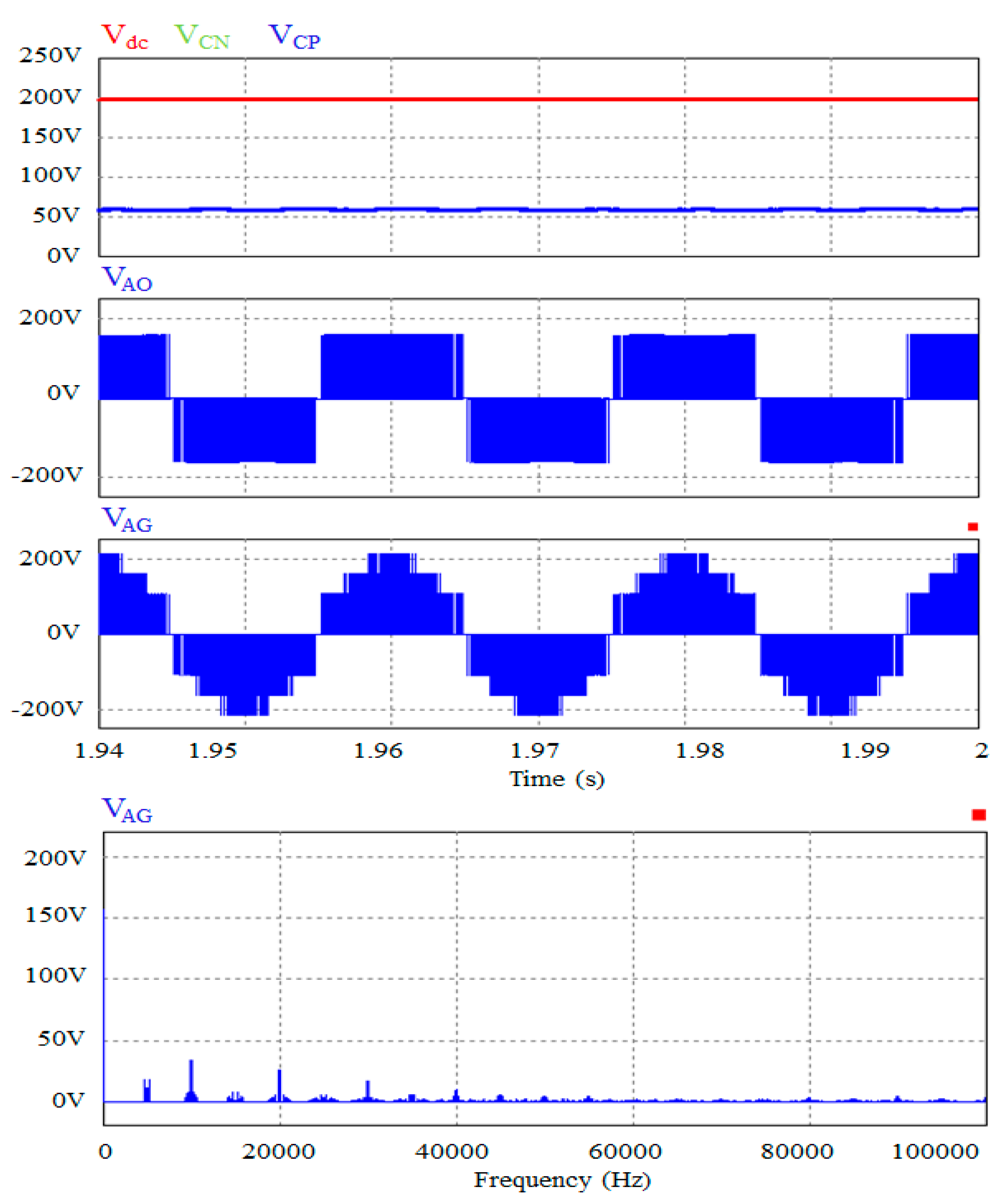

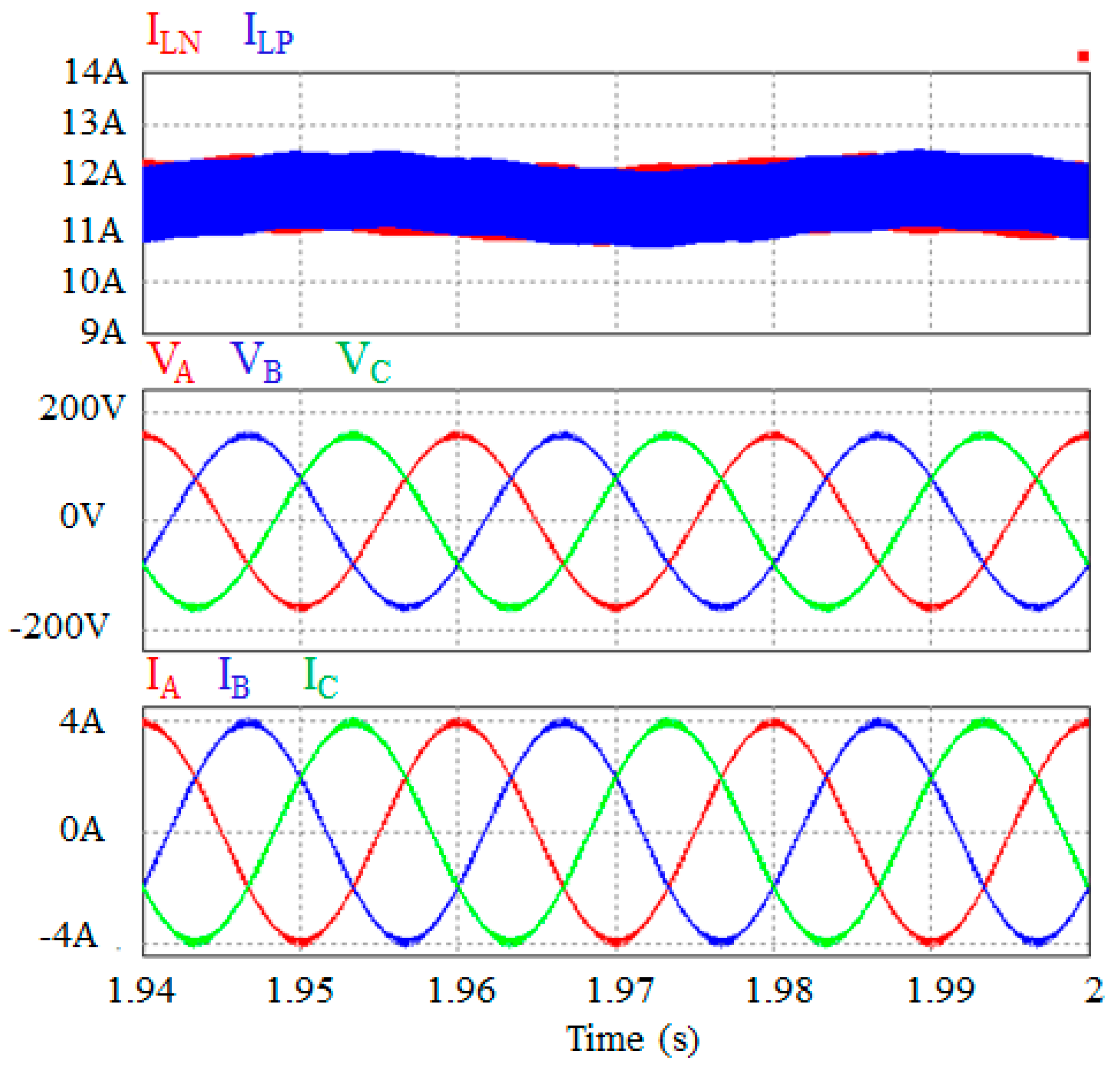

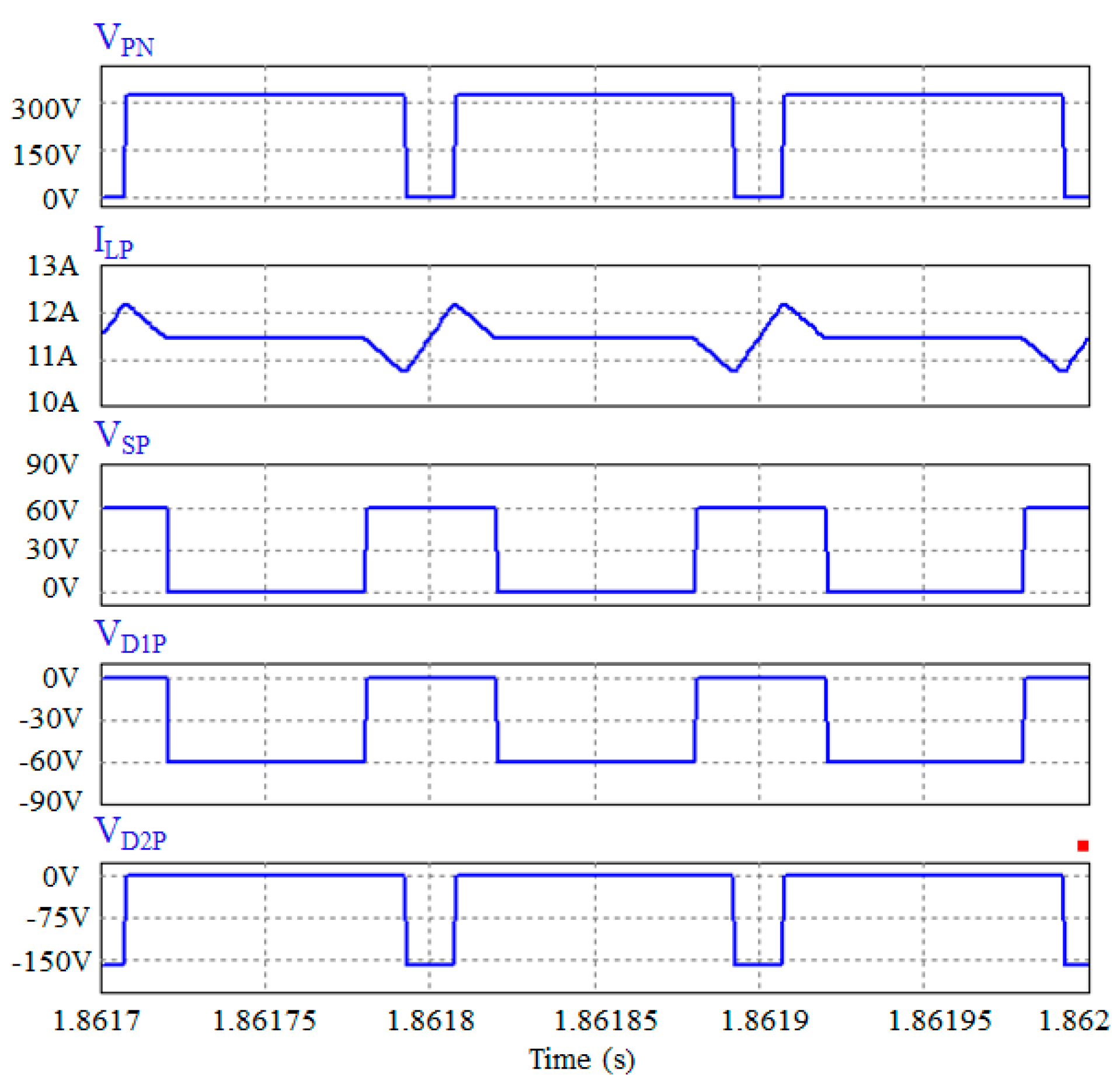

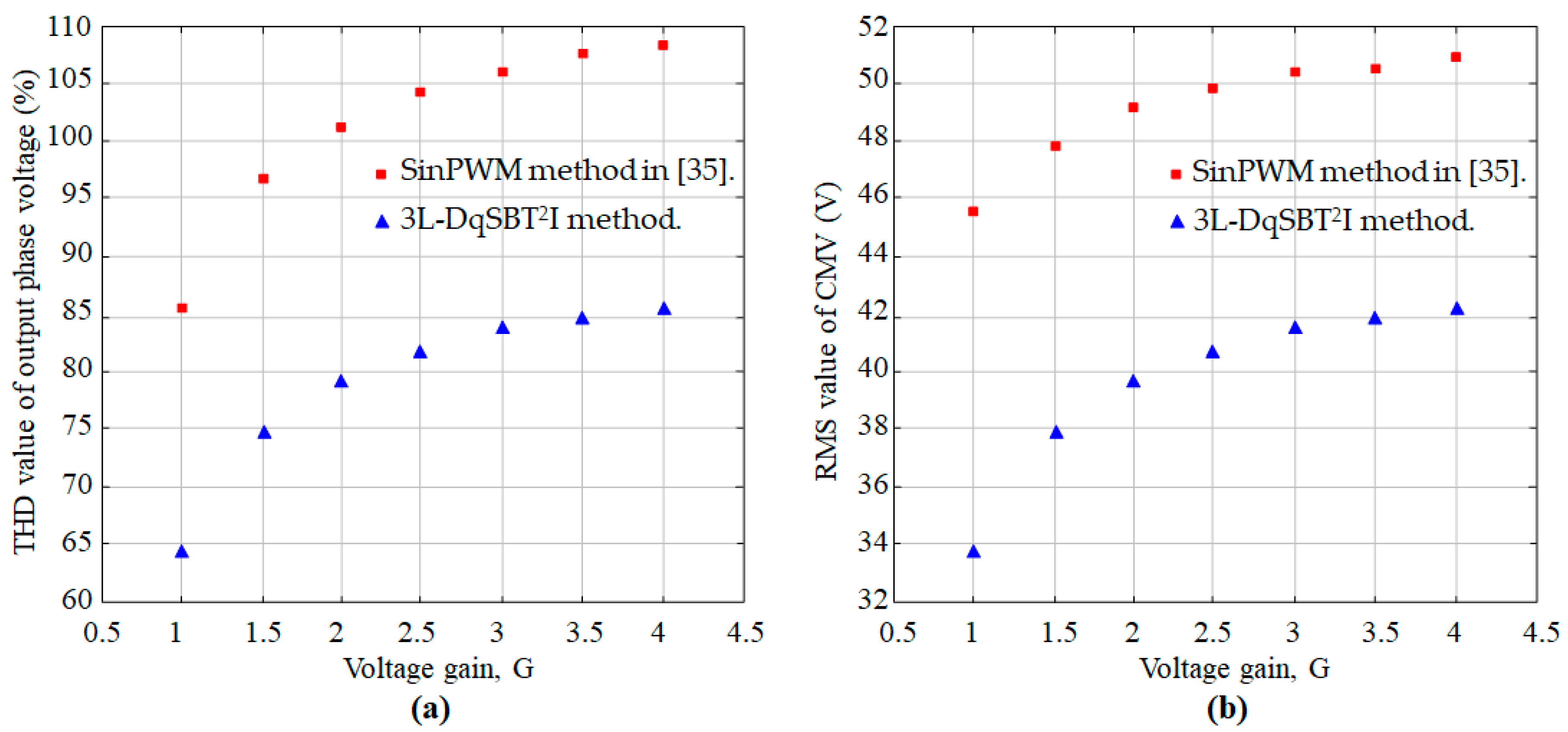

4.1. Simulation Results

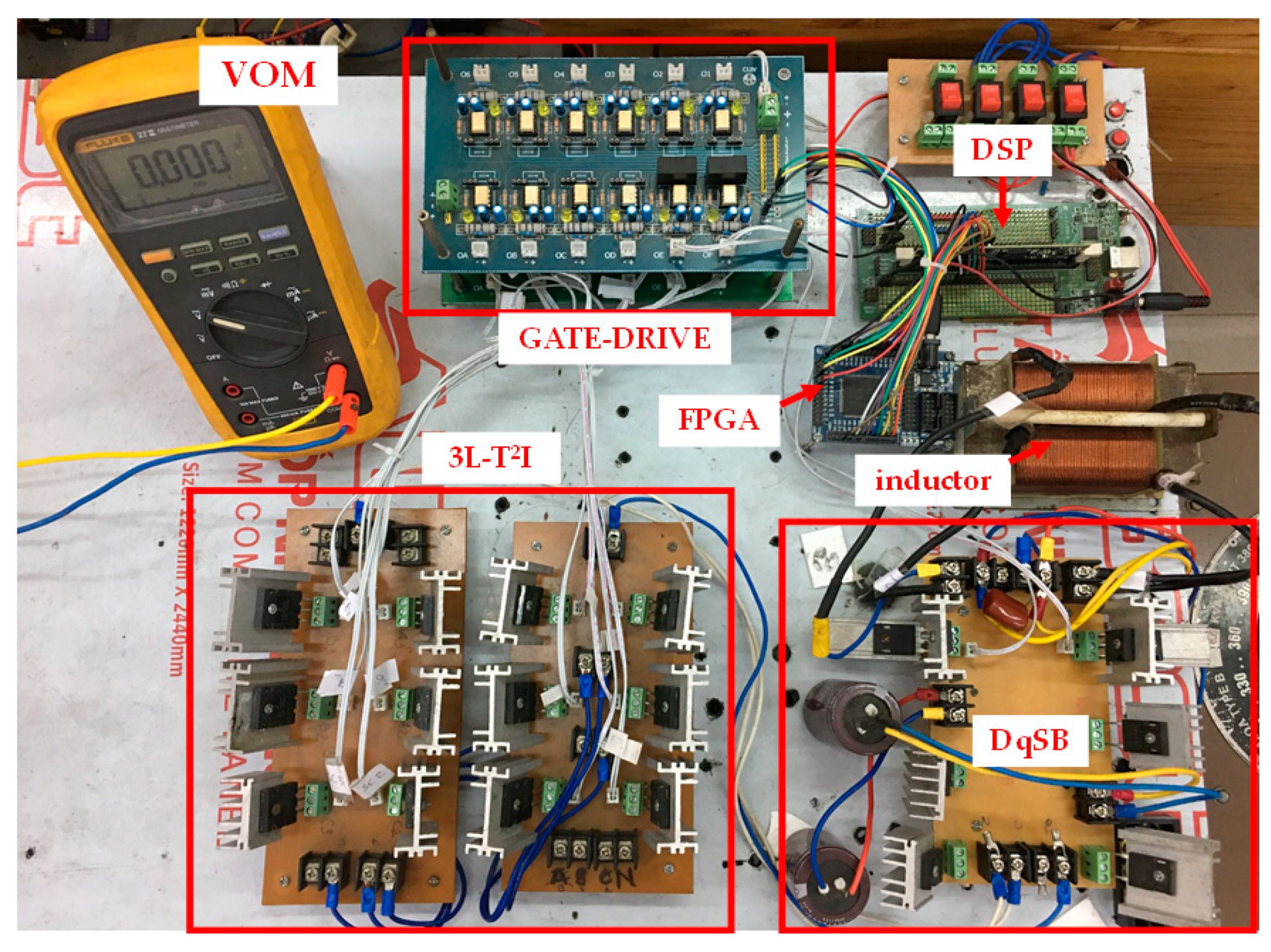

4.2. Experimental Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Nomenclature

| 3L-T2I | three-level T-Type inverter |

| 3L-DqSBT2I | three-Level DC-link type quasi switch boost T-type inverter |

| B | boost factor of the inverter |

| CMV | common-mode voltage |

| D0 | duty cycle of DqSB network’s active switches |

| DqSB | dc-link type of the qSB |

| DST | shoot-through duty ratio |

| FC | flying capacitor |

| f | switching frequency of the inverter |

| G | voltage gain of the inverter |

| IA | A-phase output load current |

| ILP | inductor LP current |

| inductor current ripple of LP | |

| ILN | inductor LN current |

| inductor current ripple of LN | |

| m | modulation index |

| MIs | multilevel inverters |

| NPC | neutral point clamped |

| NST | non-shoot-through |

| PV | photovoltaic systems |

| PWM | pulse width modulation |

| qSB | quasi-switch boost |

| qSBI | quasi-switch boost inverter |

| qZS | quasi-Z-source |

| qZSI | quasi-Z-source inverter |

| RMS | root mean square |

| ST | shoot-through |

| SVP | space vector pulse width modulation |

| T | switching period of the inverter |

| THD | total harmonic distortion |

| TM | drew-time of medium vector |

| TL | drew-time of large vector |

| TZ | drew-time of zero vector |

| UPS | uninterruptable power supply |

| zero vector | |

| large vectors | |

| medium vector | |

| VAB | output line-line voltage |

| VAG | A-phase output phase voltage |

| VAO | A-phase output pole voltage |

| VBO | B-phase output pole voltage |

| VC | capacitor voltage |

| VCMV | common-mode voltage |

| VCN | voltage across CN |

| VCO | C-phase output pole voltage |

| VCP | voltage across CP |

| Vdc | dc input voltage |

| VD1P | diode D1P voltage |

| VD2P | diode D2P voltage |

| VGO | common-mode voltage |

| VLP | voltage across LP |

| VLN | voltage across LN |

| VPN | dc-link voltage |

| reference vector | |

| VSP | switch SP voltage |

| Vx, peak | peak value of the first harmonic of output phase voltage |

| ZS | Z-source |

| ZSI | Z-source inverter |

References

- Schweizer, M.; Kolar, J.W. Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications. IEEE Trans. Power Electron. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Qin, C.; Zhang, C.; Chen, A.; Xing, X.; Zhang, G. A Space Vector Modulation Scheme of the Quasi-Z-Source Three-Level T-Type Inverter for Common-Mode Voltage Reduction. IEEE Trans. Ind. Electron. 2018, 65, 8340–8350. [Google Scholar] [CrossRef]

- Kim, H.S.; Kwon, Y.C.; Chee, S.J.; Sul, S.K. Analysis and Compensation of Inverter Nonlinearity for Three-Level T-Type Inverters. IEEE Trans. Power Electron. 2017, 32, 4970–4980. [Google Scholar] [CrossRef]

- Ho, A.V.; Chun, T.W. Topology and Modulation Scheme for Three-Phase Three-Level Modified Z-Source Neutral-Point-Clamped Inverter. IEEE Trans. Power Electron. 2019, 34, 11014–11025. [Google Scholar] [CrossRef]

- Guo, X.; Yang, Y.; Wang, B.; Blaabjerg, F. Leakage Current Reduction of Three-Phase Z-Source Three-Level Four-Leg Inverter for Transformerless PV System. IEEE Trans. Power Electron. 2018, 34, 6299–6308. [Google Scholar] [CrossRef]

- Zhou, Z.J.; Zhang, X.; Xu, P.; Shen, W.X. Single-Phase Uninterruptible Power Supply Based on Z-Source Inverter. IEEE Trans. Ind. Electron. 2008, 55, 2997–3004. [Google Scholar] [CrossRef]

- Sonar, S.; Singh, S. Improved Space Vector PWM Techniques of the Three level ZSI. In Proceedings of the 2019 International Conference on Computing, Power and Communication Technologies (GUCON), NCR New Delhi, India, 27–28 September 2019. [Google Scholar]

- Xing, X.; Zhang, C.; Chen, A.; He, J.; Wang, W.; Du, C. Space-Vector-Modulated Method for Boosting and Neutral Voltage Balancing in Z-Source Three-Level T-Type Inverter. IEEE Trans. Ind. Appl. 2016, 52, 1621–1631. [Google Scholar] [CrossRef]

- Zhang, J.; Wai, R.J. Novel Space-Vector Pulse-Width-Modulation Mechanism for Three-Level Neutral-Point-Clamped Z-Source Inverter. In Proceedings of the 2019 4th International Conference on Intelligent Green Building and Smart Grid (IGBSG), Yichang, China, 6–9 September 2019. [Google Scholar]

- Liu, H.; Chen, A.; Chen, J.; Du, C.; Zhang, C. Hybrid Modulation Strategy for Eliminating Low-Frequency Neutral-Point Voltage Oscillations in Z-Source NPC Three-Level Inverter. In Proceedings of the 2018 IEEE International Power Electronics and Application Conference and Exposition (PEAC), Shenzhen, China, 4–7 November 2018. [Google Scholar]

- Zhang, J.; Wai, R.J. Design of New SVPWM Mechanism for Three-Level NPC ZSI via Line-Voltage Coordinate System. IEEE Trans. Power Electron. 2020, 35, 8539–8606. [Google Scholar] [CrossRef]

- Ho, A.V.; Huynh, A.T.; Chun, T.W. Three-phase Modified Z-source Three-level T-Type Inverters with Continuous Source Current. In Proceedings of the 2019 International Aegean Conference on Electrical Machines and Power Electronics (ACEMP) & 2019 International Conference on Optimization of Electrical and Electronic Equipment (OPTIM), Istanbul, Turkey, 27–29 August 2019. [Google Scholar]

- Anderson, J.; Peng, F.Z. Four quasi-z-Source inverters. In Proceedings of the 2008 IEEE Power Electronics Specialists Conference, Rhodes, Greece, 15–19 June 2008. [Google Scholar]

- Stepenko, S.; Husev, O.; Vinnikov, D.; Pimentel, S.P.; Prystupa, A. Experimental Efficiency and Thermal Parameters Evaluation in Full-SiC Quasi-Z-Source Inverter. In Proceedings of the IEEE 60th International Scientific Conference on Power and Electrical Engineering of Riga Technical University (RTUCON) 2019, Riga, Latvia, 7–9 October 2019. [Google Scholar]

- Makovenko, E.; Husev, O.; Cadaval, E.R.; Vinnikov, D.; Stepenko, S. Single-Phase Three-Level qZ-Source Inverter Connected to the Grid with Battery Storage and Active Power Decoupling Function. In Proceedings of the International Scientific Conference on Power and Electrical Engineering 2018, Barcelona, Spain, 26–27 July 2018. [Google Scholar]

- Stepenko, S.; Husev, O.; Vinnikov, D.; Fesenko, A.; Clemente, C.R.; Pimentel, S.P.; Santasheva, E. Experimental Comparison of Two-Level Full-SiC and Three-Level Si–SiC Quasi-Z-Source Inverters for PV Applications. Energies 2019, 12, 2509. [Google Scholar] [CrossRef]

- Stepenko, S.; Husev, O.; Vinnikov, D.; Fesenko, A.; Matiushkin, O. Feasibility Study of Interleaving Approach for Quasi-Z-Source Inverter. Electronics 2020, 9, 277. [Google Scholar] [CrossRef]

- Roncero-Clemente, C.; Romero-Cadaval, E.; Pires, V.F.; Martins, J.F.; Vilhena, N.; Husev, O. Efficiency and loss distribution analysis of the 3L-Active NPC qZS inverter. In Proceedings of the 2018 IEEE 12th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG 2018), Doha, Qatar, 10–12 April 2018. [Google Scholar]

- Pires, V.F.; Cordeiro, A.; Foito, D.; Martins, J.F. Quasi-Z-Source Inverter With a T-Type Converter in Normal and Failure Mode. IEEE Trans. Power Electron. 2016, 31, 7462–7470. [Google Scholar] [CrossRef]

- Ruiz-Cortés, M.; Romero-Cadaval, E.; Roncero-Clemente, C.; González-Romera, E.; Husev, O. Evaluation of losses in three-level neutral-point-clamped and T-type quasi-Z-source inverters with modified carrier based modulation method. In Proceedings of the 2017 11th IEEE International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), Cadiz, Spain, 4–6 April 2017. [Google Scholar]

- Pan, X.; Pang, Z.; Li, L.; Zhao, F. Input Current Ripples Cancellation in A New Three-level Neutral-Point-Clamped Bi-directional Coupled Quasi Z-Source Inverter. In Proceedings of the 2019 IEEE International Conference on Industrial Technology (ICIT), Melbourne, Australia, 13–15 February 2019. [Google Scholar]

- Ahmadzadeh, T.; Babaei, I. Improved quasi-Z-source based three-phase three-level neutral point clamped inverter. In Proceedings of the 2018 9th Annual Power Electronics, Drives Systems and Technologies Conference (PEDSTC), Tehran, Iran, 13–15 February 2018. [Google Scholar]

- Wang, T.; Wang, X.; He, Y.; Chen, X.; Ruan, X.; Zhang, Z. An Improved Quasi-Z-Source Three-Level T-Type Inverter and Its Modulation Scheme. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020. [Google Scholar]

- Aly, M.; Mayorga, N.; Llor, A.M. A Simplified SVPWM Method for Neutral Point Voltage Control and Common Mode Voltage Reduction in Three-Level qZS T-type PV Inverters. In Proceedings of the 2020 IEEE International Conference on Industrial Technology (ICIT), Buenos Aires, Argentina, 26–28 February 2020. [Google Scholar]

- Komurcugil, H.; Bayhan, S. PI and Sliding Mode Based Control Strategy for Three-Phase Grid-Tied Three-Level T-Type qZSI. In Proceedings of the IECON 2019—45th Annual Conference of the IEEE Industrial Electronics Society, Lisbon, Portugal, 14–17 October 2019. [Google Scholar]

- Nguyen, M.K.; Le, T.V.; Park, S.J.; Lim, Y.C. A Class of Quasi-Switched Boost Inverters. IEEE Trans. Ind. Electron. 2015, 62, 1526–1536. [Google Scholar] [CrossRef]

- Nguyen, M.K.; Tran, T.T.; Lim, Y.C. A Family of PWM Control Strategies for Single-Phase Quasi-Switched-Boost Inverter. IEEE Trans. Power Electron. 2019, 34, 1458–1469. [Google Scholar] [CrossRef]

- Do, D.T.; Nguyen, M.K. Three-Level Quasi-Switched Boost T-Type Inverter: Analysis, PWM Control, and Verification. IEEE Trans. Ind. Electron. 2018, 65, 8320–8329. [Google Scholar] [CrossRef]

- Do, D.T.; Nguyen, M.K.; Quach, T.H.; Tran, V.T.; Blaabjerg, F.; Vilathgamuwa, M. A PWM Scheme for a Fault-Tolerant Three-Level Quasi-Switched Boost T-Type Inverter. IEEE J. Emerg. Sel. Top. Power Electron. 2019. [Google Scholar] [CrossRef]

- Do, D.T.; Nguyen, M.K.; Ngo, V.T.; Quach, T.H.; Tran, V.T. Common Mode Voltage Elimination for Quasi-Switch Boost T-Type Inverter Based on SVM Technique. Electronics 2020, 9, 76. [Google Scholar] [CrossRef]

- Do, D.T.; Nguyen, M.K.; Quach, T.H.; Tran, V.T.; Le, C.B.; Lee, K.W.; Cho, G.B. Space Vector Modulation Strategy for Three-Level Quasi-Switched Boost T-Type Inverter. In Proceedings of the 2018 IEEE 4th Southern Power Electronics Conference (SPEC), Singapore, 10–13 December 2018. [Google Scholar]

- Tran, V.T.; Do, D.T.; Nguyen, M.K.; Nguyen, D.T. Space Vector Modulation Scheme for Three-Level T-Type Quasi-Switched Boost Inverter to Reduce Common Mode Voltage. In Proceedings of the 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019—ECCE Asia), Busan, Korea, 27–30 May 2019. [Google Scholar]

- Duong, T.D.; Nguyen, M.K.; Lim, Y.C.; Choi, J.H.; Vilathgamuwa, D.M.; Walker, G. A study on DC-link-type quasi-switched-boost inverters with improved voltage gain. In Proceedings of the 2019 21st European Conference on Power Electronics and Applications (EPE ‘19 ECCE Europe), Genova, Italy, 3–5 September 2019. [Google Scholar]

- Nguyen, M.K.; Duong, T.D.; Lim, Y.C.; Choi, J.H.; Vilathgamuwa, D.M.; Walker, G.R. DC-Link Quasi-Switched Boost Inverter With Improved PWM Strategy and its Comparative Evaluation. IEEE Access 2020, 8, 53857–53867. [Google Scholar] [CrossRef]

- Sahoo, M.; Keerthipati, S. A Three-Level LC-Switching-Based Voltage Boost NPC Inverter. IEEE Trans. Ind. Electron. 2017, 64, 2876–2883. [Google Scholar] [CrossRef]

- Sahoo, M.; Keerthipati, S. Fault tolerant three-level boost inverter with reduced source and LC count. IET Power Electron. 2018, 11, 399–405. [Google Scholar] [CrossRef]

| Mode | ON Switches | ON Diodes | Vx |

|---|---|---|---|

| NST 1 | SP, SN | D2P, D2N | +VPN/2, 0 or −VPN/2 |

| NST 2 | Sx1 or Sx2 or Sx3 | D1P, D1N, D2P, D2N | +VPN/2, 0 or −VPN/2 |

| ST | Sx1, Sx2, Sx3 | D1P, D1N | 0 |

| ZSI in [8] | qZSI with PWM in [19] | qZSI with PWM in [2] | qSBI with PWM in [34] | qSBI with PWM in [35] | Proposed 3L-DqSBT2I | |

|---|---|---|---|---|---|---|

| Boost factor, B | 1/(1 − 2DST) | 1/(1 − 2DST) | 1/(1 − 2DST) | 1/(1 − 2DST) | 1/(1 − 2DST) | (1 − D0)/(1 −D0 − DST) |

| Voltage gain, G | m·B/ | m·B/2 | m·B/ | m·B/2 | m·B/2 | m·B/ |

| Capacitor voltage stress, Vc/Vdc | (1 − DST)B | DST·B/2, (1 − DST)B/2 | DST·B/2, (1 − DST)B/2 | B/2 | B/2 | 0.5·DST/(1 − D0 − DST) |

| Diode voltage stress, VD/Vdc | B | B/2 | B/2 | B/2 | B/2 | 0.5·DST/(1 − D0 − DST), B/2 |

| Switch voltage stress, VS/Vdc | NA | NA | NA | B/2 | B/2 | 0.5·DST/(1 − D0 − DST) |

| Inductors | 2 | 4 | 4 | 2 | 1 | 2 |

| Capacitors | 2 | 4 | 4 | 2 | 2 | 2 |

| Diodes | 2 | 2 | 2 | 4 | 4 | 4 |

| Switches | NA | NA | NA | 2 | 2 | 2 |

| Input current ripple | Very high | Small | Small | Small | Small | High |

| Parameter/Components | Values | |

|---|---|---|

| DC input voltage | Vdc | 200 V |

| Output voltage | Vx,RMS | 110 VRMS |

| Output frequency | fo | 50 Hz |

| Carrier frequency | fs | 5 kHz |

| ST duty cycle | DST | 0.15 |

| Modulation index | m | 0.85 |

| Boost inductors | LP = LN | 1 mH/20 A |

| Capacitors | C1 = C2 | 2200 μF/600 V |

| LC filter | Lf and Cf | 3 mH and 10 μF |

| Diode | D1P,D2P,D1N,D2N | DSEI60-12A (1200 V, 60 A) |

| Switches | SP and SN | 6R045A (650 V, 60 A) |

| Sx1 and Sx3 | FGL40N150D (1500 V, 40 A) | |

| Sx2 | FGL40N120D (1200 V, 40 A) | |

| Resistor load | R | 40 Ω |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tran, V.-T.; Do, D.-T.; Do, V.-D.; Nguyen, M.-K. A Three-Level DC-Link Quasi-Switch Boost T-Type Inverter with Voltage Stress Reduction. Energies 2020, 13, 3727. https://doi.org/10.3390/en13143727

Tran V-T, Do D-T, Do V-D, Nguyen M-K. A Three-Level DC-Link Quasi-Switch Boost T-Type Inverter with Voltage Stress Reduction. Energies. 2020; 13(14):3727. https://doi.org/10.3390/en13143727

Chicago/Turabian StyleTran, Vinh-Thanh, Duc-Tri Do, Van-Dung Do, and Minh-Khai Nguyen. 2020. "A Three-Level DC-Link Quasi-Switch Boost T-Type Inverter with Voltage Stress Reduction" Energies 13, no. 14: 3727. https://doi.org/10.3390/en13143727

APA StyleTran, V.-T., Do, D.-T., Do, V.-D., & Nguyen, M.-K. (2020). A Three-Level DC-Link Quasi-Switch Boost T-Type Inverter with Voltage Stress Reduction. Energies, 13(14), 3727. https://doi.org/10.3390/en13143727