A Single-Phase Nine-Level Boost Inverter

Abstract

:1. Introduction

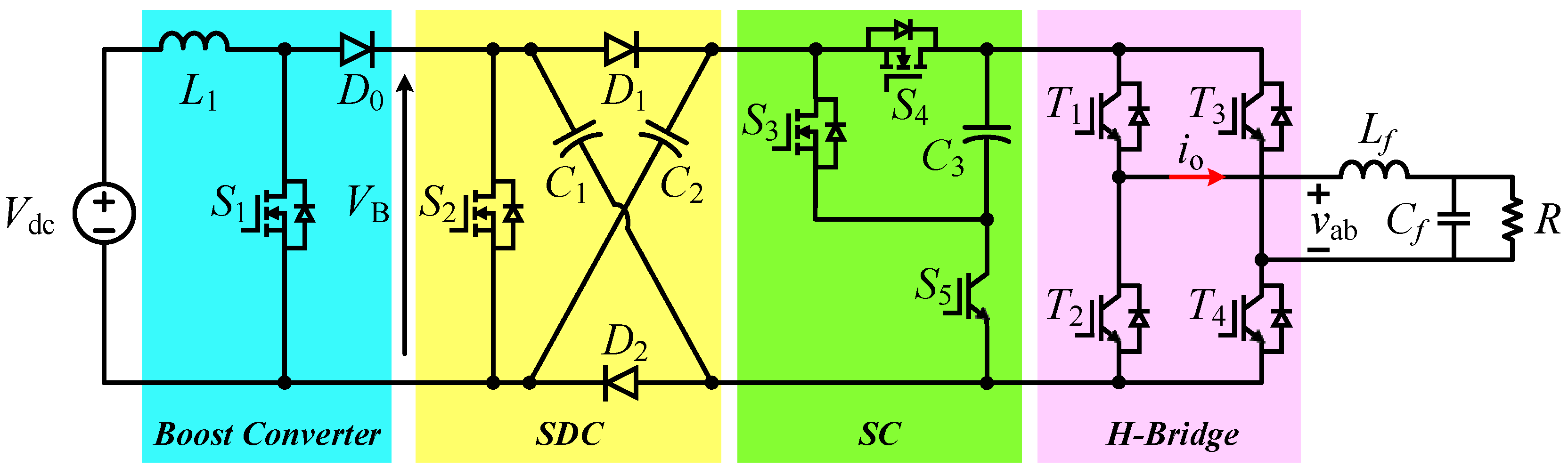

2. Proposed Single-Phase Nine-Level Boost Inverter

2.1. Operating Principle of the Proposed Inverter

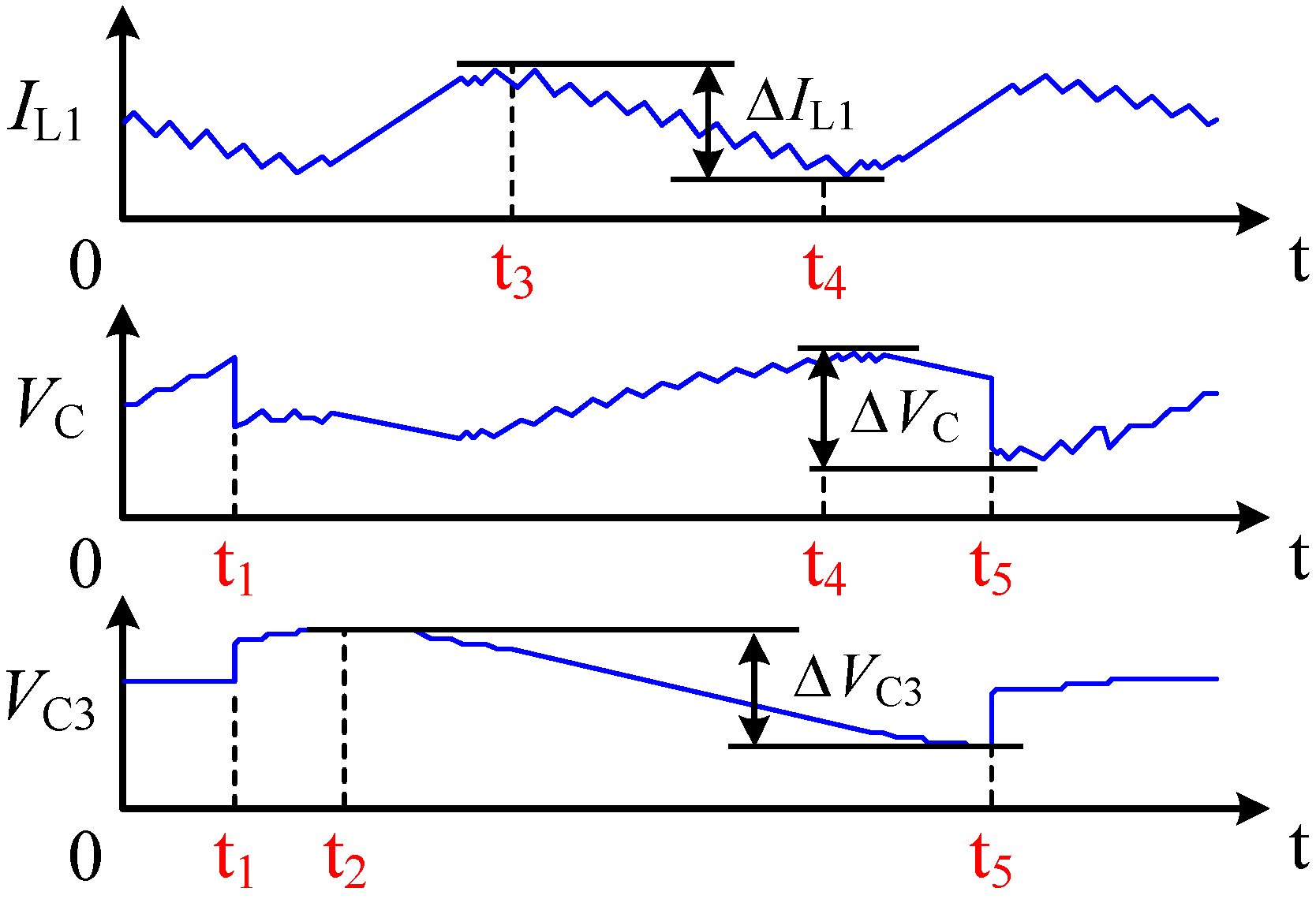

2.2. Circuit Analysis of the Proposed Inverter

3. Inductor and Capacitor Selections

4. Simulation and Experimental Results

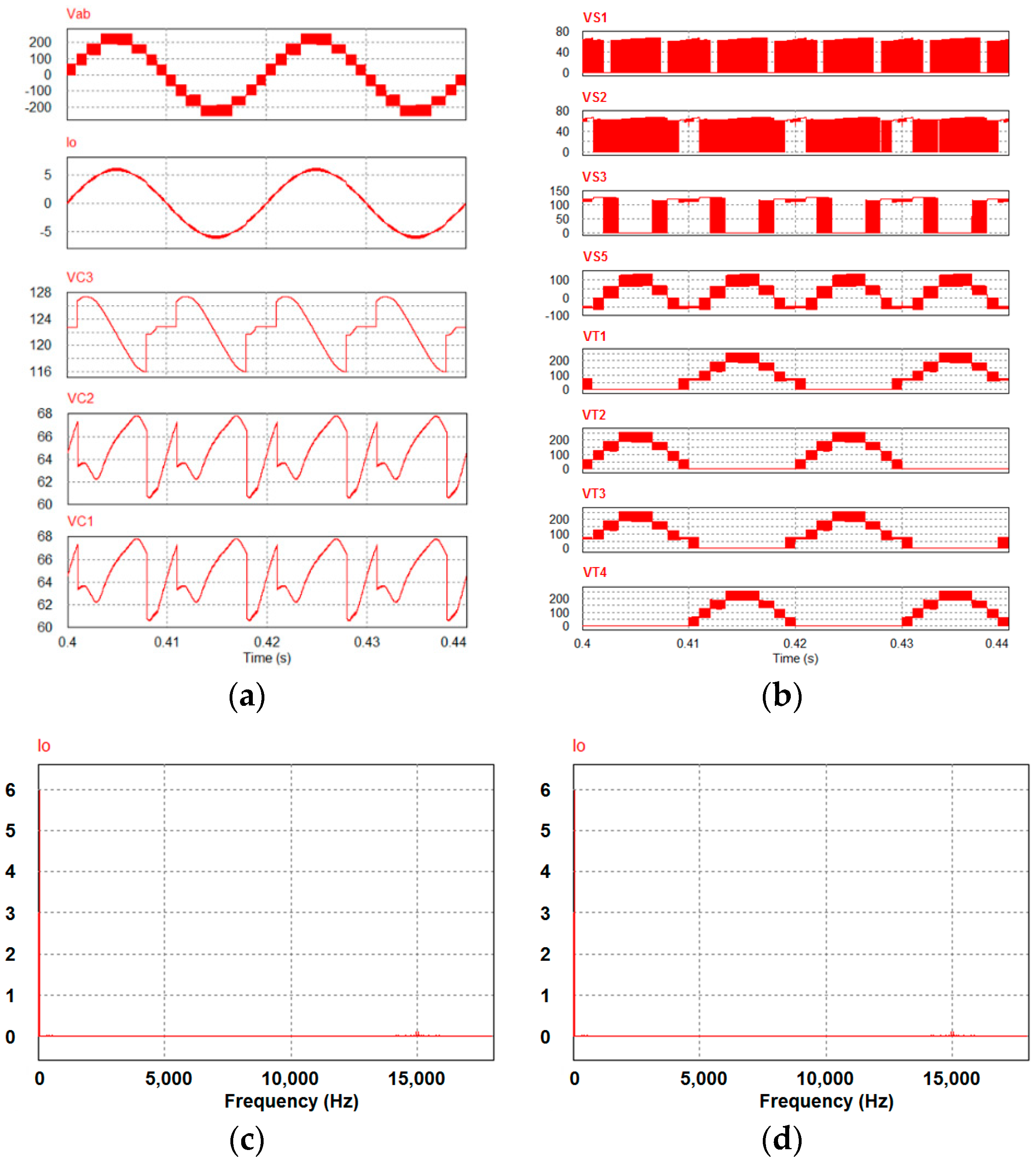

4.1. Simulation Results

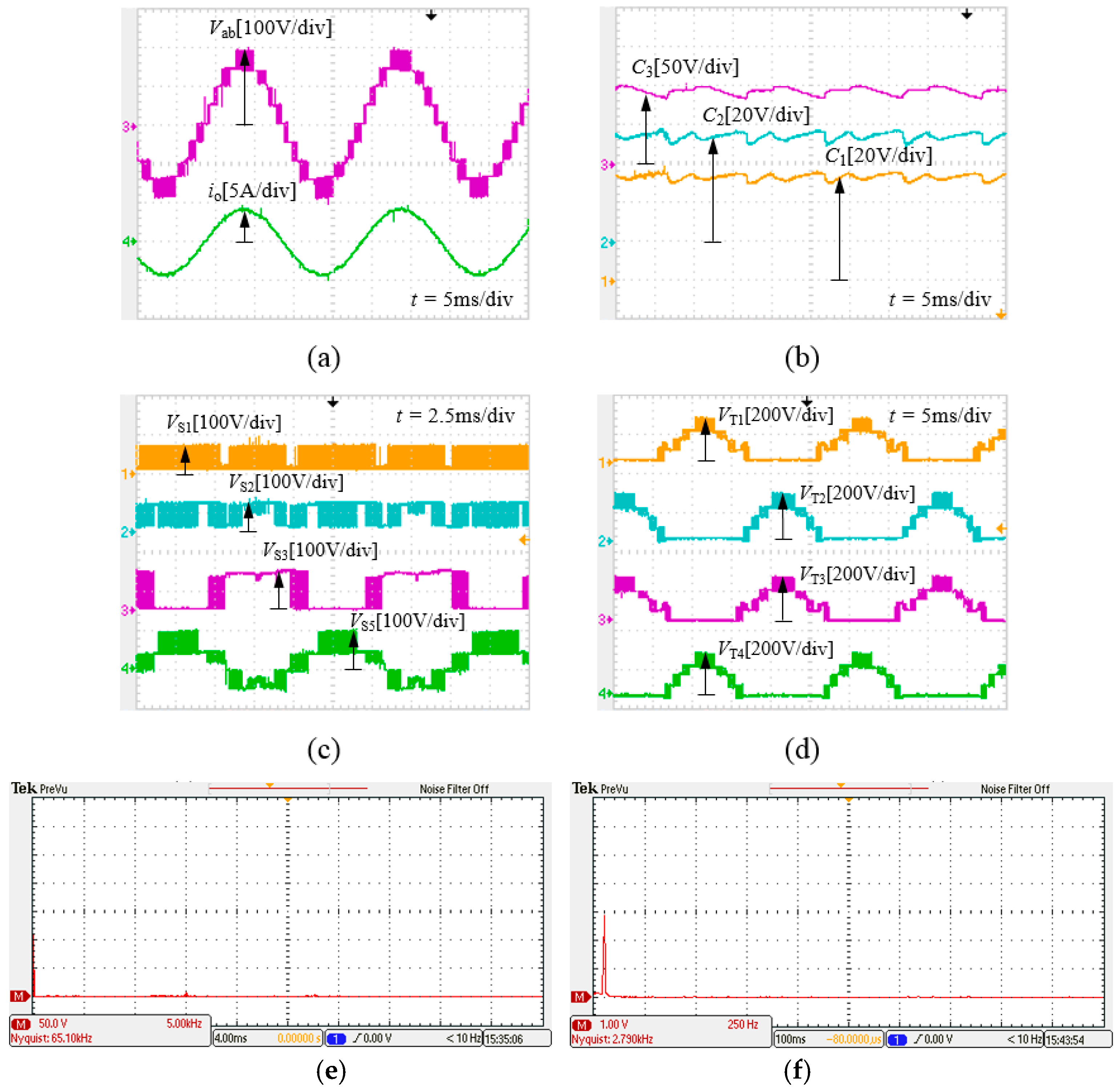

4.2. Experimental Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Nomenclature

| Am | peak amplitude of control waveform ex |

| B | boost factor |

| CHB | cascade H-bridge |

| davg | average duty cycle of the boost inductor in each period Ts |

| dL1 | duty cycle of the boost inductor |

| dS1 | duty cycle generated by switch S1 |

| dS2 | duty cycle generated by switch S2 |

| dx | duty cycle generated by switch S1 and S2 |

| en | constant voltage |

| ex | control waveform |

| fout | output frequency |

| FC | flying-capacitor |

| G | voltage gain |

| io | load current |

| Io | amplitude of output current |

| IL1 | average input current |

| ΔIL1 | current ripple of the inductor |

| KL | current ripple factor of the inductor |

| MI | multilevel inverter |

| NLBI | nine-level boost inverter |

| NPC | neutral-point-clamped |

| PWM | pulse-width modulation |

| SC | switched-capacitor |

| SCMI | switched-capacitor multilevel inverter |

| SDC | switch-diode-capacitor |

| Tavg | average time interval of the charging inductor mode during the period Ts |

| Ts | period time |

| Vab | output voltage |

| VB | boost voltage |

| Vdc | dc source |

| VL | inductor L1 voltage |

References

- Abu-Rub, H.; Holtz, J.; Rodriguez, J.; Baoming, G. Medium-Voltage Multilevel Converters-State of the Art, Challenges, and Requirements in Industrial Applications. IEEE Trans. Ind. Electron. 2010, 57, 2581–2596. [Google Scholar] [CrossRef]

- Soeiro, T.B.; Kolar, J.W. The new high-efficiency hybrid neutral-point-clamped converter. IEEE Trans. Ind. Electron. 2013, 60, 1919–1935. [Google Scholar] [CrossRef]

- Dargahi, S.; Babaei, E.; Eskandari, S.; Dargahi, V.; Sabahi, M. Flying-capacitor stacked multicell multilevel voltage source inverters: Analysis and modelling. IET Power Electron. 2014, 7, 2929–2987. [Google Scholar] [CrossRef]

- Zha, X.; Xiong, L.; Gong, J.; Liu, F. Cascaded multilevel converter for medium-voltage motor drive capable of regenerating with part of cells. IET Power Electron. 2014, 7, 1313–1320. [Google Scholar] [CrossRef]

- Tran, T.T.; Nguyen, M.K. Cascaded five-level quasi-switched-boost inverter for single-phase grid-connected system. IET Power Electron. 2017, 10, 1896–1903. [Google Scholar] [CrossRef]

- Rodriguez, P.; Bellar, M.D.; Munoz-Aguilar, R.S.; Busquets-Monge, S.; Blaabjerg, F. Multilevel-clamped multilevel converters (MLC2). IEEE Trans. Power Electron. 2012, 27, 1055–1060. [Google Scholar] [CrossRef]

- Husev, O.; Roncero-Clemente, C.; Romero-Cadaval, E.; Vinnikov, D.; Stepenko, S. Single phase three-level neutral-point-clamped quasi-Z-source inverter. IET Power Electron. 2015, 8, 1–10. [Google Scholar] [CrossRef]

- Teymour, H.R.; Sutanto, D.; Muttaqi, K.M.; Ciufo, P. A novel modulation technique and a new balancing control strategy for a single-phase five-level ANPC converter. IEEE Trans. Ind. Appl. 2015, 51, 1215–1227. [Google Scholar] [CrossRef]

- Ajami, A.; Oskuee, M.; Mokhberdoran, A.; Bossche, A.V.D. Developed cascaded multilevel inverter topology to minimize the number of circuit devices and voltage stresses of switches. IET Power Electron. 2014, 7, 459–466. [Google Scholar] [CrossRef]

- Tsang, K.; Chan, W. Single DC source three-phase multilevel inverter using reduced number of switches. IET Power Electron. 2014, 7, 775–783. [Google Scholar] [CrossRef]

- Wang, K.; Li, Y.; Zedong, Z.; Xu, L. Voltage balancing and fluctuation-suppression methods of floating capacitors in a new modular multilevel converter. IEEE Trans. Ind. Electron. 2013, 60, 1943–1954. [Google Scholar] [CrossRef]

- Najafi, E.; Yatim, A.H.M. Design and implementation of a new multilevel inverter topology. IEEE Trans. Ind. Electron. 2012, 59, 4148–4154. [Google Scholar] [CrossRef]

- Hinago, Y.; Koizumi, H. A single-phase multilevel inverter using switched series/parallel dc voltage sources. IEEE Trans. Ind. Electron. 2010, 57, 2643–2650. [Google Scholar] [CrossRef]

- Rahim, N.A.; Chaniago, K.; Selvaraj, J. Single-phase seven-level grid-connected inverter for photovoltaic system. IEEE Trans. Ind. Electron. 2011, 58, 2435–2443. [Google Scholar] [CrossRef]

- Hinago, Y.; Koizumi, H. A switched-capacitor inverter using series/parallel conversion with inductive load. IEEE Trans. Ind. Electron. 2012, 59, 878–887. [Google Scholar] [CrossRef]

- Raman, R.S.; Ye, Y.; Cheng, E.W.K. Switched-capacitor multilevel inverters for high frequency ac microgrids. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 2559–2564. [Google Scholar] [CrossRef]

- Barzegarkhoo, R.; Kojabadi, H.M.; Zamiry, E.; Vosooghi, N.; Chang, L. Generalized structure for a single phase switched-capacitor multilevel inverter using a new multiple dc link producer with reduced number of switches. IEEE Trans. Power Electron. 2016, 31, 5604–5617. [Google Scholar] [CrossRef]

- Tsunoda, A.; Hinago, Y.; Koizumi, H. Level- and phase-shifted PWM for seven-level switched-capacitor inverter using series/parallel conversion. IEEE Trans. Ind. Electron. 2014, 61, 4011–4021. [Google Scholar] [CrossRef]

- Ye, Y.; Cheng, K.W.E.; Liu, J.; Ding, K. A step-up switched-capacitor multilevel inverter with self-voltage balancing. IEEE Trans. Ind. Electron. 2014, 61, 6672–6680. [Google Scholar] [CrossRef]

- Babaei, E.; Gowgani, S.S. Hybrid multilevel inverter using switched-capacitor units. IEEE Trans. Ind. Electron. 2014, 61, 4614–4621. [Google Scholar] [CrossRef]

- Ngo, B.B.; Nguyen, M.K.; Kim, J.H.; Zare, F. Single-phase multilevel inverter based on switched-capacitor structure. IET Power Electron. 2018, 11, 1858–1865. [Google Scholar] [CrossRef]

- Liu, J.; Cheng, K.W.E.; Ye, Y. A cascaded multilevel inverter based on switched-capacitor for high-frequency ac power distribution system. IEEE Trans. Power Electron. 2014, 29, 4219–4230. [Google Scholar] [CrossRef]

- Sun, X.; Wang, B.; Zhou, Y.; Wang, W.; Du, H.; Lu, Z. A single dc source cascaded seven-level inverter integrating switched-capacitor techniques. IEEE Trans. Ind. Electron. 2016, 63, 7184–7194. [Google Scholar] [CrossRef]

- Gao, F. An enhanced single phase step-up five-level inverter. IEEE Trans. Power Electron. 2016, 31, 8024–8030. [Google Scholar] [CrossRef]

- Hou, S.; Chen, J.; Sun, T.; Bi, X. Multi-input step-up converters based on the switched-diode-capacitor voltage accumulator. IEEE Trans. Power Electron. 2016, 31, 381–393. [Google Scholar] [CrossRef]

| Topology | Literature | Advantages | Disadvantages |

|---|---|---|---|

| Series-connected DC voltage sources | Proposed in Reference [12] |

|

|

| Switched serial/parallel DC voltage sources | Proposed in Reference [13] |

|

|

| Additional boost converter | Proposed in References [14,24] |

|

|

| Series/parallel connection | Proposed in References [15,18] |

|

|

| Based on switched capacitor | Proposed in References [16,17,19,20,21] |

|

|

| Cascaded multilevel inverter | Proposed in References [22,23] |

|

|

| State | Stage | ON Diodes | ON Switches | Capacitor State | Inductor L1 State | Output Voltage | ||

|---|---|---|---|---|---|---|---|---|

| C1 | C2 | C3 | ||||||

| 1 | 1, 7 | S1, S4, T2, T4 | I | I | I | + | 0 | |

| 2 | 1, 7 | D0, D1, D2 | S4, T2, T4 | + | + | I | − | 0 |

| 3 | 1, 2, 6, 7 | D1, D2 | S1, S4, T1, T4 | − | − | I | + | VB |

| 4 | 1, 2, 6, 7 | D0, D1, D2 | S4, T1, T4 | + | + | I | − | VB |

| 5 | 2, 6 | D0 | S2, S4, S5, T1, T4 | − | − | + | + | 2 VB |

| 6 | 3, 5 | D0 | S2, S4, T1, T4 | − | − | I | + | 2 VB |

| 7 | 3, 4, 5 | D1, D2 | S1, S3, T1, T4 | − | − | − | + | 3 VB |

| 8 | 3, 4, 5 | D0, D1, D2 | S3, T1, T4 | + | + | − | − | 3 VB |

| 9 | 4 | D0 | S1, S2, S3, T1, T4 | − | − | − | + | 4 VB |

| 10 | 8, 14 | S1, S4, T2, T4 | I | I | I | + | 0 | |

| 11 | 8, 14 | D0, D1, D2 | S4, T2, T4 | + | + | I | − | 0 |

| 12 | 8, 9, 13, 14 | D1, D2, D3 | S1, S4, T2, T3 | − | − | I | + | −VB |

| 13 | 8, 9, 13, 14 | D0, D1, D2, D3 | S4, T2, T3 | + | + | I | − | −VB |

| 14 | 9, 14 | D0, D3 | S2, S4, S5, T2, T3 | − | − | + | + | −2 VB |

| 15 | 10, 12 | D0, D3 | S2, S4, T2, T3 | − | − | I | + | −2 VB |

| 16 | 10, 11, 12 | D1, D2 | S1, S3, T2, T3 | − | − | − | + | −3 VB |

| 17 | 10, 11, 12 | D0, D1, D2 | S3, T2, T3 | + | + | − | − | −3 VB |

| 18 | 11 | D0 | S1, S2, S3, T2, T3 | − | − | − | + | −4 VB |

| Parameter | Value | |

|---|---|---|

| Power rating | 350 W | |

| Input voltage (Vdc) | 24 V | |

| Output voltage (Vab) | 110 Vrms/50 Hz | |

| Carrier ware frequency (fs) | 15 kHz | |

| Inductors | L1 | 2 mH |

| Lf | 1 mH | |

| Capacitors | C1, C2, C3 | 2200 µF/200 V |

| Cf | 1 µF | |

| Power switches | S1, S2, S3, S4 | 47N60C3 |

| S5 | G40N60 | |

| T1, T2, T3, T4 | G40N120 | |

| Diodes (D0, D1, D2, D3) | DSEI60-06A | |

| Gate drives | TLP250 (Photo-coupler) | |

| Data from | Vab (V) | ΔVab (%) | B | VC1 and VC2 (V) | VC3 (V) |

|---|---|---|---|---|---|

| Theory | 156.2 | 0 | 2.7 | 65 | 130 |

| Simulation | 152.2 | 2.56 | 2.7 | 64.6 | 122.3 |

| Experiment | 110 | 29.57 | 2.17 | 52.2 | 92.5 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Vo, D.-V.; Nguyen, M.-K.; Do, D.-T.; Choi, Y.-O. A Single-Phase Nine-Level Boost Inverter. Energies 2019, 12, 394. https://doi.org/10.3390/en12030394

Vo D-V, Nguyen M-K, Do D-T, Choi Y-O. A Single-Phase Nine-Level Boost Inverter. Energies. 2019; 12(3):394. https://doi.org/10.3390/en12030394

Chicago/Turabian StyleVo, Dai-Van, Minh-Khai Nguyen, Duc-Tri Do, and Youn-Ok Choi. 2019. "A Single-Phase Nine-Level Boost Inverter" Energies 12, no. 3: 394. https://doi.org/10.3390/en12030394

APA StyleVo, D.-V., Nguyen, M.-K., Do, D.-T., & Choi, Y.-O. (2019). A Single-Phase Nine-Level Boost Inverter. Energies, 12(3), 394. https://doi.org/10.3390/en12030394