1. Introduction

Nowadays device packaging remains a major challenge in the micro electromechanical systems (MEMS) industry. The vast variation in shape and function of MEMS devices make it virtually impossible to create universal packages like those used in integrated circuits, while maintaining the integrity and functionality of the devices. Many application specific MEMS devices such as accelerometers, pressure sensors, and microgyroscopes require custom packaging to function. Microsensors often require contact with the surroundings to measure air or fluid pressure, gas content, or flowing liquids, making device packaging even more challenging and expensive. On top of being geometrically complex to package, moving parts of MEMS devices are highly sensitive to damage and contamination during fabrication and packaging processes. Damage could be caused by chemical contamination, physical touch, or contamination by micro dirt [

1]. The custom packaging and special handling needed drive packaging cost high. Moreover, stringent device performance requirements have driven the need for a packaging method that is robust, manufacturable using CMOS compatible processes, and easily fabricated and tested. In an effort to lower packaging cost, improve yield, and comply with these requirements, many MEMS manufacturers are starting to explore wafer level packaging.

Wafer level packaging is an approach at which the dies are individually encapsulated on wafer level before dicing. Using this approach, MEMS devices generally require two levels of packaging [

2]:

- i)

Wafer level packaging: at this level, encapsulation is applied simultaneously on all dies to provide protection during handling, dicing and testing. This type of packaging is usually hermetic.

- ii)

Conventional packaging: after encapsulation is applied, the wafer is diced. Then, each die is picked, placed, and bonded on a leadframe, wire bonded, and plastic molded. This type of packaging is usually non-hermetic.

A typical MEMS device consists of sensor or actuator elements fabricated on a silicon substrate. MEMS devices such as RF switches, inductors, filters, and accelerometers do not require interaction with the surroundings to function. Hence, a complete isolation of the sensor or actuator elements would increase device performance as well as its lifetime. A conventional wafer level packaging technique is cap bonding. The bonded cap, however, is commonly thick and occupies a lot of real estate as the cap has to be bonded over and around the movable elements of the device [

1]. For this reason, deposited encapsulation is becoming more favorable for packaging these isolatable MEMS devices. In this process, movable parts of a MEMS device are covered by deposited metal or silicon encapsulation, leaving a gap between the top surface of the movable parts and the bottom surface of the encapsulation. As a result, the encapsulation allows movable elements to move freely while protecting them.

Various techniques have been developed to encapsulate isolatable MEMS devices. Partridge

et al. have pioneered the use of epitaxially deposited polysilicon as an encapsulation structure for piezoresistive accelerometers [

3]. In extension to the aforementioned work, Rusu

et al. studied plasma-enhanced chemical vapor deposition polysilicon germanium as an alternate material for device encapsulation [

4]. Meanwhile, Lebouitz

et al. used permeable polysilicon to fabricate a vacuum shell over movable elements of a MEMS resonator [

5]. Alternate methods involve using chemical vapor deposition sealed micromachined cavity and SiN microshell to protect microstructures [

6-

7]. However, all the aforementioned techniques involve high process temperatures that are detrimental to prefabricated CMOS circuitry, which is often damaged at temperature higher than 450°C. As a solution, a low temperature process was introduced using electroless nickel cavity as the encapsulation structure [

8]. The fabrication process, however, requires an electroplating step, which is less compatible with CMOS and other pre-fabricated microstructures. In light of these problems, this work attempts to solve the wafer level packaging issues faced by isolatable devices through a simple and economical CMOS compatible microfabrication processes. A novel wafer level encapsulation is introduced, which uses sputtered silicon as main structural layer, eutectic gold-silicon alloy as seal layer, and high strength liquid crystal polymer (LCP) thermoplastic as outer encapsulant layer. A robust encapsulation which could withstand subsequent high pressure plastic packaging is produced only by using and carefully sequencing several CMOS compatible materials and low temperature processes, without the need for expensive packaging procedures and equipments.

2. Methodology

In order to assess the feasibility of the proposed packaging technique, sputtered silicon encapsulation was built on an unpackaged MEMSTech 50g non-crossing differential capacitive accelerometer (Sensfab Pte. Ltd., Singapore). This device is selected due to its size suitability. The device has an adequately large movable elements area for the encapsulation to be built upon. For this reason, viability of the technique on this device would imply its feasibility on other MEMS devices with smaller movable elements area, since all the CMOS compatible processes used could be scaled down. Moreover, the device structure is planar, yet fairly complicated, which made it practical to gauge the potential of this packaging technique.

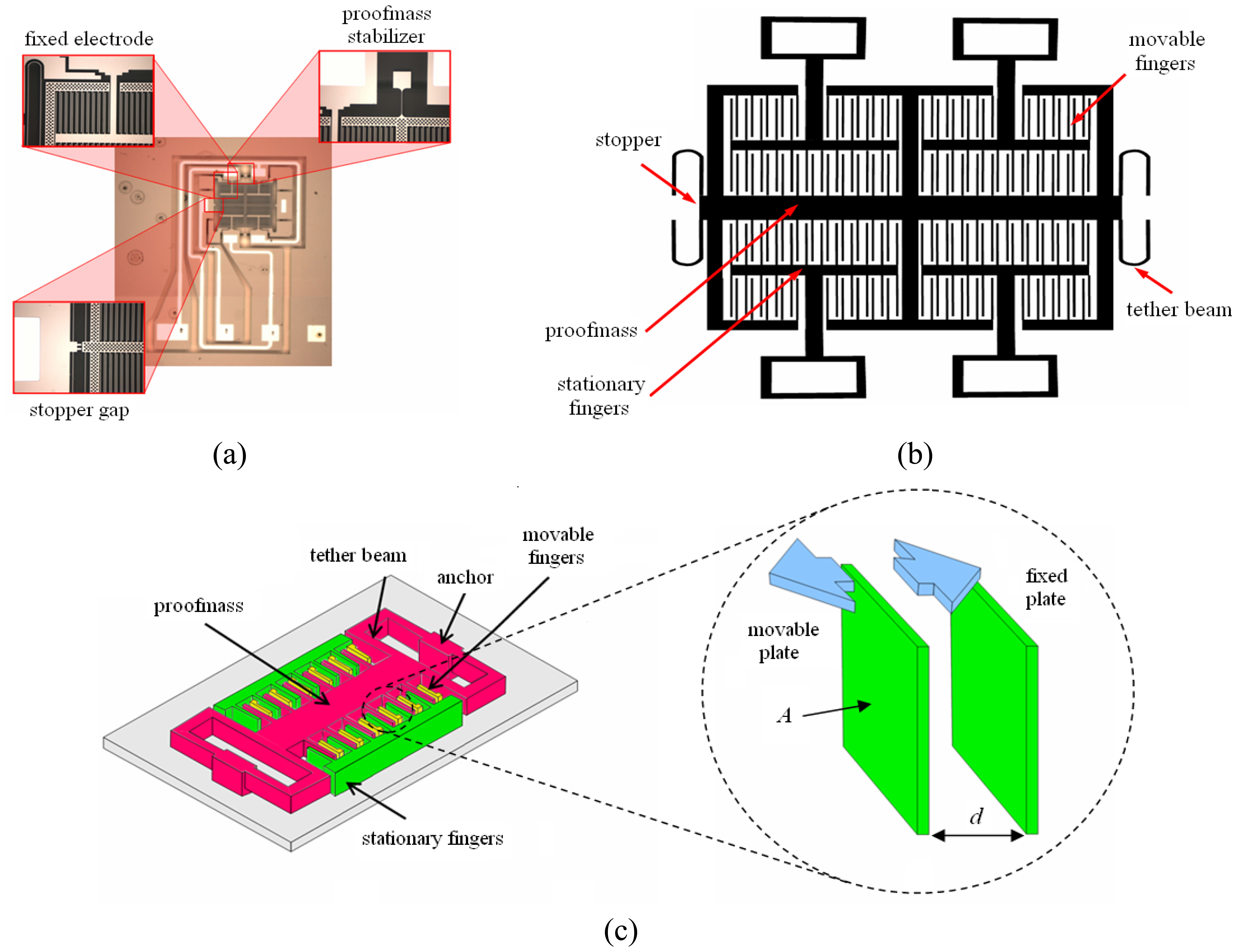

The accelerometer device has four identical quadrants of accelerometer fingers, with 84 pairs of beams per side, as shown in

Figures 1(a) and 1(b). The device has a set of stationary fingers at each quadrant and a proof mass holding all the movable fingers [

Figure 1(b)]. It has sensor die area of 2,350 × 3,020 μm

2, which includes bond pad area of 652.3 μm × 2,331.7 μm, and movable elements area of about 500 μm × 700 μm. The encapsulation structure has to cover all movable elements and have a decent base to be built upon. Considering the position of traces and isolation trenches, it was determined that the most feasible size for the encapsulation structure is 1,455 μm × 1,455 μm. Encapsulation of this size would envelop over all movable elements and critical traces while having appreciable base area to stick to. The inner cavity would have a dimension of 1,250 μm × 1,250 μm, and height of approximately 5 μm. The difference between outer and inner dimension, which is 205 μm, would provide a base of width 102.5 μm around the perimeter of the encapsulation structure.

Capacitive accelerometer detects the variance of capacitance resulting from movement of the parallel plates due to impact, as depicted in

Figure 1(c). Capacitance (

C) of a pair of parallel plates is given by:

where

A is the overlapping area of the plates,

d is the spacing between the plates, and

εs is the static permittivity of the material between the plates. For the 50g accelerometer used, the static permittivity is close to vacuum permittivity (

ε0) since the gap between the plates is occupied by air. The accelerometer has an absolute capacitance value of approximately 1 pF.

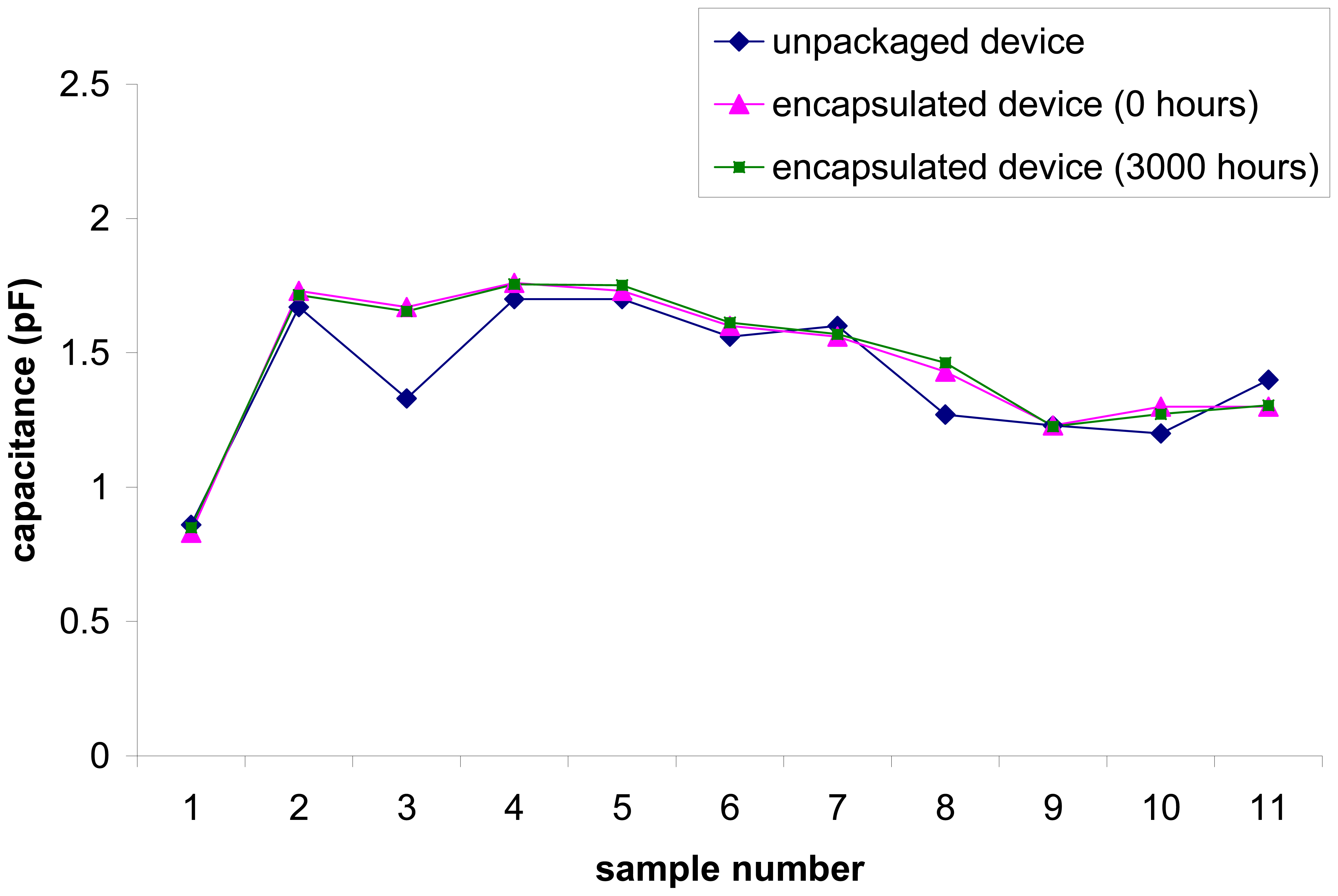

Several tests are conducted on the encapsulation structure after fabrication. The encapsulated device was visually inspected for defects and microstructure release using a scanning electron microscope (SEM) and optical microscopy. Then, a profile scan is performed across the encapsulation using a

Tencor surface profiler to check for surface uniformity and existence of microcracks on the structure. After outer encapsulant application, strength of the dome shaped outer encapsulant layer was determined using a Micro Materials' (Wrexham, U.K.)

NanoTest indenter system, which measures hardness and Young's modulus of the outer encapsulant. Seven identical cured encapsulant samples were used in the strength measurement test, with one indent per sample. The final test performed on the encapsulated device was a capacitance test, which was measured using an Agilent 4284A Precision LCR Meter. As shown by

Equation (1), the capacitance value depends on the static permittivity, which varies depending on the material occupying the gap between the parallel capacitor plates. Therefore, complete release of sacrificial material can be verified by comparing capacitance value before and after encapsulation fabrication. 11 samples are tested before and after encapsulation and capacitance values are compared

3. Encapsulation Fabrication Process

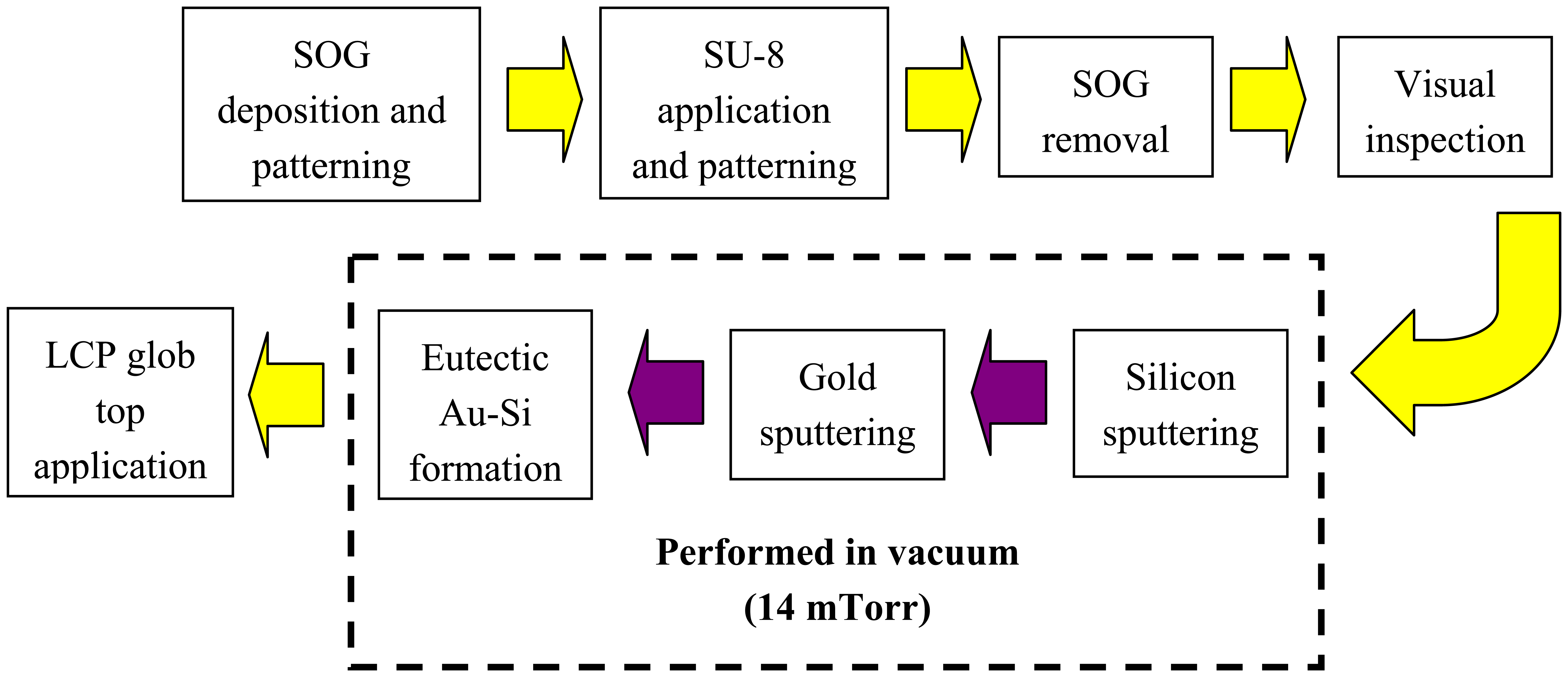

Encapsulation fabrication involves several deposition and etching steps. The process is initialized by sacrificial spin-on glass (SOG) deposition and patterning, and followed by SU-8 base layer formation, sacrificial SOG removal, visual inspection of release etch, silicon main structural layer formation, gold layer deposition, eutectic gold-silicon seal layer formation, and LCP glob top outer encapsulant application, all in the stated order. These process steps are summarized in

Figure 2. Schematic showing different parts of completed wafer level packaging for MEMSTech 50g accelerometer is depicted in

Figure 3.

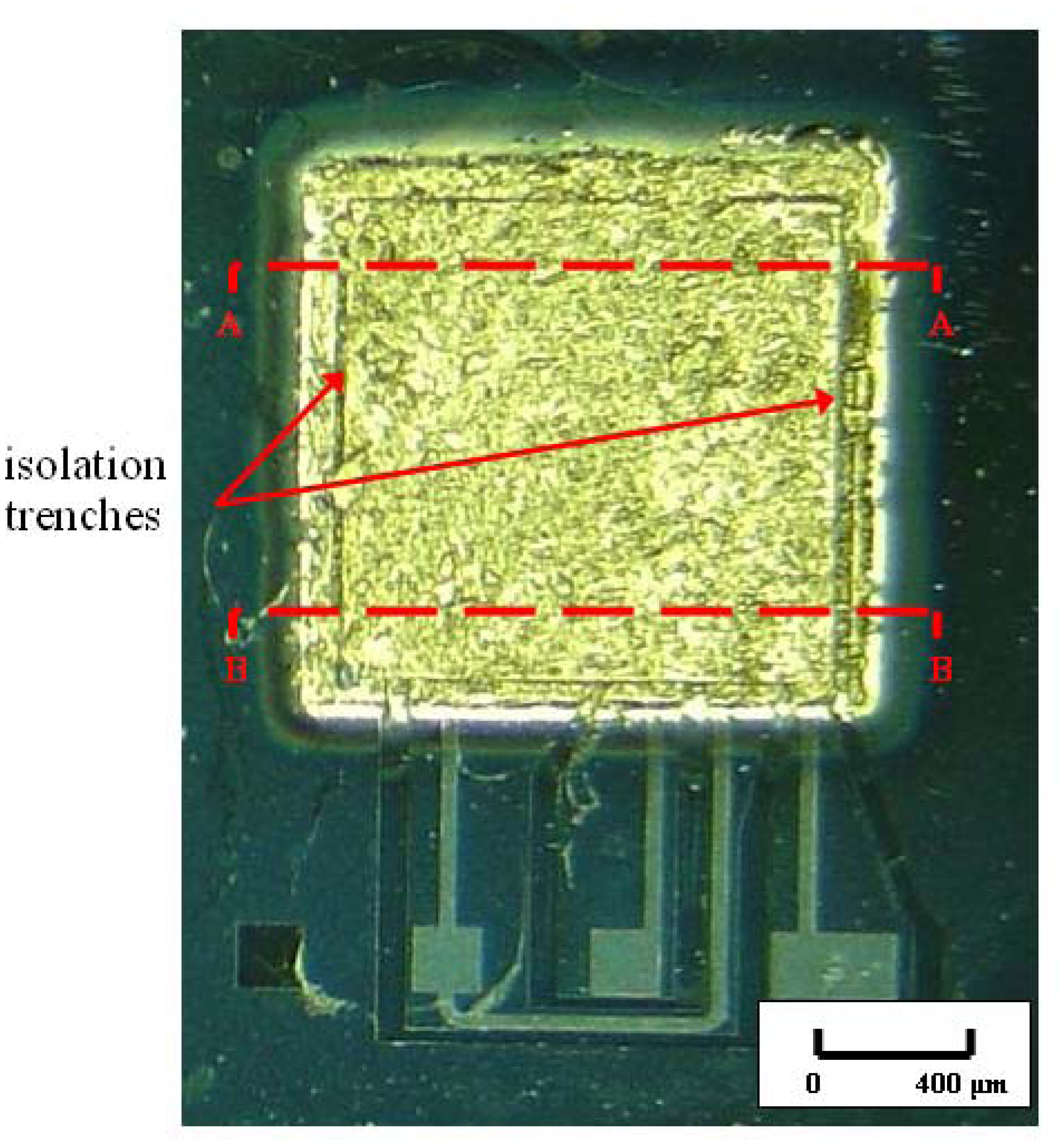

3.3. Release Etch and Visual Inspection

The most critical step in determining the functionality of the device after encapsulation is the release etch. The etch release step was performed using 5% HF solution (1:20 HF-H

2O). This solution was found effective in removing sacrificial SOG, while being less damaging to both the SU-8 base layer and silicon structure of the accelerometer [

10].

Optimal etch time needed to be determined for complete removal of sacrificial oxide. For the accelerometer device selected, total etch time is the summation of etch times at all the subsections. Maximum etch distance needs to be taken into account. Schematic of SU-8 encapsulated 50G accelerometer with side etch channels is depicted in

Figure 4 below. It could be seen that total etch time could be formulated as follows:

Note that

tC is T-junction region. Etch rate in this section is 2/3 of the etch rate in straight sections [

10]. For the 50g accelerometer device, the etch time and total etch time to completely release the structure is tabulated in

Table 1 below. Upon completion of release etch step, moisture was removed from within encapsulation base structure via direct hotplate baking. The device was gradually heated to 90°C and maintained at peak temperature for 20 minutes, before being slowly cooled to room temperature. Next, owing to transparent property of cured SU-8, visual inspection of complete SOG removal was performed using optical microscope.

3.4. Encapsulation Main Structure Formation

Sputtered silicon was used as the main structure for the encapsulation. A silicon mask with square openings was used to pattern the sputtered silicon so as only the area underneath the openings were sputtered. The samples were aligned such that the SU-8 square base structure was at the very center of the mask square opening. The samples were then placed in

NanoFilm (NTI Pte. Ltd., Singapore) sputtering chamber and RF silicon sputtering was performed at 400W forward power with 20 sccm argon flow, at approximately 80°C. The sputtering process was performed for a total of 23 hours and 50 minutes, at pressure level of approximately 14 mTorr, yielding a silicon layer of approximately 25 μm in height. Despite lower deposition rate, this pressure level was selected because of its higher film adhesion due to lower sputtering pressure [

11].

3.6. Application of Outer Encapsulant

Outer encapsulant needs to be added on top of the encapsulation structure in order to strengthen the encapsulation structure for the subsequent transfer molding process. A thin glob of RTP 3485-1 LCP carbon fiber was melt-dispensed on encapsulated MEMSTech 50g accelerometer using a dispenser heated to approximately 300°C to melt the thermoplastic, yielding an encapsulated device with a uniform glob top after curing. During hardening, slow cooling was used to avoid stress build-up. This thermoplastic was selected as encapsulant material because of its sufficiently high Young's modulus value and its matching coefficient of thermal expansion (CTE) with the outermost gold layer. Gold, which possesses CTE value of 14 ppm/°C, could be excellently matched by the CTE value of LCP carbon fiber, which is on the range of 12-18 ppm/°C [

17]. CTE matching guarantees low thermal stress build-up between gold and thermoplastic interfaces, thus reducing the possibility of post-process intrinsic stress build-up and delamination. Only a thin layer of glob, not to exceed 210 μm thick, is dispensed on the encapsulation structure to maintain the thin profile of the packaged device. For this thickness, cured LCP with Young's modulus value greater than 26.5 GPa is needed to withstand pressure up to 100 atm during subsequent plastic package transfer molding process [

18].

5. Conclusions

This work has presented a novel wafer level packaging technique for isolatable MEMS devices using a simple and economical CMOS compatible microfabrication processes. The encapsulation uses spin-on glass (SOG) as the sacrificial layer, annealed SU-8 polymer as the base layer, RF sputtered silicon as the main structural layer, eutectic gold-silicon alloy as the seal layer, and high strength liquid crystal polymer (LCP) thermoplastic as the outer encapsulant layer. A robust encapsulation is produced only by using and carefully sequencing these CMOS compatible materials and processes, without the need for expensive packaging equipments. The encapsulation could be fabricated on prereleased as well as released MEMS devices. The completed encapsulation consists of a 25 μm thick silicon encapsulation, 8.75 μm thick base layer, 1 μm thick gold layer, and approximately 210 μm thick LCP layer built on movable elements of MEMSTech 50g accelerometer. The layout was 1,900 μm by 1,900 μm square, with a 1,250 μm by 1,250 μm inner cavity area. The encapsulation has 5 μm clearance between the movable elements and the encapsulation structure. Prior to LCP encapsulant application, the silicon encapsulation is tested for surface uniformity using Tencor surface profiler. It is observed that the fabrication process has yielded an encapsulation structure with an average thickness of approximately 40 μm with no detrimental cracks. Subsequently, the encapsulated devices are broken in half to inspect the internal features of the encapsulation. Scanning electron microscope (SEM) inspection indicates that the accelerometer fingers are completely released upon sacrificial SOG removal using hydrofluoric acid (HF). Moreover, comparable capacitance values before and after encapsulation indicate complete release of the movable fingers. Completed encapsulation structure with LCP outer encapsulant coating is tested for strength using NanoTest indenter system. Nanoindentation test results indicate that the glob top outer encapsulant is sufficiently strong to endure transfer molding process. The encapsulation technique developed in this work has successfully produced robust MEMS packaging using cheap and simple CMOS compatible processes. Solution for some of the common MEMS packaging problems such as process compatibility, custom and complex packaging equipments required, and high cost has been offered for isolatable MEMS devices.