In Situ Time-Based Sensor for Process Identification Using Amplified Back-End-of-Line Resistance and Capacitance

Abstract

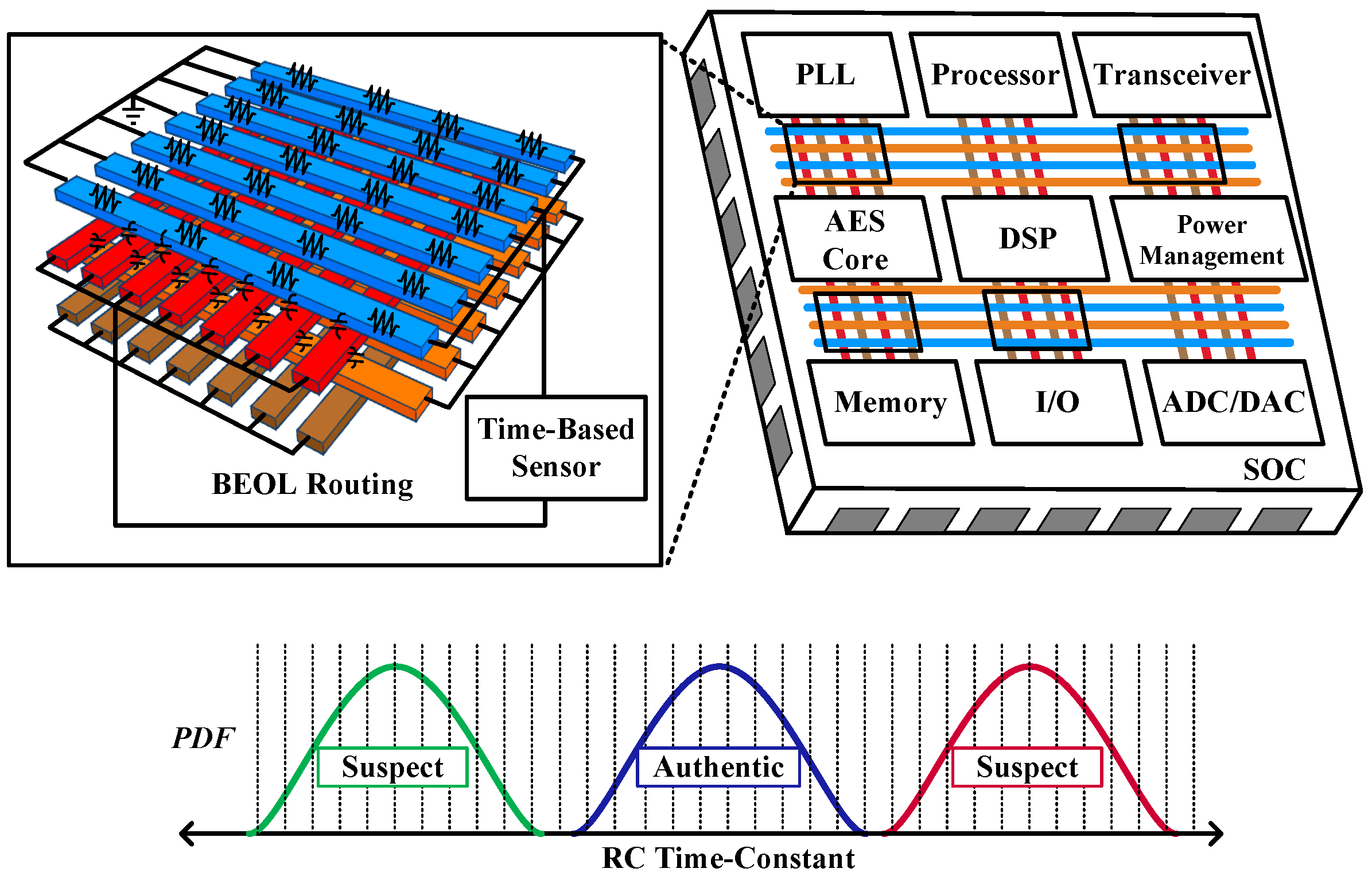

1. Introduction

2. Proposed Time-Based Sensor

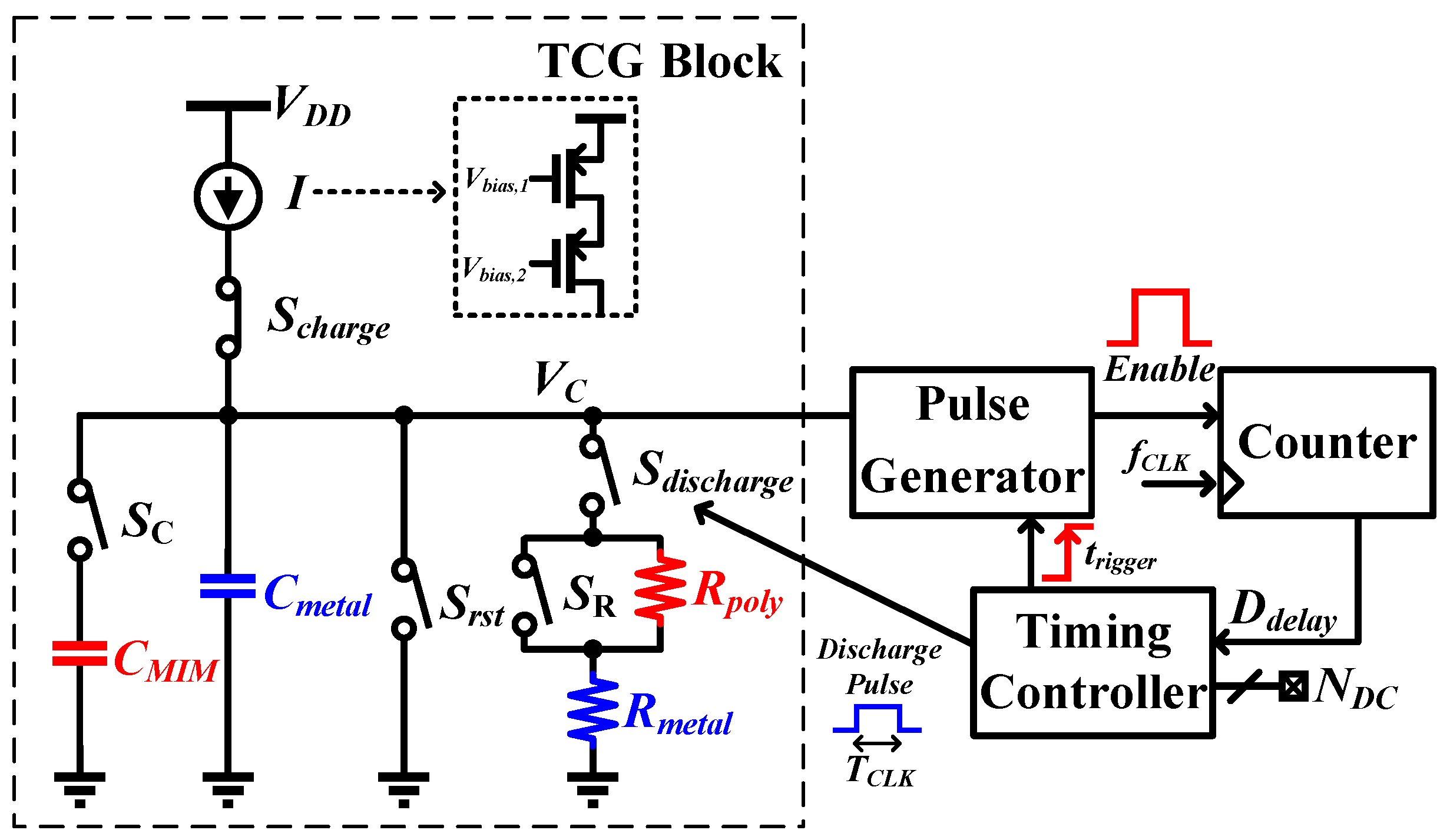

2.1. Architecture Overview

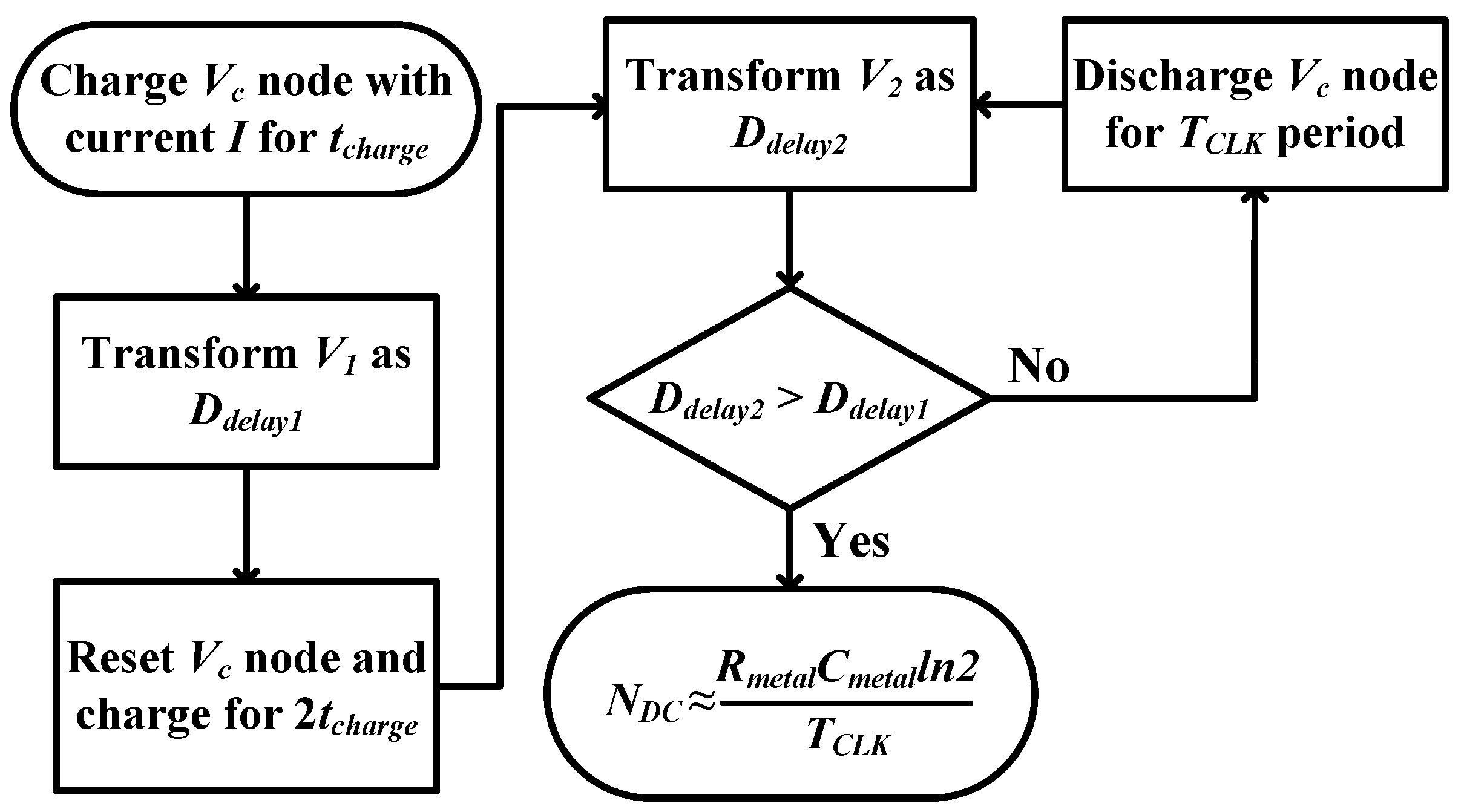

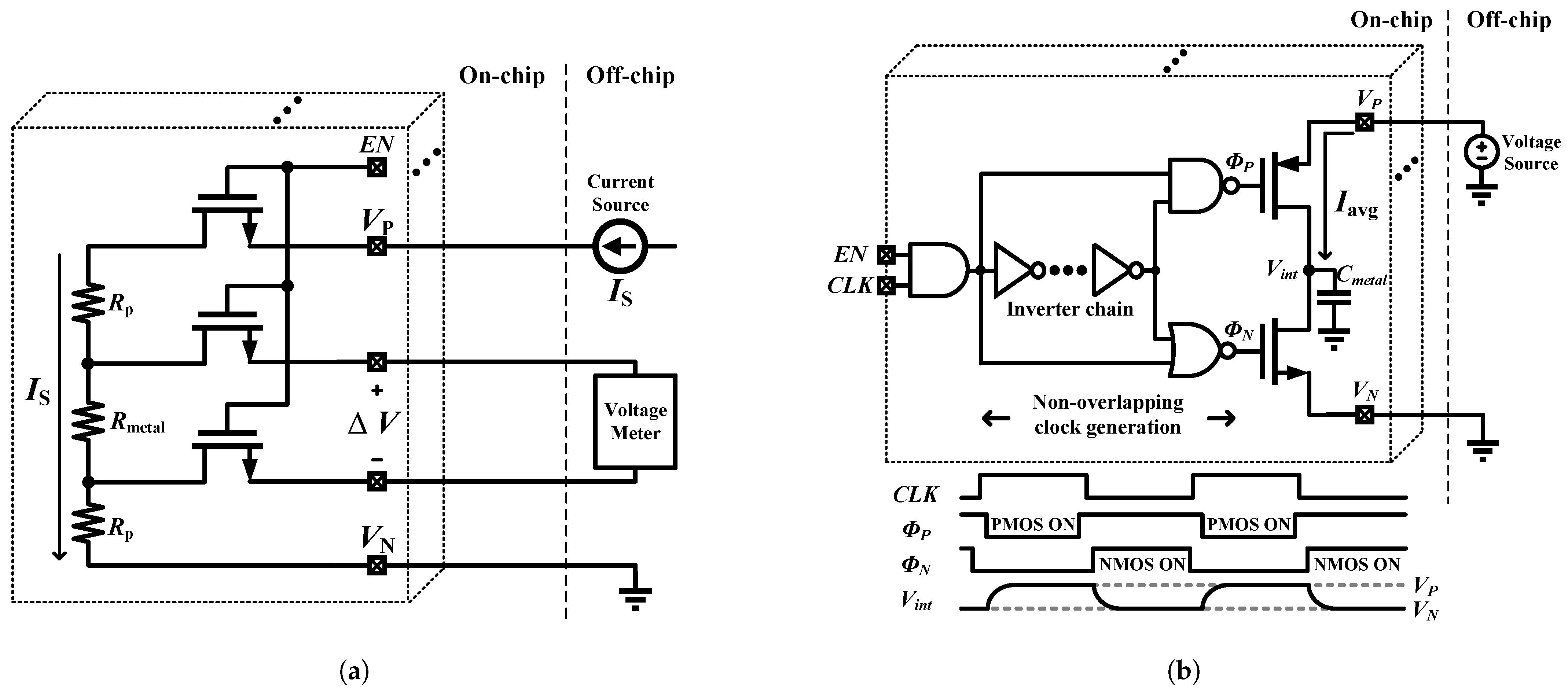

2.2. Circuit Operation

2.3. Measurement Error in Direct Measurement

2.4. Three-Configuration Measurement

2.5. Process, Voltage, and Temperature Variations

3. Analytical Model

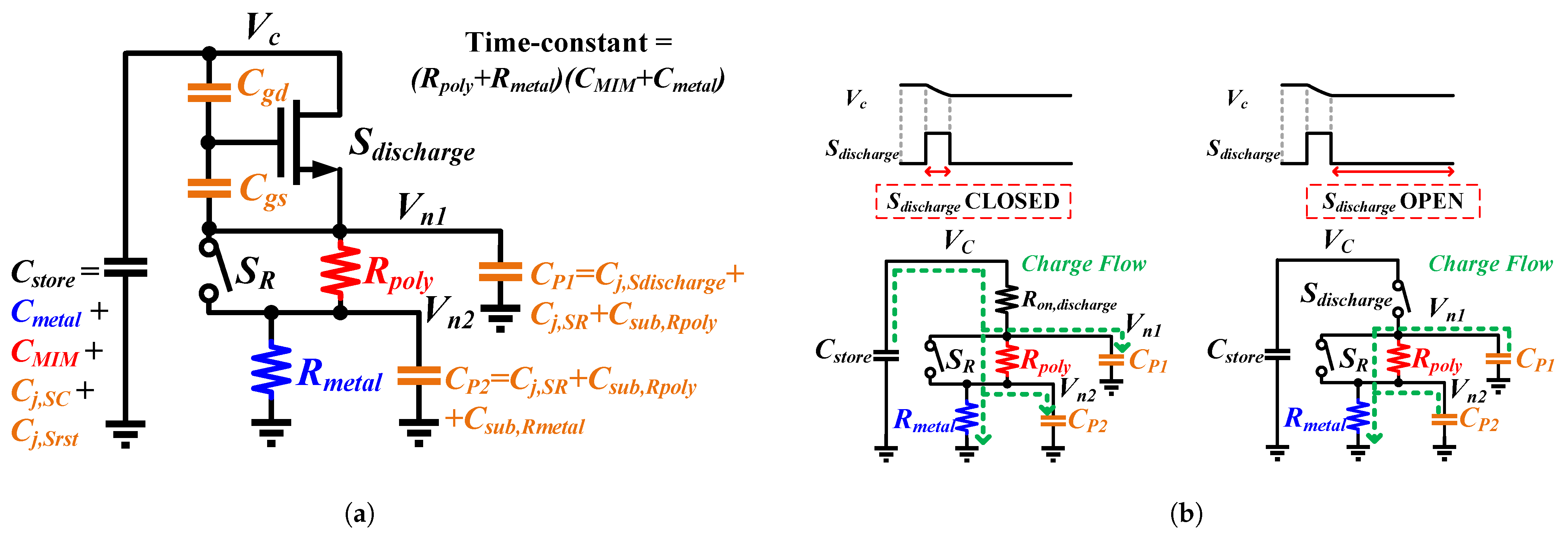

3.1. Charge Redistribution Effect

3.2. Clock Feedthrough Effect

3.3. Simulation Results

4. Implementation Details

4.1. TCG Block

4.2. Pulse Generator

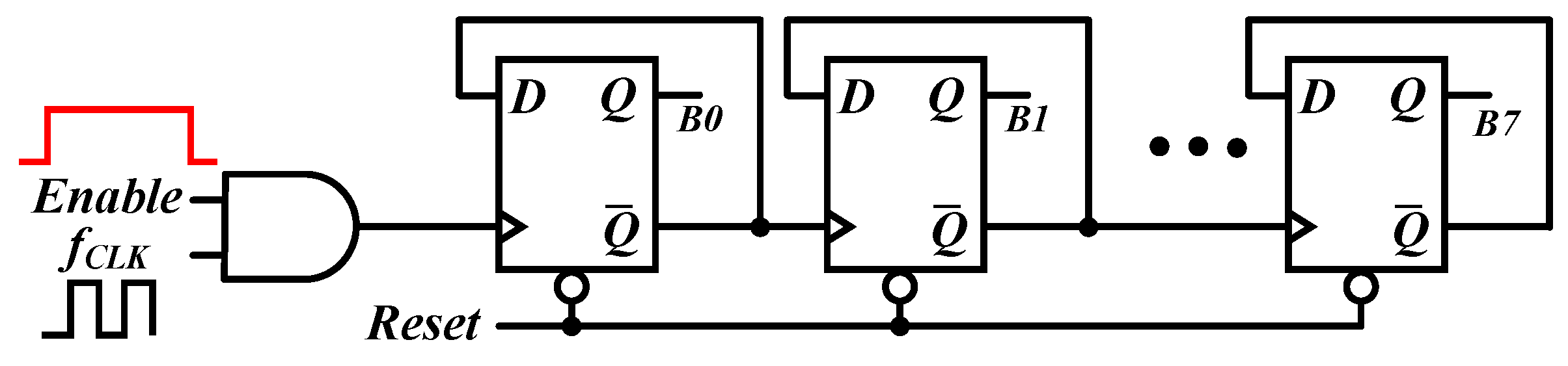

4.3. Counter

4.4. Timing Controller

4.5. Time-Based Sensor

4.6. Direct Measurement Array

5. Measurement Results

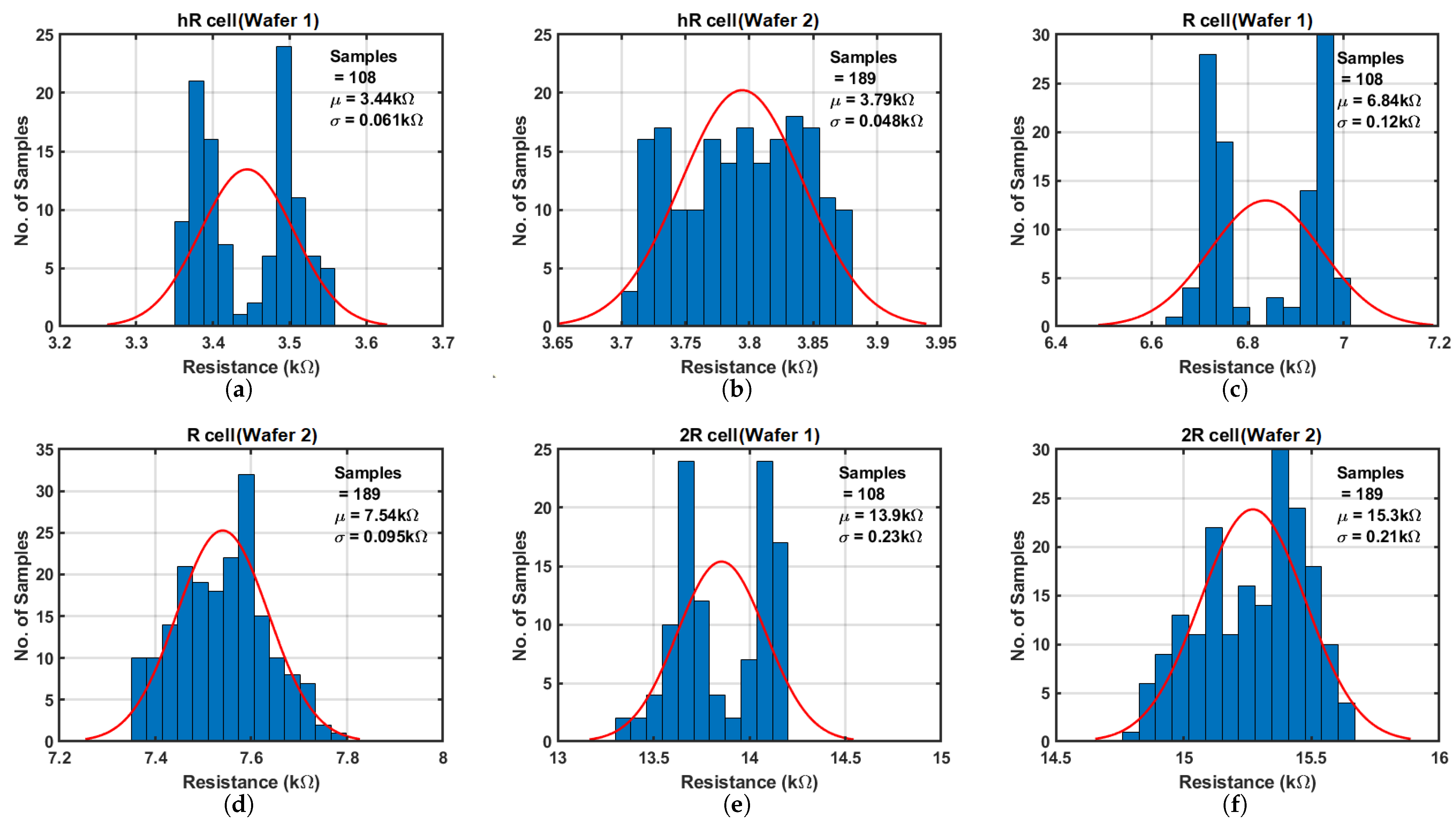

5.1. Direct Measurement Array—Resistor Array

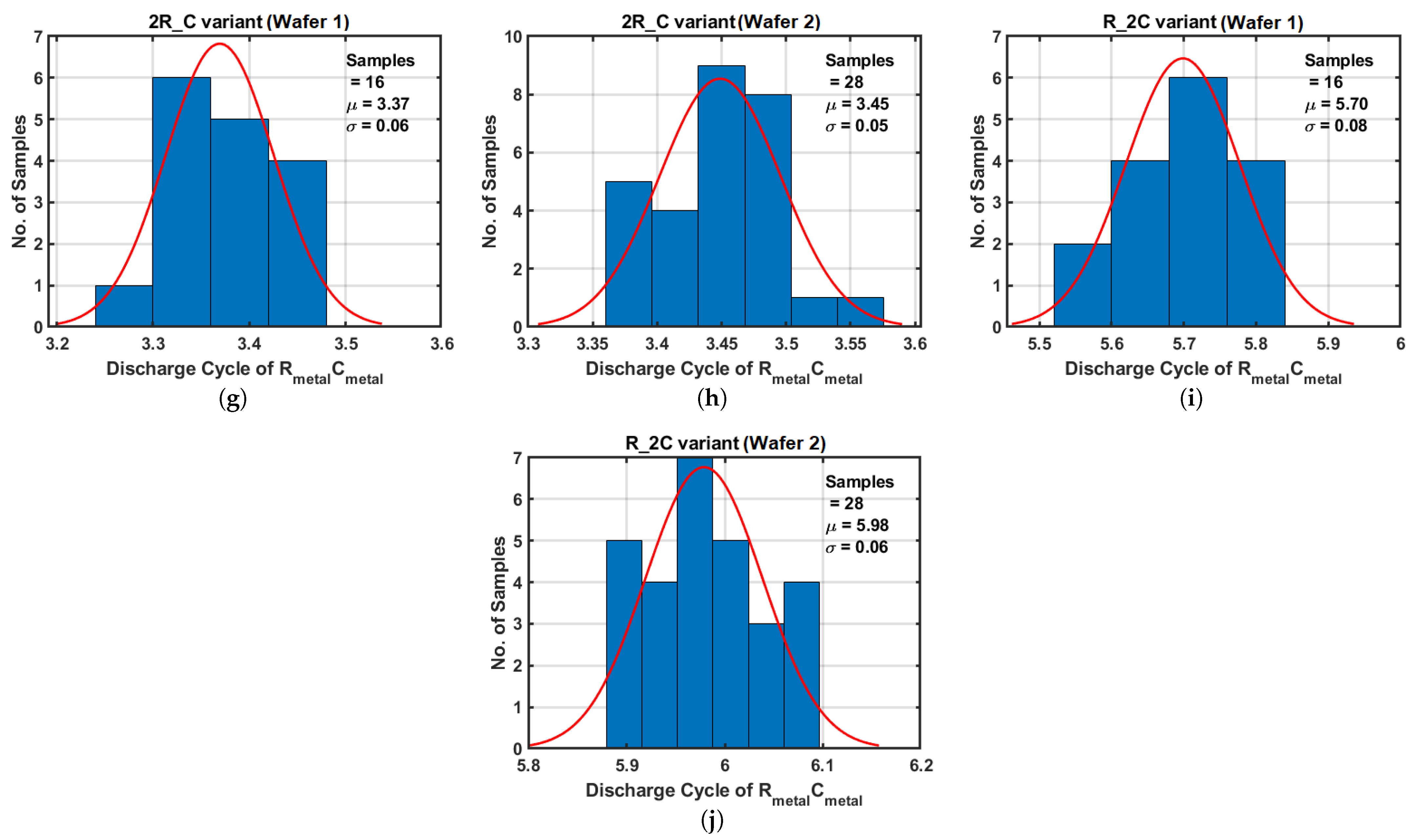

5.2. Direct Measurement Array—Capacitor Array

5.3. Time-Based Sensors

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

Appendix A. Three-Configuration Measurement Derivation

References

- Guin, U.; Huang, K.; DiMase, D.; Carulli, J.M.; Tehranipoor, M.; Makris, Y. Counterfeit Integrated Circuits: A Rising Threat in the Global Semiconductor Supply Chain. Proc. IEEE 2014, 102, 1207–1228. [Google Scholar] [CrossRef]

- Bhunia, S.; Hsiao, M.S.; Banga, M.; Narasimhan, S. Hardware Trojan Attacks: Threat Analysis and Countermeasures. Proc. IEEE 2014, 102, 1229–1247. [Google Scholar] [CrossRef]

- Hu, W.; Chang, C.H.; Sengupta, A.; Bhunia, S.; Kastner, R.; Li, H. An Overview of Hardware Security and Trust: Threats, Countermeasures, and Design Tools. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2021, 40, 1010–1038. [Google Scholar] [CrossRef]

- Cobb, W.E.; Laspe, E.D.; Baldwin, R.O.; Temple, M.A.; Kim, Y.C. Intrinsic Physical-Layer Authentication of Integrated Circuits. IEEE Trans. Inf. Forensics Secur. 2012, 7, 14–24. [Google Scholar] [CrossRef]

- Xu, Q.; Zheng, R.; Saad, W.; Han, Z. Device Fingerprinting in Wireless Networks: Challenges and Opportunities. IEEE Commun. Surv. Tutor. 2016, 18, 94–104. [Google Scholar] [CrossRef]

- Bihl, T.J.; Bauer, K.W.; Temple, M.A. Feature Selection for RF Fingerprinting With Multiple Discriminant Analysis and Using ZigBee Device Emissions. IEEE Trans. Inf. Forensics Secur. 2016, 11, 1862–1874. [Google Scholar] [CrossRef]

- Zhang, J.; Woods, R.; Sandell, M.; Valkama, M.; Marshall, A.; Cavallaro, J. Radio Frequency Fingerprint Identification for Narrowband Systems, Modelling and Classification. IEEE Trans. Inf. Forensics Secur. 2021, 16, 3974–3987. [Google Scholar] [CrossRef]

- Herder, C.; Yu, M.D.; Koushanfar, F.; Devadas, S. Physical Unclonable Functions and Applications: A Tutorial. Proc. IEEE 2014, 102, 1126–1141. [Google Scholar] [CrossRef]

- Maes, R.; Rozic, V.; Verbauwhede, I.; Koeberl, P.; van der Sluis, E.; van der Leest, V. Experimental evaluation of Physically Unclonable Functions in 65 nm CMOS. In Proceedings of the 2012 Proceedings of the ESSCIRC (ESSCIRC), Bordeaux, France, 17–21 September 2012; pp. 486–489. [Google Scholar] [CrossRef]

- Delavar, M.; Mirzakuchaki, S.; Mohajeri, J. A Ring Oscillator-Based PUF With Enhanced Challenge-Response Pairs. Can. J. Electr. Comput. Eng. 2016, 39, 174–180. [Google Scholar] [CrossRef]

- Liu, K.; Min, Y.; Yang, X.; Sun, H.; Shinohara, H. A 373-F2 0.21%-Native-BER EE SRAM Physically Unclonable Function With 2-D Power-Gated Bit Cells and VSS Bias-Based Dark-Bit Detection. IEEE J. Solid-State Circuits 2020, 55, 1719–1732. [Google Scholar] [CrossRef]

- Wendt, J.B.; Koushanfar, F.; Potkonjak, M. Techniques for foundry identification. In Proceedings of the 2014 51st ACM/EDAC/IEEE Design Automation Conference (DAC), San Francisco, CA, USA, 1–5 June 2014; pp. 1–6. [Google Scholar] [CrossRef]

- Shylendra, A.; Bhunia, S.; Trivedi, A.R. An Intrinsic and Database-Free Authentication by Exploiting Process Variation in Back-End Capacitors. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 27, 1253–1261. [Google Scholar] [CrossRef]

- Bahar Talukder, B.M.S.; Menon, V.; Ray, B.; Neal, T.; Rahman, M.T. Towards the Avoidance of Counterfeit Memory: Identifying the DRAM Origin. In Proceedings of the 2020 IEEE International Symposium on Hardware Oriented Security and Trust (HOST), San Jose, CA, USA, 4–7 May 2020; pp. 111–121. [Google Scholar] [CrossRef]

- Sakib, S.; Milenković, A.; Ray, B. Flash-DNA: Identifying NAND Flash Memory Origins Using Intrinsic Array Properties. IEEE Trans. Electron Devices 2021, 68, 3794–3800. [Google Scholar] [CrossRef]

- Skoric, B.; Maubach, S.; Kevenaar, T.; Tuyls, P. Information-theoretic analysis of capacitive physical unclonable functions. J. Appl. Phys. 2006, 100, 24902–24911. [Google Scholar] [CrossRef]

- Roy, D.; Klootwijk, J.H.; Verhaegh, N.A.M.; Roosen, H.H.A.J.; Wolters, R.A.M. Comb Capacitor Structures for On-Chip Physical Uncloneable Function. IEEE Trans. Semicond. Manuf. 2009, 22, 96–102. [Google Scholar] [CrossRef]

- Gisha, C.G.; Chakraborty, A.S.; Chakraborty, R.S.; Jose, B.A.; Mathew, J. Diode-Triode Current Mirror Inverter PUF: A Novel Mixed-Signal Low Power Analog PUF. In Proceedings of the 2023 IEEE 66th International Midwest Symposium on Circuits and Systems (MWSCAS), Tempe, AZ, USA, 6–9 August 2023; pp. 1132–1136. [Google Scholar] [CrossRef]

- Yoo, M.; Kim, S.B.; Son, H.; Kim, K.; Wi, J.; Nam, G.; Son, M.; Choi, M.; Yu, I.; Kim, D.K.; et al. DRAM Physically Unclonable Function (PUF) Using Dual Word-Line Activated Twin-Cells. IEEE Trans. Circuits Syst. II Express Briefs 2025, 72, 514–518. [Google Scholar] [CrossRef]

- Ni, L.; Wang, P.; Zhang, Y.; Li, X.; Li, G.; Ding, L.; Zhang, J. SI PUF: An SRAM and Inverter-Based PUF With a Bit Error Rate of 0.0053% and 0.073/0.042 pJ/bit. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 2339–2343. [Google Scholar] [CrossRef]

- Dehghanzadeh, P.; Mandal, S.; Bhunia, S. MBM PUF: A Multi-Bit Memory-Based Physical Unclonable Function. IEEE Trans. Circuits Syst. I Regul. Pap. 2025, 72, 2114–2127. [Google Scholar] [CrossRef]

- He, Y.; Li, D.; Yu, Z.; Yang, K. ASCH-PUF: A “Zero” Bit Error Rate CMOS Physically Unclonable Function With Dual-Mode Low-Cost Stabilization. IEEE J. Solid-State Circuits 2023, 58, 2087–2097. [Google Scholar] [CrossRef]

- Jeon, D.; Lee, D.; Kim, D.K.; Choi, B.D. A 325F2 Physical Unclonable Function Based on Contact Failure Probability With Bit Error Rate < 0.43 ppm After Preselection With 0.0177Discard Ratio. IEEE J. Solid-State Circuits 2023, 58, 1185–1196. [Google Scholar] [CrossRef]

- Ahmadi, A.; Bidmeshki, M.M.; Nahar, A.; Orr, B.; Pas, M.; Makris, Y. A machine learning approach to fab-of-origin attestation. In Proceedings of the 2016 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Austin, TX, USA, 7–10 November 2016; pp. 1–6. [Google Scholar] [CrossRef]

- Kincal, S.; Abraham, M.C.; Schuegraf, K. RC Performance Evaluation of Interconnect Architecture Options Beyond the 10-nm Logic Node. IEEE Trans. Electron Devices 2014, 61, 1914–1919. [Google Scholar] [CrossRef]

- Bonilla, G.; Lanzillo, N.; Hu, C.K.; Penny, C.; Kumar, A. Interconnect scaling challenges, and opportunities to enable system-level performance beyond 30 nm pitch. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 20.4.1–20.4.4. [Google Scholar] [CrossRef]

- Reverter, F.; Jordana, J.; Gasulla, M.; Pallàs-Areny, R. Accuracy and resolution of direct resistive sensor-to-microcontroller interfaces. Sens. Actuators A Phys. 2005, 121, 78–87. [Google Scholar] [CrossRef]

- Woo, K.C.; Yang, B.D. 0.3-V RC -to-Digital Converter Using a Negative Charge-Pump Switch. IEEE Trans. Circuits Syst. II Express Briefs 2020, 67, 245–249. [Google Scholar] [CrossRef]

- Alhoshany, A.; Salama, K.N. A Precision, Energy-Efficient, Oversampling, Noise-Shaping Differential SAR Capacitance-to-Digital Converter. IEEE Trans. Instrum. Meas. 2019, 68, 392–401. [Google Scholar] [CrossRef]

- Ohkawa, S.; Aoki, M.; Masuda, H. Analysis and characterization of device variations in an LSI chip using an integrated device matrix array. IEEE Trans. Semicond. Manuf. 2004, 17, 155–165. [Google Scholar] [CrossRef]

- Chen, J.; Sylvester, D.; Hu, C. An on-chip, interconnect capacitance characterization method with sub-femto-farad resolution. IEEE Trans. Semicond. Manuf. 1998, 11, 204–210. [Google Scholar] [CrossRef]

- Jin, G.; Wu, H.; Yin, Y.; Zheng, L.; Zhuang, Y. A High-Accuracy RC Time Constant Auto-Tuning Scheme for Integrated Continuous-Time Filters. Micromachines 2024, 15, 166. [Google Scholar] [CrossRef]

| Configuration | Analytical Model | Circuit Simulation a | Model Error | |

|---|---|---|---|---|

| 26 | 26 | <1% | ||

| 32 | 32 | <1% | ||

| 277 | 270 | <2.6% | ||

| 3.0 b | 3.1 b | <3.2% | ||

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| 1.5 V | 16 pF | ||

| 500 MHz | 1.5 pF | ||

| 60 kΩ | 0.4 V | ||

| 6 kΩ | 0.8 V |

| Configuration | Std | a | Error b | |||

|---|---|---|---|---|---|---|

| 99 ns | 25.9 | 3.6 | 74.7 ns | 26.6% | ||

| 105 ns | 32.2 | 4.4 | 92.9 ns | 11.5% | ||

| 1155 ns | 269.8 | 16.7 | 778.5 ns | 32.6% | ||

| 9 ns | 3.09 c | 0.64 | 8.92 ns | 0.89% | ||

| Cell | Simulation Results | Measurement Results | Process Shift |

|---|---|---|---|

| hR | 3 kΩ | 3.67 kΩ | 22% |

| R | 6 kΩ | 7.28 kΩ | 21% |

| 2R | 12 kΩ | 14.8 kΩ | 23% |

| Cell | Simulation Results | Measurement Results | Process Shift |

|---|---|---|---|

| hC | 0.73 pF | 0.74 pF | 1.4% |

| C | 1.45 pF | 1.47 pF | 1.4% |

| 2C | 2.88 pF | 2.81 pF | −2.5% |

| Configuration | Simulation | Measurement | Error b | |||

|---|---|---|---|---|---|---|

| R Cell | C Cell | a | Std | a | Std | |

| R | hC | 1.91 | 0.06 | 1.82 | 0.063 | 4.9% |

| hR | C | 2.24 | 0.06 | 2.19 | 0.085 | 2.2% |

| R | C | 3.32 | 0.07 | 3.13 | 0.069 | 6.1% |

| 2R | C | 3.45 | 0.06 | 3.42 | 0.063 | 0.8% |

| R | 2C | 5.88 | 0.10 | 5.88 | 0.15 | 0% |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hsueh, J.-C.; Kines, M.; Tantawy, Y.A.; Smith, D.S.; McCue, J.; Dupaix, B.; Patel, V.J.; Khalil, W. In Situ Time-Based Sensor for Process Identification Using Amplified Back-End-of-Line Resistance and Capacitance. Sensors 2025, 25, 3255. https://doi.org/10.3390/s25113255

Hsueh J-C, Kines M, Tantawy YA, Smith DS, McCue J, Dupaix B, Patel VJ, Khalil W. In Situ Time-Based Sensor for Process Identification Using Amplified Back-End-of-Line Resistance and Capacitance. Sensors. 2025; 25(11):3255. https://doi.org/10.3390/s25113255

Chicago/Turabian StyleHsueh, Jen-Chieh, Mike Kines, Yousri Ahmed Tantawy, Dale Shane Smith, Jamin McCue, Brian Dupaix, Vipul J. Patel, and Waleed Khalil. 2025. "In Situ Time-Based Sensor for Process Identification Using Amplified Back-End-of-Line Resistance and Capacitance" Sensors 25, no. 11: 3255. https://doi.org/10.3390/s25113255

APA StyleHsueh, J.-C., Kines, M., Tantawy, Y. A., Smith, D. S., McCue, J., Dupaix, B., Patel, V. J., & Khalil, W. (2025). In Situ Time-Based Sensor for Process Identification Using Amplified Back-End-of-Line Resistance and Capacitance. Sensors, 25(11), 3255. https://doi.org/10.3390/s25113255