1. Introduction

Medical diagnostic procedures such as electromyography (EMG), electrocardiography (ECG), electroencephalography (EEG), or electrooculography (EOG) have significant clinical importance in the diagnosis of numbness, muscle weakness (EMG), many common heart problems (ECG), epilepsy, brain disorders (EEG), etc. These methods have been known for a long time; however, their development is continually progressing, the same as their sensing and processing development.

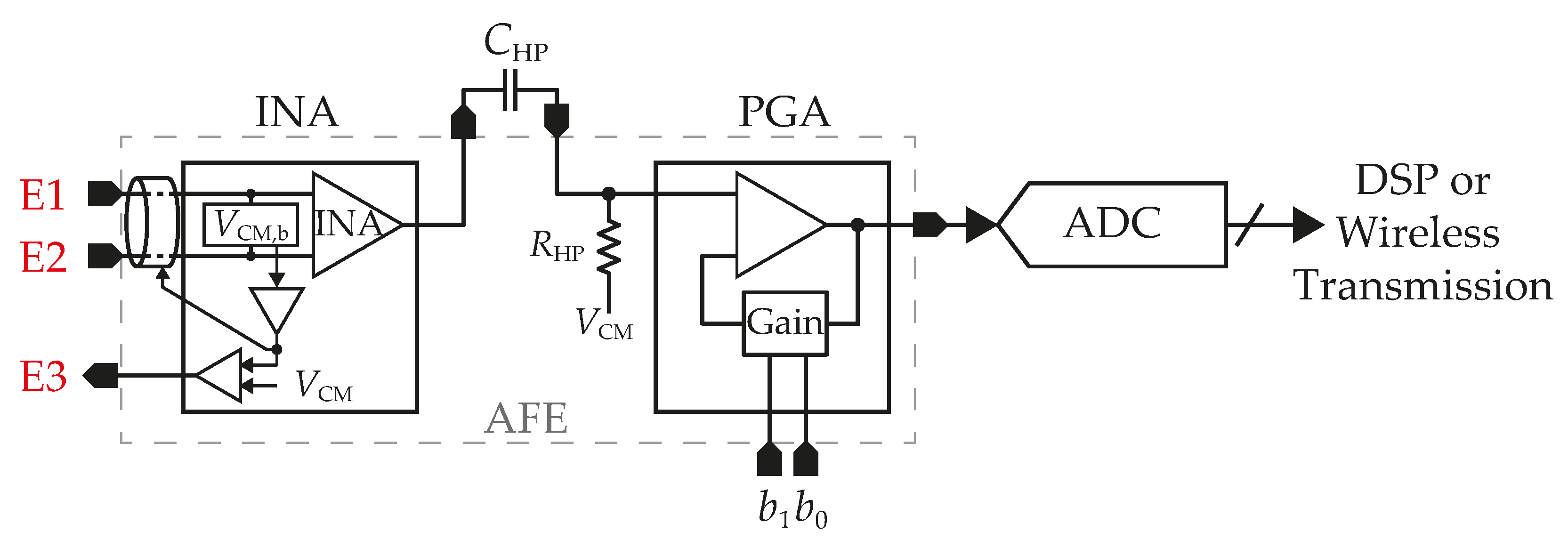

Biomedical information processing comprises techniques that apply mathematical tools to extract crucial diagnostic information from biomedical data. The main steps of a typical biomedical measurement and processing system are shown in

Figure 1.

The first step is to identify the relevant physical properties of the biomedical system, followed by measuring using suitable sensors. The next step is preprocessing and filtering. The preprocessing block comprises a low-noise instrumentation amplifier (INA) and a programmable-gain amplifier (PGA). Together with a filter, it constitutes an analog front-end component (AFE). Preprocessing by the INA is necessary because the measured electric signal is weak and must be increased in amplitude so it can be further processed. Magnifying of the amplitude is the essential function of the AFE, which must meet many specific requirements. These are listed below:

high input impedance to provide minimal loading of the measured signal;

high open-loop gain;

variable amplification selective to the physiological signal;

high rejection of superimposed noise and interference signals;

high common-mode rejection ratio (CMRR) and guaranteeing the safety of the patient;

low power consumption.

The high-pass (HPF) and low-pass (LPF) filters aim to eliminate interference signals such as electrode half-cell potentials or offset of the INA and reduce the noise level by limiting the amplifier bandwidth. Filtering is followed by converting an analog signal into a digital signal, which enables further digital signal processing (DSP). The delta-sigma analog-to-digital converter (ADC) is currently one the most popular types of ADC architecture in biomedical signal processing, owing to its power efficiency and high resolution [

1,

2,

3]. It is also possible to implement only a delta-sigma modulator on a wearable sensor integrated circuit (IC) when a stream of single bits from the modulator´s output (PDM) is transmitted via wireless communication to a computer [

4,

5].

Many authors have introduced AFE for ECG or EEG signal processing, in which requirements for signal ranges in frequency and amplitude are lower than in EMG, as can be seen in

Table 1.

Parameters related to the frequency spectrum of ECG or EEG signals enable achieving a very low power consumption of AFE in hundreds of nW [

7,

8,

9]. Some articles deal only with the design of a differential difference amplifier (DDA) as an attractive replacement for a classical INA composed of three operational amplifiers [

10,

11,

12,

13]. For example, the authors of [

13] introduced a DDA suitable for ECG signal processing with a power consumption of only 313 nW.

As can be seen from

Table 1, the EMG signal ranges in frequency from 20 Hz to 2 kHz depending on the type of examination. Moreover, setting the bandwidth of the AFE to above 20 Hz can greatly reduce the skin potentials and motion artifacts [

14]. Signal amplitudes range from tens of µV to approx. 10 mV, depending on the type of signal and electrodes used. Thus, EMG amplifiers must have a wider frequency response than ECG amplifiers.

This paper aims to design an AFE suitable for EMG signal processing with the low power supply voltage VDD = 1 V. Such low voltage considerably limits the design options for each analog block when it is difficult to use cascodes. For this reason, FDSOI 28 nm technology from STMicroelectronics is utilized, enabling adjusting of transistors’ threshold voltages (

). In addition, a very wide

tuning range of ∼250 mV for FD-SOI versus ∼10 mV for bulk CMOS, very good analog intrinsic performances, high-performance energy-efficient solutions, negligible input current, and reduced parasitic capacitances are achieved [

15]. As a result, all transistors in the circuit operate in the strong inversion region. The proposed AFE uses a fully differential difference amplifier (FDDA) to replace the classical three-amplifier INA topology to improve AFE parameters such as

CMRR, power consumption, area, etc. In addition, the following PGA utilizes a fully differential structure, which subsequently enables easy implementation of a fully differential ADC. The use of a low voltage power supply together with FDSOI technology is unpublished yet in the field of AFE design for biomedical signal processing. The circuit was designed for

= 1 V,

V and

= 0 V.

This paper is organized as follows:

Section 2 introduces the whole system at the top level. Sub-blocks such as active grounding, INA, and PGA are described in more detail in the subsections, where relevant schematics, mathematical relationships, and specific values for the utilized components are mentioned.

Section 3 shows detailed transistor-level schematics of the employed amplifiers. The subsections introduce the single-ended operational amplifier (OA) and two different FDDA circuits (FDDA1 and FDDA2) designed to meet specific application requirements in the block of use. Simulations are also included in these subsections.

Section 4 deals with verifying the whole system’s functionality in PVT corners (process, voltage, temperature). The achieved parameters are compared with results in similar works. Finally,

Section 5 highlights the major conclusions of the work.

2. The Proposed Structure of the Analog Front-End (AFE)

The proposed system is designed to process all types of EMG signal sources mentioned in

Table 1. This means the system can process a frequency range from 20 Hz to 2 kHz. The total gain consists of two components: a gain of the input INA and the PGA amplifier. While the gain of the INA is fixed, the PGA enables four different gains that are adjustable via a two-bit digital signal. Both active grounding and shielding methods are used to improve the system’s

CMRR and to reduce superimposed noise and interference signals.

Replacement of a standard polysilicon resistor with a pseudo-resistor composed of two MOSFETS enables the design of an OA with a very low quiescent current. Values of these resistors are in hundreds of G

or even in units of T

[

16,

17,

18,

19]—this means currents lower than 100 pA. However, poor linearity and especially leakage currents of some devices may become significant and cause system non-functionality. For example, in the utilized technology, the leakage current of the MIM capacitor is in units of nA at 85 °C when the voltage across a capacitor is 0.1 V. Further, MOSFET´s parasitic substrate, off-state, or gate current may have a significant impact on system functionality. Therefore, polysilicon high-precision non-silicided resistors are employed in the proposed system, the block diagram of which is shown in

Figure 2.

The first block contains the active ground circuit and INA, whose gain, denoted as , is set with respect to the nature of the EMG signal to ensure the INA does not saturate when the maximum signal amplitude appears at the input. It is also important to take into account the offset voltage of both the INA and active ground circuit; the sum is amplified by the gain given by the coefficient and then may contribute to the INA saturation. The first block also contains the active ground circuit setting the common-mode voltage () and shielding.

The next circuit is a passive 1st-order HPF with a cutoff frequency of 20 Hz. Its purpose is to reduce the skin potentials and motion artifacts, as mentioned earlier, and minimize the dc component arising from the previous stage. However, the low cut-off frequency requires large values of capacitors and resistors, which occupy a large silicon area. For this reason, external capacitors (

) are used, while resistors (

) are implemented directly on the chip. The filter´s output is led to the PGA with adjustable gains of 2, 5, 10, or 20. The total gain of the AFE can be calculated as

The gain of the PGA is controlled by two digital control bits decoded into one of three outputs driving particular gain settings. Then, the PGA’s output signal is converted into a digital one for further signal processing. A suitable type of ADC could be an asynchronous delta-sigma modulator presented in [

2] or a continuous delta-sigma modulator [

20]; both have implicit antialiasing filters, low power consumption, or relaxed requirements on analog circuits.

2.1. Active Grounding and Shielding

The active grounding circuit is shown in

Figure 3. It consists of four operational amplifiers (OA

), five resistors, and two capacitors. Two unity gain stages A

and A

prevent biopotential signals from being affected by load currents produced by resistors in a common-mode voltage (

) generator comprising two resistors (

) with a value of 500 k

. The following unity gain stage (A

) output is connected to an inverting A

configuration and a low-impedance conductor (shield), which surrounds the input signal line and prevents external interference. Shielding brings several benefits, such as minimizing the effect of unequal cable capacities or minimizing leakage currents [

21,

22,

23].

With a feedback loop gain of

, the effective impedance of E3 is significantly reduced. This scheme is also known as driven-right-leg to suppress 50/60 Hz interference [

24]. When active grounding is employed,

is defined as

where

is the displacement current from the mains with a value in the range of few nA to several

A depending on the surroundings, and

is the active grounding electrode impedance, which is reduced by a gain of

, mathematically described as

Increasing leads to a decrease in the deviation. Resistor values are designed to give = 40 and simultaneously low A loading current, which results in a reduction in power consumption of A. Therefore, = 20 k and = 780 k have been chosen. Resistor does not affect . Its function is associated with protecting a patient from a possible excessive flow of currents due to the A defect when this resistor limits A output current to the maximal value given by . The output current is limited to 50 µA in this design, thus .

Additionally, the amplifiers’ offset or polarization voltage across the electrode interface may introduce further deviation in

, increasing the amplifiers’ input dynamic range requirements. Considering these parameters, (

2) can be extended; thus

where

denotes the offset voltages of amplifiers A

from

Figure 3;

are the polarization voltages of electrodes. For simplicity, it is assumed that

(without mismatch errors).

Due to the active grounding circuit composing negative feedback, the loop stability must be examined. Capacitors

= 10 pF and

= 190 pF are implemented to provide a stable active ground loop, which requires a phase margin of at least 45° across PVT corners [

25].

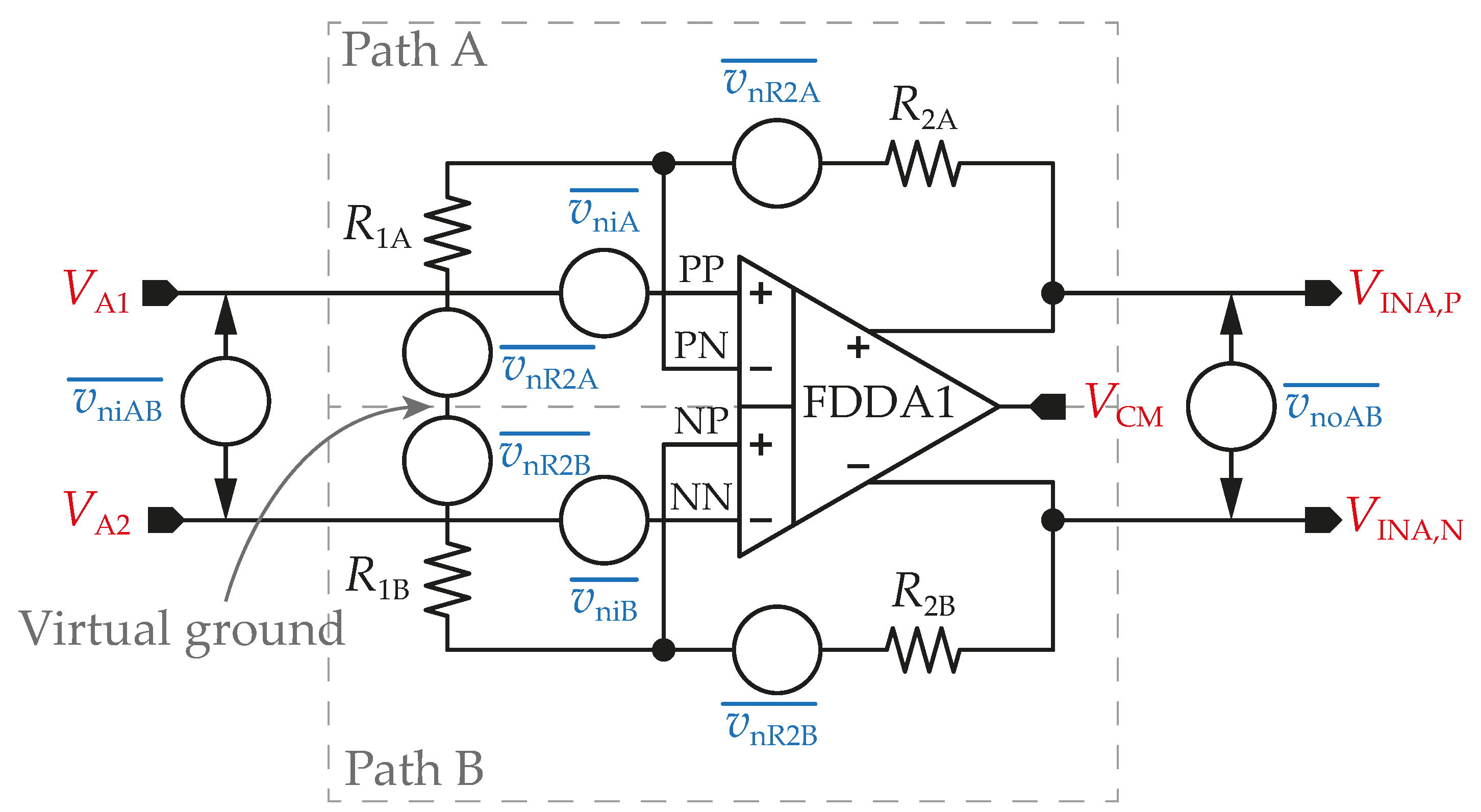

2.2. Instrumentation Amplifier (INA)

The input amplifier stage is realized via an INA with a high

CMRR for interference reduction. However, a classical triple operational amplifier INA’s

CMRR strongly depends on a mismatch of internal resistances, where perfect matching is necessary to obtain a high

CMRR. If a triple-OA INA is utilized, an HPF must be added to the INA input to reduce the dc offset. Detailed analysis of different INA structures is given in [

26,

27]. In this paper, an FDDA INA architecture has been chosen. The FDDA architecture can obtain high

CMRR without perfect matching of resistances; it has good

CMRR even if there are variations in process parameters. The architecture offers good performance in high input impedance and high

CMRR. The maximum gain is limited so as not to make the DDA output saturated to the supply voltage. According to

Table 1, the maximum input signal amplitude is

= 10 mV. Furthermore, if

= 220 mV [

27,

28],

= 5 mV,

= 51 k

, and

µA are considered, the theoretical maximum voltage swing at A

input can be calculated from

By assuming that

,

and

, (

5) can be simplified to

which results in

mV in the worst case; based on this value, the closed-loop gain (

) is set to 10. Parameter

is defined as

where

is the DDA’s open-loop gain,

= 100 k

and

= 450 k

.

The next important property of the INA is its high input impedance. Large electrode impedance may attenuate the biopotential signal before amplification due to the limited INA input impedance (

). Moreover, a low-frequency biopotential signal near dc is prone to distortion since the capacitance

reduces the electrode impedance as the frequency increases. If the impedance is not high enough, the phase shift of the low-frequency signal can be pronounced [

27,

29].

2.3. High-Pass Filter (HPF) and Programmable Gain Amplifier (PGA)

Before further amplifying, the dc offset of the PGA´s input signal must be removed. The classical HPF with resistors connected to ground suffers from finite common-mode input impedance that may degrade the

CMRR. A better option is to utilize a floating HPF, which has very large common-mode input impedance achieved by eliminating resistors to ground while the cutoff frequency is still the same. Component parameters are

= 800 k

and

= 10 nF, for a cutoff frequency of 20 Hz, when

is implemented as the external component. As will be proposed in the next section, the FDDA1 uses a CMFB circuit that includes a resistor divider composed of two resistors, designated

and

. These resistors are also utilized in the HPF to save power and chip area, as illustrated in

Figure 4.

The topology of the PGA is the same as the INA circuit, with the exception of an adjustable value consisting of a chain of resistors = 26.3 k, = 29.2 k, = 194.5 k, and = 250 k in series. Three CMOS switches set the value to 52.6 k, 111 k, 500 k, or 1 M between the PN and NP inputs of the FDDA2. Minimum gain is set as the default condition in the case of all switches being OFF to prevent glitches during switching among measured ranges. Resistor , with a value of 500 k, is divided into 50 k segments to increase the resistor’s matching accuracy.

2.4. Noise

Amplifiers A

generate noise coupled to the active ground signal line. However, this signal is applied to both electrodes E1 and E2, and due to fully differential signal processing, the noise signal of A

is canceled out. For the cascade of gain stages, the most important noise contribution comes from the first stage. To represent the noise of each stage with an input referred generator, the AFE´s noise is given by

Referring to the input of the AFE, this results in

This proves the assumption that the noise of the first stage is the most significant. The same is valid for an internal topology of multi-stage operational amplifiers, where the noise of the first stage implemented as a differential pair is dominant.

3. Circuit Design on the Transistor Level

In this section, the implementation of the three different amplifiers at the transistor level will be described. The amplifiers utilize the band-gap reference (IP core), which provides the and multiple current outputs and . The circuit power supply is 1 V ( = 1 V). This does not provide sufficient voltage headroom for cascaded topologies if all MOSFETs work in strong or moderate inversion. The employed technology offers regular (RVT) and low-voltage threshold (LVT) MOSFETs. However, they cannot be easily mixed without guard ring protection in some cases.

3.1. Operational Amplifier (A–A)

The folded cascode has been chosen as the structure of the amplifier A

mainly due to the high gain–bandwidth product (

GBW); it has only one single non-dominant pole, and it is very fast. The folded cascode structure is also an excellent first stage for a two-stage Miller CMOS OTA [

30]. The topology of the circuit utilized in the components

is shown in

Figure 5.

An important parameter of the amplifier is the input common mode range (

). As has been derived from (

6), the maximum voltage swing at A

input is

mV in the worst case. Next, the amplifier A

is connected to the

node; its input voltage range is not affected by

and is directly equal to the

variation according to (

4). That is, ±18 mV. The last amplifier (A

) used in an inverting configuration keeps the input voltage at noninverting and inverting terminals at

and

, respectively. Based on these considerations, the input differential pair is designed with LVT PMOS transistors (M

) and their threshold voltage (

) is further reduced by connecting the back gate electrode to

. Besides the input transistors, the threshold voltages of RVT transistors M

are also lowered by connecting the back gate electrode to

. In the case of M

(LVT NMOS), their back gate electrode is connected to the transistors’ sources only to eliminate the body effect. Care must be taken to ensure sufficient voltage remains on the M

drains and that they operate in the saturation region. Mathematically,

is

Voltage is set by , whose maximum value is limited by the voltage headroom in the branch M. When variation is considered as well as the body effect occurring if the back gate electrode is connected to , transistor M saturation would not be guaranteed.

3.1.1. Input Common Mode Range

The minimum value of

of the proposed folded cascode topology is limited by the requirement that M

operate in saturation at all times. Thus,

should be at most

below the voltage at the drains of M

. The latter voltage is determined by

and must allow for a voltage drop across M

at least equal to their overdrive voltage,

. Assuming that M

are operated at the edge of saturation,

is

The maximum value of

is limited by the need to keep M

always operating in saturation, which is assured by keeping the voltage across M

equal to or greater than

at all times. Thus

While the minimum value can be easily achieved, the maximum value needs to design M and M with the minimum possible and use LVT transistors instead of RVT in the case of M. Furthermore, of M is further lowered by connecting the back gate electrode to .

Due to the fact that A are connected as voltage followers, their output voltage swing is the same as the input voltage range. The inverting amplifiers’ output is directly connected to the active ground electrode; thus, A4’s output voltage swing should be as large as possible.

3.1.2. Voltage Gain

The second stage is added to the circuit to achieve a higher voltage gain, higher output voltage swing, and the capability to drive the resistance load without a major impact on voltage gain and phase margin. Further, when the output voltage is close to

, the output transistor M

enters the linear region, and the second stage loses gain, there is still sufficient gain remaining in the first stage to suppress the distortion. The dc open-loop gain can be mathematically expressed as

3.1.3. Noise

The noise analysis is based on the assumption, as mentioned earlier, that the cascoding amplifier stages have a minor impact on the equivalent input-referred noise because their contribution is attenuated by the voltage gain of the previous stage. The same situation applies in a two-stage amplifier for the transistors in the second stage.

The noise of the current source implemented via M

has a negligible effect on the output voltage since it flows evenly in the two branches, which are assumed to be well-matched. The noise of cascaded transistors M

is also neglected because their noise gain to the output is considerably lower than the gain from M

, M

, and M

. The contribution of the transistors M

, M

, and M

to the input-referred noise voltage can be expressed as

,

, and

, respectively. The total input-referred noise is then given by

where

where

j denotes the number of the transistor (1, 3, or 8),

k is Boltzmann’s constant,

T is the temperature in kelvin,

is the bias-dependent noise parameter,

is the transistor’s transconductance,

is the flicker noise coefficient (process-dependent constant),

represents the oxide capacitance per unit area,

L is the transistor length,

is the drain current, and

f is the frequency. Note that a bandwidth of 1 Hz is assumed.

The flicker (or

) noise corner frequency is

This result implies that generally depends on the device’s area and transconductance. To reduce the impact of noise, the device’s area must be large. Generally, PMOS devices exhibit less noise than NMOS transistors.

The formula for calculating the total thermal noise and

noise of a single transistor for a band from

to

can be obtained by modifying (

14). That is,

Simplification in the second part of (

17) can be performed if

. At frequencies beyond

, the contribution of

noise can be ignored, while the thermal noise becomes dominant.

3.1.4. Simulations

The frequency responses of the amplifier are represented in

Figure 6.

Figure 6a shows that the input-referred noise varies from 2.5 to 3.2 µV/

at 1 Hz over the process corners. The total integrated input-referred noise in the frequency range 20 Hz–2 kHz is obtained; 7.6 µV in the typical process corner. Next, as presented in

Figure 6b, the input impedance corner values are 26.5 G

(FF corner) and 48 G

(SS corner) at the frequency of 1 Hz. The value for the typical process is 14.2 G

.

Figure 6c indicates that the dc gain is in the range 118 dB–132 dB, with a value of 128 dB (phase margin of 70°) for the typical process corner. The results also demonstrate that the proposed amplifier is stable (phase margin > 61° in the worst case). Finally,

Figure 6d shows

CMRR = 88 dB in the typical process corner when it drops to 78 dB in the worst case. The standard deviation of the dc offset is 2.1 mV, and the simulated power consumption is 8 µW.

3.2. Fully Differential Difference Differential Amplifier (FDDA1)

The gain stage is composed of an amplifier, denoted as FDDA1, which is implemented as a fully differential non-inverting gain stage with a very large input impedance. Due to the fully differential structure, designing a common-mode feedback (CMFB) circuit was also required. The CMFB loop could adjust either

or

by controlling the gate voltages of the transistors that generate those currents. The CMFB’s gain is provided by common-source NMOS transistors M

, which have larger

than PMOS transistors when the same size is used. The output of FDDA1 is loaded by resistors in the CMFB circuit, resistors in the feedback loop setting the gain (

), and components in the HPF comprising further resistors and large external capacitors. Therefore, the amplifier is designed with class AB output stages to ensure the capability to drive this load. Moreover, they can generate much greater output currents than the total bias current in the output stage and save power. The complete circuit schematic is shown in

Figure 7.

The input differential pairs consist of LVT PMOS transistors M

and M

with the back gate electrode connected to

. Then, the input stage provides a sufficiently large input voltage range when expected fluctuation has been derived in (

6) to be

28 mV. Three inverting common-source amplifiers follow the differential stage. The first two inverting amplifiers (M

or M

and M

or M

) are combined with the gate-drain feedback to behave as a single noninverting common-source stage. The gain-drain feedback is created across the second common-source amplifier by resistor

. Transistors M

and M

form the output class AB rail-to-rail stage. A detailed analysis of this three-stage class AB topology has been proposed in [

31].

3.2.1. Input Common-Mode Range

The minimum value of

of the proposed FDDA1 topology is limited by the requirement that M

operate in saturation at all times. Thus,

should be at most

below the voltage at the drains of M

. Assuming that M

are operated at the edge of saturation,

is given by

Due to the fact that FDDA1 operates in the closed-loop configuration with a gain of 10, the output voltage can vary over a range determined by (

6) extended with the FDDA1 offset. Thus,

where

is FDDA1´s offset voltage. According to (

6), the output voltage swing can reach values up to

when

= 5 mV is assumed.

The maximum value of

is limited by the need to keep current mirrors composed of M

always operating in saturation, which is assured by keeping the voltage across M

equal to or greater than

at all times. Then,

3.2.2. Voltage Gain

The overall gain and effective number of amplifier stages are decreased from four to three by introducing feedback resistor

. The first stage consists of differential pairs with the active load formed by M

. Its gain can be expressed as

The second amplifier stage is constituted from the cascade of the first two inverting common-source amplifiers (M

and M

) that behave as a single stage. The second stage gain is given as [

31]

The gain of the amplifier is approximately the product of the gains of all three stages and is given by

3.2.3. Noise

The transistors in the amplifier’s first stage have a dominant effect on the FDDA1 noise, as was mentioned for multistage amplifiers in

Section 2.4. The noise of the current sources implemented via M

have a negligible effect on the output voltage since they affect evenly all four branches, which are assumed to be well-matched. All other transistors in the first stage affect the input-referred noise as follows

where

(

j denotes the transistor number) has been defined in (

15).

Since the amplifier operates with resistor feedback, it is necessary to consider their noise.

Figure 8 shows the implementation of a feedback amplifier using FDDA1, including noise sources modeling the resistors’ thermal noise.

Each source makes its own contribution to the noise at the amplifier’s output. At the beginning, input-referred noise is derived. Resistor R

is divided into two parts, R

and R

; each belongs to the corresponding feedback. A node between R

and R

behaves as the virtual ground; that is,

in this case. Then, each feedback path can be analyzed separately. Firstly, the impact of path A on the amplifier input-referred noise can be mathematically described as

where the noise from a resistor is modeled as

.

Extending the noise analysis to the feedback path B, assumed as well-matched with the feedback path A, an equation for the overall FDDA1 input-referred noise can be written as

The output-referred noise can be simply calculated by multiplying the input-referred noise by the gain of the amplifier.

It should be noted that a single-pole system is assumed where the feedback network is purely resistive and that the noise gain versus frequency is flat. Otherwise, capacitances (e.g., FDDA1’s input capacitance, load capacitance, etc.) cause the noise gain not to be constant over the bandwidth of interest, and more complex techniques must be used to calculate the total noise.

3.2.4. Simulations

The simulation results for FDDA1 are presented in

Figure 9.

Figure 9a shows that the input-referred noise of FDDA1 is 1.6 µV/

at 1 Hz over the process corners, with the resistors in the feedback having a negligible effect on the overall noise. The total integrated input-referred noise in the frequency range 20 Hz–2 kHz is obtained as 5.7 µV. Next, as presented in

Figure 9b, the input impedance corner values are 8.6 G

(FF corner) and 54 G

(SS corner) at the frequency of 20 Hz. The value for the typical process is 37 G

.

Figure 9c indicates that the gain varies from 91.1 dB to 101.5 dB, with a value of 98.7 dB (phase margin of 80.6°) for the typical process corner. The results also demonstrate that the proposed system is stable (phase margin > 78.5° in the worst case). The

CMRR parameter of the fully differential FDDA1 was verified using Monte Carlo analyses that comprised fifth-hundred samples for the global and local process variations.

Figure 9d shows the mean value of 89 dB when the sigma deviation is 9.42 dB. The standard deviation of the dc offset is 3.9 mV, and the simulated power consumption is 7.1 µW.

3.3. Fully Differential Difference Amplifier for PGA (FDDA2)

The signal coming into the PGA block is divested of the dc component, and thereby, FDDA2 amplifies only the ac signal in the bandwidth of interest together with a small dc component in the form of its own offset. The maximum amplitude of the ac signal from FDDA1 is given by

= 100 mV. Considering the impact of process variations, it would not be possible for a simple input differential pair to process such amplitude; hence the differential pair is designed as rail-to-rail with two input pairs (PMOS and NMOS) in parallel as illustrated in

Figure 10.

Both input differential pairs utilize LVT transistors with further lowered by connecting their back gate electrode and in the NMOS and PMOS pair, respectively. However, this solution needs to create triple-well isolation in the case of the PMOS transistors, negatively affecting the input voltage offset.

For

and

, we can write

Since the amplifier’s output is loaded by a large resistance composed of resistors in the CMFB circuit and feedback, the second stage employs a rail-to-rail class A common source amplifier. Then, the dc open-loop gain is given by

The noise is derived according to the principles mentioned for the previous two amplifiers. Then, we can write

where

(

j denotes the transistor number) has been defined in (

15).

If the noise of the whole PGA is considered, i.e., with feedback resistors, the total noise will depend on the selected gain. Equation (

27) can therefore be rewritten as

where

k can be an even number in the specified interval.

The simulation results for FDDA2 are presented in

Figure 11.

Figure 11a shows that the input-referred noise of FDDA2 is 3 µV/

at 1 Hz over the process corners, with the resistors in the feedback having a negligible effect on the overall noise. The total integrated input-referred noise in the frequency range 20 Hz–2 kHz is obtained as 7.5 µV. Next, as presented in

Figure 11b, the input impedance corner values are 7.4 G

(FF corner) and 61 G

(SS corner) at the frequency of 20 Hz. The value for the typical process is 35 G

.

Figure 11c indicates that the gain varies from 97.6 dB to 120.6 dB, with a value of 113 dB (phase margin of 80.3°) for the typical process corner. The results also demonstrate that the proposed system is stable (phase margin > 79° in the worst case). The

CMRR parameter of the fully differential FDDA1 was verified using Monte Carlo analyses that comprised fifth-hundred samples for the global and local process variations.

Figure 11d shows the mean value of 75.9 dB when the sigma deviation is 9.42 dB. The standard deviation of the dc offset is 4.4 mV, and the simulated power consumption is 8.6 µW.

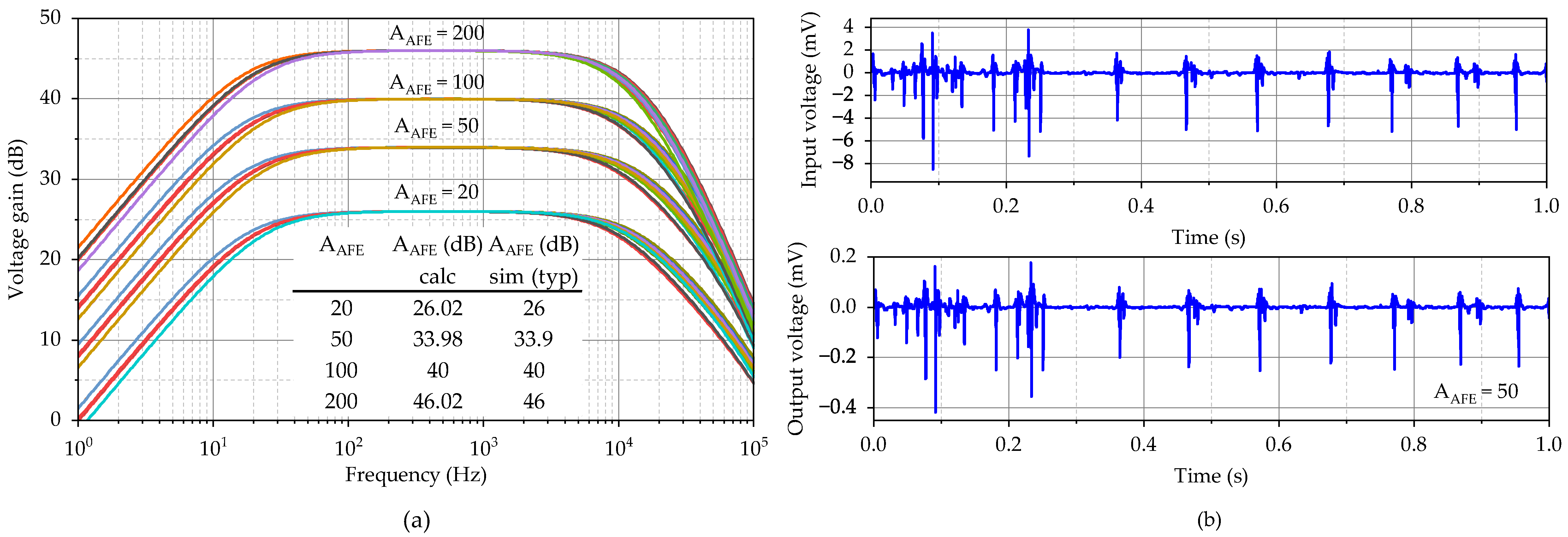

4. Simulation Results

The proposed AFE was designed using STMicroelectronics 28 nm FDSOI technology with a 1 V supply voltage. Proper functionality against PVT variations was verified; a supply voltage variation of and a commercial temperature range from 0 °C to 70 °C were considered. The circuit layout has not been created; nevertheless, an estimate of the area is presented, derived from the sum of the areas occupied by each component, setting according to the boundary layer with a margin for metal paths. The total area is 0.09 mm, with the amplifiers (A–A) occupying 0.017 mm (OA), 0.021 mm (FDDA1), 0.008 mm (FDDA2), and 0.034 mm, together with , and the rest of the area is occupied by feedback resistors.

In the first step, the active ground loop stability was investigated. The electrical model of the Ag/AgCl electrode with component values used for the simulation was adopted from [

32]. The simulation results are shown in

Figure 12, including the circuit diagram of the electrode with the component values in

Figure 12a.

Figure 12b shows the extracted phase margin of all PVT corner runs. In order to secure the active ground feedback loop’s stability, two capacitors,

= 10 pF and

= 190 pF, are implemented into the circuit. As can be seen from

Figure 12b, the minimum value of the phase margin over the PVT range is 44.1°. For typical conditions, the phase margin takes the value 54.7°. The gain of the feedback loop is 32 dB, which corresponds to the assumptions in (

3).

In the second step, the

CMRR of the system was analyzed. The input signal source was connected between electrodes E2 and E3, while electrodes E1 and E2 were connected together; thus, the same signal occurred at two FDDA1 inputs. The impact of

CMRR was probed at the fully differential output of FDDA2. In order to find correct values, the almost ideal symmetry of the fully differential structure must be broken. Therefore, a Monte Carlo analysis with 500 runs was employed, where both process and mismatch variation were performed. As a result, the frequency response and several histograms are shown; the mean value and standard deviation of 1

are noted for each of them, as shown in

Figure 13. The results show that the mean value of

CMRR fluctuates from 92.5 to 111.5 dB (105.5 typical) and a standard deviation of about

dB is obtained.

Figure 14a depicts the input impedance of the system, which consists of a parallel combination of input resistance OA and FDDA1. The typical dc value of 11 GOhm is achieved, while the minimum dc value from the PVT corner analysis is 2.1 G

. As the resistance decreases with frequency, its minimum value, 4.2 M

, appears at the maximum frequency of the band of interest (2 kHz).

Figure 14b illustrates the input noise of the system measured between nodes V

and V

(FDDA1 inputs), which is 3.2 µV/

at 27 °C and 3.5 µV/

at 70 °C in the worst case.

The system amplification for all four settings, i.e., 20, 50, 100, and 200, is shown in

Figure 15a, and a table with simulated

values at 1 kHz is also delivered. The amplification is defined by the ratio of the feedback resistors, whose values and, thereby, areas are large. The process variance will not practically affect the gain; however, a mismatch between the resistors will. Due to the large area of the resistors, good matching is achieved, and the gain error is very small in the order of tens of dB.

Figure 15b shows the processing of an EMG recording [

33] of a patient with neuropathy when the system gain was set to 50.

The parameters of the proposed system are summarized in

Table 2, where they are further compared with related works.

Many studies are dealing with biological signal processing, mostly ECG; however, ECG signals have significantly lower bandwidths requiring a different design approach. Therefore, papers proposing systems suitable for signal processing in the order of a few kHz were chosen for the comparison table except for [

37,

38]. These papers are listed because the presented topology contains a similar active ground circuit and has high

CMRR in the case of [

37,

38].

Compared with other works, this design presents the highest CMRR (105.5 dB), achieved using an active ground circuit. The active ground circuit contains several buffers; hence, higher CMRR is achieved at the cost of higher power consumption. The designed circuit is also characterized by high input impedance and tunable gain.