Integrated Filter Design for Analog Field Mill Sensor Interface

Abstract

1. Introduction

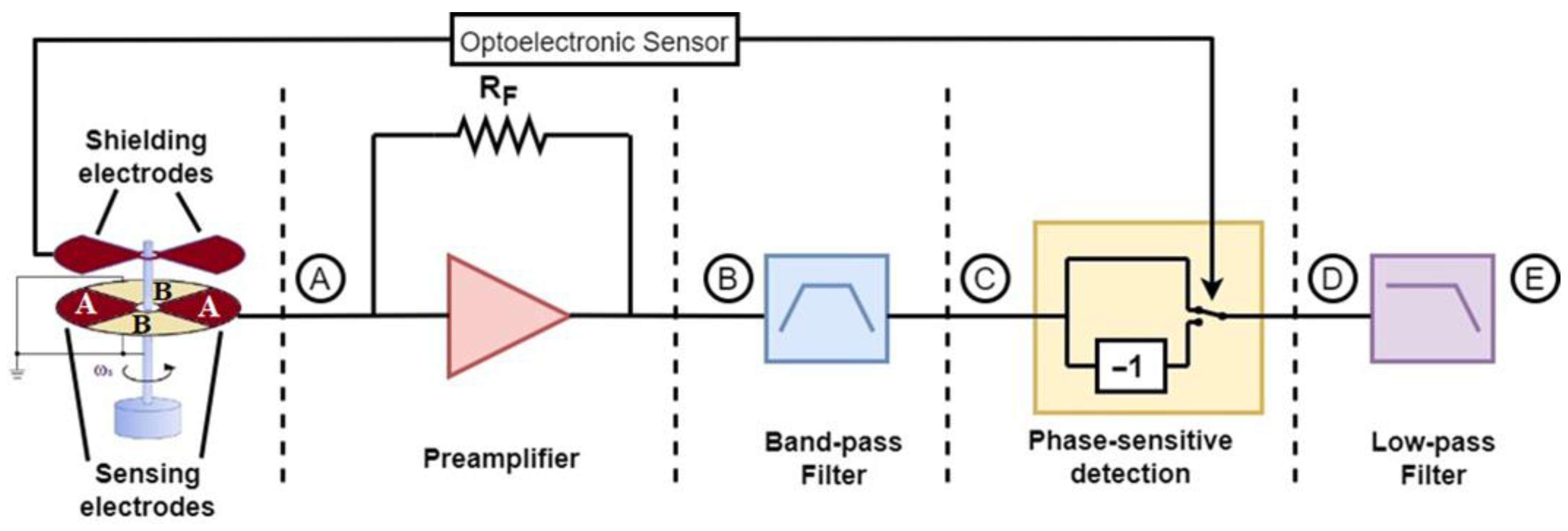

2. Electric Field Mill Sensor Interface and Specifications

3. Integrated Filter Design Theory and Techniques

3.1. Higher Order Filters Using Cascaded Topologies

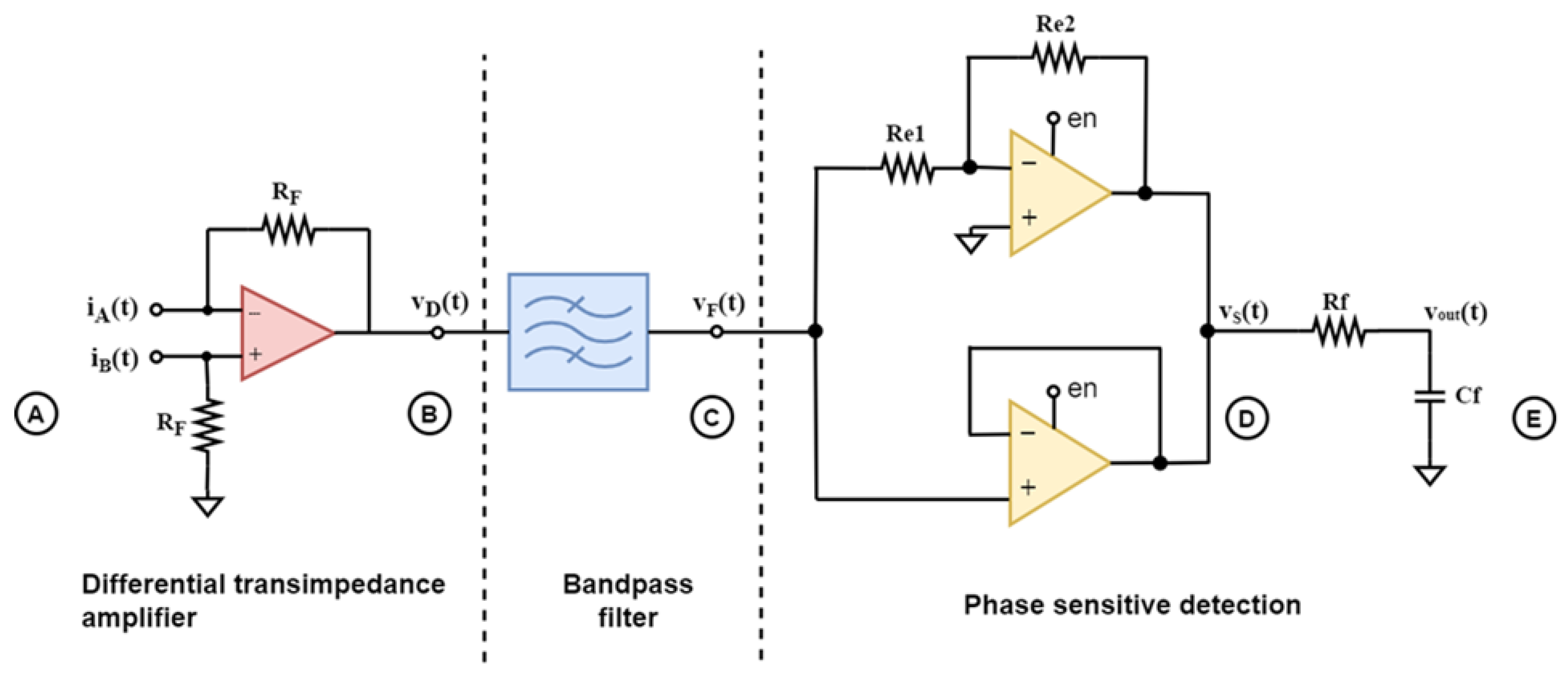

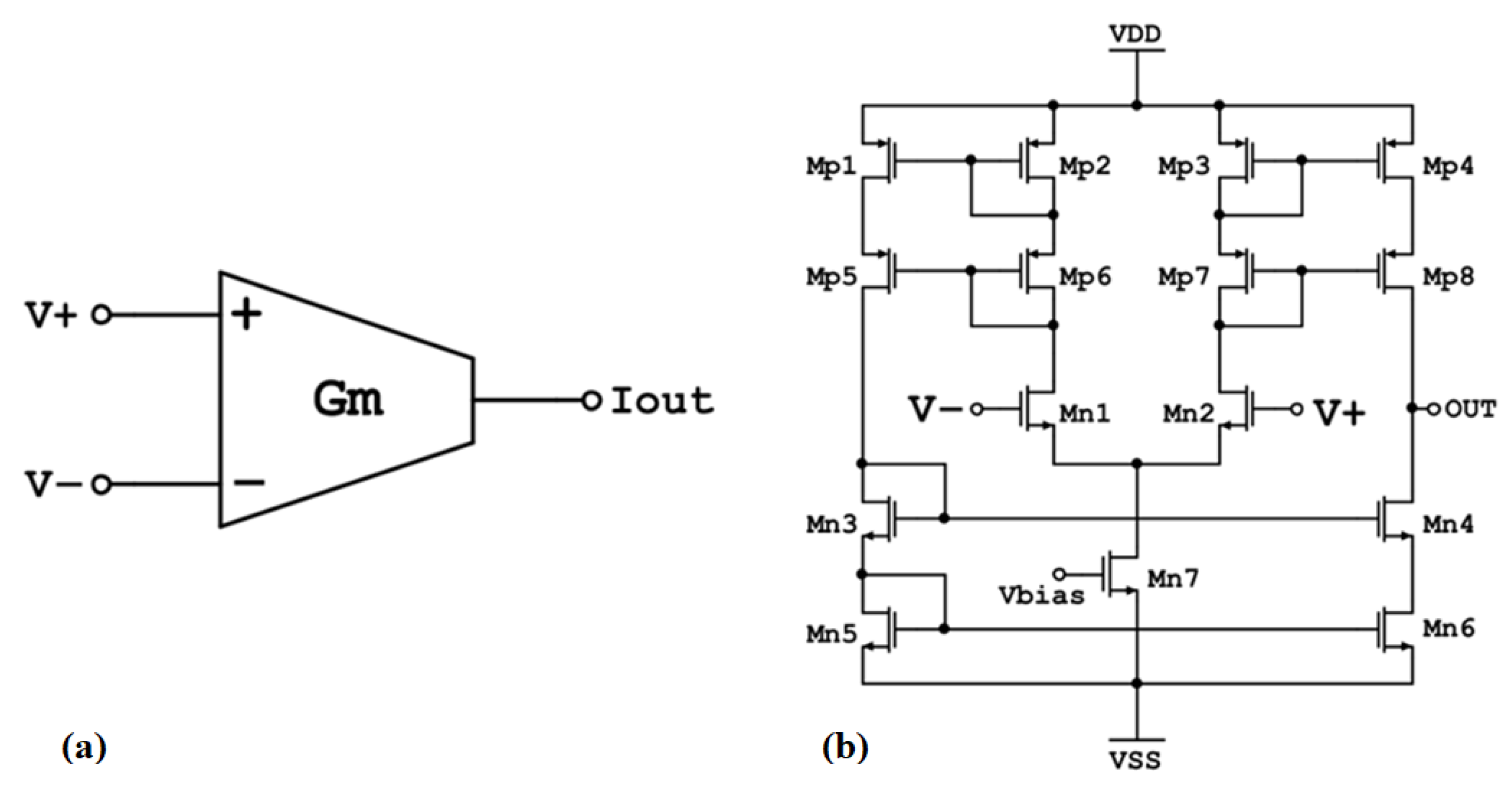

3.2. Cascaded Topologies with OTA-Based Passive Element Replacement

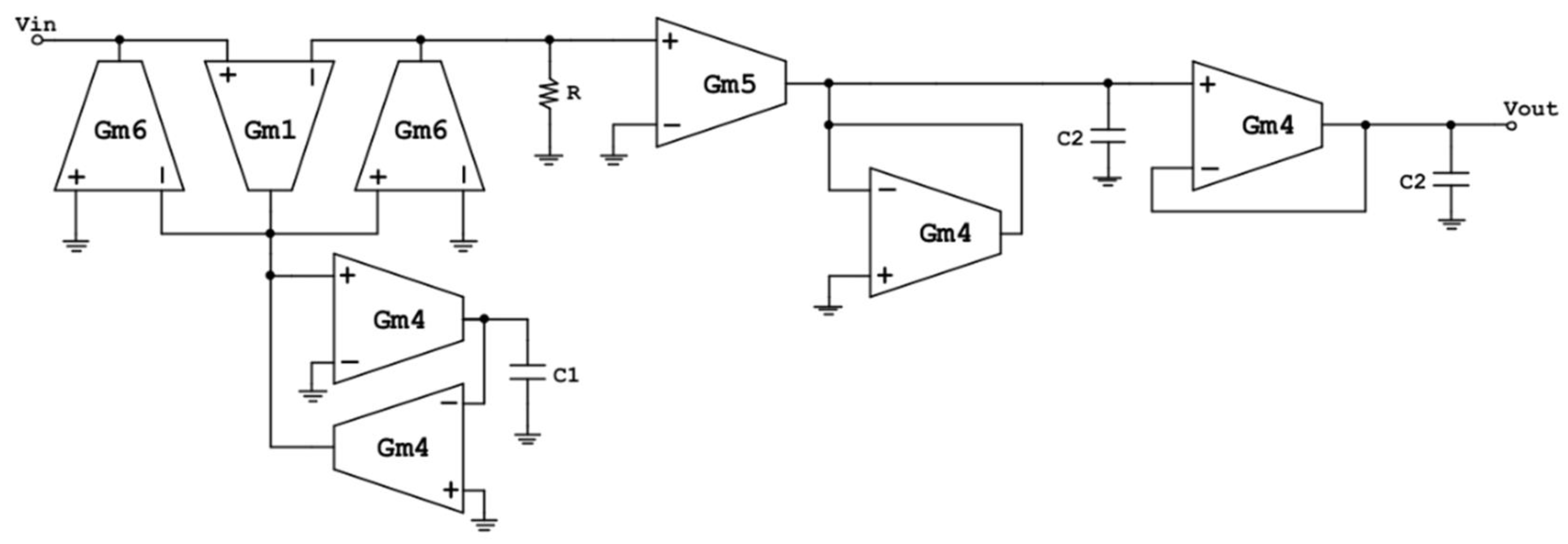

3.3. Bandpass Filter Using Leapfrog Technique

3.4. Filters Comparison

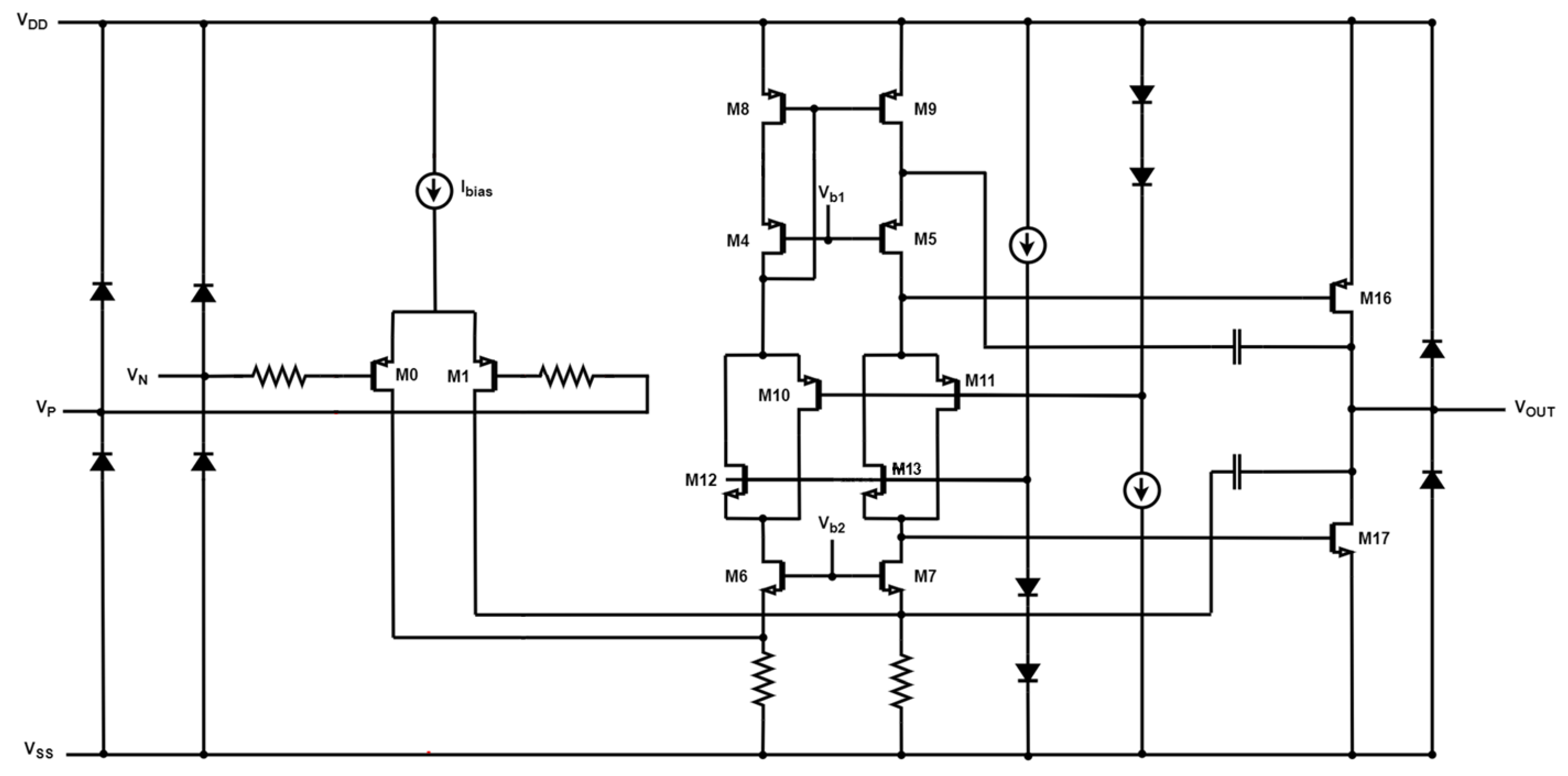

3.5. Narrow Bandpass Filter

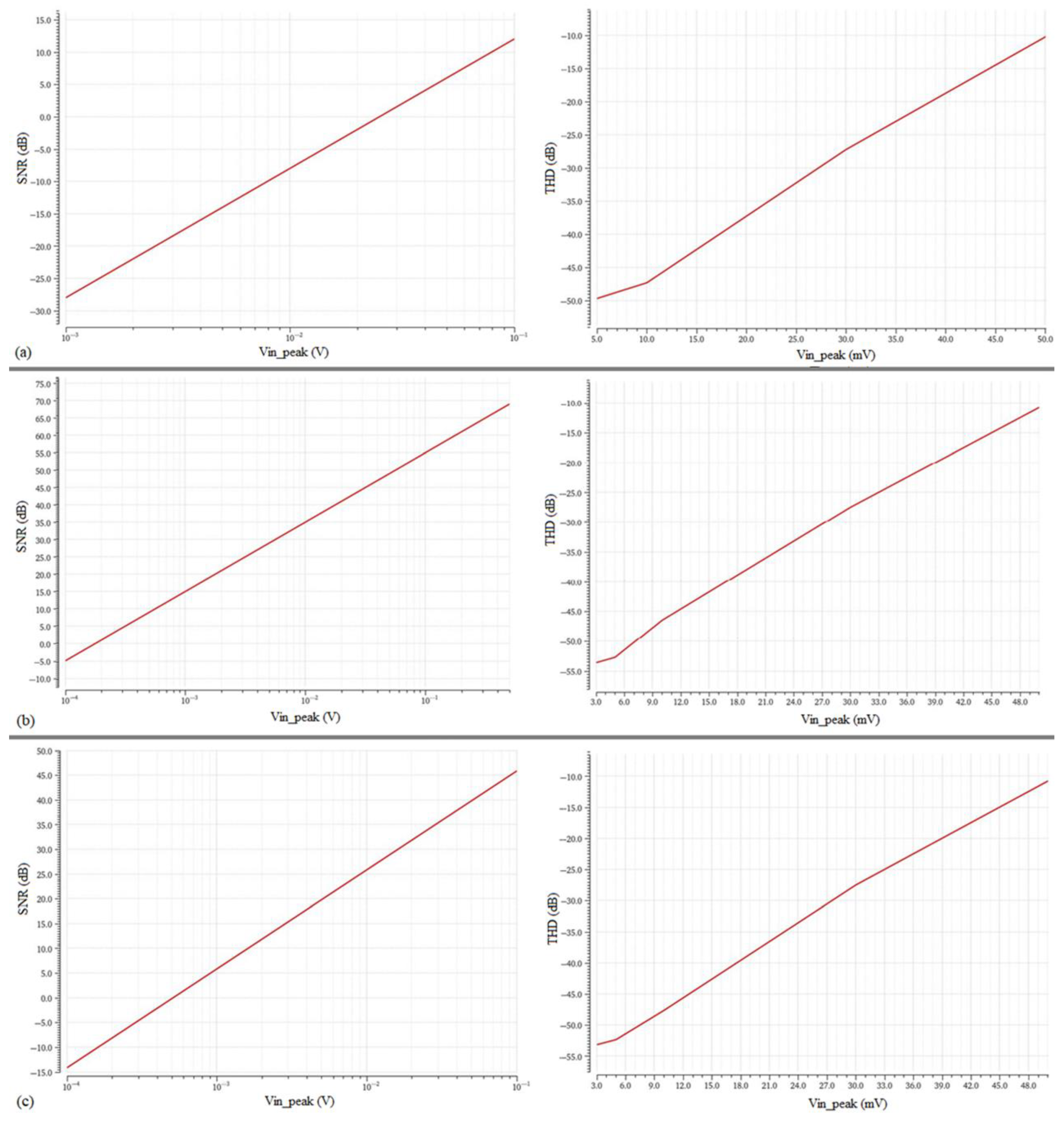

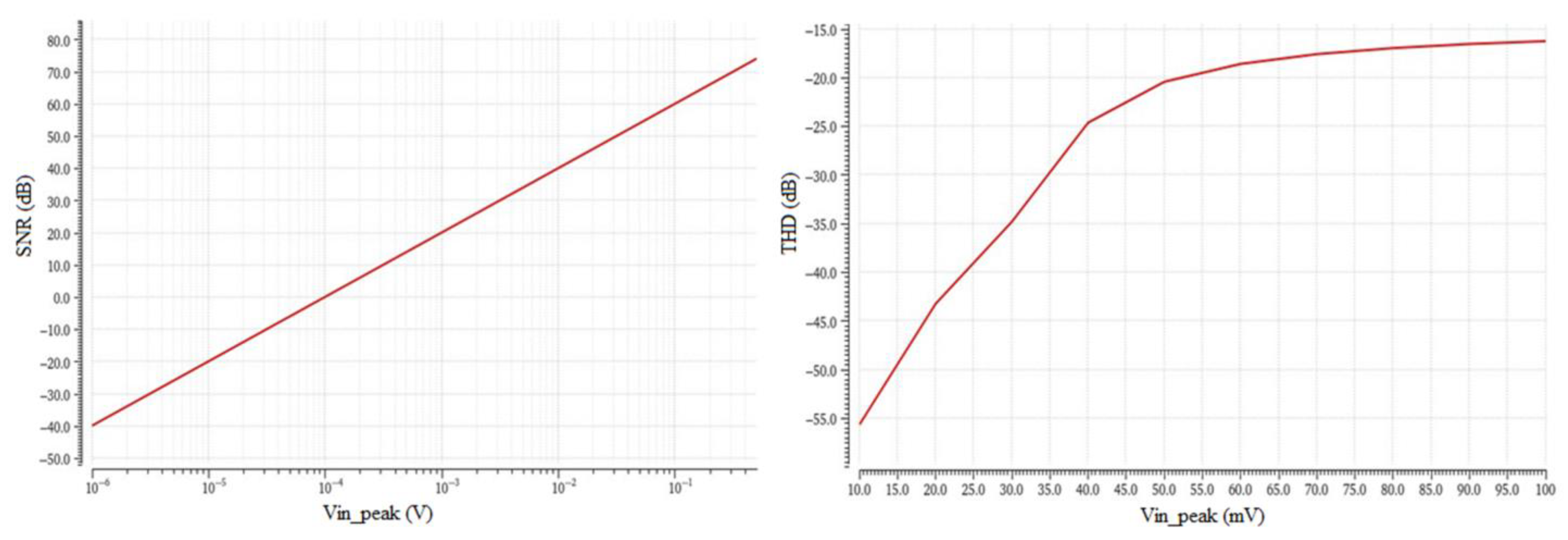

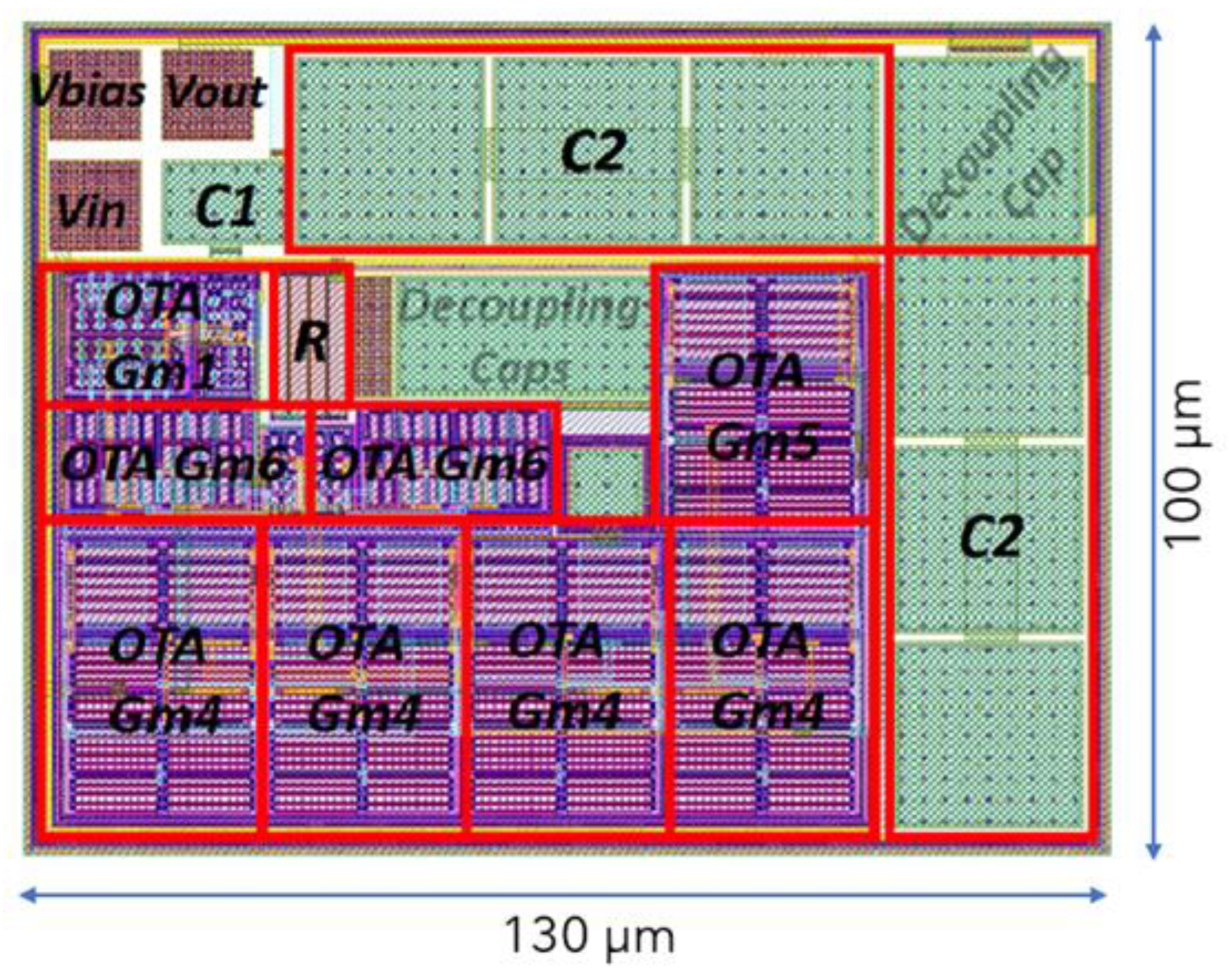

4. Simulation Results

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Maruvada, P.; Dallaire, R.; Pedneault, R. Development Of Field-Mill Instruments For Ground-Level And Above-Ground Electric Field Measurement Under HVDC Transmission Lines. IEEE Trans. Power Appar. Syst. 1983, PAS-102, 738–744. [Google Scholar] [CrossRef]

- Cui, Y.; Song, X.; Wang, C.; Zhao, L.; Wu, G. Ground-Level DC Electric Field Sensor For Overhead HVDC/HVAC Transmission Lines In Hybrid Corridors. IET Gener. Transm. Distrib. 2020, 14, 4173–4178. [Google Scholar] [CrossRef]

- Bateman, M.; Stewart, M.; Podgorny, S.; Christian, H.; Mach, D.; Blakeslee, R.; Bailey, J.; Daskar, D. A Low-Noise, Microprocessor-Controlled, Internally Digitizing Rotating-Vane Electric Field Mill For Airborne Platforms. J. Atmos. Ocean. Technol. 2007, 24, 1245–1255. [Google Scholar] [CrossRef]

- Antunes de Sá, A.; Marshall, R.; Sousa, A.; Viets, A.; Deierling, W. An Array Of Low-Cost, High-Speed, Autonomous Electric Field Mills For Thunderstorm Research. Earth Space Sci. 2020, 7, e2020EA001309. [Google Scholar] [CrossRef] [PubMed]

- Harrison, R.; Marlton, G. Fair Weather Electric Field Meter For Atmospheric Science Platforms. J. Electrost. 2020, 107, 103489. [Google Scholar] [CrossRef]

- Wang, G.; Kim, W.; Kil, G.; Park, D.; Kim, S. An Intelligent Lightning Warning System Based On Electromagnetic Field And Neural Network. Energies 2019, 12, 1275. [Google Scholar] [CrossRef]

- Xu, W.; Zhang, C.; Ji, X.; Xing, H. Inversion of a Thunderstorm Cloud Charging Model Based on a 3D Atmospheric Electric Field. Appl. Sci. 2018, 8, 2642. [Google Scholar] [CrossRef]

- Cui, Y.; Yuan, H.; Song, X.; Zhao, L.; Liu, Y.; Lin, L. Model, Design, And Testing Of Field Mill Sensors For Measuring Electric Fields Under High-Voltage Direct-Current Power Lines. IEEE Trans. Ind. Electron. 2018, 65, 608–615. [Google Scholar] [CrossRef]

- Makihata, M.; Matsushita, K.; Pisano, A.P. MEMS-based non-contact voltage sensor with multi-mode resonance shutter. Sens. Actuators A Phys. 2019, 294, 25–36. [Google Scholar] [CrossRef]

- Wen, X.; Yang, P.; Zhang, Z.; Chu, Z.; Peng, C.; Liu, Y.; Wu, S.; Zhang, B.; Zheng, F. Resolution-Enhancing Structure for the Electric Field Microsensor Chip. Micromachines 2021, 12, 936. [Google Scholar] [CrossRef] [PubMed]

- Agorastou, Z.; Noulis, T.; Siskos, S. Analog Sensor Interface for Field Mill Sensors in Atmospheric Applications. Sensors 2022, 22, 8405. [Google Scholar] [CrossRef] [PubMed]

- Noulis, T.; Deradonis, C.; Siskos, S.; Sarrabayrouse, G. Detailed study of particle detectors OTA-based CMOS Semi-Gaussian shapers. Nucl. Instrum. Methods 2007, 583, 469–478. [Google Scholar] [CrossRef]

- Noulis, T.; Deradonis, C.; Siskos, S. Advanced readout system IC current mode Semi-Gaussian shapers using CCIIs and OTAs. VLSI Des. 2007, 2007, 1–12. [Google Scholar] [CrossRef]

- Sellars, M.P. Electric Field Mill: For the Simultaneous Measurement of Electric Field Strength and Ion Current Density. Master’s Thesis, University of Cape Town, Cape Town, South Africa, 1995. [Google Scholar]

- Agorastou, Z.; Noulis, T.; Siskos, S. Noise-optimized Low-quiescent current CMOS Preamplifier for Electric Field Mill Sensor Interface. In Proceedings of the XXXVII Conference on Design of Circuits and Integrated Systems (DCIS 2022), Pamplona, Spain, 16–18 November 2022. [Google Scholar]

- Lemonou, A.; Agorastou, Z.; Noulis, T.; Siskos, S. Low Noise-Low Power Transimpedance Amplifier Design for Electric Field Sensing. In Proceedings of the 2022 Panhellenic Conference on Electronics & Telecommunications (PACET), Tripolis, Greece, 2–3 December 2022; pp. 1–6. [Google Scholar]

- Hong, X.; Wang, H.; Zhou, J.; Yang, X.; Wang, M.; Ma, Y.; Zhou, W.; Liu, Y.; Zhu, X. Peak tailing cancellation techniques for digital CR-(RC)n filter. Appl. Radiat. Isot. 2021, 167, 109471. [Google Scholar] [CrossRef] [PubMed]

- Sansen, W.M.C.; Chang, Z.Y. Limits of low noise performance of detector readout front ends in CMOS technology. IEEE Trans. Cicuits Syst. 1990, 37, 1375–1382. [Google Scholar] [CrossRef]

- Geiger, R.L.; Sánchez-Sinencio, E. Active Filter Design Using Operational Transconductance Amplifiers: A Tutorial. IEEE Circuits Devices Mag. 1985, 1, 20–32. [Google Scholar] [CrossRef]

- Schaumann, R.; Valkenburg, M.E. Design of Analog Filters; Oxford University Press: New York, NY, USA, 2001. [Google Scholar]

- Deliyannis, T.; Sun, Y.; Fidler, K. Continuous-Time Active Filter Design; CRC Press LLC.: Boca Raton, FL, USA, 1999. [Google Scholar]

- Pactitis, S.A. Active Filters. In Theory and Design; CRC Press LLC: Boca Raton, FL, USA, 2007. [Google Scholar]

- Noulis, T.; Siskos, S.; Sarrabayrouse, G. Development and Testing of an Advanced CMOS Readout Architecture dedicated to X-rays silicon strip detectors. In Proceedings of the Topical Workshop on Electronics for Particle Physics (TWEPP), Naxos, Greece, 15 September 2008. [Google Scholar]

- Martincorena-Arraiza, M.; Carlosena, A.; De La Cruz-Blas, C.A.; Beloso-Legarra, J.; Lopez-Martin, A. A family of AC amplifiers for ultra-low frequency operation. Int. J. Circuit Theory Appl. 2021, 49, 3317–3327. [Google Scholar] [CrossRef]

- Martincorena-Arraiza, M.; De La Cruz-Blas, C.A.; Carlosena, A.; Lopez-Martin, A. AC coupled amplifier with a resistance multiplier technique for ultra-low frequency operation. Int. J. Electron. Commun. 2022, 149, 154176. [Google Scholar] [CrossRef]

- Fort, A.; Mugnaini, M.; Vignoli, V.; Rocchi, S.; Perini, F.; Monari, J.; Schiaffino, M.; Fiocchi, F. Design, Modeling, And Test Of A System For Atmospheric Electric Field Measurement. IEEE Trans. Instrum. Meas. 2011, 60, 2778–2785. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Number of vanes | 6 |

| Motor frequency | 75 Hz |

| Motor type | Brushless DC |

| Signal frequency | 450 Hz |

| Transfer Function H(s) | Gain | |||

|---|---|---|---|---|

| R simulator | ||||

| C simulator | ||||

| L simulator |

| Cascade Topologies | Leapfrog | ||||||

|---|---|---|---|---|---|---|---|

| Resistance Simulator | Capacitance Simulator | Inductance Simulator | |||||

| Gm2 | 1.2 μA/V | Gm1 | 523 μA/V | Gm2 | 1.2 μA/V | Gm2 | 1.2 μA/V |

| Gm3 | 4.8 μA/V | Gm2 | 1.2 μA/V | Gm3 | 4.8 μA/V | Gm4 | 93 nA/V |

| C1 | 11 pF | Gm3 | 4.8 μA/V | C1 | 11 pF | Gm5 | 346 nA/V |

| C2 | 12 pF | C1 | 1.8 pF | C2 | 12 pF | C1 | 8.3 pF |

| R | 1 kΩ | C2 | 12 pF | R | 1 kΩ | C2 | 375 pF |

| R | 22 kΩ | ||||||

| OTA Gm1 | W(μm)/ L(μm) | OTA Gm2 | W(μm)/ L(μm) | OTA Gm3 | W(μm)/ L(μm) | OTA Gm4 | W(μm)/ L(μm) | OTA Gm5 | W(μm)/ L(μm) |

|---|---|---|---|---|---|---|---|---|---|

| Mn1-Mn4, Mn7 | 2/0.6 | Mn1-Mn4 | 0.9/14 | Mn1-Mn4 | 0.9/14 | Mn1-Mn4 | 0.6/50 | Mn1- | 0.6/50 |

| Mn5, Mn6 | 8/0.6 | Mn5, Mn6 | 1/14 | Mn5, Mn6 | 1/14 | Mn7 | 0.6/50 | Mn7 | 1.2/10 |

| Mp2, Mp3, Mp6, Mp7 | 1/0.6 | Mn7 | 1.5/14 | Mn7 | 15/14 | Mn5, Mn6 | 0.6/40 | Mn5, Mn6 | 0.6/40 |

| Mp1, Mp4, Mp5, Mp8 | 20/0.6 | Mp1-Mp8 | 1/0.9 | Mp1-Mp8 | 1/0.9 | Mp2, Mp3, Mp6, Mp7 | 1/10 | Mp2, Mp3, Mp6, Mp7 | 1/10 |

| Vbias | −1.1 V | Vbias | −1.1 V | Vbias | −1.1 V | Mp1, Mp4, Mp5, Mp8 | 1/20 | Mp1, Mp4, Mp5, Mp8 | 1/20 |

| Vbias | −1.1 V | Vbias | −1.1 V |

| OTA-Based Bandpass Filter Design Gm Characteristics | |||||

|---|---|---|---|---|---|

| Gm Process Corners | Monte Carlo | ||||

| Corner | Slow–Slow | Typical–Typical | Fast–Fast | Mean | |

| R simulator | Gm2 | 754 nA/V | 1.2 μA/V | 1.8 μA/V | 1.18 μA/V |

| Gm3 | 3.3 μA/V | 4.8 μA/V | 6.6 μA/V | 4.77 μA/V | |

| C simulator | Gm1 | 294.7 μA/V | 523 μA/V | 875.1 μA/V | 524.85 μA/V |

| Gm2 | 754 nA/V | 1.2 μA/V | 1.8 μA/V | 1.18 μA/V | |

| Gm3 | 3.3 μA/V | 4.8 μA/V | 6.6 μA/V | 4.77 μA/V | |

| L simulator | Gm2 | 754 nA/V | 1.2 μA/V | 1.8 μA/V | 1.18 μA/V |

| Gm3 | 3.3 μA/V | 4.8 μA/V | 6.6 μA/V | 4.77 μA/V | |

| Leapfrog | Gm2 | 754 nA/V | 1.2 μA/V | 1.8 μA/V | 1.18 μA/V |

| Gm4 | 58.9 nA/V | 93.1 nA/V | 140.7 nA/V | 93.03 nA/V | |

| Gm5 | 236 nA/V | 346 nA/V | 487.5 nA/V | 345.96 nA/V | |

| Power Consumption | Monte Carlo | |||

|---|---|---|---|---|

| TM Corner | WP Corner | WS Corner | Mean | |

| R simulator | 20.1 μW | 32.8 μW | 11.8 μW | 16.3 μW |

| C simulator | 699.1 μW | 1.25 mW | 373.6 μW | 705.6 μW |

| L simulator | 20.1 μW | 32.8 μW | 11.9 μW | 16.5 μW |

| Leapfrog | 12.5 μW | 20.5 μW | 7.3 μW | 9.4 μW |

| Output Noise (rms) | |||

|---|---|---|---|

| TM Corner | WP Corner | WS Corner | |

| R simulator | 70.4 mV | 81.3 mV | 49.9 mV |

| C simulator | 1.45 mV | 1.87 mV | 1.13 mV |

| L simulator | 498.3 μV | 515.4 μV | 476.7 μV |

| Leapfrog | 290 μV | 384 μV | 210 μV |

| Gain | ||||||

|---|---|---|---|---|---|---|

| TM Corner | WP Corner | WS Corner | @THD = −40 dB | @SNR = 0 dB | DR | |

| R simulator | 12 dB | 11.3 dB | 12.8 dB | Vin_peak = 17.2 mV | Vin_peak = 26.6 mV | −3.8 dB |

| C simulator | 12.1 dB | 11.4 dB | 12.8 dB | Vin_peak = 17.5 mV | Vin_peak = 510 μV | 30.7 dB |

| L simulator | 12.1 dB | 11.4 dB | 12.9 dB | Vin_peak = 16.7 mV | Vin_peak = 176.2 μV | 39.5 dB |

| Leapfrog | −5.93 dB | −5.89 dB | −5.96 dB | Vin_peak = 655.3 mV | Vin_peak = 850 μV | 57.7 dB |

| R Simulator | C Simulator | L Simulator | |||||||

|---|---|---|---|---|---|---|---|---|---|

| Process Corner | SS | TT | FF | SS | TT | FF | SS | TT | FF |

| fc(Highpass) | 8.4 Hz | 20.1 Hz | 44.3 Hz | 20.4 Hz | 20.5 Hz | 21.2 Hz | 8.4 Hz | 20.1 Hz | 44.6 Hz |

| fc(Lowpass) | 5.8 kHz | 10.2 kHz | 17.6 kHz | 5.8 kHz | 10.2 kHz | 17.7 kHz | 5.8 kHz | 10.2 kHz | 17.6 kHz |

| Gain | 12 dB | 11.3 dB | 12.8 dB | 12.1 dB | 11.4 dB | 12.8 dB | 12.1 dB | 11.4 dB | 12.9 dB |

| Vbias | −1.12 V | −1.1 V | −1.08 V | −1.12 V | −1.1 V | −1.08 V | −1.12 V | −1.1 V | −1.08 V |

| fc(Highpass) | 14.3 Hz | 20.1 Hz | 27.3 Hz | 24.3 Hz | 20.4 Hz | 17.4 Hz | 14.3 Hz | 20.1 Hz | 27.4 Hz |

| fc(Lowpass) | 8.6 kHz | 10.2 kHz | 12 kHz | 8.6 kHz | 10.2 kHz | 11.9 kHz | 8.6 kHz | 10.2 kHz | 12 kHz |

| Gain | 12.5 dB | 12 dB | 11.6 dB | 12.6 dB | 12.1 dB | 11.7 dB | 12.6 dB | 12.1 dB | 11.7 dB |

| Temperature | −40 °C | 0 °C | 40 °C | −40 °C | 0 °C | 40 °C | −40 °C | 0 °C | 40 °C |

| fc(Highpass) | 12.4 Hz | 17.7 Hz | 20.9 Hz | 48.3 Hz | 26.9 Hz | 18.3 Hz | 12.5 Hz | 17.8 Hz | 21 Hz |

| fc(Lowpass) | 8 kHz | 9.6 kHz | 10.2 kHz | 8 kHz | 9.6 kHz | 10.4 kHz | 8 kHz | 9.6 kHz | 10.4 kHz |

| Gain | 13.5 dB | 12.5 dB | 11.9 dB | 13.5 dB | 12.6 dB | 12.1 dB | 13.6 dB | 12.6 dB | 11.9 dB |

| Leapfrog | |||

|---|---|---|---|

| Process Corner | SS | TT | FF |

| fc(Highpass) | 12.2 Hz | 20.6 Hz | 34 Hz |

| fc(Lowpass) | 7 kHz | 10.3 kHz | 14.6 kHz |

| Gain | −5.93 dB | −5.91 dB | −5.94 dB |

| Vbias | −1.12 V | −1.1 V | −1.08 V |

| fc(Highpass) | 18.3 Hz | 20.6 Hz | 22.8 Hz |

| fc(Lowpass) | 9 kHz | 10.2 kHz | 11.4 kHz |

| Gain | −5.93 dB | −5.93 dB | −5.94 dB |

| Temperature | −40 °C | 0 °C | 40 °C |

| fc(Highpass) | 17.8 Hz | 19.8 Hz | 20.9 Hz |

| fc(Lowpass) | 9.3 kHz | 10 kHz | 10.2 kHz |

| Gain | −5.92 dB | −5.93 dB | −5.94 dB |

| Filter Order | 3rd |

|---|---|

| 20 Hz | |

| 1 kHz | |

| Gain | 12 dB |

| Capacitance Simulator | |

|---|---|

| Parameter | Value |

| Gm1 | 523 μA/V |

| Gm4 | 93.1 nA/V |

| Gm5 | 346 nA/V |

| Gm6 | 46.1 μA/V |

| C1 | 450 fF |

| C2 | 10 pF |

| R | 5 kΩ |

| VDD | 1.8 V |

| VSS | −1.8 V |

| (μm/μm) | (μm/μm) | (μm/μm) | (μm/μm) | ||||

|---|---|---|---|---|---|---|---|

| Mn1, Mn2, Mn3, Mn4, | 2/0.6 | Mn1, Mn2, Mn3, Mn4, | 0.6/50 | Mn1, Mn2, Mn3, Mn4, | 0.6/50 | Mn1, Mn2, Mn3, Mn4, | 1/1 |

| Mn7 | 2/0.6 | Mn7 | 0.6/50 | Mn7 | 1.2/10 | Mn7 | 1/1 |

| Mn5, Mn6 | 8/0.6 | Mn5, Mn6 | 0.6/40 | Mn5, Mn6 | 0.6/40 | Mn5, Mn6 | 2/1 |

| Mp2, Mp3, Mp6, Mp7 | 1/0.6 | Mp2, Mp3, Mp6, Mp7 | 1/10 | Mp2, Mp3, Mp6, Mp7 | 1/10 | Mp2, Mp3, | 6/1 |

| Mp6, Mp7 | 3/1 | ||||||

| Mp1, Mp4, Mp5, Mp8 | 20/0.6 | Mp1, Mp4, Mp5, Mp8 | 1/20 | Mp1, Mp4, Mp5, Mp8 | 1/20 | Mp1, Mp4, | 24/1 |

| Mp5, Mp8 | 12/1 | ||||||

| −1.1 V | −1.1 V | −1.1 V | −1.1 V |

| Gm Process Corners | Monte Carlo | |||

|---|---|---|---|---|

| Corner | Slow–Slow | Typical–Typical | Fast–Fast | Mean |

| Gm1 | 294.7 μA/V | 523 μA/V | 875.1 μA/V | 524.85 μA/V |

| Gm4 | 58.9 nA/V | 93.1 nA/V | 140.7 nA/V | 93.03 nA/V |

| Gm5 | 236 nA/V | 346 nA/V | 487.5 nA/V | 345.96 nA/V |

| Gm6 | 27.5 μA/V | 46.1 μA/V | 73.1 μA/V | 46.07 μA/V |

| Power Consumption | Monte Carlo | ||

|---|---|---|---|

| TM Corner | WP Corner | WS Corner | Mean |

| 280.6 μW | 497.2 μW | 151 μW | 282.7 μW |

| Output Noise (rms) | ||

|---|---|---|

| TM Corner | WP Corner | WS Corner |

| 251.3 μV | 223.5 μV | 268 μV |

| Gain | |||||

|---|---|---|---|---|---|

| TM Corner | WP Corner | WS Corner | THD = −40 dB | SNR = 0 dB | |

| 11.3 dB | 10.7 dB | 11.8 dB | Vin_peak = 23.8 mV | Vinpeak = 97.9 μV | DR = 47.7 dB |

| PVT Analysis | ||||

|---|---|---|---|---|

| Process Variation | ||||

| Process Corner | SS | TT | FF | |

| fc(Highpass) | 19.2 Hz | 20.4 Hz | 22.4 Hz | |

| fc(Lowpass) | 581.2 Hz | 1 kHz | 1.8 kHz | |

| Gain | 11.3 dB | 10.7 dB | 11.8 dB | |

| Voltage Variation | ||||

| Vbias | −1.12 V | −1.1 V | −1.08 V | |

| fc(Highpass) | 23.2 Hz | 20.4 Hz | 18.2 Hz | |

| fc(Lowpass) | 872.4 Hz | 1 kHz | 1.2 kHz | |

| Gain | 11.6 dB | 11.3 dB | 10.9 dB | |

| Temperature Variation | ||||

| Temperature | −40 °C | 0 °C | 27 °C | 40 °C |

| fc(Highpass) | 36.3 Hz | 24.5 Hz | 20.4 Hz | 19.1 Hz |

| fc(Lowpass) | 812.8 Hz | 957.1 Hz | 1.02 kHz | 1.04 kHz |

| Gain | 12.4 dB | 11.7 dB | 11.3 dB | 11.1 dB |

| Component | Value | Unit |

|---|---|---|

| RF | 500 | kΩ |

| Ra1 | 50 | kΩ |

| Ra2 | 1 | MΩ |

| Re1, Re2 | 2.5 | MΩ |

| Rf (external) | 2.5 | MΩ |

| Cf (external) | 10 | nF |

| Parameter | Value | Unit |

|---|---|---|

| Input voltage noise @ 450 Hz | 53.65 | nV/√Hz |

| Input current noise @ 450 Hz | 2.01 | fA/√Hz |

| Power consumption of preamplifier | 404.28 | μW |

| Parameter | Value | Unit |

|---|---|---|

| Power consumption of preamplifier | 404.28 | μW |

| Power consumption of filter | 386.6 | μW |

| Total power consumption | 1.13 | mW |

| Parameter | [4] | [5] | [6] | [26] | Previous Work [11] | This Work |

|---|---|---|---|---|---|---|

| Number of sector-shaped vanes, n | 3 | 2 | 6 | 2 circle-shaped sensing electrodes | 2 | 6 |

| Sensor dimensions | 11.5 cm diameter | 3 cm diameter | N/A | 5 cm diameter of each electrode | 15.2 cm diameter | 15 cm diameter |

| Electric field range | N/A | ±150 V/m | 0–80 kV/m | 1.5 kV/m (high sensitivity channel) 15 kV/m (low sensitivity channel) | ±20 kV/m | ±20 kV/m |

| Sensitivity | N/A | ~1 mV/V/m | 48.75 mV/kV/m | N/A | 45 mV/kV/m | 45.75 mV/kV/m |

| Resolution | 16 bits 2 V/m | 16 bits | N/A | 3 V/m (high sensitivity channel) 30 V/m (low sensitivity channel) | 16 bits 0.6 V/m | 16 bits 0.61 V/m |

| Rotation frequency, f (Hz) | 33.3 | 60 | N/A | N/A | 12.75 | 75 |

| Motor type | Three-phase motor Maxon EC32 | N/A | Brushless DC motor | Step motor | Brushless DC motor | Brushless DC motor |

| Power supply | 8 V motor and motor driver 5 V digital systems and sensors ±5 V analog circuitry | 6 V | >4 V | N/A | 3 V analog front-end supply 5 V motor supply | ±1.8 V analog front-end supply 3–6 V motor supply |

| Power consumption | 4 W | 408 mW (264 mW motor consumption) | N/A | 1.8 W | 180.165 mW | 483 mW (@3 V motor supply) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Agorastou, Z.; Michailidis, A.; Lemonou, A.; Themeli, R.; Noulis, T.; Siskos, S. Integrated Filter Design for Analog Field Mill Sensor Interface. Sensors 2023, 23, 3688. https://doi.org/10.3390/s23073688

Agorastou Z, Michailidis A, Lemonou A, Themeli R, Noulis T, Siskos S. Integrated Filter Design for Analog Field Mill Sensor Interface. Sensors. 2023; 23(7):3688. https://doi.org/10.3390/s23073688

Chicago/Turabian StyleAgorastou, Zoi, Anastasios Michailidis, Aikaterini Lemonou, Rafaela Themeli, Thomas Noulis, and Stylianos Siskos. 2023. "Integrated Filter Design for Analog Field Mill Sensor Interface" Sensors 23, no. 7: 3688. https://doi.org/10.3390/s23073688

APA StyleAgorastou, Z., Michailidis, A., Lemonou, A., Themeli, R., Noulis, T., & Siskos, S. (2023). Integrated Filter Design for Analog Field Mill Sensor Interface. Sensors, 23(7), 3688. https://doi.org/10.3390/s23073688