Automotive 2.1 μm Full-Depth Deep Trench Isolation CMOS Image Sensor with a 120 dB Single-Exposure Dynamic Range †

Abstract

:1. Introduction

2. Pixel Design and Operation

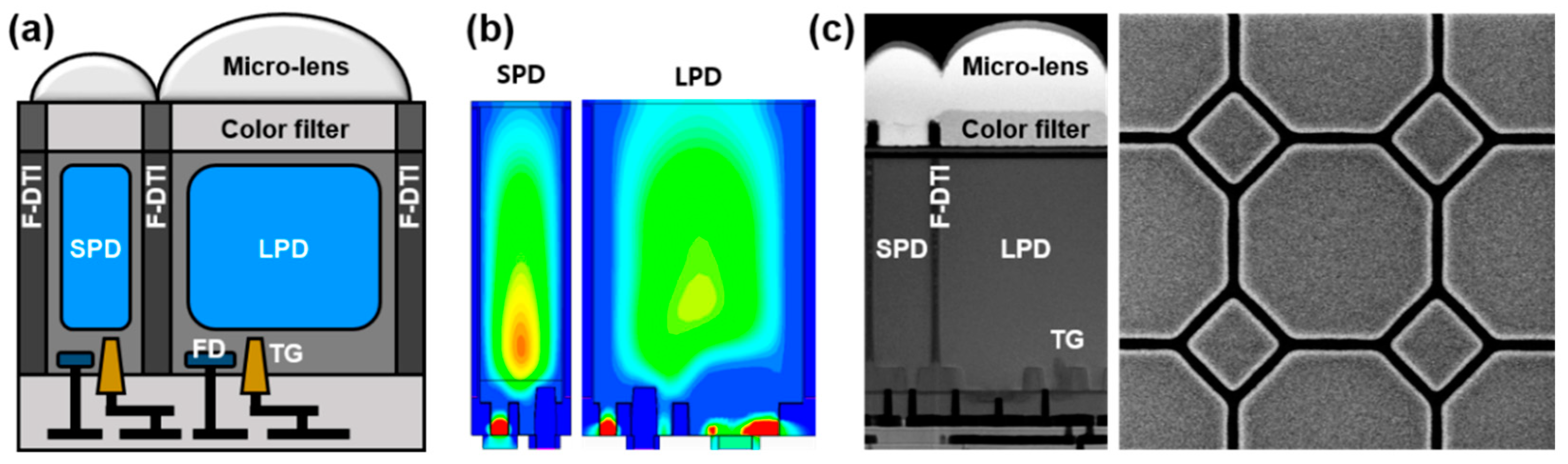

2.1. A 2.1 μm F-DTI Pixel Capped with a Storage Capacitor

2.2. Pixel Circuit and Operation

3. Results and Discussion

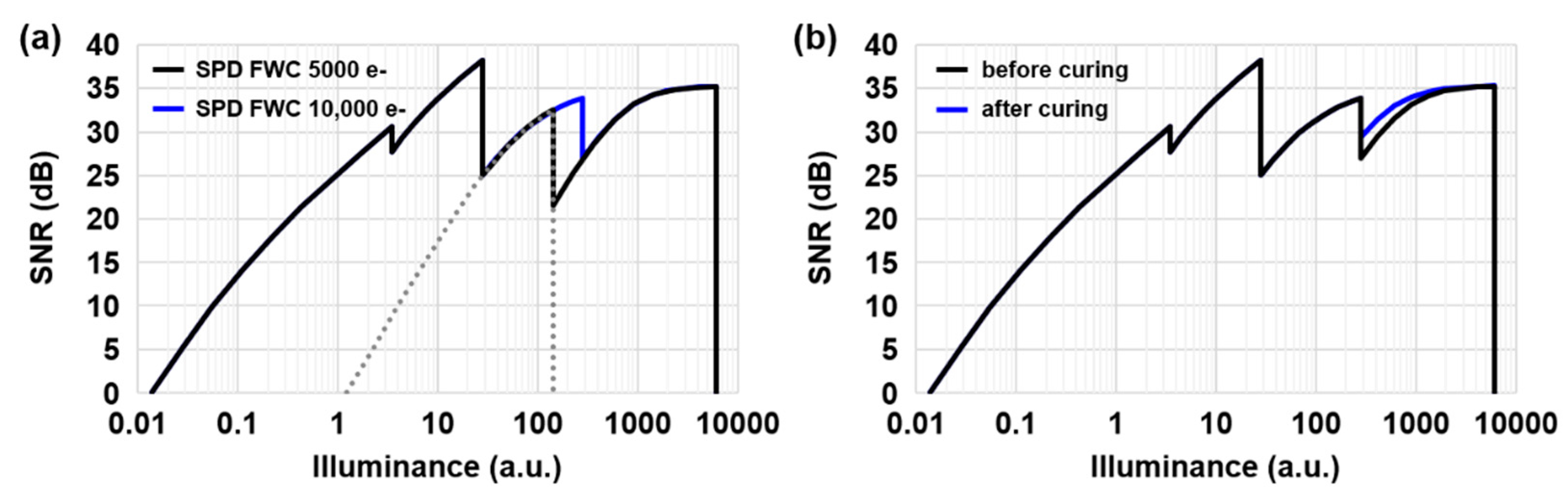

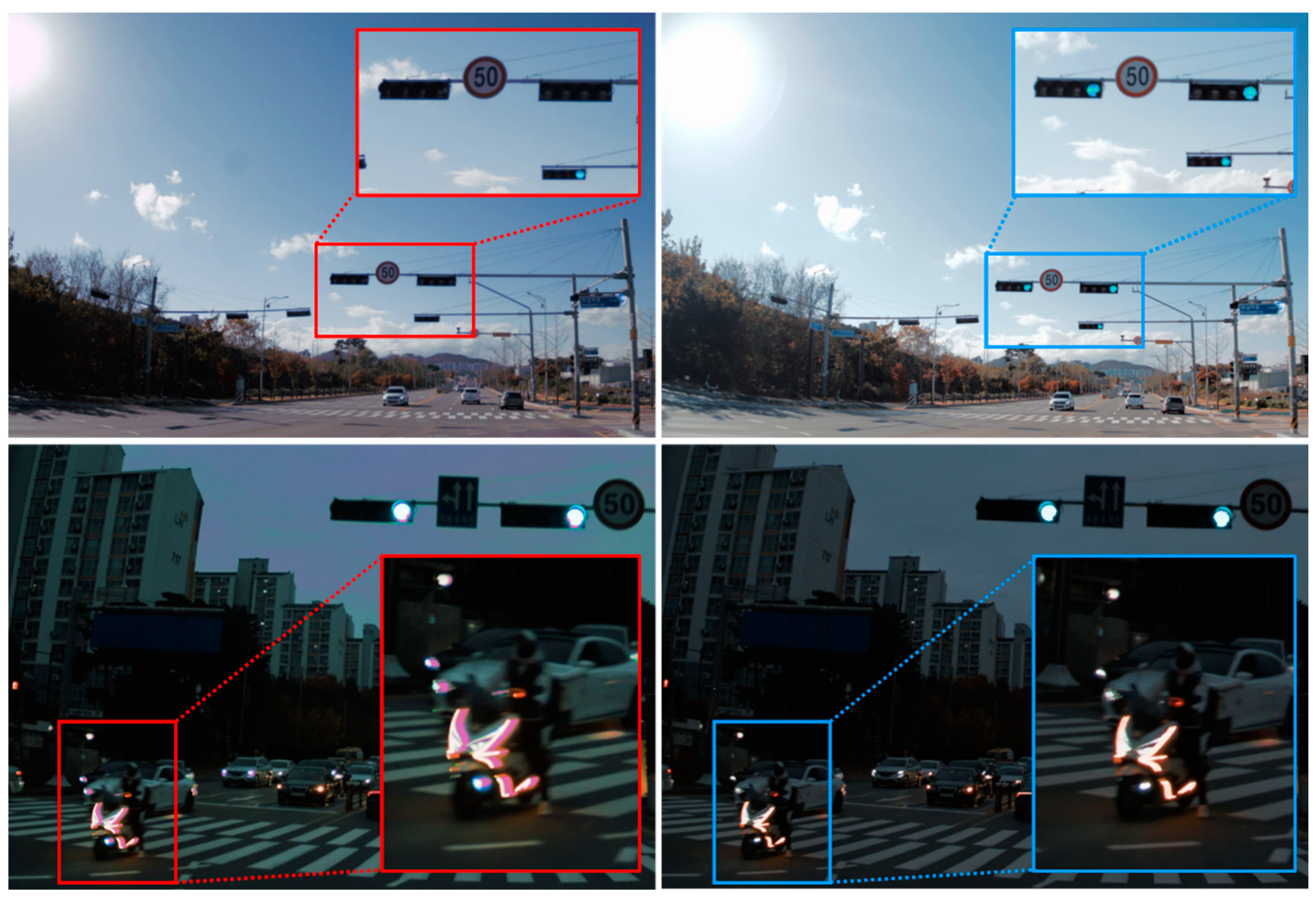

3.1. HDR Characteristics

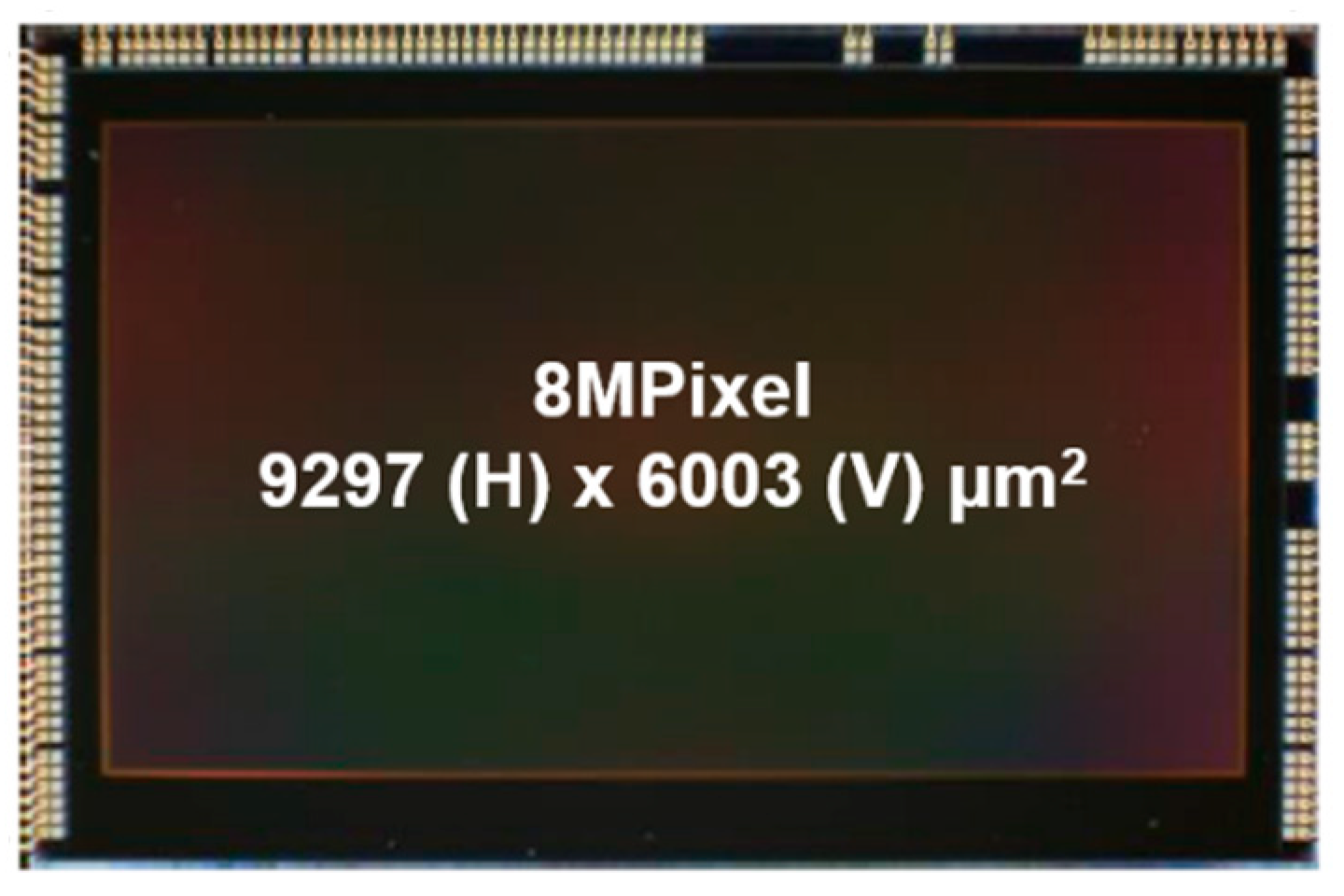

3.2. Sensor Characteristics

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Takayanagi, I.; Kuroda, R. HDR CMOS Image Sensors for Automotive Applications. IEEE Trans. Electron Devices 2022, 69, 2815–2823. [Google Scholar] [CrossRef]

- Solhusvik, J.; Kuang, J.; Lin, Z.; Manabe, S.; Lyu, J.H.; Rhodes, H. A comparison of high dynamic range CIS technologies for automotive applications. Proc. Int. Image Sensor Workshop (IISW) 2013, 421–424. [Google Scholar]

- Sugawa, S.; Akahane, N.; Adachi, S.; Mori, K.; Ishiuchi, T.; Mizobuchi, K. A 100 dB dynamic range CMOS image sensor using a lateral overflow integration capacitor. In Proceedings of the ISSCC. 2005 IEEE International Digest of Technical Papers. Solid-State Circuits Conference, San Francisco, CA, USA, 10 February 2005; Volume 1, pp. 352–603. [Google Scholar]

- Oh, M.; Nicholes, S.; Suryadevara, M.; Lin, L.; Chang, H.C.; Tekleab, D.; Guidash, M.; Amanullah, S.; Velichko, S.; Innocent, M.; et al. 3.0 um Backside Illuminated, Lateral Overflow, High Dynamic Range, LED Flicker Mitigation Image Sensor. Proc. Int. Image Sensor Workshop (IISW) 2019, 262–265. [Google Scholar]

- Innocent, M.; Velichko, S.; Lloyd, D.; Beck, J.; Hernandez, A.; Vanhoff, B.; Silsbv, C.; Oberoi, A.; Singh, G.; Gurindagunta, S.; et al. Automotive 8.3 MP CMOS Image Sensor with 150 dB Dynamic Range and Light Flicker Mitigation. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 30.2.1–30.2.4. [Google Scholar]

- Sakano, Y.; Toyoshima, T.; Nakamura, R.; Asatsuma, T.; Hattori, Y.; Yamanaka, T.; Yoshikawa, R.; Kawazu, N.; Matsuura, T.; Iinuma, T.; et al. A 132 dB Single-Exposure-Dynamic-Range CMOS Image Sensor with High Temperature Tolerance. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 106–108. [Google Scholar]

- Oh, Y.; Lim, J.; Park, S.; Yoo, D.; Lim, M.; Park, J.; Kim, S.; Jung, M.; Kim, S.; Lee, J.; et al. A 140 dB Single-Exposure Dynamic-Range CMOS Image Sensor with In-Pixel DRAM Capacitor. In Proceedings of the 2022 International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2022; pp. 37.7.1–37.7.4. [Google Scholar]

- Ahn, J.; Lee, K.; Kim, Y.; Jeong, H.; Kim, B.; Kim, H.; Park, J.; Jung, T.; Park, W.; Lee, T.; et al. A 1/4-inch 8Mpixel CMOS image sensor with 3D backside-illuminated 1.12μm pixel with front-side deep-trench isolation and vertical transfer gate. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014; pp. 124–125. [Google Scholar]

- Jung, Y.J.; Venezia, V.C.; Lee, S.; Ai, C.Y.; Zhu, Y.; Yeung, K.W.; Park, G.; Choi, W.; Lin, Z.; Yang, W.Z.; et al. A 64M CMOS Image Sensor using 0.7 um pixel with high FWC and switchable conversion gain. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 16.3.1–16.3.4. [Google Scholar]

| Characteristics | Data |

|---|---|

| Process | Pixel 65 nm/Logic 28 nm, stacked BSI |

| Power supply | 2.8 V/1.8 V/1.05 V |

| Si thickness | 3.0 μm |

| Pixel array (H × V) | 3840 × 2160 |

| Max frame rate | 36 fps @ 12 bit |

| FWC (LPD, SPD, in-pixel capacitor) | 10 ke-, 10 ke-, 210 ke- |

| Sensitivity | 32,000 e-/lux.sec (RCCB) |

| Sensitivity ratio | 10 |

| Conversion gain (HCG, LOFIC) | 185 μV/e-, 4.2 μV/e- |

| Read noise (HCG) | 0.83 e- |

| Single-exposure DR @ Tj 85 °C | 120 dB |

| Minimum SNR dip @ Tj 105 °C | 25 dB |

| Color filter array | RCCB (RGGB, RCCG, RYYCy support) |

| HDR Characteristics | This Work | IEDM | IEDM | ISSCC | IISW |

|---|---|---|---|---|---|

| (2.1 μm F-DTI) | 2022 [7] | 2021 [5] | 2020 [6] | 2019 [4] | |

| Pixel pitch | 2.1 μm | 2.1 μm | 2.1 μm | 3.0 μm | 3.0 μm |

| HDR technology | Sub-pixel | Sub-pixel | LOFIC | Sub-pixel | LOFIC |

| LOFIC | LOFIC | LOFIC | |||

| FWC (LPD, LOFIC) | 10 ke- | 10 ke- | 10 ke- | 12.8 ke- | 20 ke- |

| 210 ke- | 1.8 Me- | 600 ke- | 166 ke- | 175 ke- | |

| Single-exposure DR | 120 dB | 140 dB | 110 dB | 121 dB | 96 dB |

| (based on total noises) | 85 °C | 85 °C | 80 °C | 85 °C | 85 °C |

| Minimum SNR dip | 25 dB | 23 dB | 25 dB | 25 dB | 25 dB |

| 105 °C | 105 °C | 125 °C | 100 °C | 100 °C |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yoo, D.; Jang, Y.; Kim, Y.; Shin, J.; Lee, K.; Park, S.-Y.; Shin, S.; Lee, H.; Kim, S.; Park, J.; et al. Automotive 2.1 μm Full-Depth Deep Trench Isolation CMOS Image Sensor with a 120 dB Single-Exposure Dynamic Range. Sensors 2023, 23, 9150. https://doi.org/10.3390/s23229150

Yoo D, Jang Y, Kim Y, Shin J, Lee K, Park S-Y, Shin S, Lee H, Kim S, Park J, et al. Automotive 2.1 μm Full-Depth Deep Trench Isolation CMOS Image Sensor with a 120 dB Single-Exposure Dynamic Range. Sensors. 2023; 23(22):9150. https://doi.org/10.3390/s23229150

Chicago/Turabian StyleYoo, Dongsuk, Youngtae Jang, Youngchan Kim, Jihun Shin, Kangsun Lee, Seok-Yong Park, Seungho Shin, Hongsuk Lee, Seojoo Kim, Joongseok Park, and et al. 2023. "Automotive 2.1 μm Full-Depth Deep Trench Isolation CMOS Image Sensor with a 120 dB Single-Exposure Dynamic Range" Sensors 23, no. 22: 9150. https://doi.org/10.3390/s23229150

APA StyleYoo, D., Jang, Y., Kim, Y., Shin, J., Lee, K., Park, S.-Y., Shin, S., Lee, H., Kim, S., Park, J., Park, C., Lim, M., Bae, H., Park, S., Jung, M., Kim, S., Choi, S., Kim, S., Heo, J., ... Ahn, J. (2023). Automotive 2.1 μm Full-Depth Deep Trench Isolation CMOS Image Sensor with a 120 dB Single-Exposure Dynamic Range. Sensors, 23(22), 9150. https://doi.org/10.3390/s23229150