Design and Characterization of 5 μm Pitch InGaAs Photodiodes Using In Situ Doping and Shallow Mesa Architecture for SWIR Sensing †

Abstract

:1. Introduction

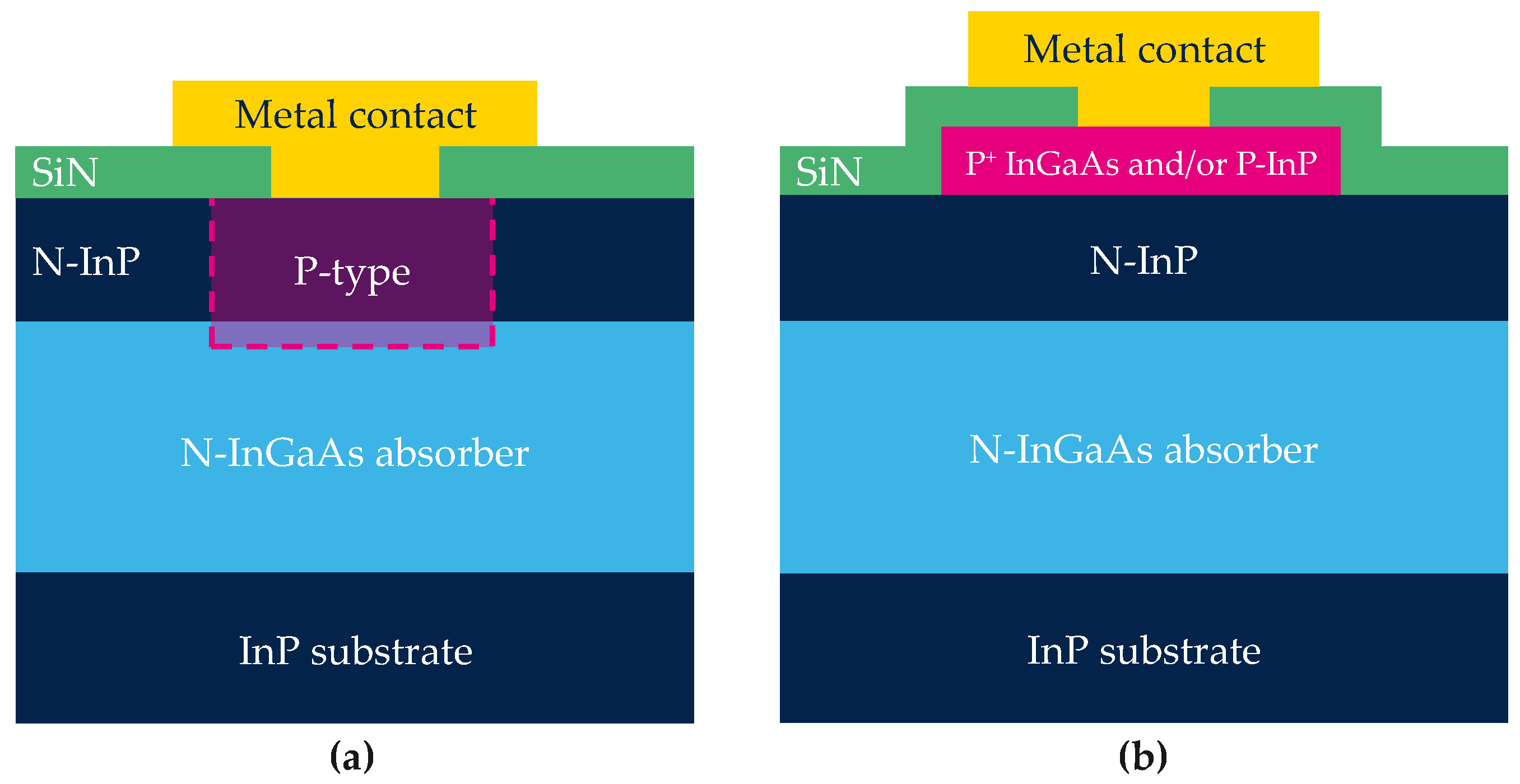

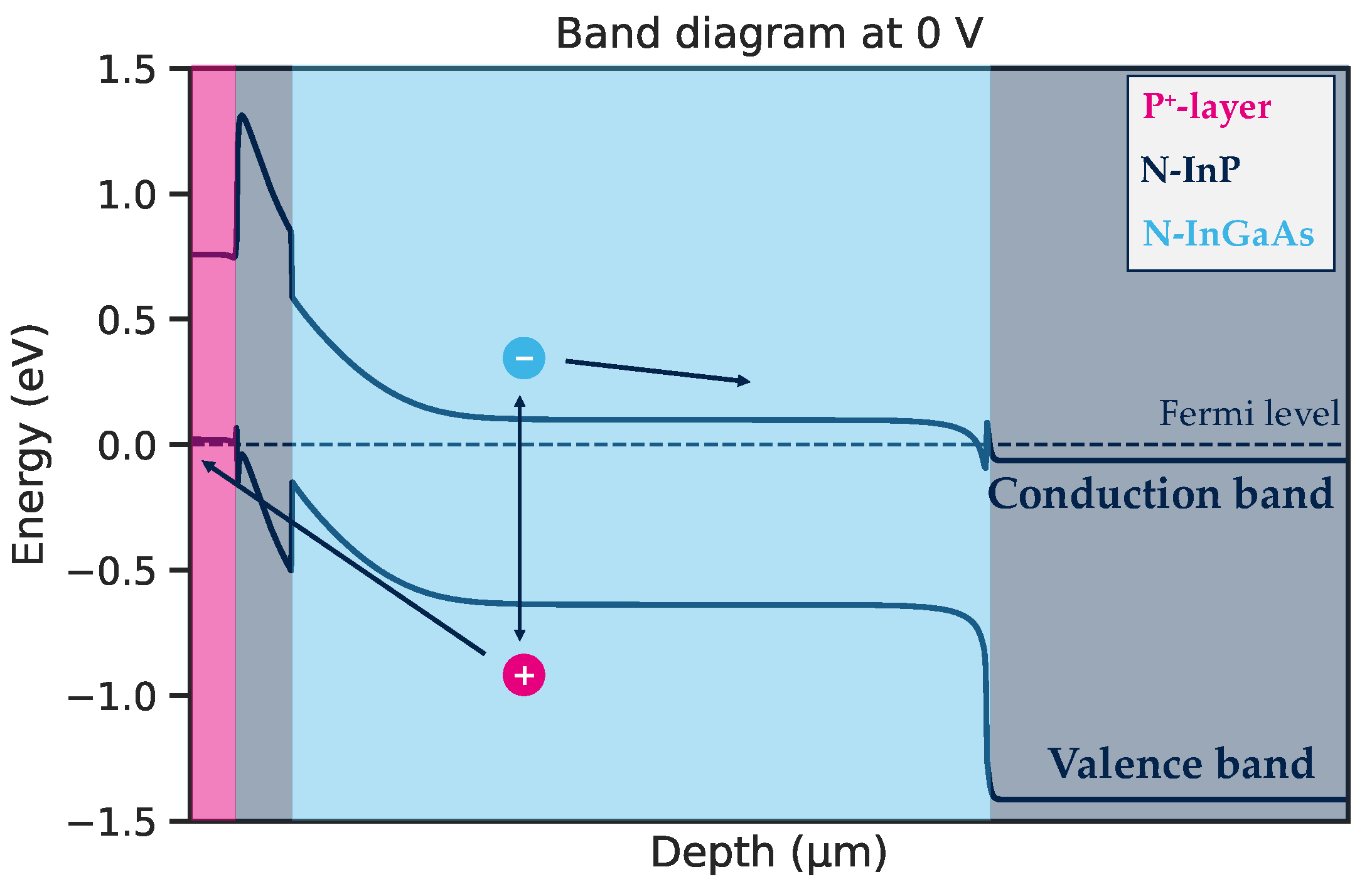

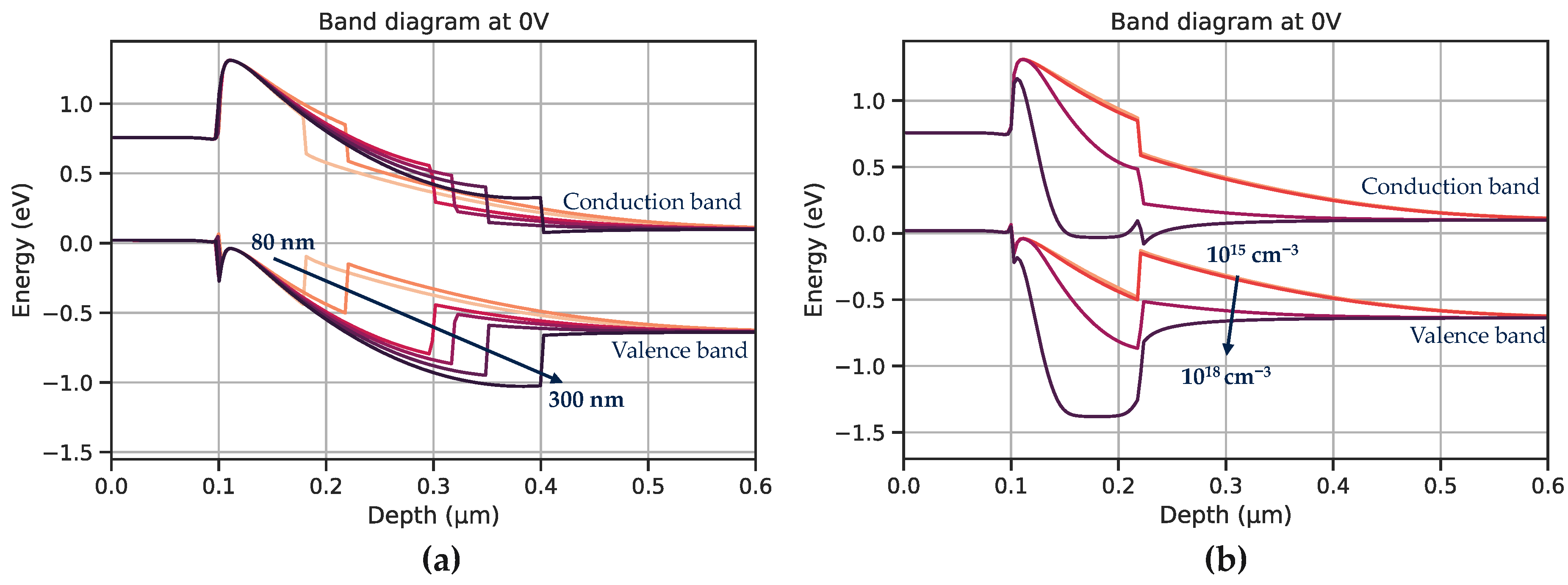

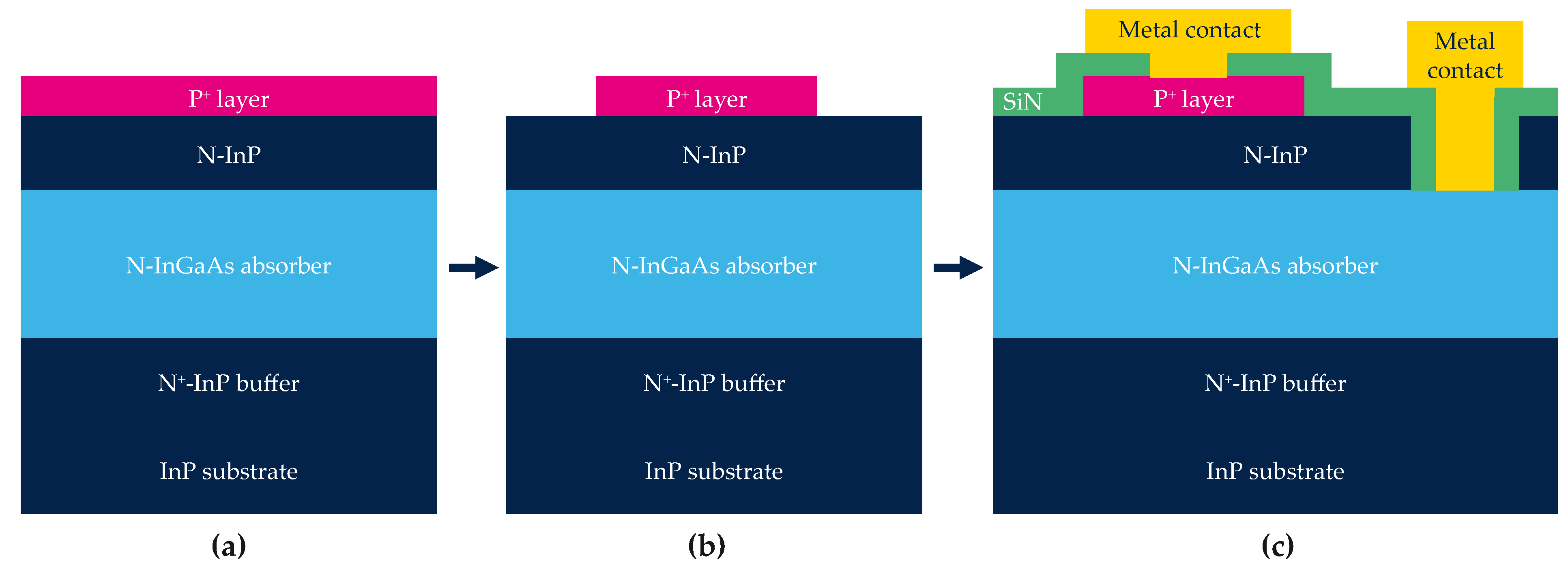

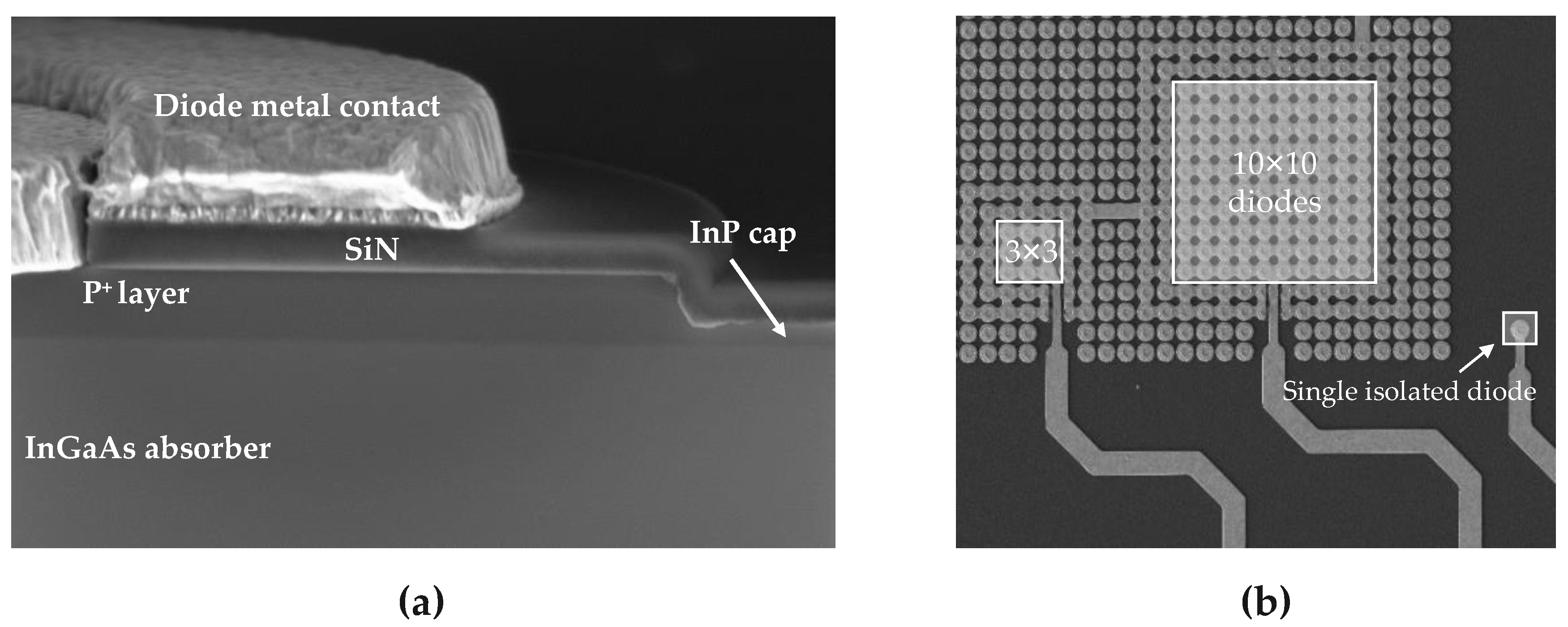

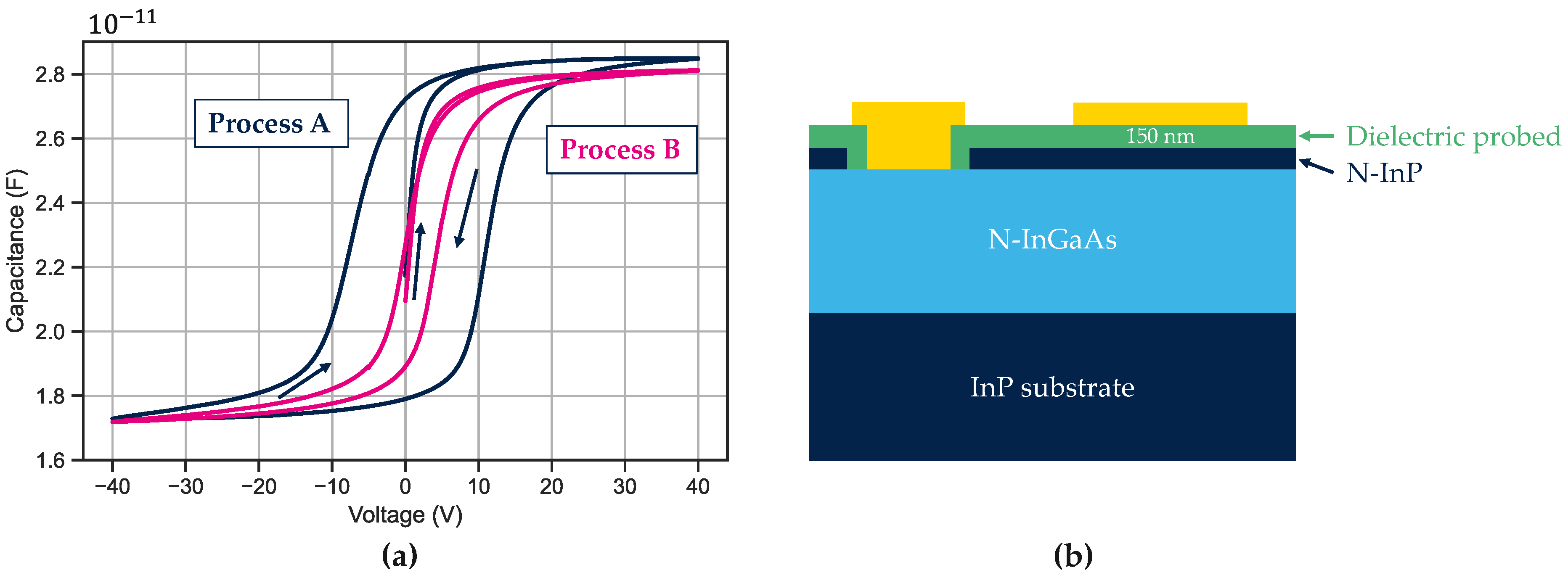

2. Design of the Shallow-Mesa Architecture

3. Fabrication

4. Results

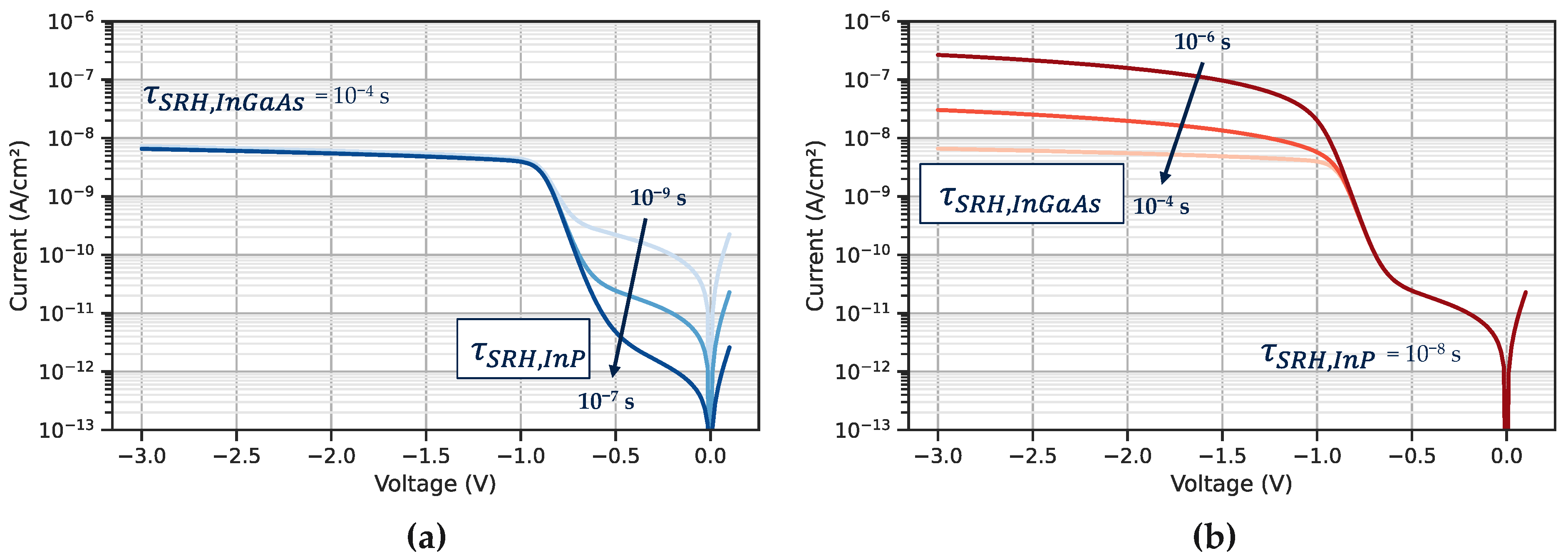

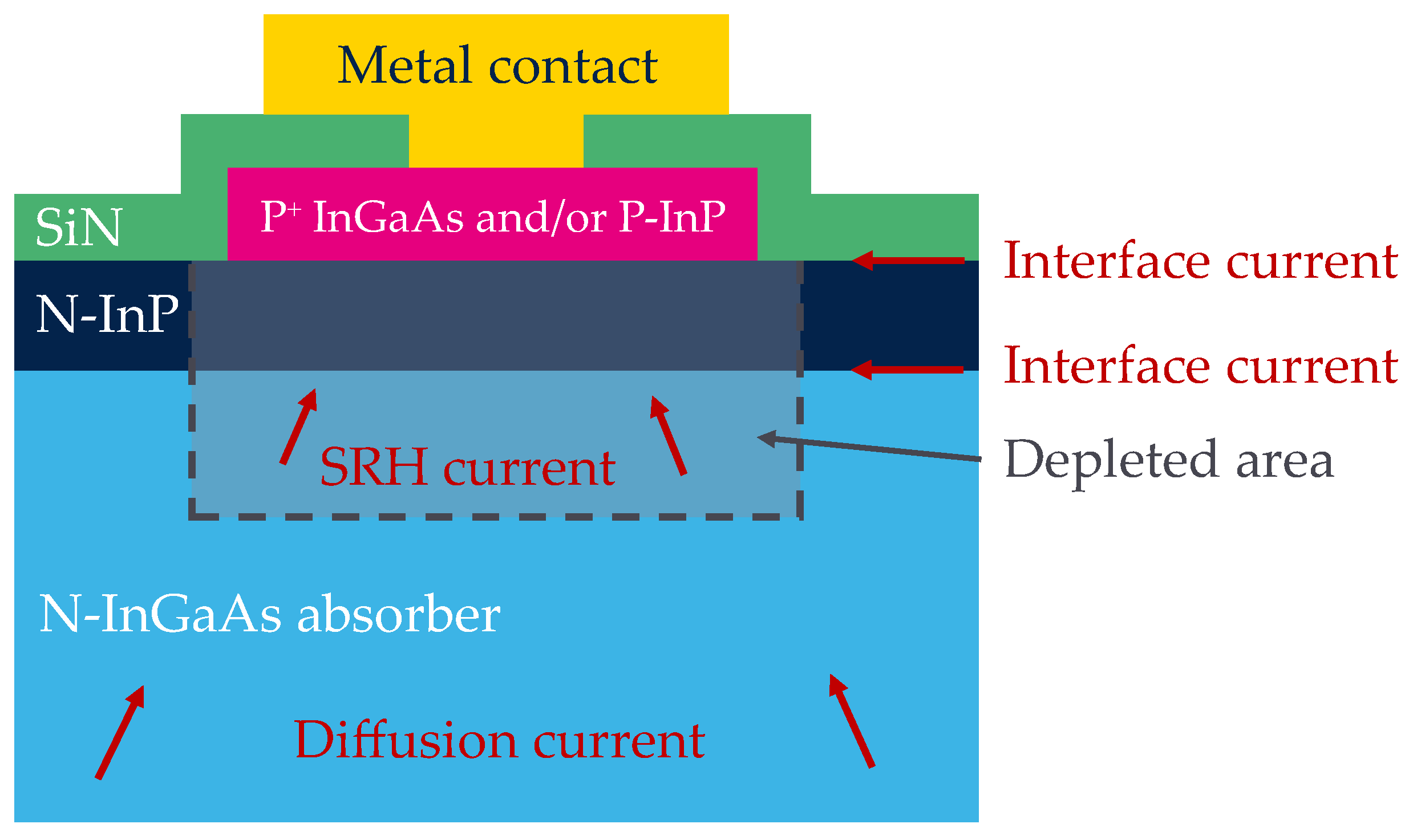

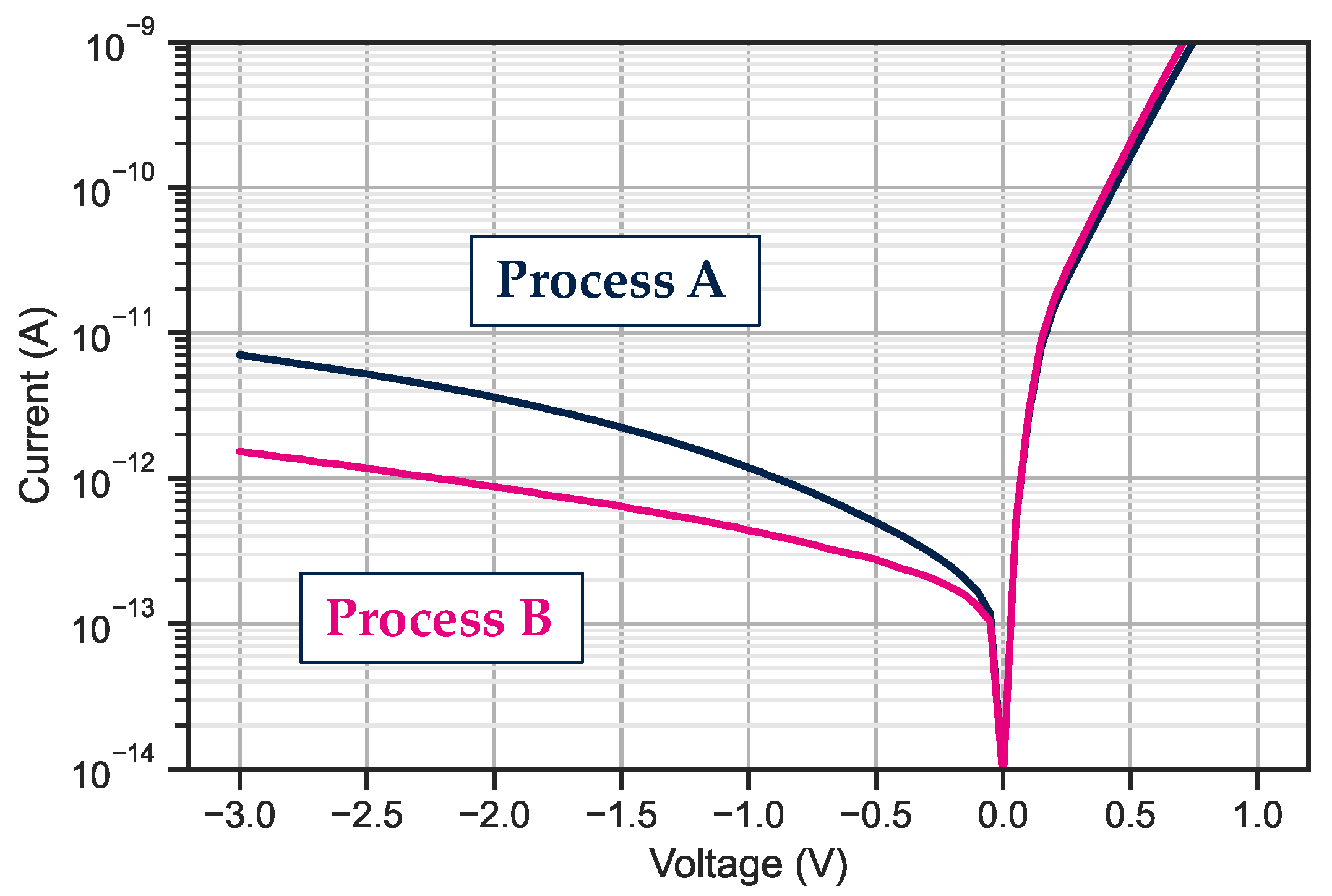

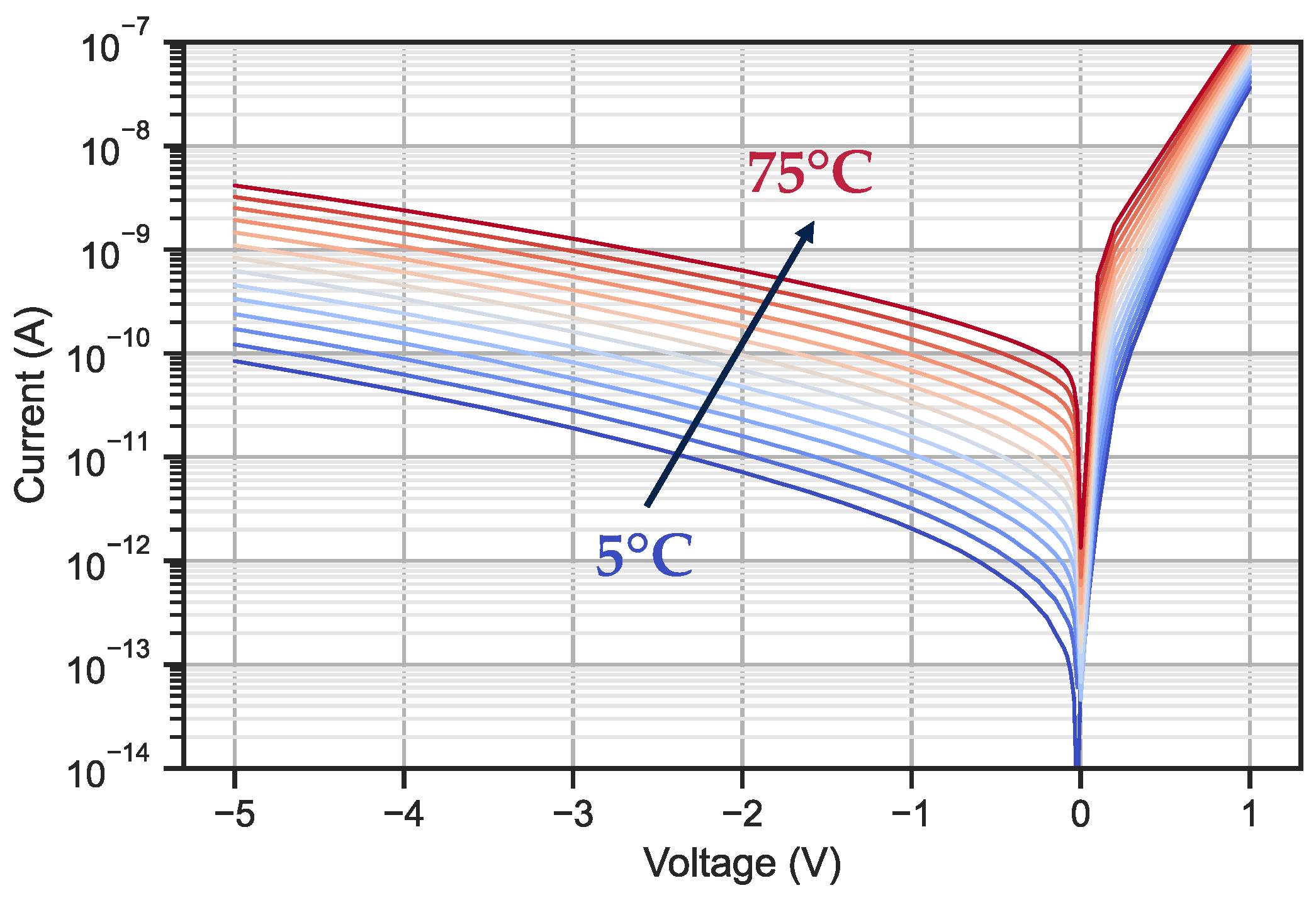

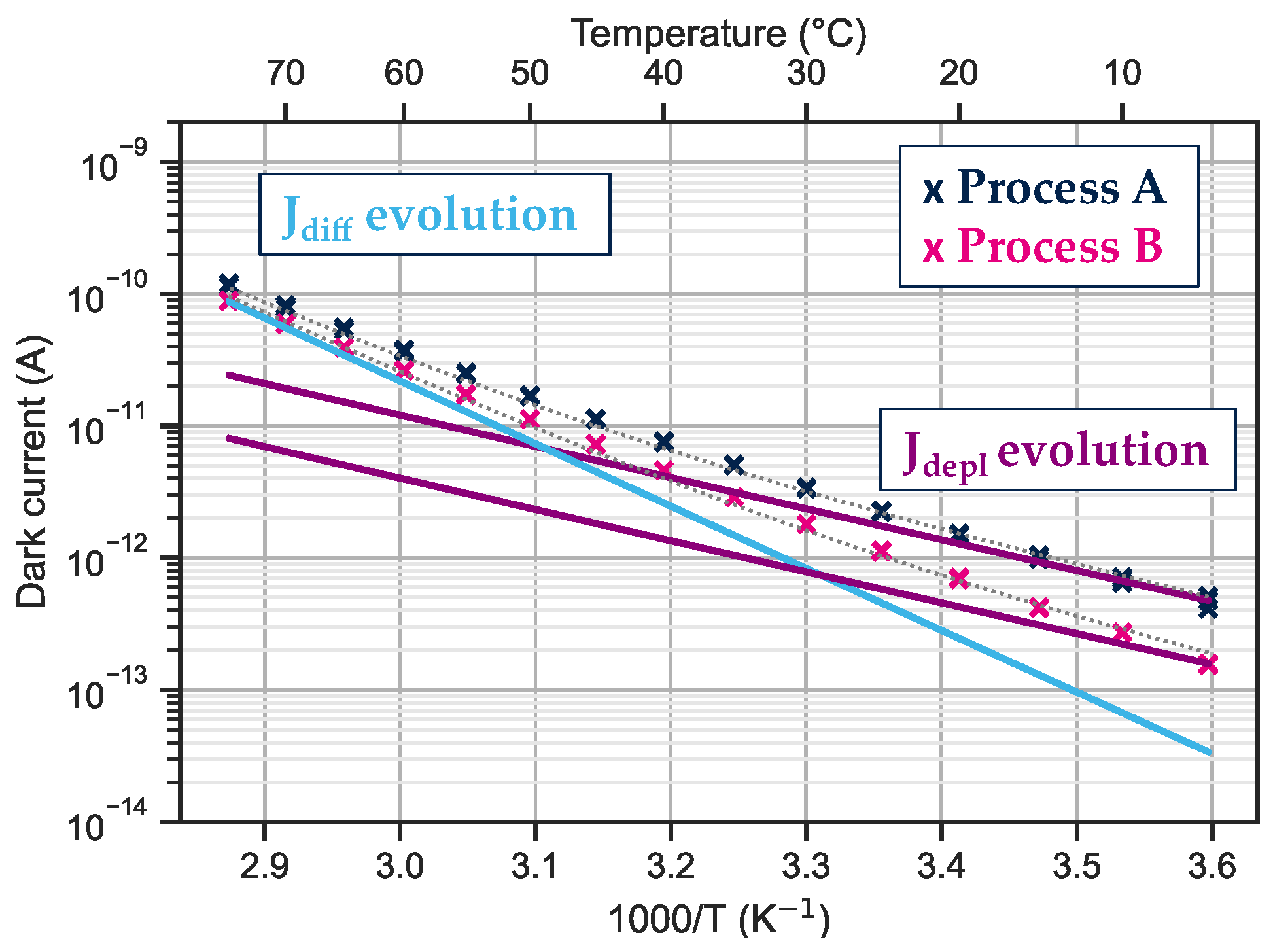

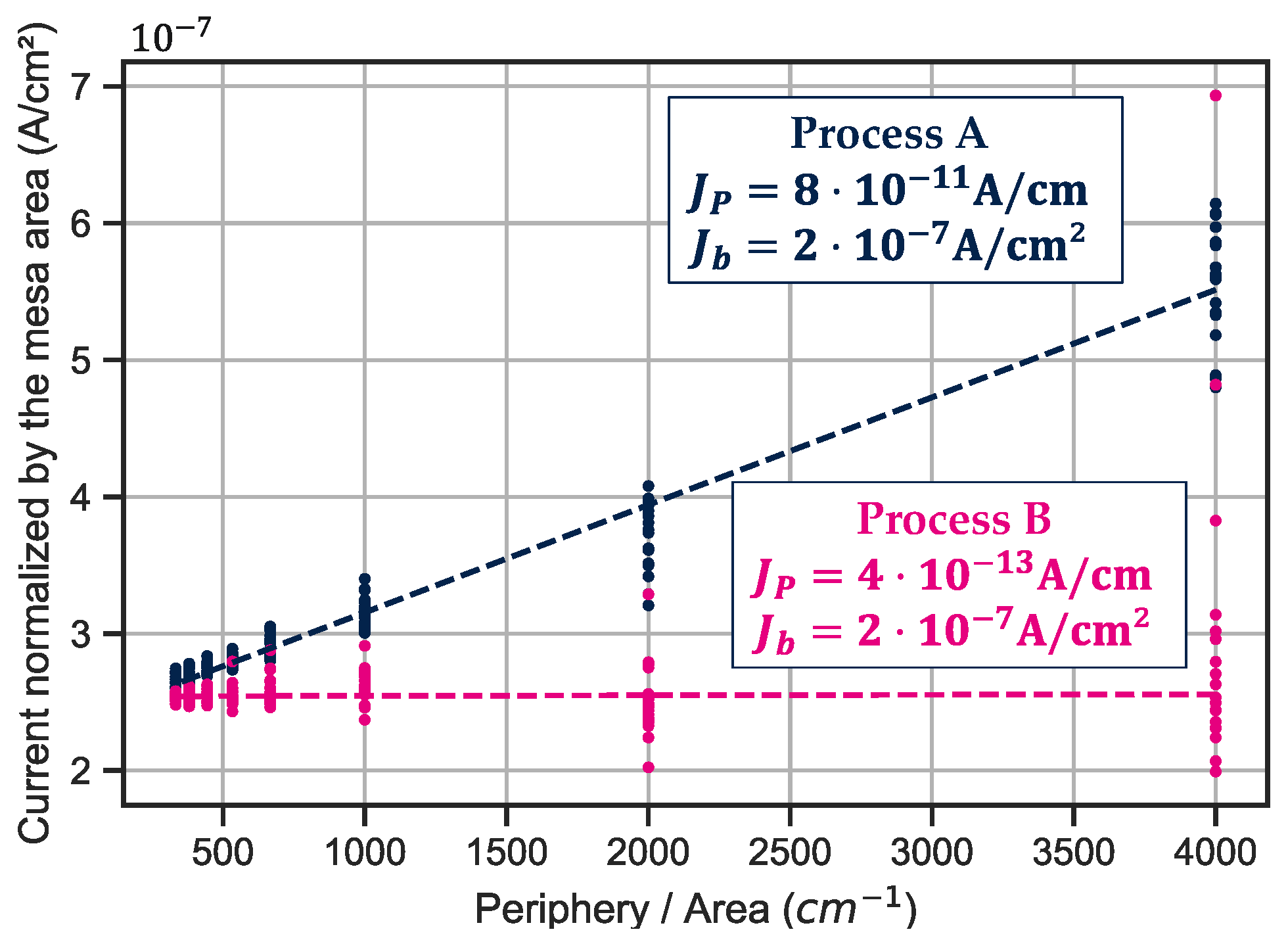

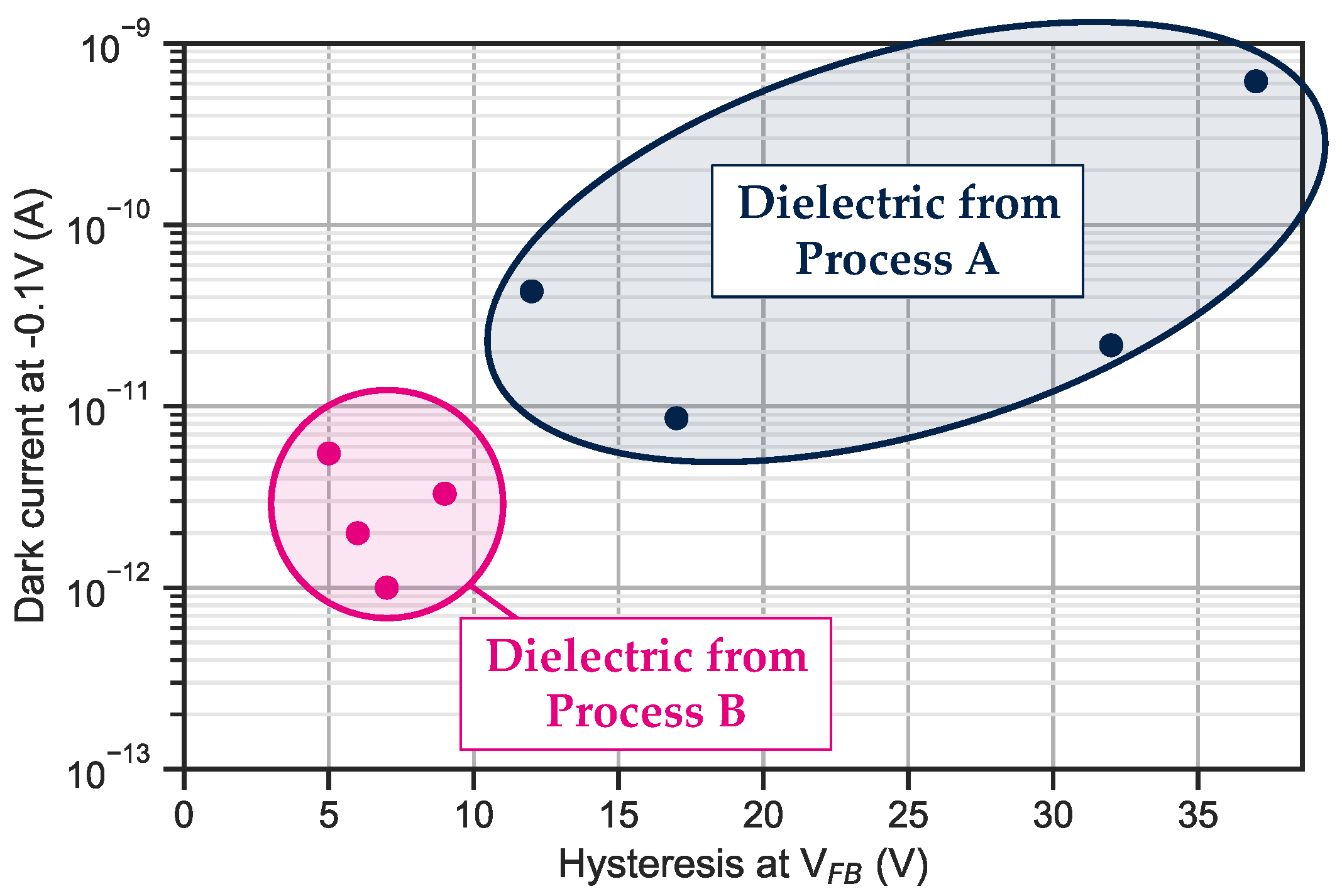

4.1. Dark Current Contributor Investigation

4.2. Photodiode Performances for 5 μm Pixel Pitch

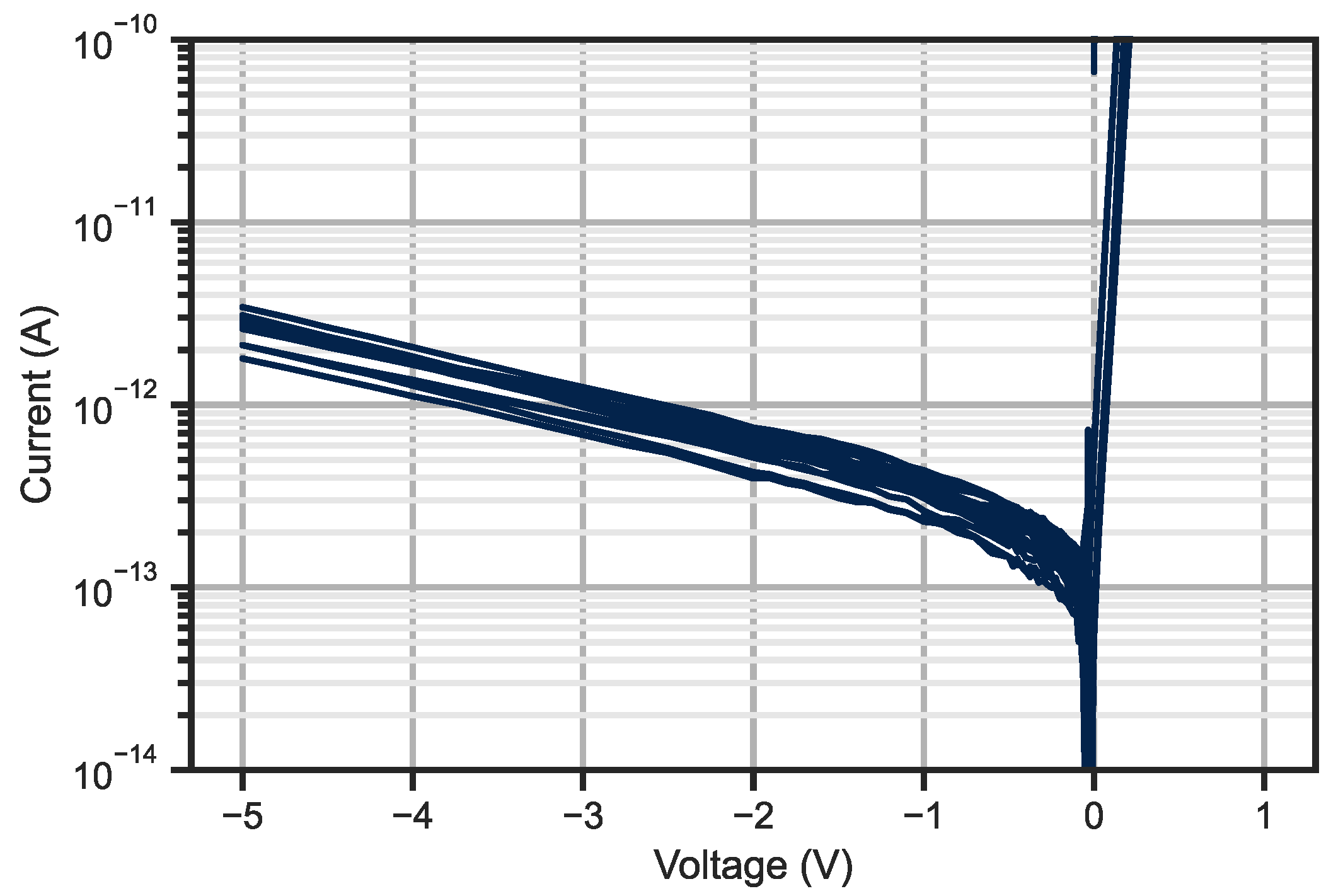

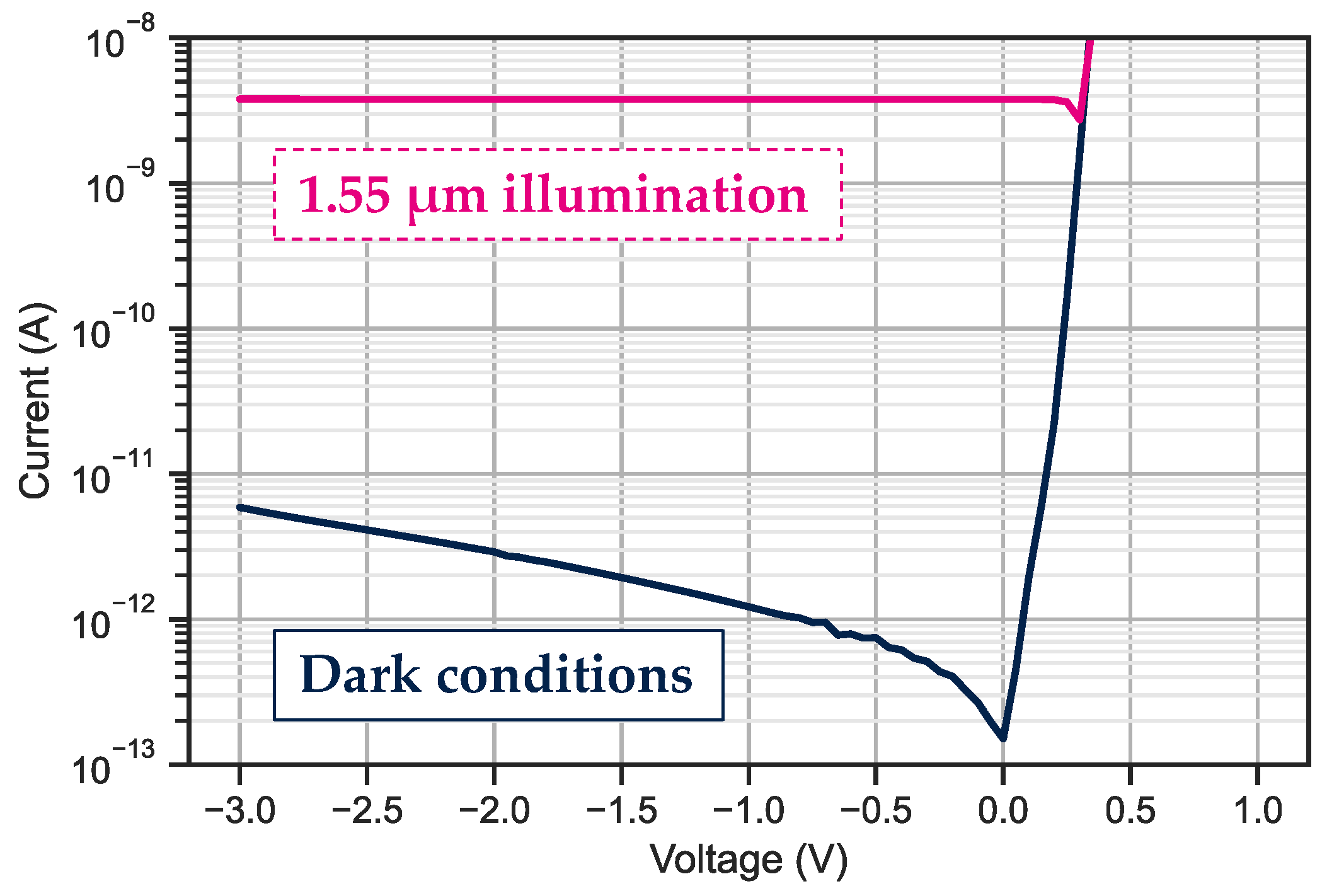

4.2.1. Dark Current

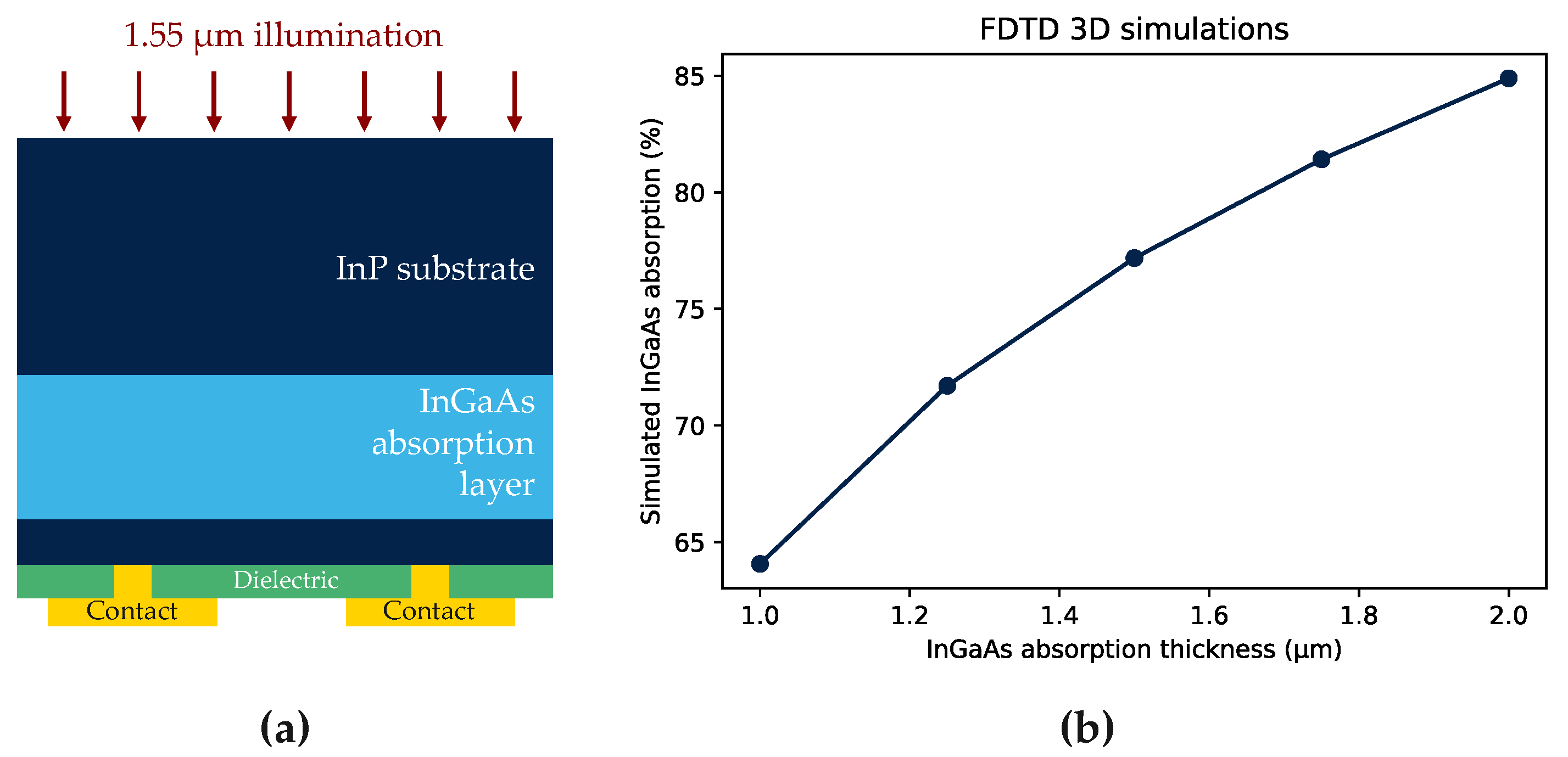

4.2.2. Quantum Efficiency

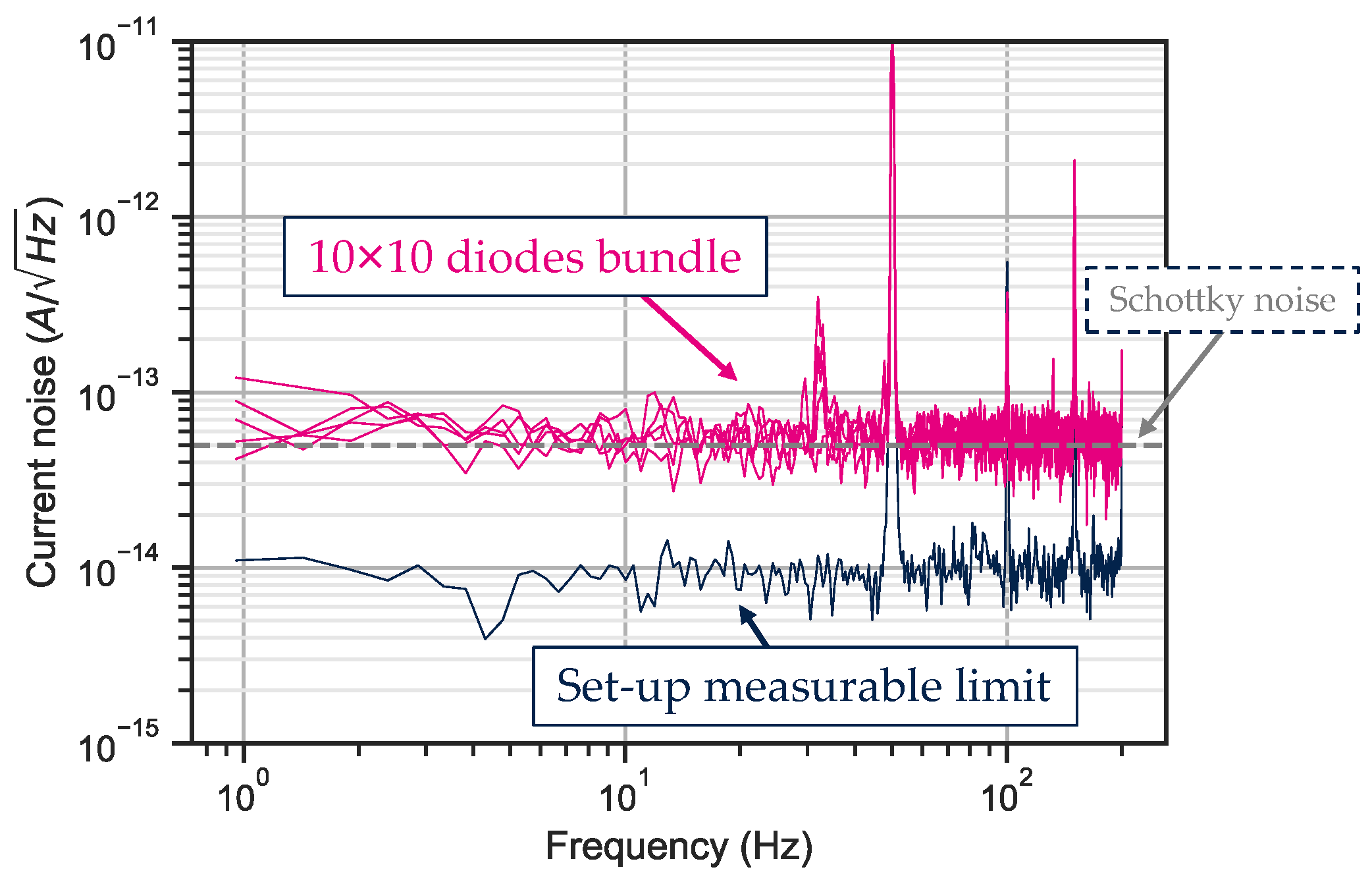

4.2.3. Sensor Spectral Noise under Illumination

4.3. Towards Smaller Pixel Pitch: 3 μm Pixel Pitch Shallow-Mesa Photodiodes

5. Discussion

6. Conclusions

Author Contributions

Funding

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Clouet, A.; Chalak, A.; Domengie, F.; Bouhamri, Z. SWIR Imaging 2023; Yole: Lyon, France, 2023; pp. 27–28. [Google Scholar]

- Steckel, J.S.; Pattantyus-Abraham, A.G.; Josse, E.; Mazaleyrat, E.; Rochereau, K. High resolution quantum dot global shutter imagers. Dig. Tech. Pap. SID Int. Symp. 2021, 52, 975–977. [Google Scholar] [CrossRef]

- Manda, S.; Zaizen, Y.; Hirano, T.; Iwamoto, H.; Matsumoto, R.; Saito, S.; Maruyama, S.; Minari, H.; Hirano, T.; Takachi, T.; et al. High-definition Visible-SWIR InGaAs Image Sensor using Cu-Cu Bonding of III-V to Silicon Wafer. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 390–393. [Google Scholar] [CrossRef]

- Rouvié, A.; Coussement, J.; Huet, O.; Truffer, J.P.; Pozzi, M.; Oubensaid, E.H.; Hamard, S.; Chaffraix, V.; Costard, E. InGaAs focal plane array developments and perspectives. In Proceedings of the Infrared Technology and Applications XLI, Baltimore, MD, USA, 20–24 April 2015; Volume 9451, p. 945105. [Google Scholar] [CrossRef]

- Fraenkel, R.; Berkowicz, E.; Bikov, L.; Elishkov, R.; Giladi, A.; Hirsh, I.; Ilan, E.; Jakobson, C.; Kondrashov, P.; Louzon, E.; et al. Development of low-SWaP and low-noise InGaAs detectors. In Proceedings of the Infrared Technology and Applications XLIII, Anaheim, CA, USA, 9–13 April 2017; Volume 10177, p. 1017703. [Google Scholar] [CrossRef]

- Yuan, H.; Meixell, M.; Zhang, J.; Bey, P.; Kimchi, J.; Kilmer, L.C. Low dark current small pixel large format InGaAs 2D photodetector array development at Teledyne Judson Technologies. In Proceedings of the Infrared Technology and Applications XXXVIII, Baltimore, MD, USA, 23–27 April 2012; Volume 8353, pp. 105–108. [Google Scholar] [CrossRef]

- Rouse, C.; Zeller, J.W.; Efstathiadis, H.; Haldar, P.; Lewis, J.S.; Dhar, N.K.; Wijewarnasuriya, P.; Puri, Y.R.; Sood, A.K. Development of Low Dark Current SiGe Near-Infrared PIN Photodetectors on 300 mm Silicon Wafers. Opt. Photonics J. 2016, 6, 61–68. [Google Scholar] [CrossRef]

- Durlin, Q.; Aliane, A.; André, L.; Kaya, H.; Le Cocq, M.; Goudon, V.; Vialle, C.; Veillerot, M.; Hartmann, J.M. Fabrication and characterisation of the PiN Ge photodiode with poly-crystalline Si:P as n-type region. Aula Abierta 2023, 31, e144550. [Google Scholar] [CrossRef]

- Farooq, U.; Min-Dianey, K.A.A.; Rajagopalan, P.; Malik, M.; Kongnine, D.M.; Choi, J.R.; Pham, P.V. Photodetection Tuning with High Absorptivity Using Stacked 2D Heterostructure Films. Nanomaterials 2022, 12, 712. [Google Scholar] [CrossRef]

- Koppens, F.H.L.; Mueller, T.; Avouris, P.; Ferrari, A.C.; Vitiello, M.S.; Polini, M. Photodetectors based on graphene, other two-dimensional materials and hybrid systems. Nat. Nanotechnol. 2014, 9, 780–793. [Google Scholar] [CrossRef]

- Paul, S.; Roy, J.B.; Basu, P.K. Empirical expressions for the alloy composition and temperature dependence of the band gap and intrinsic carrier density in GaxIn 1-xAs. J. Appl. Phys. 1991, 69, 827–829. [Google Scholar] [CrossRef]

- Laukkanen, P.; Punkkinen, M.P.J.; Kuzmin, M.; Kokko, K.; Lång, J.; Wallace, R.M. Passivation of III-V surfaces with crystalline oxidation. Appl. Phys. Rev. 2021, 8, 23. [Google Scholar] [CrossRef]

- Zhou, L.; Bo, B.; Yan, X.; Wang, C.; Chi, Y.; Yang, X. Brief review of surface passivation on III-V semiconductor. Crystals 2018, 8, 226. [Google Scholar] [CrossRef]

- Hang, Z.; Shen, H.; Pollak, F. Temperature dependance of the E0 and E0 + △0 gaps of InP up to 600 °C. Solid State Commun. 1990, 73, 15–18. [Google Scholar] [CrossRef]

- Dolas, M.H.; Atesal, O.; Caliskan, M.D.; Bek, A.; Ozbay, E. Low dark current diffusion limited planar type InGaAs photodetectors. In Proceedings of the Infrared Sensors, Devices, and Applications IX, San Diego, CA, USA, 11–15 August 2019; p. 10. [Google Scholar] [CrossRef]

- Chen, C.L.; Yost, D.R.; Knecht, J.M.; Chapman, D.C.; Oakley, D.C.; Mahoney, L.J.; Donnelly, J.P.; Soares, A.M.; Suntharalingam, V.; Berger, R.; et al. Wafer-scale 3D integration of InGaAs image sensors with Si readout circuits. In Proceedings of the 2009 IEEE International Conference on 3D System Integration, San Francisco, CA, USA, 28–30 September 2009; pp. 1–4. [Google Scholar] [CrossRef]

- Tillement, J.; Cervera, C.; Baylet, J.; Gravrand, O.; Lalauze, Q.; Jany, C.; Di Rito, T.; Saxod, O.; Moussy, N.; Baron, T.; et al. Fabrication of 3 μm Pixel Pitch InGaAs Photodiodes Using Be Implantation Doping for SWIR Sensing. Solid State Devices Materials. 2022. Available online: https://confit.atlas.jp/guide/organizer/ssdm/events?lang=en (accessed on 10 November 2023).

- Chen, C.L.; Yost, D.R.; Knecht, J.M.; Wey, J.; Chapman, D.C.; Oakley, D.C.; Soares, A.M.; Mahoney, L.J.; Donnelly, J.P.; Chen, C.K.; et al. Wafer-scale 3D integration of InGaAs photodiode arrays with Si readout circuits by oxide bonding and through-oxide vias. Microelectron. Eng. 2011, 88, 131–134. [Google Scholar] [CrossRef]

- Dolas, M.H.; Circir, K.; Kocaman, S. Optimization of mesa structured InGaAs based photodiode arrays. In Proceedings of the Image Sensing Technologies: Materials, Devices, Systems, and Applications IV, Anaheim, CA, USA, 9–13 April 2017; Volume 10209, p. 102090K. [Google Scholar] [CrossRef]

- Djedidi, A.; Rouvie, A.; Reverchon, J.; Pires, M.; Chevalier, N.; Mariolle, D. Investigation of the Influence of Zn-diffusion profile on the electrical properties of InGaAs/InP photodiodes. In Proceedings of the 2012 International Conference on Indium Phosphide and Related Materials, Santa Barbara, CA, USA, 27–30 August 2012; pp. 110–112. [Google Scholar] [CrossRef]

- Akano, U.G.; Mitchell, I.V.; Shepherd, F.R.; Miner, C.J. Ion implantation damage of InP and InGaAs. Nucl. Inst. Methods Phys. Res. B 1995, 106, 308–312. [Google Scholar] [CrossRef]

- Sadana, D.K. Mechanisms of amorphization and recrystallization in ion implanted III-V compound semiconductors. Nucl. Inst. Methods Phys. Res. B 1985, 7–8, 375–386. [Google Scholar] [CrossRef]

- Tandon, J.L.; Madok, J.H.; Leybovich, I.S.; Bai, G.; Nicolet, M.-A. Sequential nature of damage annealing and activation in implanted GaAs. Appl. Phys. Lett. 1989, 54, 448–450. [Google Scholar] [CrossRef]

- Ronning, C.; Dalmer, M.; Uhrmacher, M.; Restle, M.; Vetter, U.; Ziegeler, L.; Hofsäss, H.; Gehrke, T.; Järrendahl, K.; Davis, R.F. Ion implanted dopants in GaN and AIN: Lattice sites, annealing behavior, and defect recovery. J. Appl. Phys. 2000, 87, 2149–2157. [Google Scholar] [CrossRef]

- Pearton, S.J. Ion implantation for isolation of III-V semiconductors. Mater. Sci. Rep. 1990, 4, 313–363. [Google Scholar] [CrossRef]

- Klem, J.F.; Kim, J.K.; Cich, M.J.; Keeler, G.A.; Hawkins, S.D.; Fortune, T.R. Mesa-isolated InGaAs photodetectors with low dark current. Appl. Phys. Lett. 2009, 95, 2–5. [Google Scholar] [CrossRef]

- Lau, J.H. Recent Advances and Trends in Cu-Cu Hybrid Bonding. IEEE Trans. Compon. Packag. Manuf. Technol. 2023, 13, 399–425. [Google Scholar] [CrossRef]

- Synopsys. SentaurusTM Device User Guide; P-2019.03.; Synopsys, Inc.: Mountain View, CA, USA, 2019. [Google Scholar]

- Ahrenkiel, R.K.; Ellingson, R.; Johnston, S.; Wanlass, M. Recombination lifetime of In0.53Ga0.47As as a function of doping density. Appl. Phys. Lett. 1998, 72, 3470–3472. [Google Scholar] [CrossRef]

- Vignaud, D.; Lampin, J.F.; Lefebvre, E.; Zaknoune, M.; Mollot, F. Electron lifetime of heavily Be-doped In0.53Ga0.47As as a function of growth temperature and doping density. Appl. Phys. Lett. 2002, 80, 4151–4153. [Google Scholar] [CrossRef]

- Trezza, J.A.; Masaun, N.; Ettenberg, M. Analytic modeling and explanation of ultra-low noise in dense SWIR detector arrays. In Proceedings of the Infrared Technology and Applications XXXVII, Orlando, FL, USA, 25–29 April 2011; Volume 8012, p. 80121Y. [Google Scholar] [CrossRef]

- Boisvert, J.; Isshiki, T.; Sudharsanan, R.; Yuan, P.; McDonald, P. Performance of very low dark current SWIR PIN arrays. In Proceedings of the Infrared Technology and Applications XXXIV, Orlando, FL, USA, 16–20 March 2008; Volume 6940, p. 69400L. [Google Scholar]

- Yuan, P.; Chang, J.; Boisvert, J.; Karam, N. Low-dark current 1024 × 1280 InGaAs PIN arrays. In Proceedings of the Infrared Technology and Applications XL, Baltimore, MD, USA, 5–9 May 2014; Volume 907007. [Google Scholar] [CrossRef]

- DeWames, R.E.; Schuster, J. Performance and limitations of NIR and extended wavelength eSWIR InP/InGaAs image sensors. In Proceedings of the Quantum Sensing and Nano Electronics and Photonics XVII, San Francisco, CA, USA, 1–6 February 2020; p. 17. [Google Scholar] [CrossRef]

- Sze, S.M.; Kwok, K.N. Physics of Semiconductor Devices; Springer: Berlin/Heidelberg, Germany, 2006; Volume 10, ISBN 978-0-470-06832-8. [Google Scholar]

- Maserjian, J.; Petersson, G.; Svensson, C. Saturation capacitance of thin oxide MOS structures and the effective surface density of states of silicon. Solid-State Electron. 1974, 17, 335–339. [Google Scholar] [CrossRef]

- Schroder, D. Semiconductor Material and Device Characterization; J. Wiley & Sons: Hoboken, NJ, USA, 2006. [Google Scholar]

- Tillement, J.; Cervera, C.; Baylet, J.; Jany, C.; Nardellib, F.; Lalauze, Q.; Di Rito, T.; Paquet, R.; Saxod, O.; Moussy, N.; et al. Fabrication of Small Pitch InGaAs Photodiodes Using In-Situ Doping and Shallow Mesa Architecture for SWIR Sensing. 2023. Available online: https://imagesensors.org/Past%20Workshops/2023%20Workshop/2023%20Papers/R63.pdf (accessed on 10 November 2023).

- Verdun, M. Photodétecteurs InGaAs Nanostructurés pour l’Imagerie Infrarouge; Université Paris Saclay (COmUE): Paris, France, 2016. [Google Scholar]

- Pettit, G.D.; Turner, W.J. Refractive index of InP. J. Appl. Phys. 1965, 36, 2081. [Google Scholar] [CrossRef]

- Fraenkel, R.; Berkowicz, E.; Bykov, L.; Dobromislin, R.; Elishkov, R.; Giladi, A.; Grimberg, I.; Hirsh, I.; Ilan, E.; Jacobson, C.; et al. High definition 10 μm pitch InGaAs detector with asynchronous laser pulse detection mode. In Proceedings of the Infrared Technology and Applications XLII, Baltimore, MD, USA, 17–21 April 2016; Volume 9819, p. 981903. [Google Scholar]

- Steckel, J.S.; Josse, E.; Pattantyus-Abraham, A.G.; Bidaud, M.; Mortini, B.; Bilgen, H.; Arnaud, O.; Allegret-Maret, S.; Saguin, F.; Mazet, L.; et al. 1.62 μm Global Shutter Quantum Dot Image Sensor Optimized for Near and Shortwave Infrared. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 518–521. [Google Scholar]

- Circir, K.; Dolas, M.H.; Kocaman, S. Optimization of in-device depleted passivation layer for InGaAs photodetectors. Infrared Phys. Technol. 2019, 97, 360–364. [Google Scholar] [CrossRef]

- Shkedy, L.; Koifman, A.; Giladi, A.; Tuito, A.; Ilan, E.; Grimberg, I.; Bykov, L.; Elishkov, R.; Fraenkel, R.; Vasserman, S. Multi-function InGaAs Detector for SWIR Imaging. Proc. SPIE 2014, 2930312. [Google Scholar]

- Lalucaa, V.; Calvinhac, L.; Virmontois, C.; Member, S. Dark Current Random Telegraph Signal in visible and SWIR Direct Cu-Cu bonding InGaAs Image Sensor. In Proceedings of the 2021 21th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Vienna, Austria, 13–17 September 2021; pp. 1–4. [Google Scholar] [CrossRef]

- Walker, A.W.; Pitts, O.J.; Storey, C.; Waldron, P.; Flueraru, C. Minority carrier diffusion in InGaAs/InP P–i–N heterojunctions for photodetector arrays. Opt. Quantum Electron. 2020, 52, 96. [Google Scholar] [CrossRef]

- Colin, T.; Aufranc, S.; Fantini, J.; Bonvalot, C.; Grille, R.; Dagher, G.; Renaudat-Saint-Jean, M.; Coussement, J.; Péré-Laperne, N. Small pixel pitch developments in the short wave infrared range at LYNRED. In Proceedings of the Infrared Technology and Applications XLIX, Orlando, FL, USA, 30 April–5 May 2023; Volume 1253403, p. 1. [Google Scholar] [CrossRef]

| Output Power (μW) | Photocurrent at −0.1 V (μA) | Raw QE (%) | QE with Ideal Anti-Reflective Coating (%) |

|---|---|---|---|

| 86 | 55.9 | 53.5 | 75.7 |

| 97 | 61.3 | 53.2 | 75.3 |

| 107 | 69.6 | 55.2 | 78.1 |

| 117 | 78.1 | 54.6 | 77.2 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Tillement, J.; Cervera, C.; Baylet, J.; Jany, C.; Nardelli, F.; Di Rito, T.; Georges, S.; Mugny, G.; Saxod, O.; Gravrand, O.; et al. Design and Characterization of 5 μm Pitch InGaAs Photodiodes Using In Situ Doping and Shallow Mesa Architecture for SWIR Sensing. Sensors 2023, 23, 9219. https://doi.org/10.3390/s23229219

Tillement J, Cervera C, Baylet J, Jany C, Nardelli F, Di Rito T, Georges S, Mugny G, Saxod O, Gravrand O, et al. Design and Characterization of 5 μm Pitch InGaAs Photodiodes Using In Situ Doping and Shallow Mesa Architecture for SWIR Sensing. Sensors. 2023; 23(22):9219. https://doi.org/10.3390/s23229219

Chicago/Turabian StyleTillement, Jules, Cyril Cervera, Jacques Baylet, Christophe Jany, François Nardelli, Thomas Di Rito, Sylvain Georges, Gabriel Mugny, Olivier Saxod, Olivier Gravrand, and et al. 2023. "Design and Characterization of 5 μm Pitch InGaAs Photodiodes Using In Situ Doping and Shallow Mesa Architecture for SWIR Sensing" Sensors 23, no. 22: 9219. https://doi.org/10.3390/s23229219

APA StyleTillement, J., Cervera, C., Baylet, J., Jany, C., Nardelli, F., Di Rito, T., Georges, S., Mugny, G., Saxod, O., Gravrand, O., Baron, T., Roy, F., & Boeuf, F. (2023). Design and Characterization of 5 μm Pitch InGaAs Photodiodes Using In Situ Doping and Shallow Mesa Architecture for SWIR Sensing. Sensors, 23(22), 9219. https://doi.org/10.3390/s23229219