A 12-b Subranging SAR ADC Using Detect-and-Skip Switching and Mismatch Calibration for Biopotential Sensing Applications

Abstract

1. Introduction

2. Design

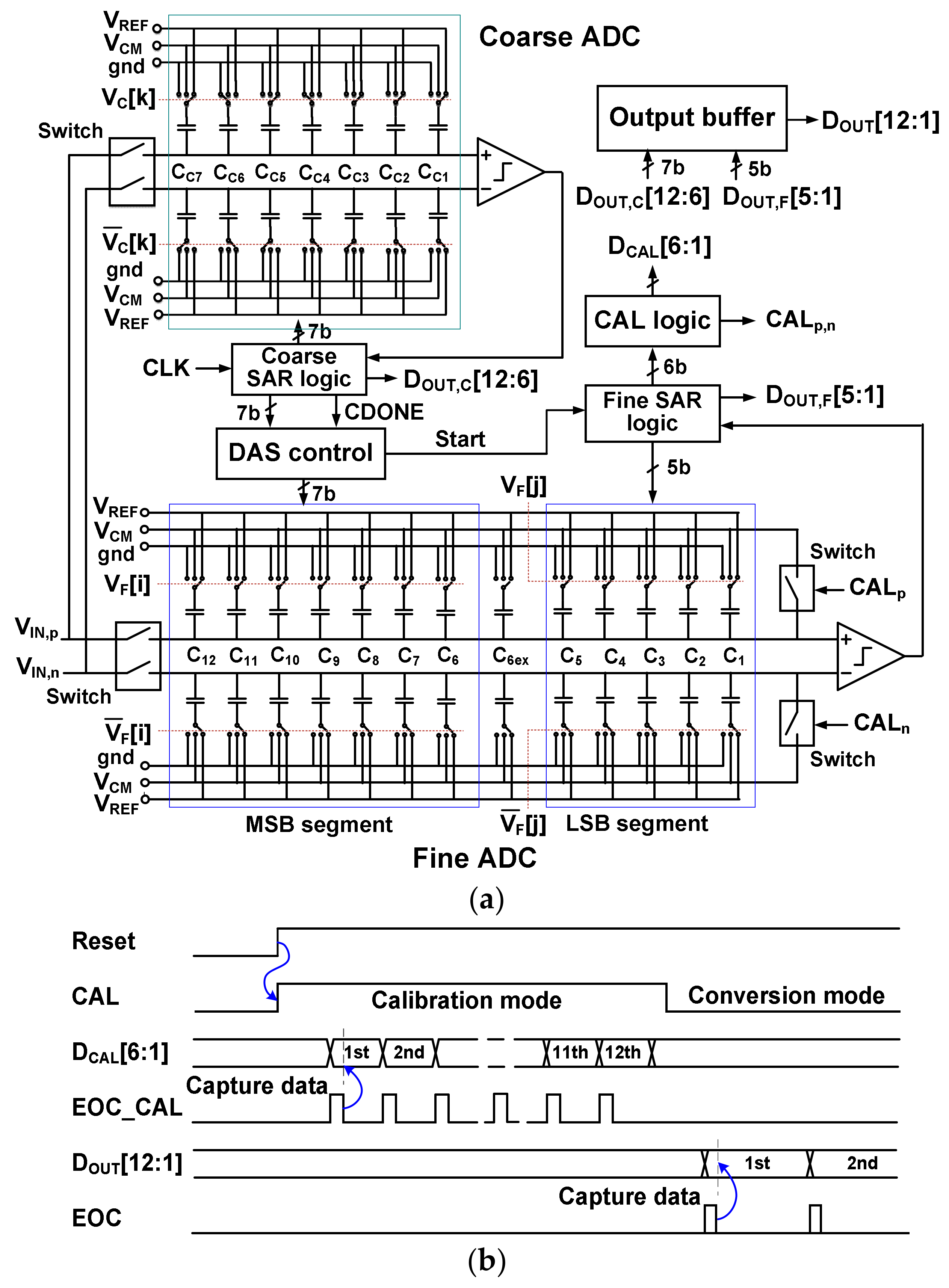

2.1. Subranging SAR ADC

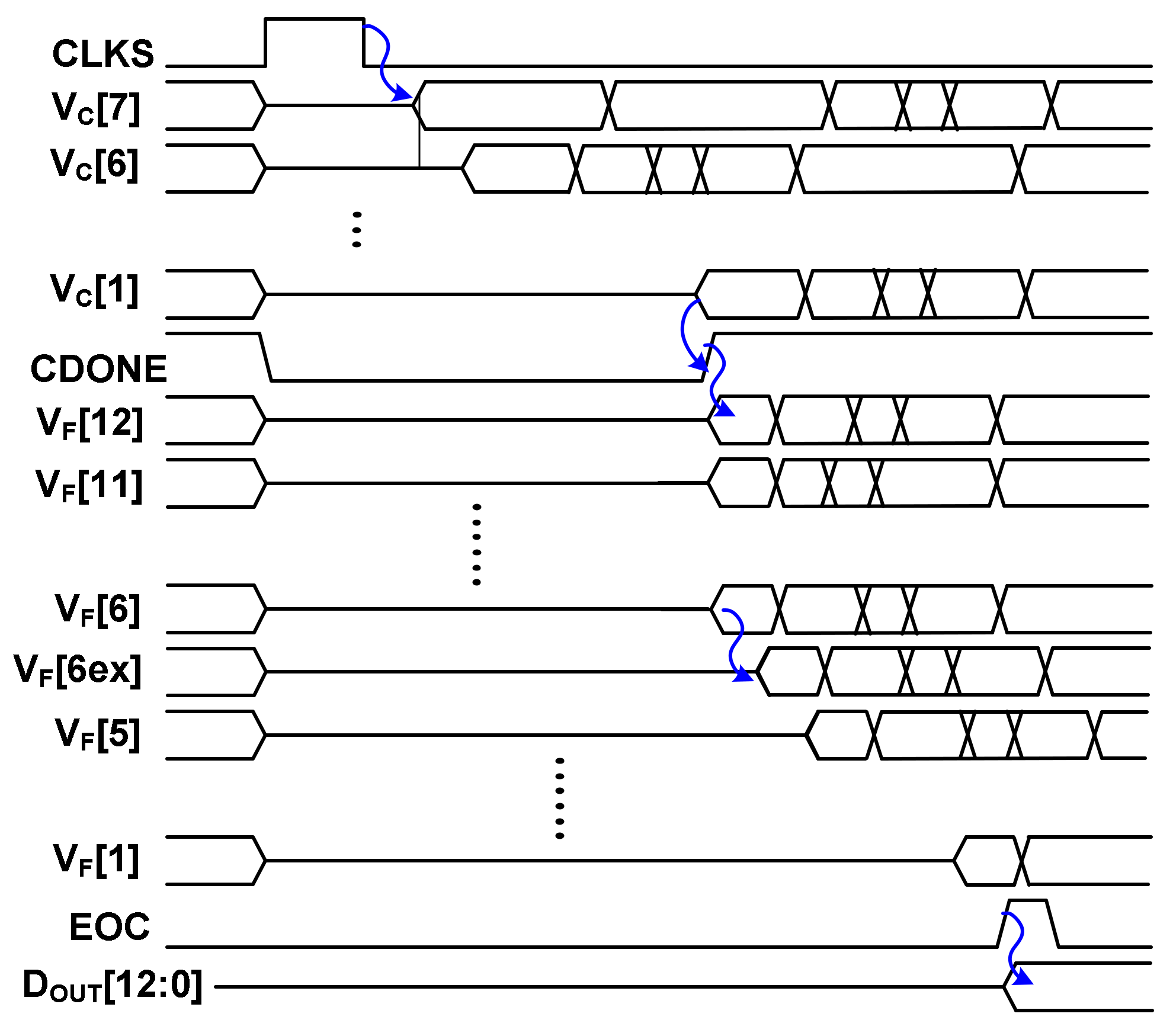

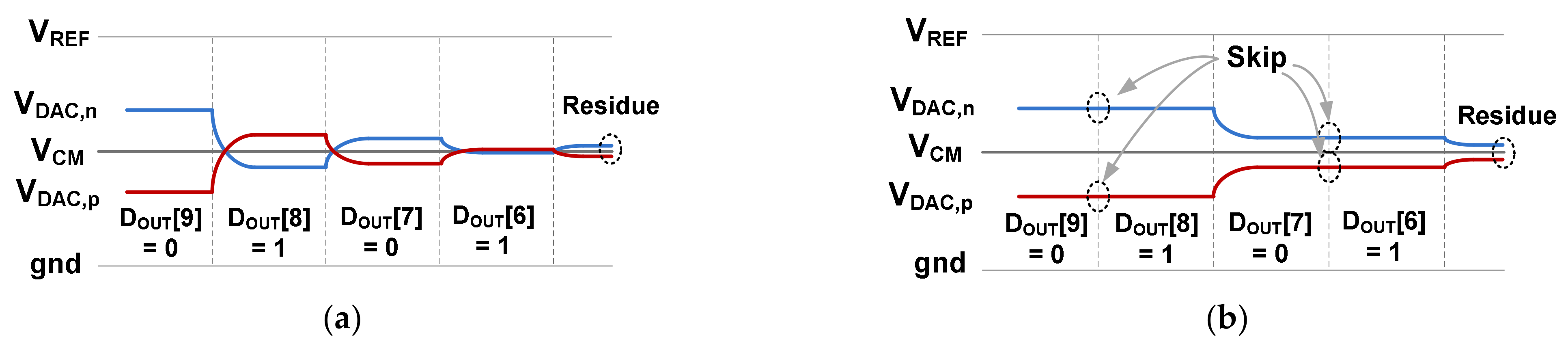

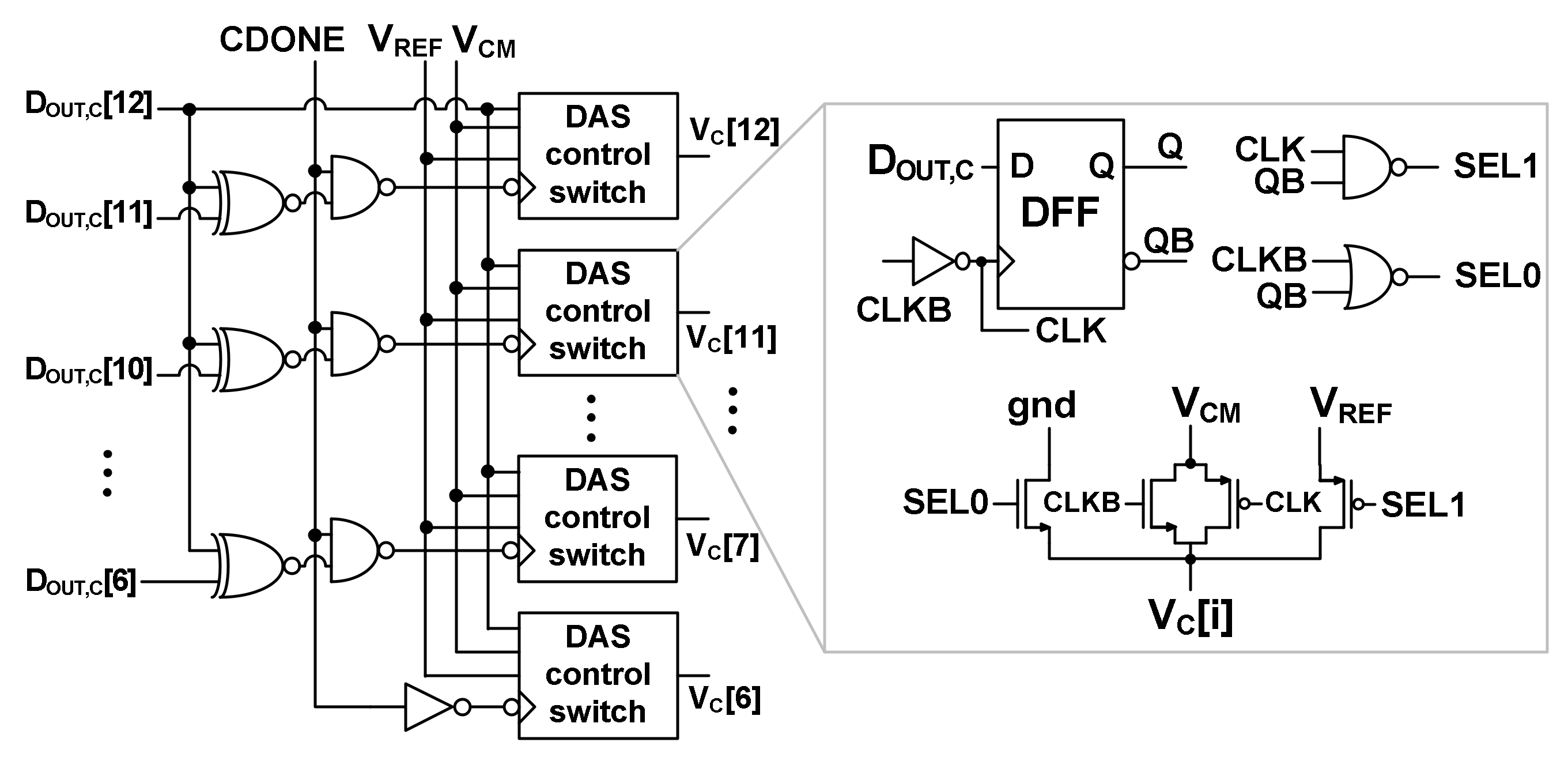

2.2. Merged Capacitor Switching with Detect and Skip

- (1)

- DOUT,C[MSB-1] = DOUT,C[MSB] → switch CMSB|DOUT,C[MSB-1] ≠ DOUT,C[MSB] → skip CMSB,

- (2)

- DOUT,C[MSB-2] = DOUT,C[MSB] → switch CMSB-1|DOUT,C[MSB-2] ≠ DOUT,C[MSB] → skip CMSB-1, …,

- (3)

- DOUT,C[MSB-k + 1] = DOUT,C[MSB] → switch CMSB-N+2|DOUT,C[MSB-k + 1] ≠ DOUT,C[MSB] → skip CMSB-N+2,

- (4)

- Switch CMSB-N+1,

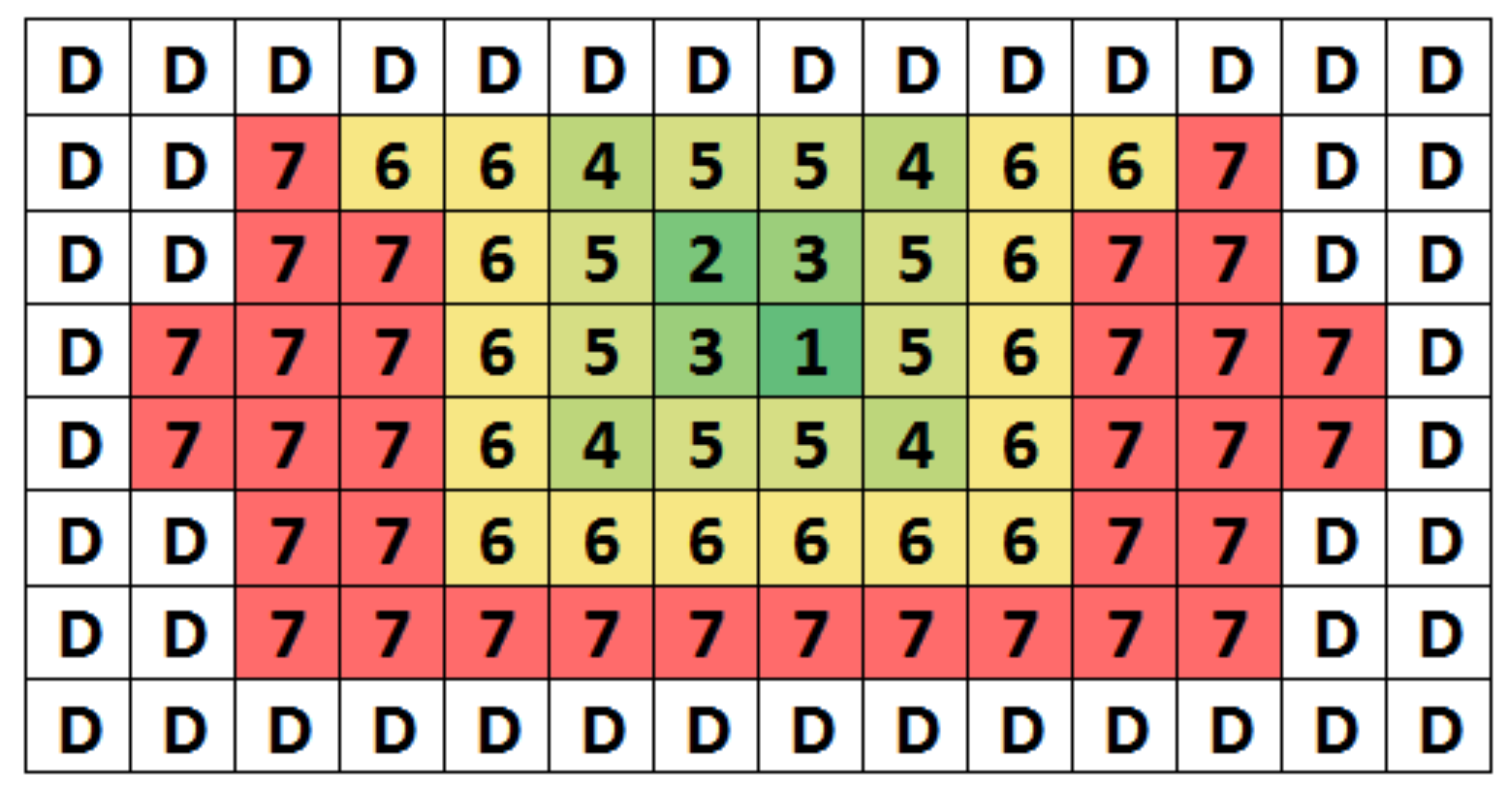

3. Mismatch Calibration

3.1. DAC Capacitor Mismatch Calibration

3.2. Mismatch Error of DAC Capacitor

3.3. Weight Error Extraction

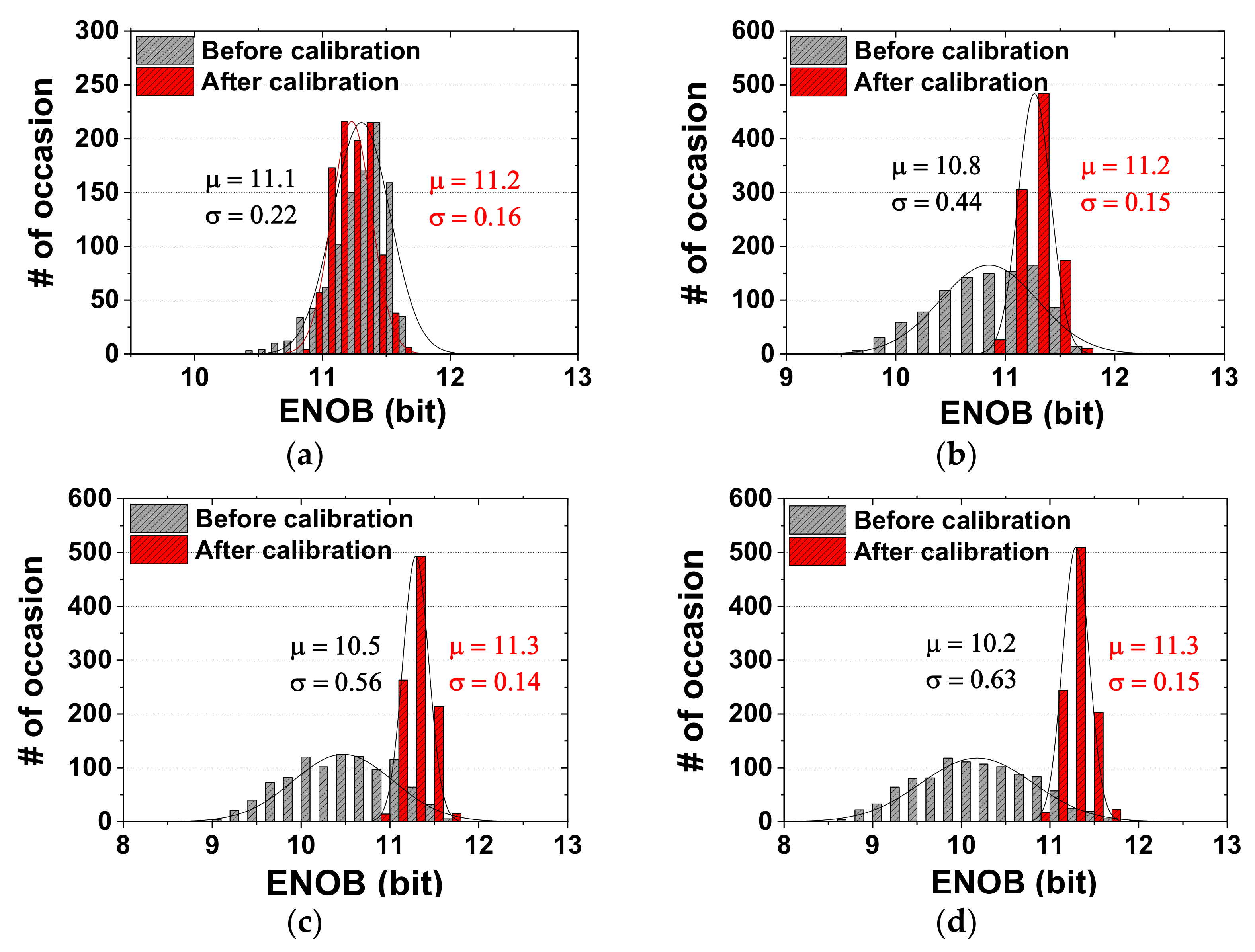

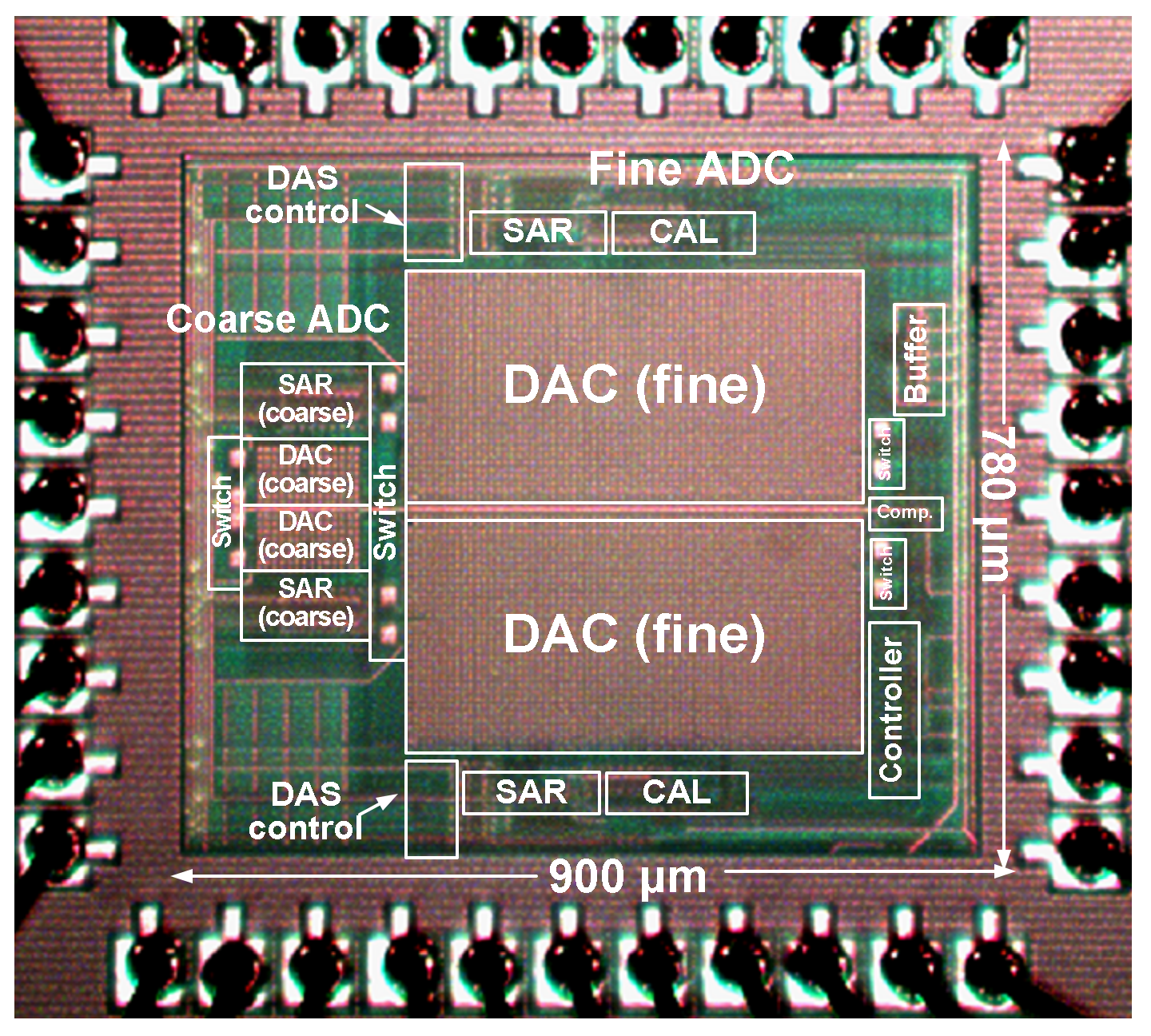

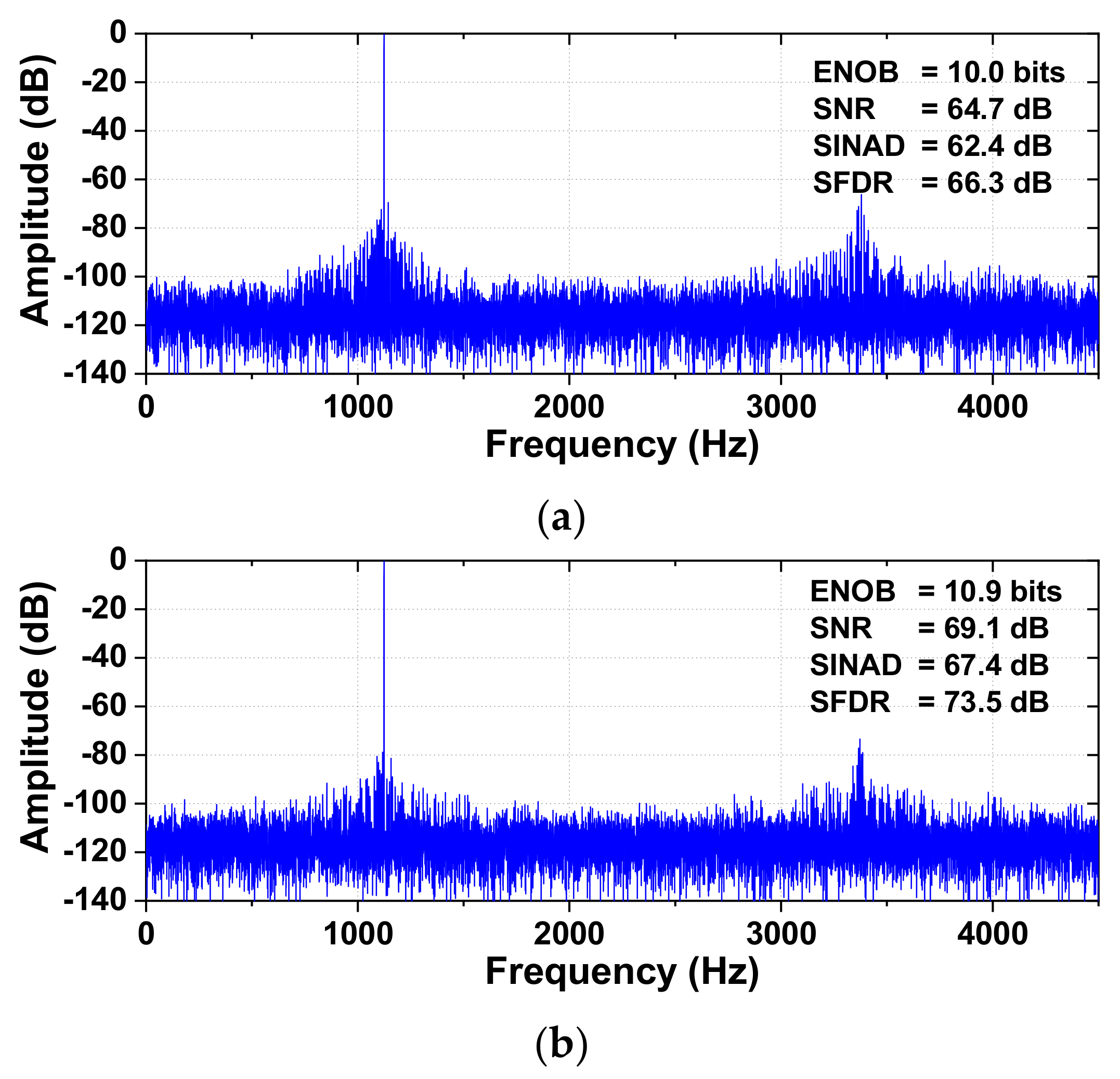

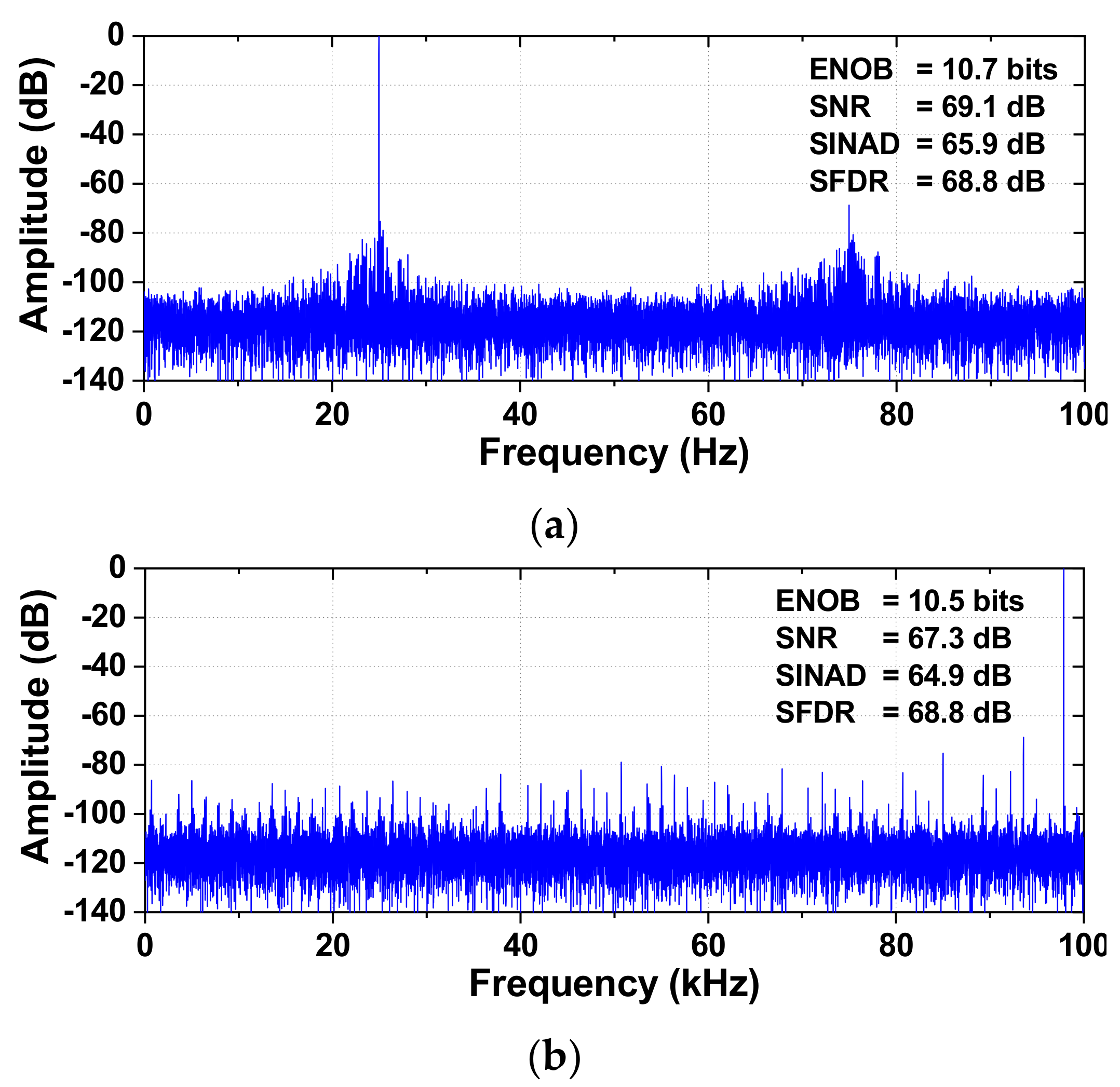

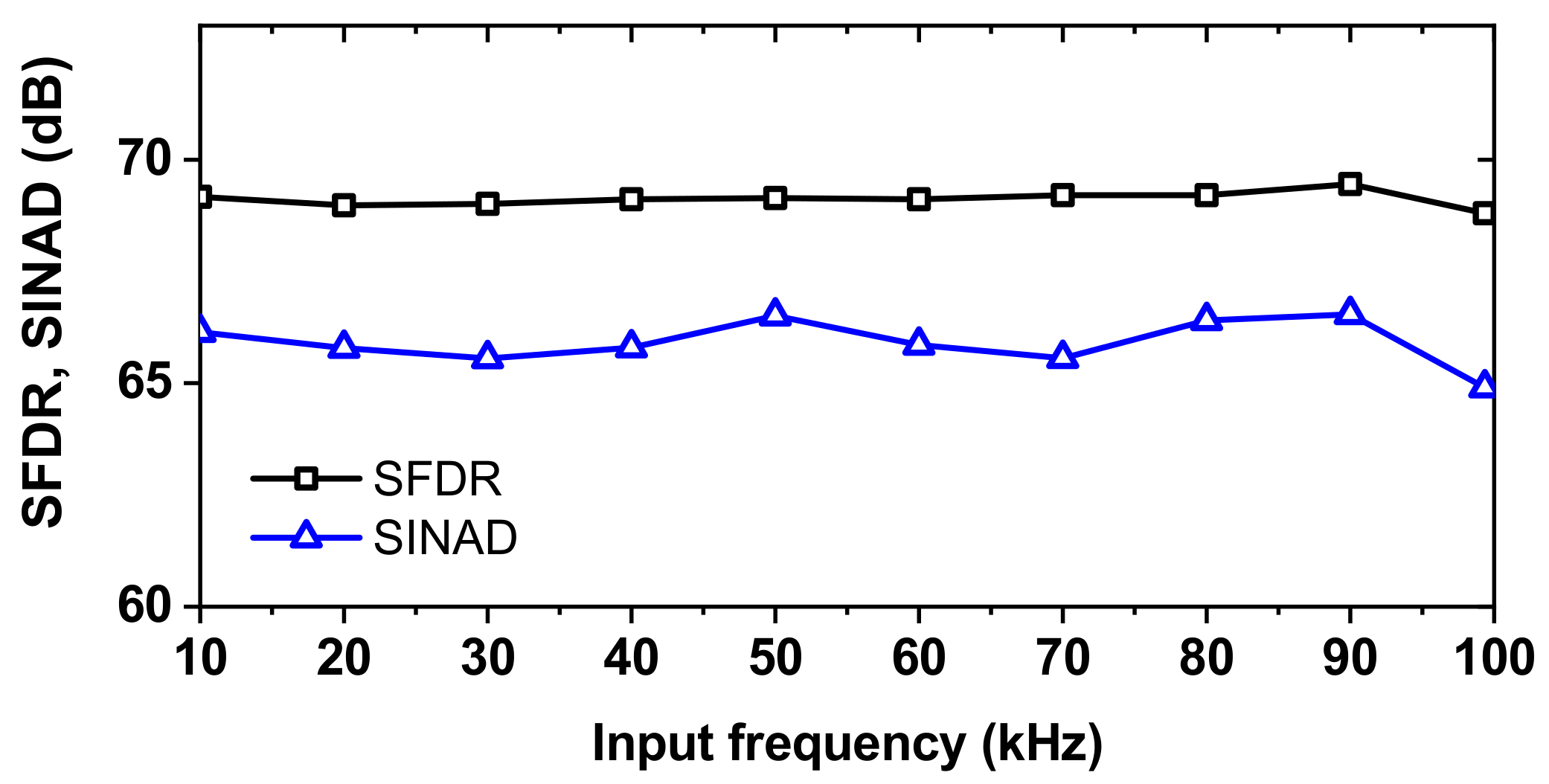

4. Measured Results

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

Appendix A. Monotonic Switching

- -

- If bN = 0, bN−1 = 0: total capacitance connected to VREF of the negative DAC branch is CT − CN−1 − CN;

- -

- If bN = 0, bN−1 = 1: total capacitance connected to VREF of the positive DAC branch is CT − CN−1;

- -

- If bN = 1, bN−1 = 0: total capacitance connected to VREF of the negative DAC branch is CT − CN−1;

- -

- If bN = 1, bN−1 = 1: total capacitance connected to VREF of the positive DAC branch is CT − CN−1 − CN.

Appendix B. Merged Capacitor Switching

References

- Saberi, M.; Lotfi, R.; Mafinezhad, K.; Serdijn, W.A. Analysis of power consumption and linearity in capacitive digital-to-analog converters used in successive approximation ADCs. IEEE Trans. Circuits Syst. I Reg. Pap. 2011, 58, 1736–1748. [Google Scholar] [CrossRef]

- Sadollahi, M.; Temes, G. An 11-bit 250-nW 10-kS/s SAR ADC with doubled input range for biomedical application. In Proceedings of the IEEE International Midwest Symposium on Circuits and Systems, Boston, MA, USA, 6–9 August 2017; pp. 385–388. [Google Scholar]

- Yoshioka, M.; Ishikawa, K.; Takayama, T.; Tsukamoto, S. A 10-b 50-MS/s 820-μW SAR ADC with on-chip digital calibration. IEEE Trans. Biomed. Circuits Syst. 2010, 4, 410–416. [Google Scholar] [CrossRef] [PubMed]

- Liu, C.; Chang, S.; Huang, G.; Lin, Y. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Liu, C.; Chang, S.; Huang, G.; Lin, Y. A 0.92 mW 10-bit 50-MS/s SAR ADC in 0.13 μm CMOS process. In Proceedings of the Symposium on VLSI Circuits, Digest of Technical Papers, Kyoto, Japan, 16–18 June 2009; pp. 236–237. [Google Scholar]

- Chang, Y.; Wang, C.; Wang, C. A 8-bit 500-KS/s low power SAR ADC for biomedical applications. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Jeju, Korea, 12–14 November 2007; pp. 228–231. [Google Scholar]

- Hariprasath, V.; Guerber, J.; Lee, S.-H.; Moon, U. Merged capacitor switching based SAR ADC with highest switching energy-efficiency. Electron. Lett. 2010, 46, 620–621. [Google Scholar] [CrossRef]

- Tai, H.-Y.; Hu, Y.-S.; Chen, H.-W.; Chen, H.-S. A 0.85fJ/conversion-step 10b 200 kS/s subranging SAR ADC in 40nm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 9–13 February 2014; pp. 196–197. [Google Scholar]

- Lee, J.H.; Park, D.; Cho, W.; Phan, H.N.; Nguyen, C.L.; Lee, J.-W. A 1.15 μW, 200 kS/s 10-b monotonic SAR ADC using dual on-chip calibrations and accuracy enhancement techniques. Sensors 2018, 18, 3486. [Google Scholar] [CrossRef] [PubMed]

- Um, J.Y.; Kim, Y.-J.; Song, E.-W.; Sim, J.-Y.; Park, H.-J. A digital-domain calibration of split-capacitor DAC for a differential SAR ADC without additional analog circuits. IEEE Trans. Circuits Syst. I Reg. Pap. 2013, 60, 2845–2856. [Google Scholar] [CrossRef]

- Ha, H.S.; Lee, S.-K.; Kim, B.S.; Park, H.-J.; Sim, J.-Y. A 0.5-V, 1.47-μW 40-kS/s 13-bit SAR ADC with capacitor error compensation. IEEE Trans. Circuits Syst. II Exp. Briefs 2014, 61, 840–844. [Google Scholar] [CrossRef]

- Liu, W.; Huang, P.; Chiu, Y. A 12-bit 45-MS/s, 3-mW redundant successive-approximation-register analog-to-digital converter with digital calibration. IEEE J. Solid-State Circuits 2011, 46, 2661–2672. [Google Scholar] [CrossRef]

- Zhang, D.; Alvandpour, A. Analysis and calibration of nonbinary-weighted capacitive DAC for high-resolution SAR ADCs. IEEE Trans. Circuits Syst. II Exp. Briefs 2014, 61, 666–670. [Google Scholar] [CrossRef][Green Version]

- Choi, C.; Lee, J.-W. An 11.8-fJ/conversion-step noise shaping SAR ADC with embedded passive gain for energy-efficient IoT sensors. Sensors 2022, 22, 869. [Google Scholar] [CrossRef] [PubMed]

- Guerber, J.; Venkatram, H.; Oh, T.; Moon, U. Enhanced SAR ADC energy efficiency from the early reset merged capacitor switching algorithm. In Proceedings of the IEEE International Symposium on Circuits and Systems, Seoul, Korea, 20–23 May 2012; pp. 2361–2364. [Google Scholar]

- Liu, M.; Roermund, A.; Harpe, P. A 7.1fJ/conv.-step 88 dB-SFDR 12b SAR ADC with energy-efficient swap-to-reset. In Proceedings of the IEEE European Solid-State Circuits Conference, Lausanne, Switzerland, 12–15 September 2016; pp. 409–412. [Google Scholar]

- Chang, D.-J.; Kim, W.; Seo, M.-J.; Hong, H.-K.; Ryu, S.-T. Normalized-full-scale-referencing digital-domain linearity calibration for SAR ADC. IEEE Trans. Circuits Syst. I Reg. Pap. 2017, 64, 322–332. [Google Scholar] [CrossRef]

- Lim, Y.; Flynn, M.P. A 1 mW 71.5 dB SNDR 50 MS/s 13 bit fully differential ring amplifier based SAR-assisted pipeline ADC. IEEE J. Solid-State Circuits 2015, 50, 2901–2911. [Google Scholar] [CrossRef]

- Ding, M.; Harpe, P.; Liu, Y.-H.; Busze, B.; Philips, K.; Groot, H. A 46 μW 13 b 6.4 MS/s SAR ADC with background mismatch and offset calibration. IEEE J. Solid-State Circuits 2016, 52, 423–432. [Google Scholar] [CrossRef]

- Chen, L.; Sanyal, A.; Ma, J.; Sun, N. A 24-μW 11-bit 1-MS/s SAR ADC with a bidirectional single-side switching technique. In Proceedings of the IEEE European Solid State Circuits Conference, Venice, Italy, 22–26 September 2014; pp. 219–222. [Google Scholar]

| DAC Capacitor | Capacitance (CU) | Ideal Weight |

|---|---|---|

| C12 | 1024 | 64/129 |

| C11 | 512 | 32/129 |

| C10 | 256 | 16/129 |

| C9 | 128 | 8/129 |

| C8 | 64 | 4/129 |

| C7 | 32 | 2/129 |

| C6 | 16 | 1/129 |

| C6ex | 16 | 1/129 |

| C5 | 8 | 1/258 |

| C4 | 4 | 1/516 |

| C3 | 2 | 1/1032 |

| C2 | 1 | 1/2064 |

| C1 | 1 | 1/2064 |

| Total | 2064 | 1 |

| [2] | [8] | [11] | [16] | [18] | [19] | [20] | This Work | |

|---|---|---|---|---|---|---|---|---|

| Tech. (nm) | 180 | 40 | 130 | 65 | 40 | 180 | 65 | 180 |

| Supply (V) | 0.75 | 0.45 | 0.5 | 0.8 | 1.0 | 1.0 | 1.2 | 1.8/1.0 |

| Resolution (bit) | 11 | 10 | 13 | 12 | 13 | 11 | 13 | 12 |

| Rate (kS/s) | 10 | 200 | 40 | 40 | 6400 | 1000 | 50,000 | 200 |

| SINAD (dB) | 60.5 | 55.6 | 66.3 | 64.2 | 64.1 | 63.4 | 70.9 | 67.4 |

| SFDR (dB) | 72.0 | 76.2 | 71.0 | 88.2 | 68.8 | 76.6 | 84.6 | 73.5 |

| ENOB † (bit) | 9.8 | 8.95 | 10.7 | 10.4 | 10.4 | 10.3 | 11.5 | 10.9 |

| Calibration | No | No | Yes | No | Yes | No | No | Yes |

| Power (μW) | 0.25 | 0.084 | 1.47 | 0.38 | 46 | 24 | 1000 | 5.08 |

| Area (mm2) | 0.13 | 0.007 | 0.9 | 0.11 | 0.07 | 0.1 | 0.05 | 0.7 |

| FoMW * (fJ/conv.-step) | 28.8 | 0.85 | 21.8 | 7.1 | 2.2 | 19.9 | 6.9 | 13.2 |

| FoMS ** (dB) | 163.5 | 176.4 | 167.6 | 171.5 | 172.5 | 166.6 | 114.9 | 170.4 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nguyen, C.L.; Phan, H.N.; Lee, J.-W. A 12-b Subranging SAR ADC Using Detect-and-Skip Switching and Mismatch Calibration for Biopotential Sensing Applications. Sensors 2022, 22, 3600. https://doi.org/10.3390/s22093600

Nguyen CL, Phan HN, Lee J-W. A 12-b Subranging SAR ADC Using Detect-and-Skip Switching and Mismatch Calibration for Biopotential Sensing Applications. Sensors. 2022; 22(9):3600. https://doi.org/10.3390/s22093600

Chicago/Turabian StyleNguyen, Cong Luong, Huu Nhan Phan, and Jong-Wook Lee. 2022. "A 12-b Subranging SAR ADC Using Detect-and-Skip Switching and Mismatch Calibration for Biopotential Sensing Applications" Sensors 22, no. 9: 3600. https://doi.org/10.3390/s22093600

APA StyleNguyen, C. L., Phan, H. N., & Lee, J.-W. (2022). A 12-b Subranging SAR ADC Using Detect-and-Skip Switching and Mismatch Calibration for Biopotential Sensing Applications. Sensors, 22(9), 3600. https://doi.org/10.3390/s22093600