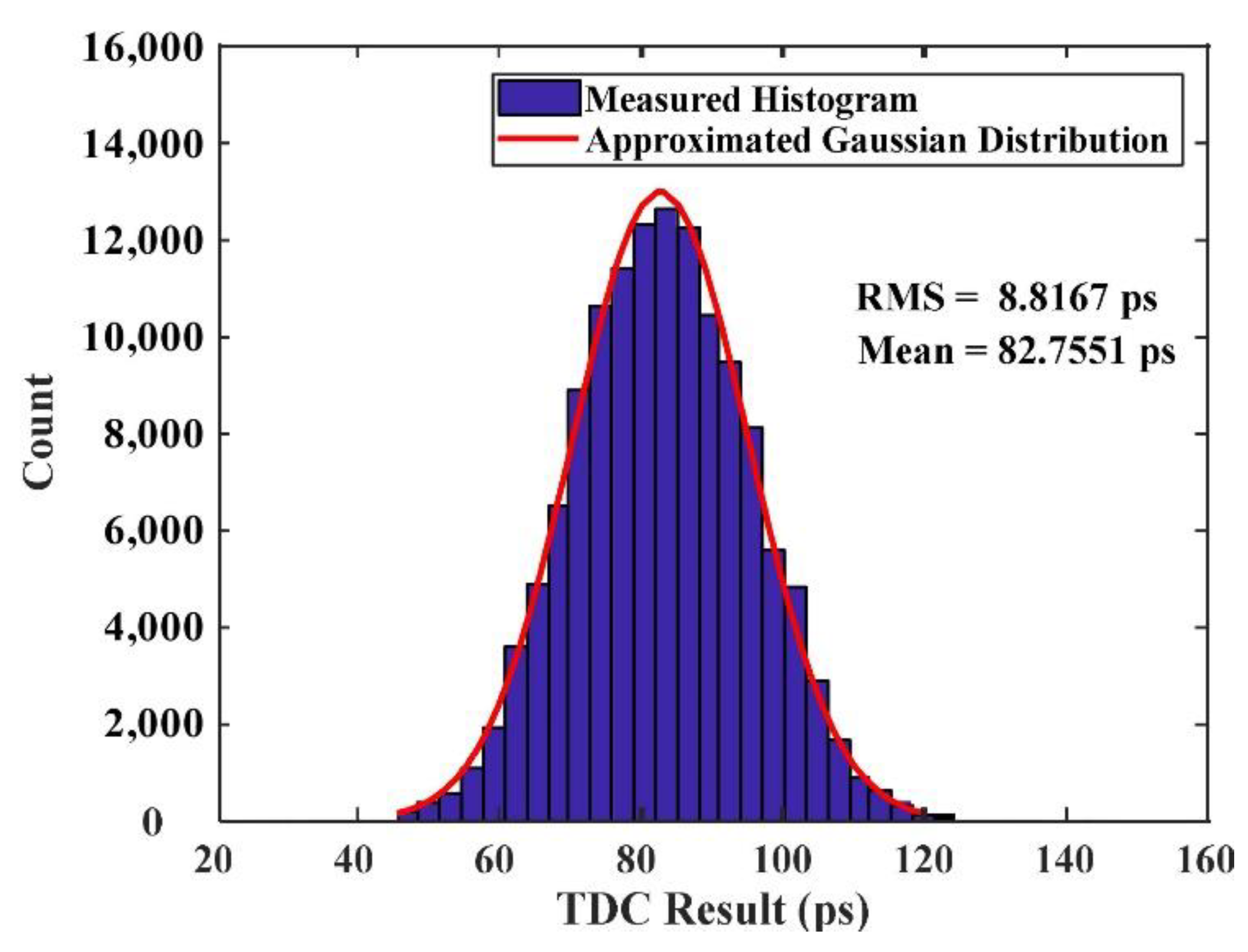

An 8.8 ps RMS Resolution Time-To-Digital Converter Implemented in a 60 nm FPGA with Real-Time Temperature Correction

Abstract

1. Introduction

2. Operating Principles

2.1. Top-Level Diagram of NUMP TDC

2.2. Temperature Characteristics of Delay Chain

2.3. Temperature Measurement Structure

2.4. Top-Level Diagram of NUMP TDC with Temperature Correction Module

3. Implementation

3.1. Top-Level Diagram of Temperature Correction Module

3.2. Clock Sorting Operation for Temperature Measurement

3.3. Temperature Correction Start Module

3.4. LUT Correction Module

3.5. LUT Reorder Module

4. Experimental Validation

4.1. Variation of Edge Values with Temperature Changes

4.2. Nonlinearities

4.3. TDC Measurement

5. Discussion

5.1. Correction Parameters of Temperature Correction Module

5.2. Carry Chain Differences between Cyclone V and Cyclone 10 LP

5.3. Resource Usage and Power Consumption

5.4. Features of the Temperature Correction Method

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Venialgo, E.; Lusardi, N.; Garzetti, F.; Geraci, A.; Brunner, S.E.; Schaart, D.R.; Charbon, E. Toward a Full-Flexible and Fast-Prototyping TOF-PET Block Detector Based on TDC-on-FPGA. IEEE Trans. Radiat. Plasma Med. Sci. 2019, 5, 538–548. [Google Scholar] [CrossRef]

- Won, J.Y.; Lee, J.S. Highly Integrated FPGA-Only Signal Digitization Method Using Single-Ended Memory Interface Input Receivers for Time-of-Flight PET Detectors. IEEE Trans. Biomed. Circuits Syst. 2018, 6, 1401–1409. [Google Scholar] [CrossRef] [PubMed]

- Carra, P.; Bertazzoni, M.; Bisogni, M.G.; Cela Ruiz, J.M.; Del Guerra, A.; Gascon, D.; Gomez, S.; Morrocchi, M.; Pazzi, G.; Sanchez, D.; et al. Auto-Calibrating TDC for an SoC-FPGA Data Acquisition System. IEEE Trans. Radiat. Plasma Med. Sci. 2019, 5, 549–556. [Google Scholar] [CrossRef]

- Carrara, L.; Fiergolski, A. An Optical Interference Suppression Scheme for TCSPC Flash LiDAR Imagers. Appl. Sci. 2019, 11, 2206–2220. [Google Scholar] [CrossRef]

- Yoshioka, K.; Kubota, H.; Fukushima, T.; Kondo, S.; Ta, T.T.; Okuni, H.; Watanabe, K.; Hirono, M.; Ojima, Y.; Kimura, K.; et al. A 20-ch TDC/ADC Hybrid Architecture LiDAR SoC for 240 x96 Pixel 200-m Range Imaging with Smart Accumulation Technique and Residue Quantizing SAR ADC. IEEE J. Solid-St. Circ. 2018, 11, 3026–3038. [Google Scholar] [CrossRef]

- Li, X.; Yang, B.; Xie, X.; Li, D.; Xu, L. Influence of Waveform Characteristics on LiDAR Ranging Accuracy and Precision. Sensors 2018, 18, 1156–1171. [Google Scholar] [CrossRef]

- Li, H.; Gong, G.; Li, J. Portable Calibration Node for LHAASO-KM2A Detector Array. IEEE Trans. Nucl. Sci. 2017, 6, 1363–1366. [Google Scholar] [CrossRef]

- Du, Q.; Gong, G.; Pan, W.; on behalf of the LHAASO Collaboration. A packet-based precise timing and synchronous DAQ network for the LHAASO project. Nucl. Instrum. Methods Phys. Res. A 2013, 732, 488–492. [Google Scholar] [CrossRef]

- Liang, Y.; Zhao, L.; Guo, Y.; Qin, J.; Yang, Y.; Cheng, B.; Liu, S.; An, Q. A multichannel front end ASIC for PMT readout in LHAASO WCDA. J. Instrum. 2018, 13. [Google Scholar] [CrossRef]

- Bifulco, P.; Izzo, V.; Mastroianni, S.; Aloisio, A.; Giordano, R.; Ameli, F.; Bocci, V.; Cadeddu, S.; Casu, L.; Lai, A.; et al. A fully-digital and fully synthetizable TDC for high energy physics experiments. In Proceedings of the 2nd International Conference on Event-Based Control, Communication, and Signal Processing (EBCCSP), Krakow, Poland, 13–15 June 2016; pp. 1–4. [Google Scholar]

- Zhang, M.; Wang, H.; Liu, Y. A 7.4 ps FPGA-Based TDC with a 1024-Unit Measurement Matrix. Sensors 2017, 17, 865–883. [Google Scholar] [CrossRef]

- Szyduczyński, J.; Kościelnik, D.; Miśkowicz, M. A Successive Approximation Time-to-Digital Converter with Single Set of Delay Lines for Time Interval Measurements. Sensors 2019, 19, 1109. [Google Scholar] [CrossRef]

- Szplet, R.; Kalisz, J.; Szymanowski, R. Interpolating time counter with 100 ps resolution on a single FPGA device. IEEE Trans. Instrum. Meas. 2000, 4, 879–833. [Google Scholar] [CrossRef]

- ANALOG DEVICES Inc. 5A, Low Noise, Programmable Output, 85mV Dropout Linear Regulator; ANALOG DEVICES, Inc.: Norwood, MA, USA, 2019. [Google Scholar]

- Wu, J.; Shi, Z. The 10ps wave union TDC: Improving FPGA TDC resolution beyond its cell delay. In Proceedings of the IEEE International Symposium Circuits and Systems, Como, Italy, 5–9 October 2008; pp. 3440–3446. [Google Scholar]

- Qin, X.; Wang, L.; Liu, D.; Zhao, Y.; Rong, X.; Du, J. A 1.15ps Bin Size and 3.5ps Single-Shot Precision Time-to-Digital Converter with On-Board Offset Correction in an FPGA. IEEE Trans. Nucl. Sci. 2017, 12, 2951–2957. [Google Scholar] [CrossRef]

- Qin, X.; Feng, C.; Zhang, D.; Miao, B.; Zhao, L.; Hao, X.; Liu, S.; An, Q. Development of a High Resolution TDC for Implementation in Flash-Based and Anti-Fuse FPGAs for Aerospace Application. IEEE Trans. Nucl. Sci. 2013, 5, 3550–3556. [Google Scholar] [CrossRef]

- Pan, W.; Gong, G.; Li, J. A 20ps Time-to-Digital Converter (TDC) Implemented in Field-Programmable Gate Array (FPGA) with Automatic Temperature Correction. IEEE Trans. Nucl. Sci. 2014, 3, 1468–1473. [Google Scholar] [CrossRef]

- Chen, Y. Time Resolution Improvement Using Dual Delay Lines for Field-Programmable-Gate- Array-Based Time-to-Digital Converters with Real-Time Calibration. Appl. Sci. 2018, 9, 20. [Google Scholar] [CrossRef]

- Van, L.; Xuan, T.; Lee, H. A Novel FPGA Implementation of a Time-to-Digital Converter Supporting Run-Time Estimation and Compensation. ACM Trans. Reconfig. Technol. Syst. 2019, 12, 10. [Google Scholar]

- Miskowicz, M. Event-Based Control and Signal Processing; CRC Press: Boca Raton, FL, USA, 2016. [Google Scholar]

- Miskowicz, M. Send-On-Delta Concept: An Event-Based Data Reporting Strategy. Sensors 2006, 6, 49–63. [Google Scholar] [CrossRef]

- Pérez-Torres, R.; Torres-Huitzil, C.; Galeana-Zapién, H. A Cognitive-Inspired Event-Based Control for Power-Aware Human Mobility Analysis in IoT Devices. Sensors 2019, 19, 832. [Google Scholar] [CrossRef]

- Barrios-Avilés, J.; Rosado-Muñoz, A.; Medus, L.D.; Bataller-Mompeán, M.; Guerrero-Martínez, J.F. Less Data Same Information for Event-Based Sensors: A Bioinspired Filtering and Data Reduction Algorithm. Sensors 2018, 18, 4122. [Google Scholar] [CrossRef]

- Leon-Garcia, F.; Palomares, J.M.; Olivares, J. D2R-TED: Data—Domain Reduction Model for Threshold-Based Event Detection in Sensor Networks. Sensors 2018, 18, 3806. [Google Scholar] [CrossRef]

- Gao, Y.; Li, Y.; Peng, L.; Liu, J. Design of Event-Triggered Fault-Tolerant Control for Stochastic Systems with Time-Delays. Sensors 2018, 18, 1929. [Google Scholar] [CrossRef]

- Shen, Y.; Kong, Z.; Ding, L. Flocking of Multi-Agent System with Nonlinear Dynamics via Distributed Event-Triggered Control. Appl. Sci. 2019, 9, 1336. [Google Scholar] [CrossRef]

- Sui, T.; Zhao, Z.; Xie, S.; Xie, Y.; Zhao, Y.; Huang, Q.; Xu, J.; Peng, Q. A 2.3ps RMS Resolution Time-to-Digital Converter Implemented in a Low-Cost Cyclone V FPGA. IEEE Trans. Instrum. Meas. 2019, 10, 3647–3660. [Google Scholar] [CrossRef]

- Intel Inc. Cyclone 10 LP Device Handbook: Logic Array Blocks; C10LP-51003; Intel Inc.: Santa Clara, CA, USA, 2020. [Google Scholar]

- Intel Inc. Cyclone II Device Handbook: Logic Array Blocks; CII-51002; Intel Inc.: Santa Clara, CA, USA, 2007. [Google Scholar]

- Tancock, S.; Arabul, E.; Dahnoun, N. A Review of New Time-to-Digital Conversion Techniques. IEEE Trans. Instrum. Meas. 2019, 10, 3406–3417. [Google Scholar] [CrossRef]

- Machado, R.; Cabral, J.; Alves, F.S. Recent Developments and Challenges in FPGA-Based Time-to-Digital Converters. IEEE T. Instrum. Meas. 2019, 11, 4205–4221. [Google Scholar] [CrossRef]

- Intel Inc. Cyclone V Device Handbook: Logic Array Blocks; CV-52001; Intel Inc.: Santa Clara, CA, USA, 2019. [Google Scholar]

| Memory Address | Cell Number | Edge Value (Uncorrected) | Edge Value (Corrected) | The Bigger Edge Value | Alternative | Alternative Address |

|---|---|---|---|---|---|---|

| 1 | 1 | 0 | 0 | 46 | 46 | 2 |

| 2 | 144 | 3 | 46 | |||

| 3 | 202 | 5 | 22 | 53 | 53 | 4 |

| 4 | 259 | 7 | 53 | |||

| 5 | 143 | 8 | 52 | 52 | 53 | 4 |

| 6 | 26 | 10 | 45 | |||

| 7 | 201 | 20 | 41 | 41 | 53 | 4 |

| 8 | 11 | 21 | 33 | |||

| 9 | 291 | 26 | 36 | 92 | 92 | 10 |

| 10 | 346 | 34 | 92 |

| Memory Address | Cell Number | Edge Value (Uncorrected) | Edge Value (Corrected) | The Bigger Edge Value | Alternative | Alternative’s Address |

|---|---|---|---|---|---|---|

| 1 | 1 | 0 | 0 | 46 | 46 | 2 |

| 2 | 144 | 3 | 46 | |||

| 3 | 202 | 5 | 22 | 53 | 53 | 4 |

| 4 | 259 | 7 | 53 | |||

| 5 | 143 | 8 | 52 | 52 | 53 | 4 |

| 6 | 26 | 10 | 45 | |||

| 7 | 201 | 20 | 41 | 41 | 53 | 4 |

| 8 | 11 | 21 | 33 | |||

| 9 | 291 | 26 | 36 | 36 | 53 | 4 |

| 10 | 346 | — | — | 92 | — | — |

| Memory Address | Cell Number | Edge Value (Uncorrected) | Edge Value (Corrected) | The Bigger Edge Value | Alternative | Alternative’s Address |

|---|---|---|---|---|---|---|

| 1 | 1 | 0 | 0 | 46 | 46 | 2 |

| 2 | 144 | 3 | 46 | |||

| 3 | 202 | 5 | 22 | 36 | 36 | 4 |

| 4 | 291 | 7 | 53 | |||

| 5 | 143 | 8 | 52 | 52 | 52 | 5 |

| 6 | 26 | 10 | 45 | |||

| 7 | 201 | 20 | 41 | 41 | 52 | 5 |

| 8 | 11 | 21 | 33 | |||

| 9 | 259 | — | — | 53 | — | — |

| 10 | 346 | — | — | 92 | — | — |

| Temperature | Delay Chain_1 | Delay Chain_2 | Delay Chain_3 | Delay Chain_4 | ΔKMAX |

|---|---|---|---|---|---|

| 20 °C–10 °C | y = 0.412x − 9.551 | y = 0.416x − 10.838 | y = 0.416x − 11.524 | y = 0.398x − 11.503 | 0.014 |

| 30 °C–10 °C | y = 0.710x − 10.38 | y = 0.727x − 14.268 | y = 0.732x − 16.601 | y = 0.709x − 16.551 | 0.022 |

| 40 °C–10 °C | y = 0.934x + 2.176 | y = 0.942x − 0.444 | y = 0.954x − 3.858 | y = 0.923x − 3.355 | 0.020 |

| 50 °C–10 °C | y = 1.242x + 4.152 | y = 1.253x + 0.278 | y = 1.242x + 4.152 | y = 1.234x − 3.393 | 0.011 |

| 60 °C–10 °C | y = 1.465x − 9.062 | y = 1.489x − 13.876 | y = 1.490x − 17.602 | y = 1.463x − 18.126 | 0.025 |

| 70 °C–10 °C | y = 1.811x − 14.357 | y = 1.837x − 20.103 | y = 1.843x − 24.844 | y = 1.794x − 24.417 | 0.032 |

| Delay Chain_1 | Delay Chain_2 | Delay Chain_3 | Delay Chain_4 | ΔMAX | |

|---|---|---|---|---|---|

| Fitting results | Y = 0.027X − 0.134 | Y = 0.028X − 0.136 | Y = 0.028X − 0.125 | Y = 0.027X − 0.141 | 0.001 |

| R2 | 0.99848 | 0.99833 | 0.99856 | 0.99862 | 0.0029 |

| Resources | Used | Utilization | |

|---|---|---|---|

| NIOS CPU | logic cells | 8826 | 7.411% |

| logic registers | 5730 | 4.812% | |

| memory bits | 104,016 | 2.612% | |

| NUMP TDC without temperature correction (single channel) | logic cells | 1377 | 1.156% |

| logic registers | 708 | 0.595% | |

| memory bits | 23,552 | 0.592% | |

| Temperature correction module | logic cells | 1230 | 1.033% |

| logic registers | 689 | 0.577% | |

| memory bits | 3072 | 0.077% |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Song, Z.; Zhao, Z.; Yu, H.; Yang, J.; Zhang, X.; Sui, T.; Xu, J.; Xie, S.; Huang, Q.; Peng, Q. An 8.8 ps RMS Resolution Time-To-Digital Converter Implemented in a 60 nm FPGA with Real-Time Temperature Correction. Sensors 2020, 20, 2172. https://doi.org/10.3390/s20082172

Song Z, Zhao Z, Yu H, Yang J, Zhang X, Sui T, Xu J, Xie S, Huang Q, Peng Q. An 8.8 ps RMS Resolution Time-To-Digital Converter Implemented in a 60 nm FPGA with Real-Time Temperature Correction. Sensors. 2020; 20(8):2172. https://doi.org/10.3390/s20082172

Chicago/Turabian StyleSong, Zhipeng, Zhixiang Zhao, Hongsen Yu, Jingwu Yang, Xi Zhang, Tengjie Sui, Jianfeng Xu, Siwei Xie, Qiu Huang, and Qiyu Peng. 2020. "An 8.8 ps RMS Resolution Time-To-Digital Converter Implemented in a 60 nm FPGA with Real-Time Temperature Correction" Sensors 20, no. 8: 2172. https://doi.org/10.3390/s20082172

APA StyleSong, Z., Zhao, Z., Yu, H., Yang, J., Zhang, X., Sui, T., Xu, J., Xie, S., Huang, Q., & Peng, Q. (2020). An 8.8 ps RMS Resolution Time-To-Digital Converter Implemented in a 60 nm FPGA with Real-Time Temperature Correction. Sensors, 20(8), 2172. https://doi.org/10.3390/s20082172