An 8-Tap CMOS Lock-In Pixel Image Sensor for Short-Pulse Time-of-Flight Measurements

Abstract

1. Introduction

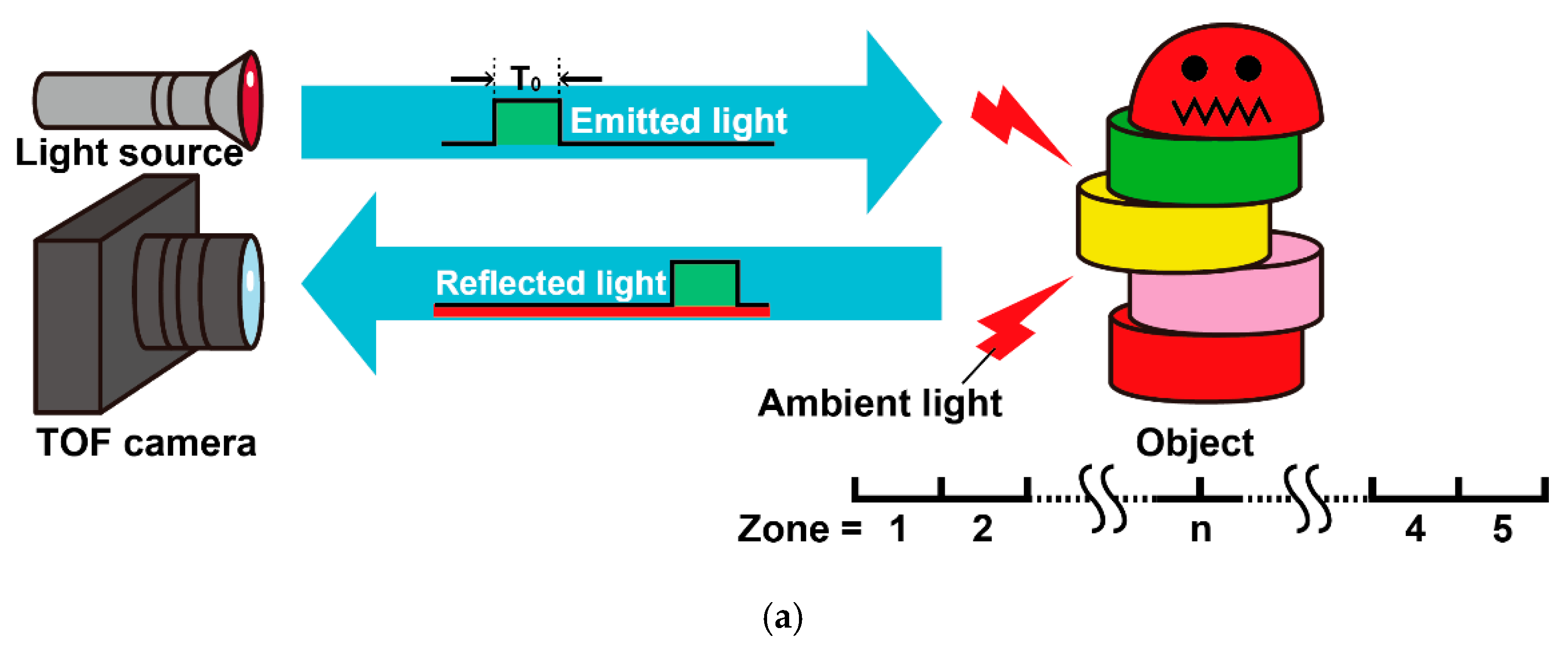

2. Multiple-Tap Lock-In-Pixel and Short-Pulse TOF Measurements

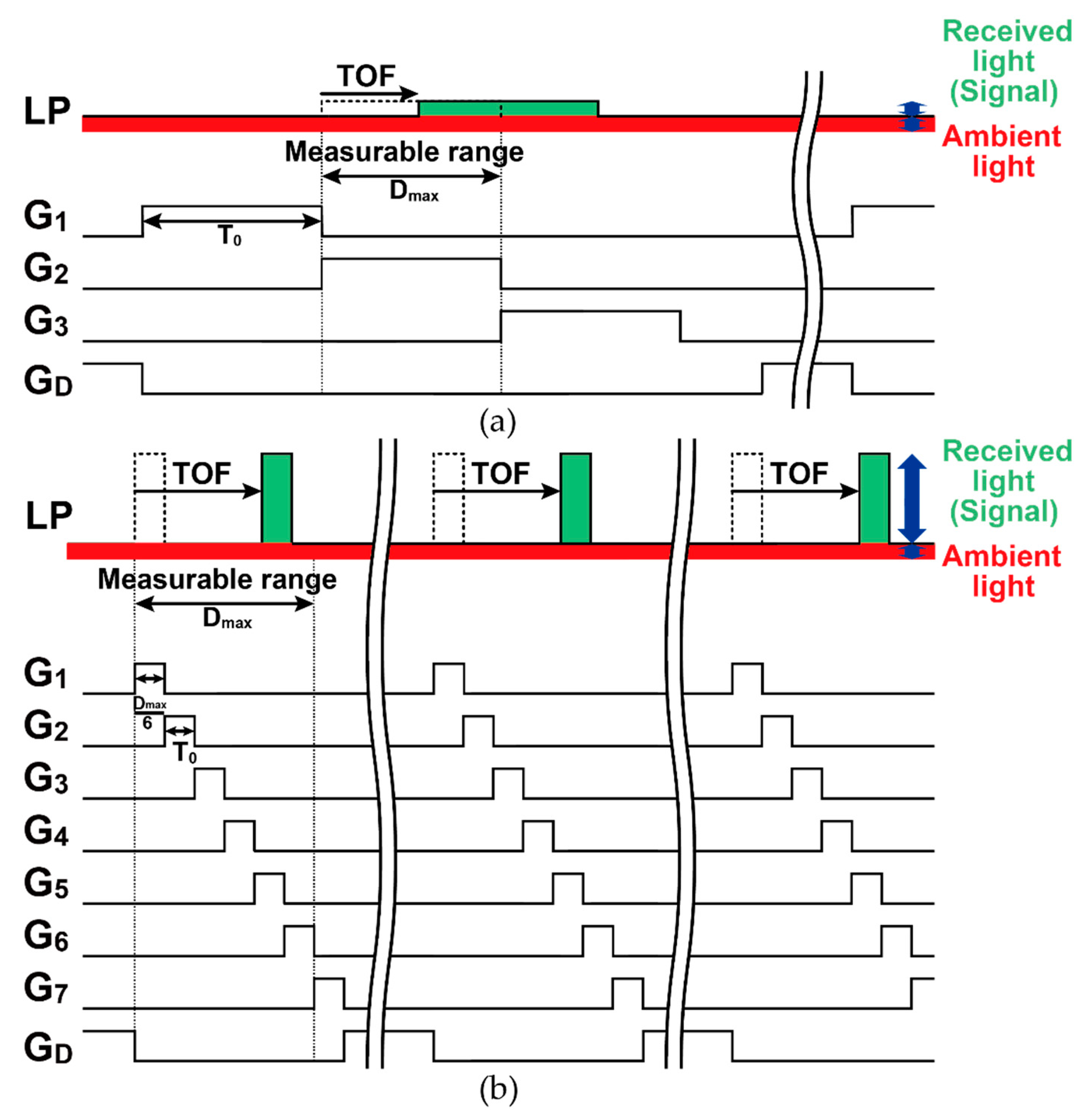

2.1. Operation Timing of Multiple-Tap Lock-In-Pixel TOF Imagers

2.2. Depth-Adaptive Time-Gating-Number Assignment for SP-TOF Measurements

2.3. Distance Calculation Algorithm

3. Design of an 8-Tap Lock-In Pixel Image Sensor for SP-TOF Measurements

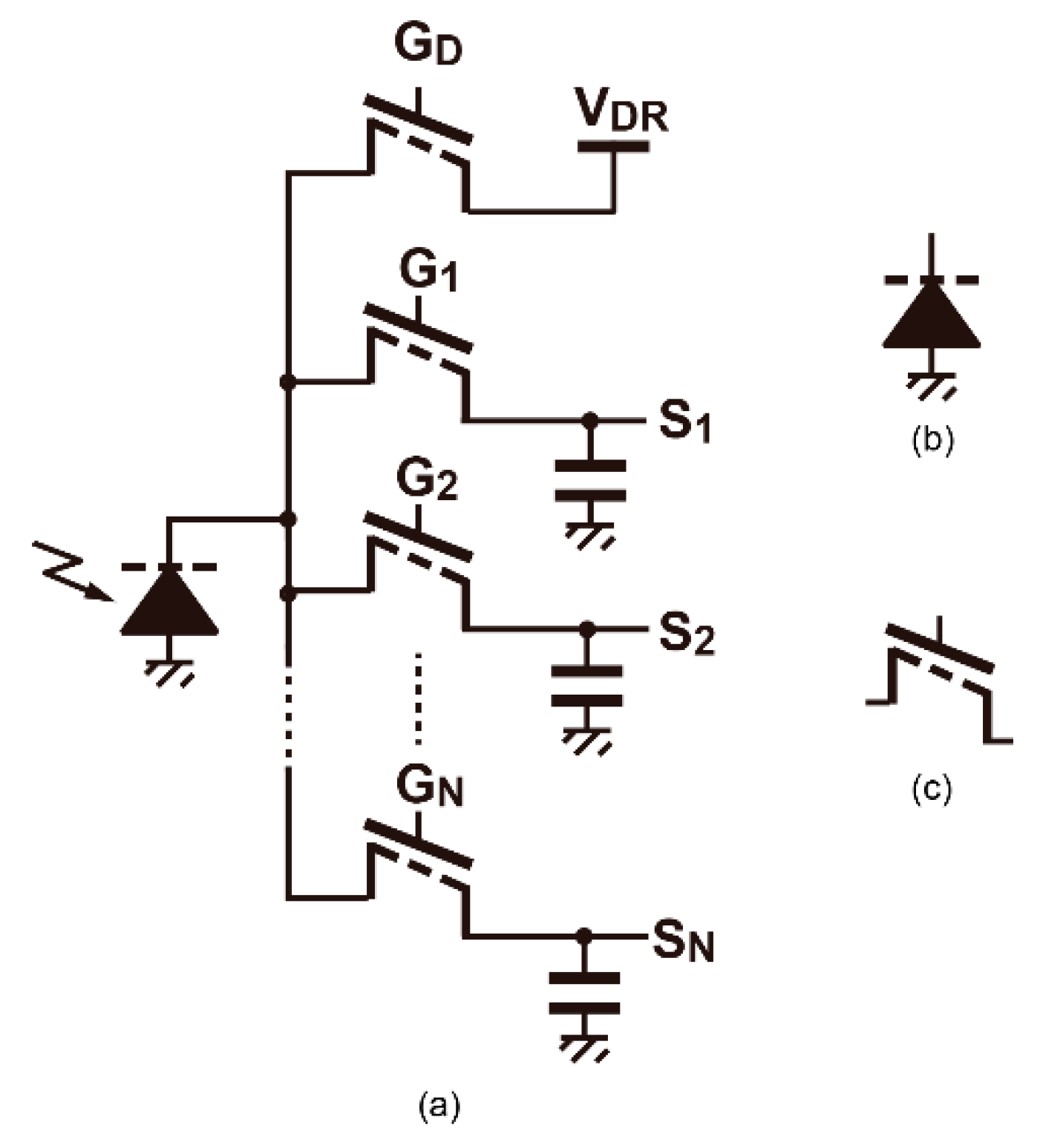

3.1. Pixel Structure

3.2. Pixel Circuits and Readout Operations

4. Implementation and Experimental Results

4.1. Implemented TOF Imager Chip

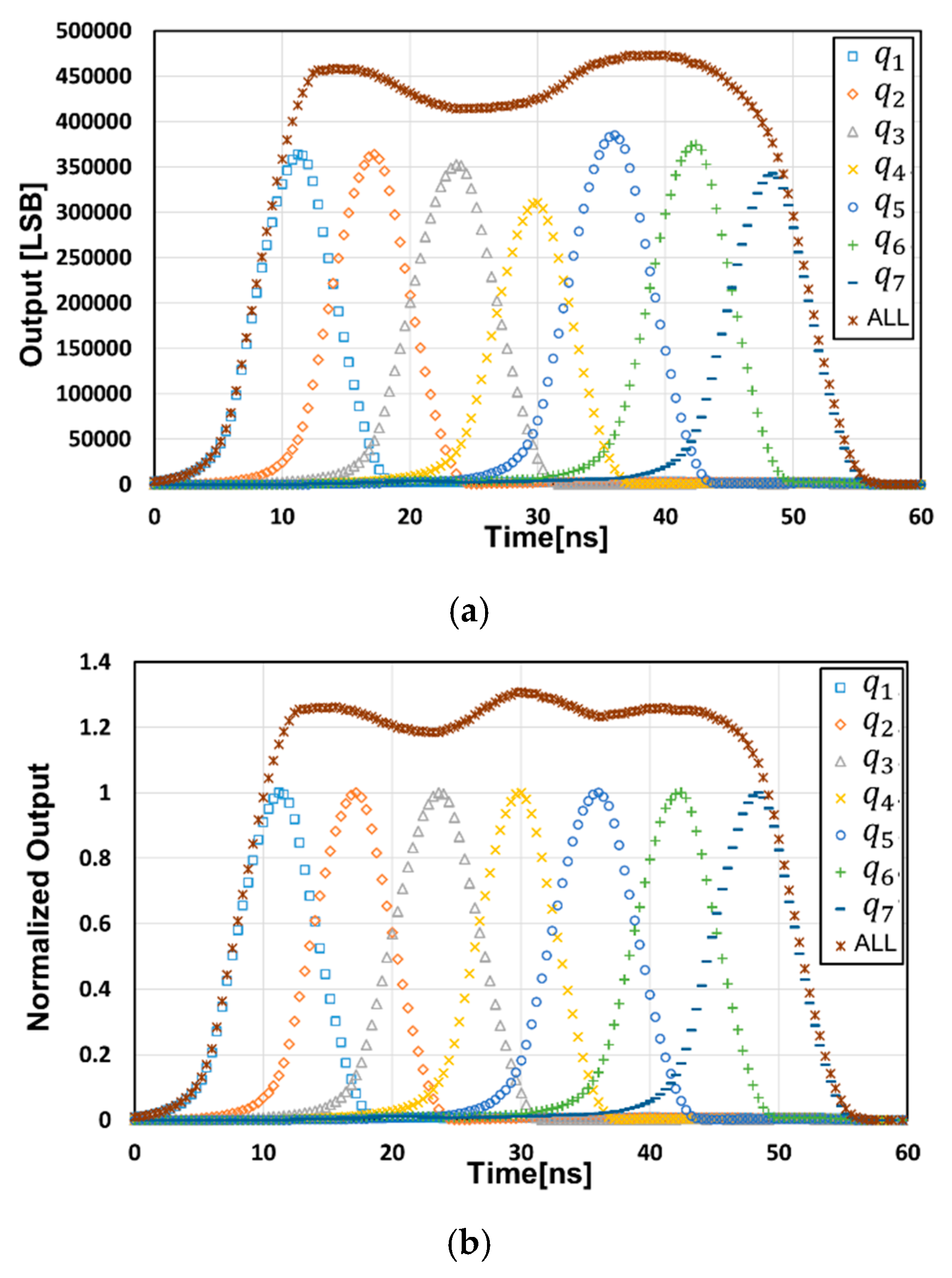

4.2. Charge Modulation Characteristics

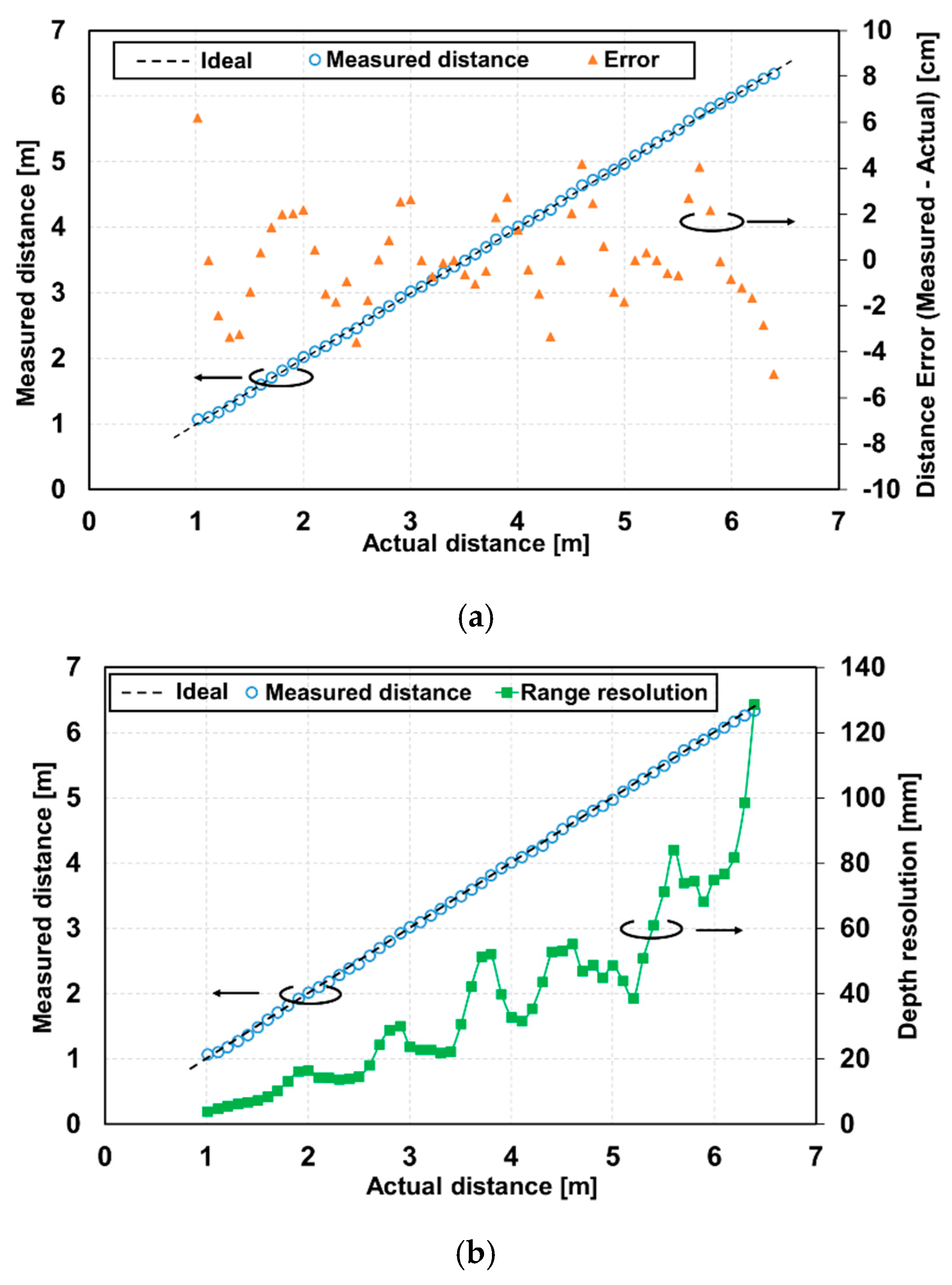

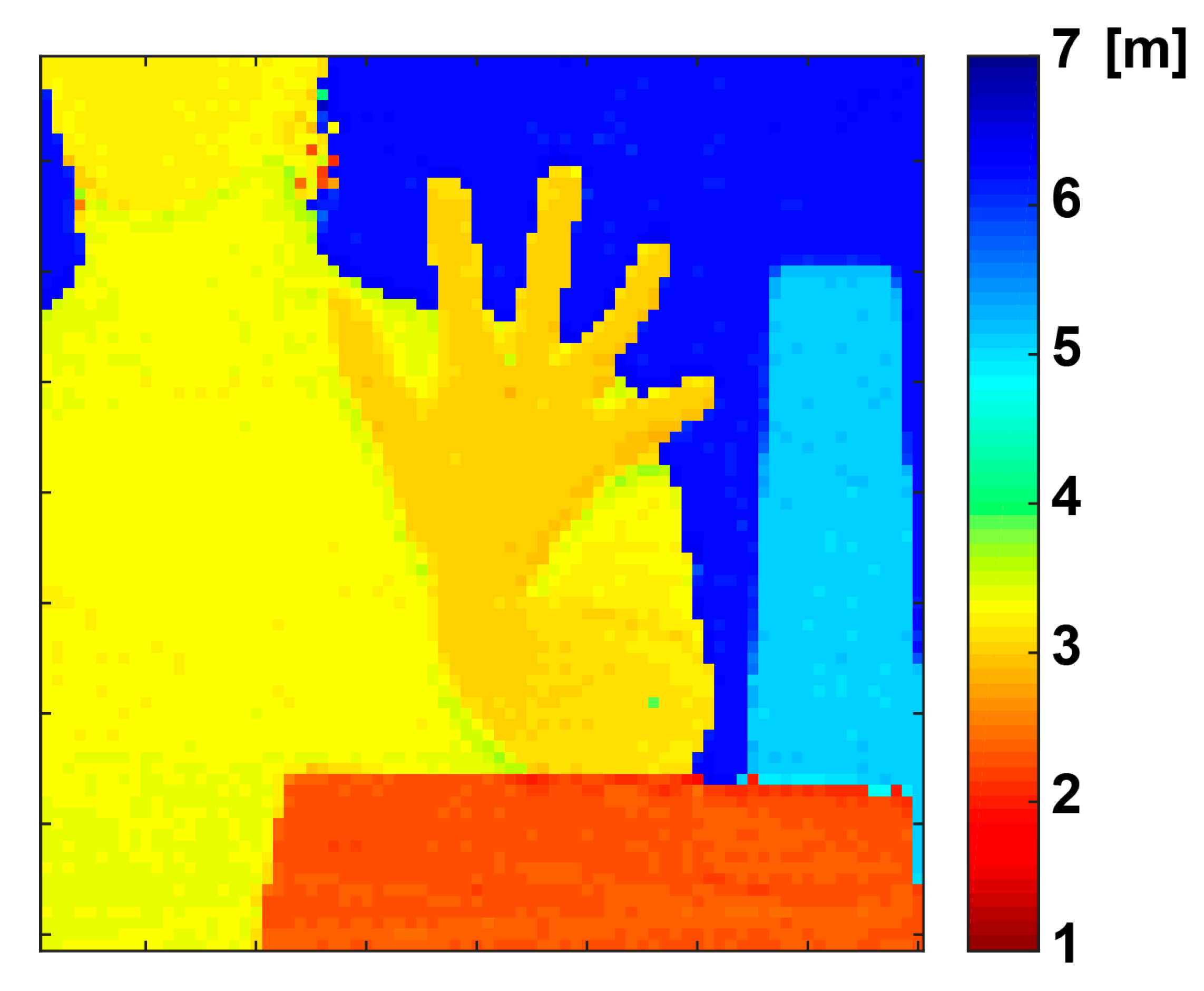

4.3. Distance Measurements

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Spirig, T.; Seitz, P.; Vietze, O.; Heitger, F. The Lock-In CCD-Two-Dimensional Synchronous Detection of Light. IEEE J. Quantum Electron. 1995, 31, 1705–1708. [Google Scholar] [CrossRef]

- Spirig, T.; Marley, M.; Seitz, P. The multitap lock-In CCD with offset subtraction. IEEE Trans. Electron Devices 1997, 44, 1643–1647. [Google Scholar] [CrossRef]

- Lange, R.; Seitz, P. Solid-state time-of-flight range camera. IEEE J. Quantum Electron. 2001, 37, 390–397. [Google Scholar] [CrossRef]

- Bamji, C.S.; O’Connor, P.; Elkhatib, T.; Mehta, S.; Thompson, B.; Prather, L.A.; Snow, D.; Akkaya, O.C.; Daniel, A.; Payne, A.D.; et al. A 0.13 μm CMOS System-on-Chip for a 512 × 424 Time-of-Flight Image Sensor with Multi-Frequency Photo-Demodulation up to130 MHz and 2GS/s ADC. IEEE J. Solid-State Circuits 2015, 50, 303–319. [Google Scholar] [CrossRef]

- Stoppa, D.; Massari, N.; Pancheri, L.; Malfatti, M.; Perenzoni, M.; Gonzo, L. A Range Image Sensor Based on 10-μm Lock-In Pixels in 0.18-μm CMOS Imaging Technology. IEEE J. Solid-State Circuits 2011, 46, 248–258. [Google Scholar] [CrossRef]

- Kim, S.-J.; Kim, J.D.K.; Kang, B.; Lee, K. A CMOS Image Sensor Based on Unified Pixel Architecture with Time-Division Multiplexing Scheme for Color and Depth Image Acquisition. IEEE J. Solid-State Circuits 2011, 46, 248–258. [Google Scholar] [CrossRef]

- Bamji, C.S.; Mehta, S.; Thompson, B.; Elkhatib, T.; Wurster, S.; Akkaya, O.; Payne, A.; Godbaz, J.; Fenton, M.; Rajasekaran, V.; et al. IMpixel 65nm BSI 320MHz demodulated TOF image sensor with 3um global shutter pixels and analog binning. In Proceedings of the 2018 IEEE International Solid—State Circuits Conference—(ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 94–96. [Google Scholar]

- Kato, Y.; Sano, T.; Moriyama, Y.; Maeda, S.; Yamazaki, T.; Nose, A.; Shina, K.; Yasu, Y.; Tempel, W.; Ercan, A.; et al. 320 × 240 back-illuminated 10um CAPD pixels for high speed modulation Time-of-Flight CMOS image sensor. In Proceedings of the 2017 Symposium on VLSI Circuits, Kyoto, Japan, 5–8 June 2017; pp. 288–289. [Google Scholar]

- Keel, M.; Jin, Y.; Kim, Y.; Kim, D.; Kim, Y.; Bae, M.; Chung, B.; Son, S.; Kim, H.; An, T.; et al. A 640 × 480 indirect time-of-flight CMOS image sensor with 4-tap 7μm global-shutter pixel and fixed-pattern phase noise self-compensation scheme. In Proceedings of the 2019 Symposium on VLSI Circuits, Kyoto, Japan, 9–14 June 2019; pp. 258–259. [Google Scholar]

- Kawahito, S.; Halin, I.A.; Ushinaga, T.; Sawada, T.; Homma, M.; Maeda, Y. A CMOS Time-of-Flight Range Image Sensor with Gates-on-Field-Oxide Structure. IEEE Sens. J. 2007, 7, 1578–1586. [Google Scholar] [CrossRef]

- Sawada, T.; Kawahito, S.; Nakayama, M.; Ito, K.; Halin, I.A.; Homma, M.; Ushinaga, T.; Maeda, Y. A TOF range image sensor with an ambient light charge drain and small duty-cycle light pulse. In Proceedings of the 2007 International Image Sensor Workshop, Ogunquit, ME, USA, 6–10 June 2007; pp. 254–257. [Google Scholar]

- Spickermann, A.; Durini, D.; Suss, A.; Ulfig, W.; Brockherde, W.; Hosticka, B.J.; Schwope, S.; Grabmaier, A. CMOS 3D image sensor based on pulse modulated time-of-flight principle and intrinsic lateral drift-field photodiode pixel. In Proceedings of the 2011 Proceedings of the ESSCIRC (ESSCIRC), Helsinki, Finland, 12–16 September 2011; pp. 111–114. [Google Scholar]

- Han, S.M.; Takasawa, T.; Yasutomi, K.; Aoyama, S.; Kagawa, K.; Kawahito, S. A time-of-flight range image sensor with background cancelling lock-in pixel based on lateral electric field charge modulation. IEEE J. Electron Devices Soc. 2015, 3, 267–275. [Google Scholar] [CrossRef]

- Lee, S.; Yasutomi, K.; Morita, M.; Kawanishi, H.; Kawahito, S. A Time-of-Flight Range Sensor Using Four-Tap Lock-In Pixels with High near Infrared Sensitivity for LiDAR Application. Sensors 2020, 20, 116. [Google Scholar] [CrossRef] [PubMed]

- Kondo, K.; Yasutomi, K.; Yamada, K.; Komazawa, A.; Handa, Y.; Okura, Y.; Michiba, T.; Aoyama, S.; Kawahito, S. A Built-in Drift-field PD Based 4-tap Lock-in Pixel for Time-of-Flight CMOS Range Image Sensors. In Proceedings of the Extended Abstracts of the 2018 International Conference on Solid State Devices and Materials, Tokyo, Japan, 9–13 September 2018; pp. 601–602. [Google Scholar]

- Sawada, T.; Ito, K.; Nakayama, M.; Kawahito, S. A range-shift technique for TOF range image sensor. IEEJ Trans. Sens. Micromachines 2009, 129, 421–425. [Google Scholar] [CrossRef]

- Shirakawa, Y.; Seo, M.W.; Yasutomi, K.; Kagawa, K.; Teranishi, N.; Kawahito, S. Design of an 8-tap CMOS lock-in pixel with lateral electric field charge modulator for highly time-resolved imaging. In Silicon Photonics XII; SPIE: San Francisco, CA, USA, 2017. [Google Scholar]

- Shirakawa, Y.; Yasutomi, K.; Kagawa, K.; Aoyama, S.; Kawahito, S. An 8-tap CMOS Lock-in Pixel Image Sensor for Short-Pulse Time-of-Flight Measurements. In Proceedings of the International Image Sensor Workshop (IISW2019), Snowbird, UT, USA, 23–27 June 2019; pp. 187–190. [Google Scholar]

- Kawahito, S.; Baek, G.; Li, Z.; Han, S.M.; Seo, M.W.; Yasutomi, K.; Kagawa, K. CMOS lock-in pixel image sensors with lateral electric field control for time-resolved imaging. In Proceedings of the International Image Sensor Workshop (IISW), Snowbird, UT, USA, 12–16 June 2013; pp. 361–364. [Google Scholar]

- Seo, M.W.; Kagawa, K.; Yasutomi, K.; Kawata, Y.; Teranishi, N.; Li, Z.; Halin, I.A.; Kawahito, S. A 10 ps Time-resolution CMOS image sensor with two-tap true-CDS lock-in pixels for fluorescence lifetime imaging. IEEE J. Solid-State Circuits 2016, 51, 141–154. [Google Scholar]

- Seo, M.W.; Shirakawa, Y.; Kawata, Y.; Kagawa, K.; Yasutomi, K.; Kawahito, S. A time-resolved four-tap lock-in pixel CMOS image sensor for real-time fluorescence lifetime imaging microscopy. IEEE J. Solid-State Circuits 2018, 53, 2319–2330. [Google Scholar] [CrossRef]

- Seo, M.W.; Suh, S.H.; Iida, T.; Takasawa, T.; Isobe, K.; Watanabe, T.; Itoh, S.; Yasutomi, K.; Kawahito, S. A low-noise high intrascene dynamic range CMOS image sensor with a 13 to 19b variable-resolution column-parallel folding-integration/cyclic ADC. IEEE J. Solid-State Circuits 2012, 47, 272–283. [Google Scholar] [CrossRef]

| Parameter | Value |

|---|---|

| Technology | 0.11-μm 1P4M CIS process |

| # of pixels | 134 (H) 128(V) |

| Pixel size | 22.4 μm 22.4 μm |

| Chip size | 5874 μm 9342 μm |

| ADC resolution | 19 bit |

| Readout time | 51.84 ms |

| Conversion gain | 69.5 |

| Full well capacity | 5600 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shirakawa, Y.; Yasutomi, K.; Kagawa, K.; Aoyama, S.; Kawahito, S. An 8-Tap CMOS Lock-In Pixel Image Sensor for Short-Pulse Time-of-Flight Measurements. Sensors 2020, 20, 1040. https://doi.org/10.3390/s20041040

Shirakawa Y, Yasutomi K, Kagawa K, Aoyama S, Kawahito S. An 8-Tap CMOS Lock-In Pixel Image Sensor for Short-Pulse Time-of-Flight Measurements. Sensors. 2020; 20(4):1040. https://doi.org/10.3390/s20041040

Chicago/Turabian StyleShirakawa, Yuya, Keita Yasutomi, Keiichiro Kagawa, Satoshi Aoyama, and Shoji Kawahito. 2020. "An 8-Tap CMOS Lock-In Pixel Image Sensor for Short-Pulse Time-of-Flight Measurements" Sensors 20, no. 4: 1040. https://doi.org/10.3390/s20041040

APA StyleShirakawa, Y., Yasutomi, K., Kagawa, K., Aoyama, S., & Kawahito, S. (2020). An 8-Tap CMOS Lock-In Pixel Image Sensor for Short-Pulse Time-of-Flight Measurements. Sensors, 20(4), 1040. https://doi.org/10.3390/s20041040