1. Introduction

Computer-aided design (CAD) tools are often used to facilitate electronic circuit design before implementation. They are developed to achieve numerous goals such as the reuse of design components, ease of design modification, automatic generation of designs, and verification of designs against specifications and design rules. The ultimate purpose is to derive predictions of circuit behavior that are highly similar or even identical to the real physical behavior of the circuit after implementation. For analog or mixed-signal integrated circuit (IC) designs, electronic design automation (EDA) tools such as HSPICE are widely used to accurately simulate the ICs for performance evaluations. This transistor-level simulator can derive circuit information precisely, enabling designers to predict the functionality, power dissipation, timing, and reliability of their designs. Although this class of transistor-level simulators is powerful for evaluating circuits for various performance metrics, the simulation process is time-consuming. Generally, this would require at least several hours or possibly several days, depending on the simulation settings. To overcome this problem, at the early design stage of numerous ICs, such as phase locked loops (PLLs), frequency synthesizers, and delta-sigma modulators, behavioral models have been built and evaluated using SIMULINK; some simulation precision was sacrificed for the rapid calculation of rough results [

1,

2,

3,

4,

5,

6,

7,

8]. Researchers developed so-called “behavioral simulation techniques”, which trade accuracy for speed; the design procedure can thus be accelerated by applying these high-speed simulation techniques. Typically, circuit trimming techniques are further applied during the design of physical device models to mitigate the gap between behavioral and transistor-level simulations. However, the required time for the trimming process is unpredictable.

In numerous industrial, home, and office electronic devices, smart temperature sensors (STSs) are increasingly required to monitor and manage temperatures. Due to the demand for small, low-dissipation devices, CMOS STSs are highly competitive and have strong appeal. Several CMOS time-domain STSs (TDSTSs) have been developed over the past 10 years [

9,

10,

11,

12,

13,

14,

15,

16,

17,

18,

19,

20]. Compared with CMOS voltage-domain STSs, which have highly favorable accuracy for voltage and process variations [

21,

22,

23,

24], CMOS TDSTSs possess the advantages of lower cost and lower circuit complexity. Thus, several TDSTSs have been reported [

10,

11,

12,

13,

14,

15,

16,

17,

18,

19,

20]. HSPICE simulations are precise but extremely time-consuming, particularly because STS simulations must simulate multiple temperature points to evaluate performance. Thus, researchers must develop a time-efficient and accurate simulation tool that can effectively derive valid temperature information regarding TDSTSs. However, to the best of our knowledge, no behavioral simulator for TDSTSs meets the standards of simulators for PLLs, frequency synthesizers, or delta-sigma modulators. Beyond behavioral simulation, accurate predictions are also desirable in transistor-level simulations of TDSTS designs. With such predictions, designers can modify a TDSTS at the early design stage without several rounds of time-consuming HSPICE simulations.

The widely used SIMULINK platform provides time-efficient behavioral simulations. Thus, this study proposes a high-speed SIMULINK-based behavioral simulator for TDSTSs. In this paper, we organize simple and accurate equations describing TDSTS into a temperature-dependent model (TDM) and derive temperature-sensing models of a CMOS NOT gate by using HSPICE, which has a very short simulation time. With the TDM and the derived models, the proposed simulator achieved rapid and accurate simulation. The remainder of this paper is arranged as follows:

Section 2 introduces the TDM of the TDSTSs, and the building blocks of the proposed SIMULINK simulator are introduced in detail in

Section 3. Subsequently,

Section 4 presents the experimental results, which validate the proposed technique, and finally,

Section 5 concludes this study.

2. TDM for the TDSTSs

In a TDSTS, an inverter-based delay line or oscillator is typically adopted to sense temperature because a simple CMOS NOT gate can act as an effective proportional to absolute temperature (PTAT) sensor that generates a temperature-dependent delay time

tNOT(

T) [

9,

12,

13,

14,

15,

16,

17], which can be expressed as follows [

13,

17]:

where

μ0,

T,

T0,

Vth,

W/

L, and

CL are the reference carrier mobility, operation temperature, reference temperature, threshold voltage, effective aspect ratio of transistors, and loading capacitance of the NOT gates, respectively. Without considering the effect of voltage variation, the summed parameter

γ can be regarded as a process-dependent factor that is nearly independent of temperature. The parameter −

km is considered to be temperature independent; this parameter determines the thermal characteristics of the CMOS NOT gate. For example, its value ranges from −1.2 to −2.0 for a 0.35-µm CMOS process and, thus, the

tNOT(

T) changes linearly with the temperature [

17].

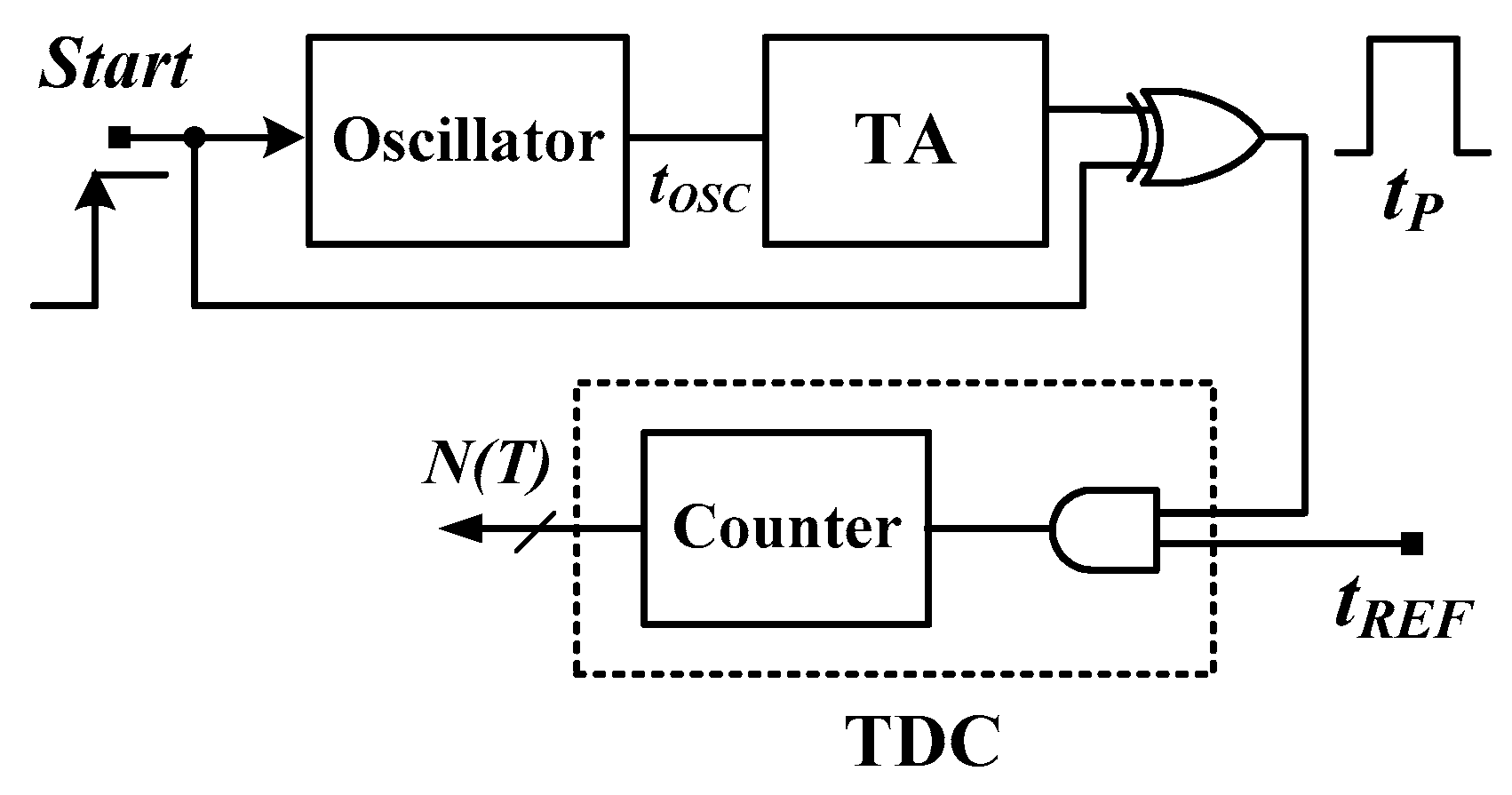

Figure 1 shows a block diagram of an all-digital CMOS oscillator-based TDSTS [

12]. An oscillator consists of an odd number (

k) stages of NOT gates that generate a PTAT period width

tOSC(

T). To achieve a satisfactory temperature resolution (

R), a time amplifier (TA) is used to amplify the

tOSC(

T) with a time gain

n. With a simple XOR gate, a sufficiently wide PTAT pulse

tP(

T) is generated. A reference clock with a stable period width (

tREF) is used to convert the

tP(

T) into a corresponding digital code

N(

T) by using an AND gate and output counter. The

N(

T) of the simple sensor can be formulated as follows [

13,

17]:

Since (in theory)

n,

k, and

tREF are ideally temperature- and process-insensitive, the thermal characteristics of

N(

T) are ideally identical to those of

tNOT(

T). Equation (2) is a simple, but accurate, equation that describes the temperature behavior of the TDSTS, which has been verified in previous studies [

12,

13,

17]. If the models (i.e.,

γ ×

T−km for process and temperature variation) of a single CMOS NOT gate can be derived precisely, the sensor code

N(

T) can be attained by computing Equation (2) such that the performance can be roughly evaluated and the design procedure can be simplified. Various crucial specifications, such as the limits of accuracy and the resolution, can be estimated quickly.

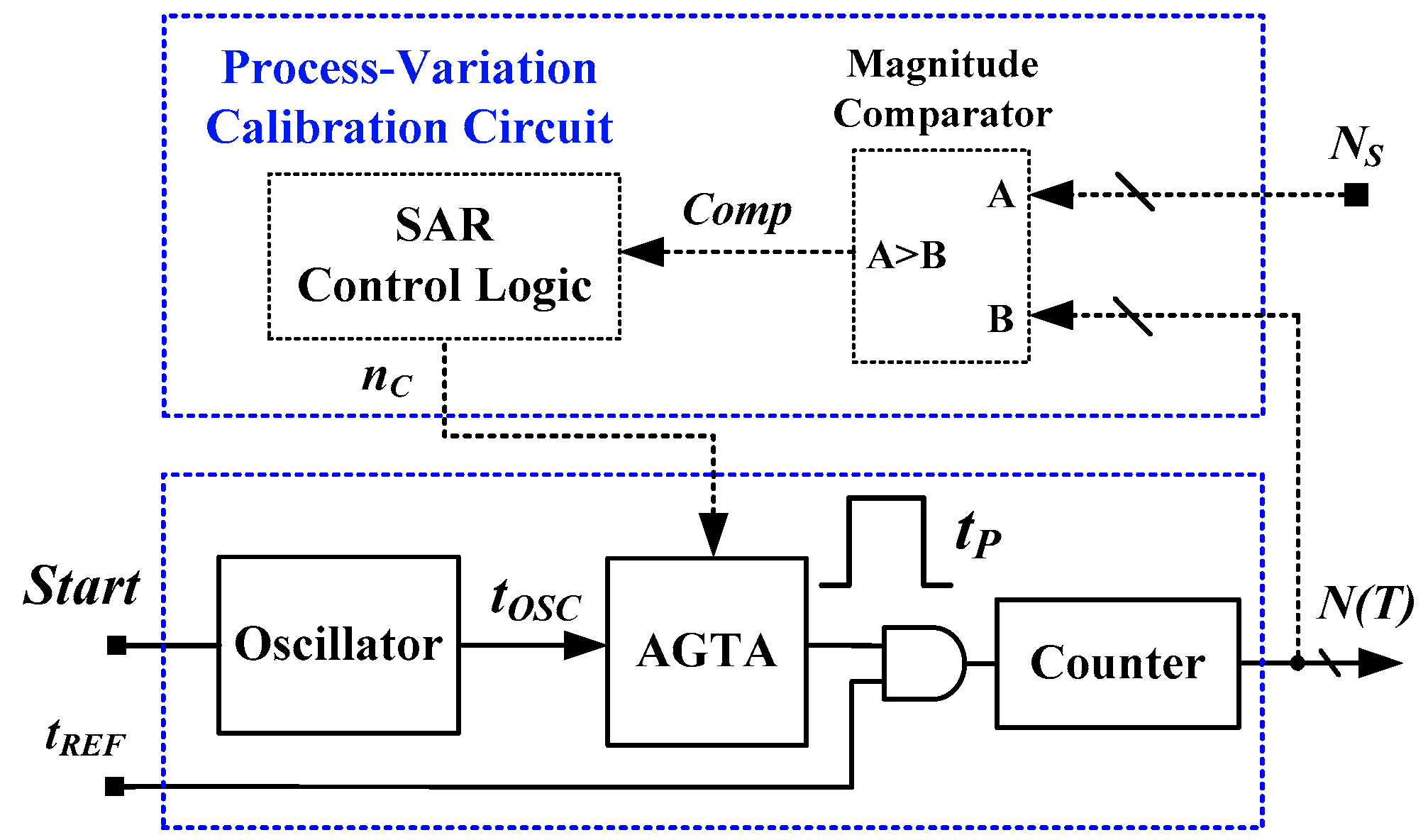

Figure 2 shows a block diagram of an all-digital TDSTS with one-point calibration support that incorporates process-variation calibration [

13]. In contrast to the simple TDSTS shown in

Figure 1, the adjustable-gain time amplifier (AGTA) shown in

Figure 2 is modified from a standard time amplifier to realize the variable time gain

nC for calibration. The calibration circuit is composed of a magnitude comparator and SAR (successive approximation register) control logic; this eliminates the influence of process variation (denoted as

i) to support one-point calibration. The calibration technique and detailed procedure were presented in [

13]. For one-point calibration, the calibrated code

NC,i(

TC) at the calibration temperature

TC can be adjusted to match the calibration value

NS. This calibration condition can be expressed as follows:

The oscillation period width of the

ith sensor on

TC (

tOSC,i(

TC)) is compensated dynamically by adjusting the corresponding

nC,i. The calibration result is presented as follows:

Finally, Equation (4) is substituted into Equation (2), and the

NC,i(

T) after the calibration can be expressed as:

In other words, with the calibration, the calibrated time gain

nC,i replaces the fixed

n in the uncalibrated sensor to generate the

NC,i(

T) of the calibrated sensor. The result of Equation (5) reveals that the process term

γ can be eliminated effectively, enabling the calibrated sensor to support one-point calibration. According to the two chosen values (

N(

T1) and

N(

T2)) and their temperature interval (

T1 −

T2), the sensor resolution

R can be determined as follows:

Furthermore, the conversion time can be estimated as the product of the digital value at the highest temperature and

tREF (i.e.,

N(

T2) ×

tREF) without considering the delay time of the devices in the sensor and, thus, the ideally lowest conversion rate (

CR) is determined as:

The transistor-level of the CMOS TDSTSs can be simulated using HSPICE to derive the uncalibrated codes Ni(T) accurately with process and temperature variations (i.e., Equation (2)). With the calibration, the calibrated nC,i (i.e., Equation (4)) can be simulated to further derive the calibrated codes NC,i(T) (i.e., Equation (5)). The HSPICE simulation is precise but extremely time-consuming. To reduce the simulation time substantially, Equations (1)–(5) were used in the proposed simulator as a TDM for behavioral simulation.

3. Proposed Behavioral Simulator Using SIMULINK

According to Equations (1)–(5) of the TDM, the

tNOT(

T) is the most crucial item because it is the only quantity related to the temperature and process. This feature can be used to develop a time-efficient behavioral simulator for TDSTSs in order to estimate behavior without using HSPICE, significantly reducing the simulation time. Another vital issue is that the simulator is concise because its equations are simple and linear. The equations have been verified to function effectively [

12,

13,

14,

15,

16,

17], which is conducive to precise simulation.

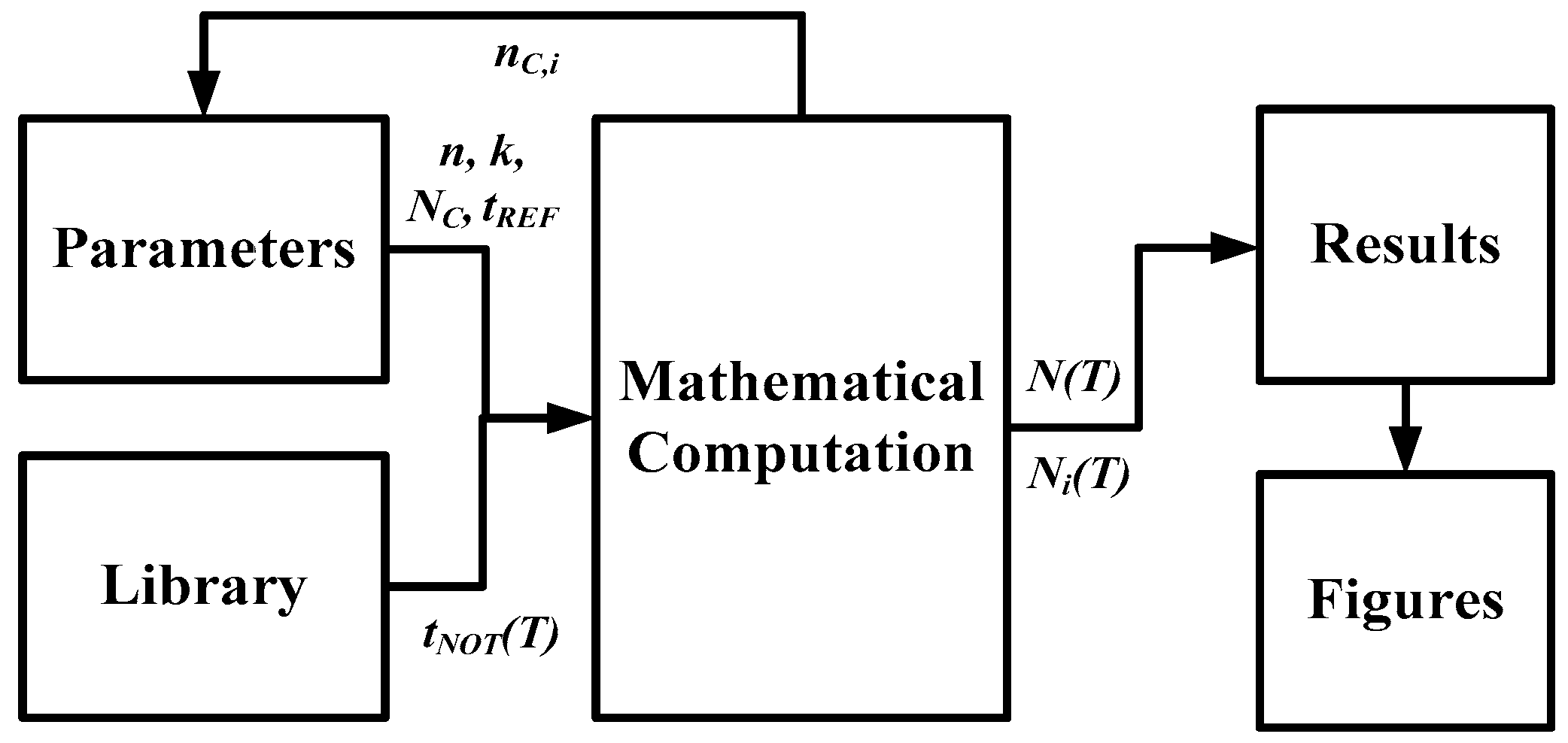

A conceptual block diagram of a concise simulation tool for a TDSTS is shown in

Figure 3. The designer selects the basic parameters (

n,

k,

tREF,

NC,

TC) and loads the models (

γ ×

T−km) from the library for mathematical computation; the system calculates the equations using the models and the input parameters. After the simulation results have been generated, the performance can be evaluated. Moreover, the figures for the results (

Ni(

T) and

NC,i(

T)) and the processed data (for example, the inaccuracy) can be directly displayed using a suitable program, which simplifies the operations and increases the functionality of the tool.

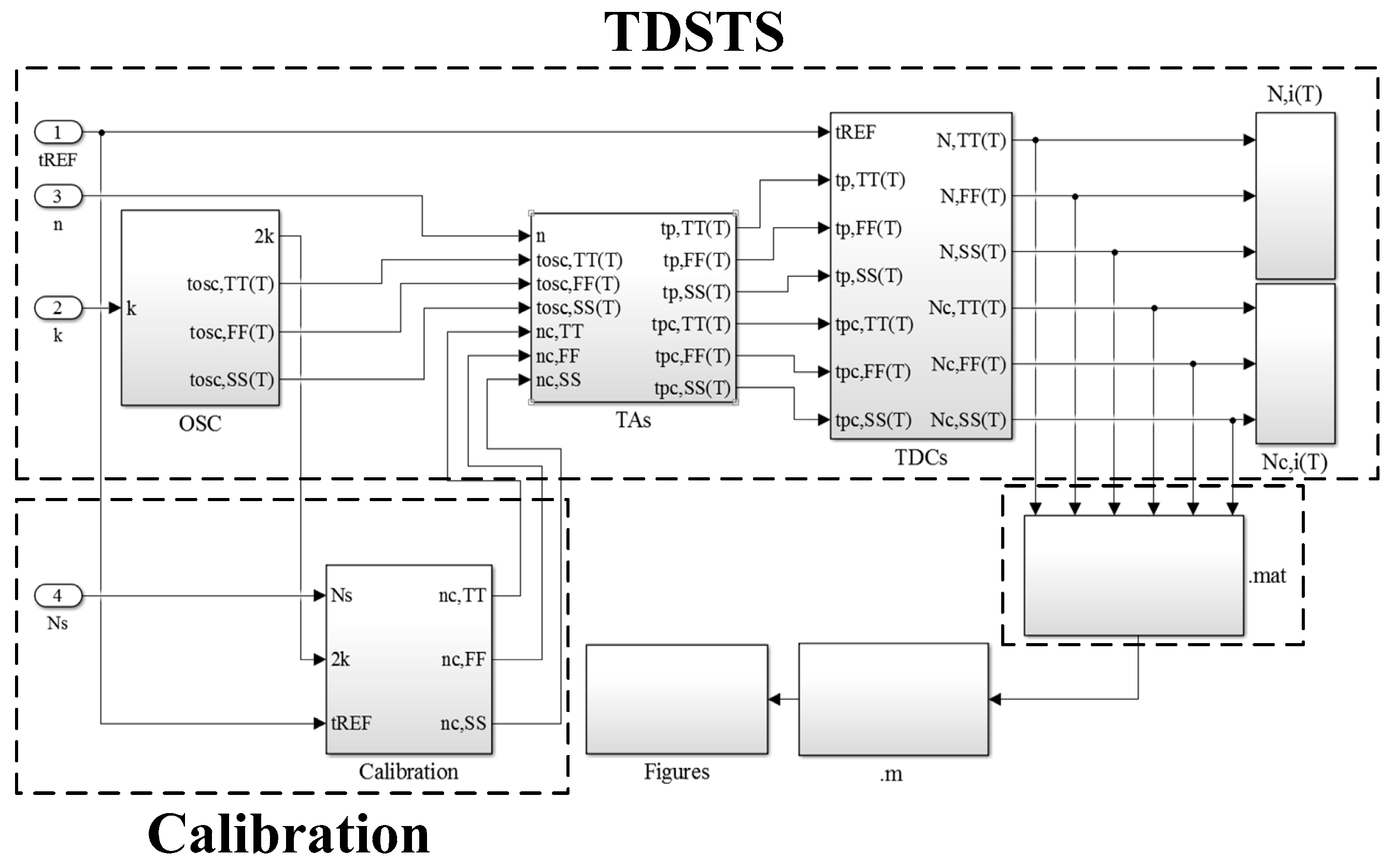

The objective of this study was to develop a concise and low-cost simulator for performing rapid and accurate TDSTS simulations. SIMULINK is a widely used behavioral simulation platform that is highly suitable for implementing the simulator. Implementation in the SIMULINK environment brings numerous advantages such as high construction flexibility, large computation capability, a user-friendly graphical interface, and extremely short computation time. The design presented in

Figure 3 can be elaborated with TDSTSs and process-variation calibration in the SIMULINK environment to yield the constructed block of the proposed simulator shown in

Figure 4. The block of the TDSTSs comprises a library that stores the temperature-sensing models of a single NOT gate derived from HSPICE simulations, and two sensors (without and with calibration) for estimating system performance. The block of the calibration is used to generate the calibrated time gain

nC,i for the sensor with calibration. Finally, the simulation results (

Ni(

T) and

NC,i(

T)) are stored in .mat files for figure generation with MATLAB. The software structure is concise and the defining equations are simple. Thus, a low-cost simulator for rapid performance evaluations can be constructed.

First, considering the uncalibrated sensor (i.e., the simple sensor without calibration), the input values of the parameters are k for determining the oscillation period width tOSC,i(T) (i denotes the three process corners: typical-typical (TT), fast-fast (FF), and slow-slow (SS)), n for amplifying the width to generate tP,i(T), and tREF for time-to-digital conversion. The results of Ni(T) are obtained using Equation (2) and the models of tNOT,i(T). Second, the process-variation calibration is activated by giving the value of NS on TC. Through Equation (3), the corresponding nC,i of the three process corners can be generated for the AGTA in the calibrated sensor. Then, the estimation of the calibrated sensor is performed. With the same tNOT,i(T), k, and tREF, the computation of Equation (5) generates the results of NC,i(T).

After the results have been generated, the data of Ni(T) and NC,i(T) are stored in a .mat file, which is loaded into a prewritten MATLAB file to estimate the sensor resolution R by using Equation (6), and to generate the figures that display the performance. In other words, the linearity and inaccuracy after data processing can be directly presented in the figures in a simple manner. This simplifies the figure generation procedure considerably.

3.1. Temperature-Sensing Model of a Single CMOS NOT Gate

In the SIMULINK platform, the blocks are described by the equations of the TDM, which express their outputs in terms of the input parameters and NOT gate models. Therefore, the precision of the behavioral simulation depends on how accurately those equations describe the actual condition of each building block and the precision of the captured model. The accurate equations are presented in previous subsections. This subsection introduces the temperature-sensing model of a NOT gate.

To build a library that stores the models for behavioral simulation, an oscillator composed of 21 stages of CMOS NOT gates (PMOS: W/L = 2/2 µm, NMOS: W/L = 1/2 µm) was simulated using HSPICE in a TSMC 0.35-µm CMOS process for process and temperature variations (TT, SS, and FF of the three process corners, ranging from 0 to 80 °C in 10 °C increments). The long MOS channel length was selected to facilitate the realization of a wider oscillation period width. An oscillator with relatively high stages was used to optimize the precision. Furthermore, the models of the single NOT gate were derived by averaging the period width and were stored in the library, as presented in

Table 1. This averaging data would be expected to dominate the precision of the proposed simulator. Thus, the numerical precision of the data for the captured models is expected to suffice. It is related to the least significant bit (LSB) time (i.e.,

tREF) and the value of 2 ×

k ×

n. For example, Equation (2) shows that when

tREF = 25 ns (i.e., 40 MHz) and 2 ×

n ×

k = 100,000, the precision needs to be in the order of tens of femtoseconds (fs) (i.e., 1/1000 in picoseconds (ps)). This is because when the data are amplified by 100,000, the amplified data of the LSB is near 10 ns at most, which is less than 25 ns (the LSB time). Equivalently, the non-ideal effect for the sensor code is less than 1 LSB and is practically irrelevant to the result. When it is necessary to estimate more results, the data for greater numbers of temperature points in a range wider than the commercial temperature range can be obtained in the same manner.

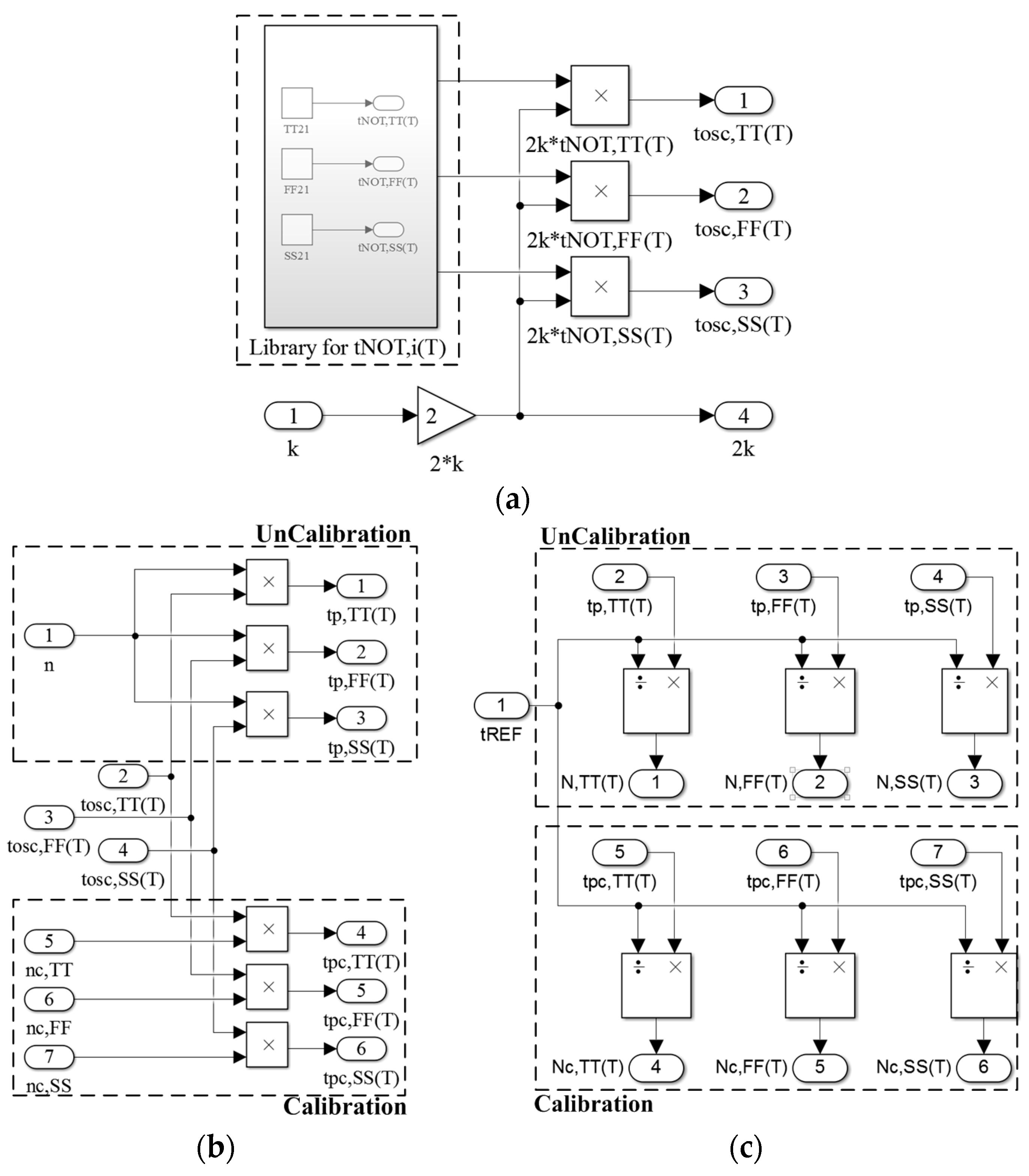

3.2. TDSTSs

Figure 5 presents the detailed construction of TDSTSs in the SIMULINK environment for (a) the block of the oscillator including the library; (b) the block of the TAs; and (c) the block of the TDCs. The sensor codes (

Ni(

T) and

NC,i(

T)) for the two sensors are generated by the two TAs and the corresponding TDCs. Their operation is totally identical except for

n and

nC,i. Although two sensors were designed in this simulator, the total simulation time was not increased considerably because the proposed simulator is concise and performed by using SIMULINK, which was a notable advantage of the SIMULINK platform.

As shown in

Figure 5a, by the product of 2 and

k and the captured models in the library, the

tOSC,i(

T) are generated and used in the two sensors. Simultaneously, the value of 2 ×

k is sent to the calibration block (next subsection). Next, when the

tOSC,i(

T) is amplified with

n or

nC,i generated from the calibration block, the

tP,i(

T) in the uncalibrated sensor and the

tPC,i(

T) in the calibrated sensor are produced, as presented in

Figure 5b.

Figure 5c presents the process generating

Ni(

T) or

NC,i(

T) by counting

tP,i(

T) or

tPC,i(

T), respectively, by using the

tREF. The three steps refer to Equations (2) and (5).

3.3. Process-Variation Calibration for the Three Process Corners

To evaluate the calibrated sensor, the calibrated time gain

nC,i (

nC,TT,

nC,FF, and

nC,SS) must be derived for time amplification. The calibration compensates for the process variation of the oscillator on

TC. Thus, only the model on

TC (i.e.,

tNOT,i(

TC)) is used in this scheme. The constructed scheme is illustrated in

Figure 6. The value

NS on

TC is selected to perform one-point calibration. The

tOSC,i(

TC) are generated using the value of 2 ×

k (from the block of the oscillator) and the model of

tNOT,i(

TC). With the product of

NS and

tREF, the corresponding

nC,i can be determined using Equation (4) and is used in the calibrated sensor. The higher the value of

NS is, the higher the value of

nC and the sensor resolution are.

3.4. Figure Generation for Performance Evaluation

Generally, after a simulation has generated results, a suitable program processes the output into a user-friendly format with figures that present the required functions (e.g., the linearity and the inaccuracy). To simplify the procedure, the simulated data of the proposed simulator are stored in .mat format during simulation and are automatically loaded into a prewritten .m file. MATLAB processes the data in the .m file and generates the required figures. For example, the linearity of the simulation results and the corresponding inaccuracy, including two-point calibration for the uncalibrated sensor and one-point calibration for the calibrated sensor, are often presented in figures to illustrate system performance. Since this simulator features an .m file, the figures of the required functions for the two sensors can be simultaneously exhibited in a remarkably simple manner. Designers can easily see whether the presented performance levels satisfy the specifications.

4. Experimental Results

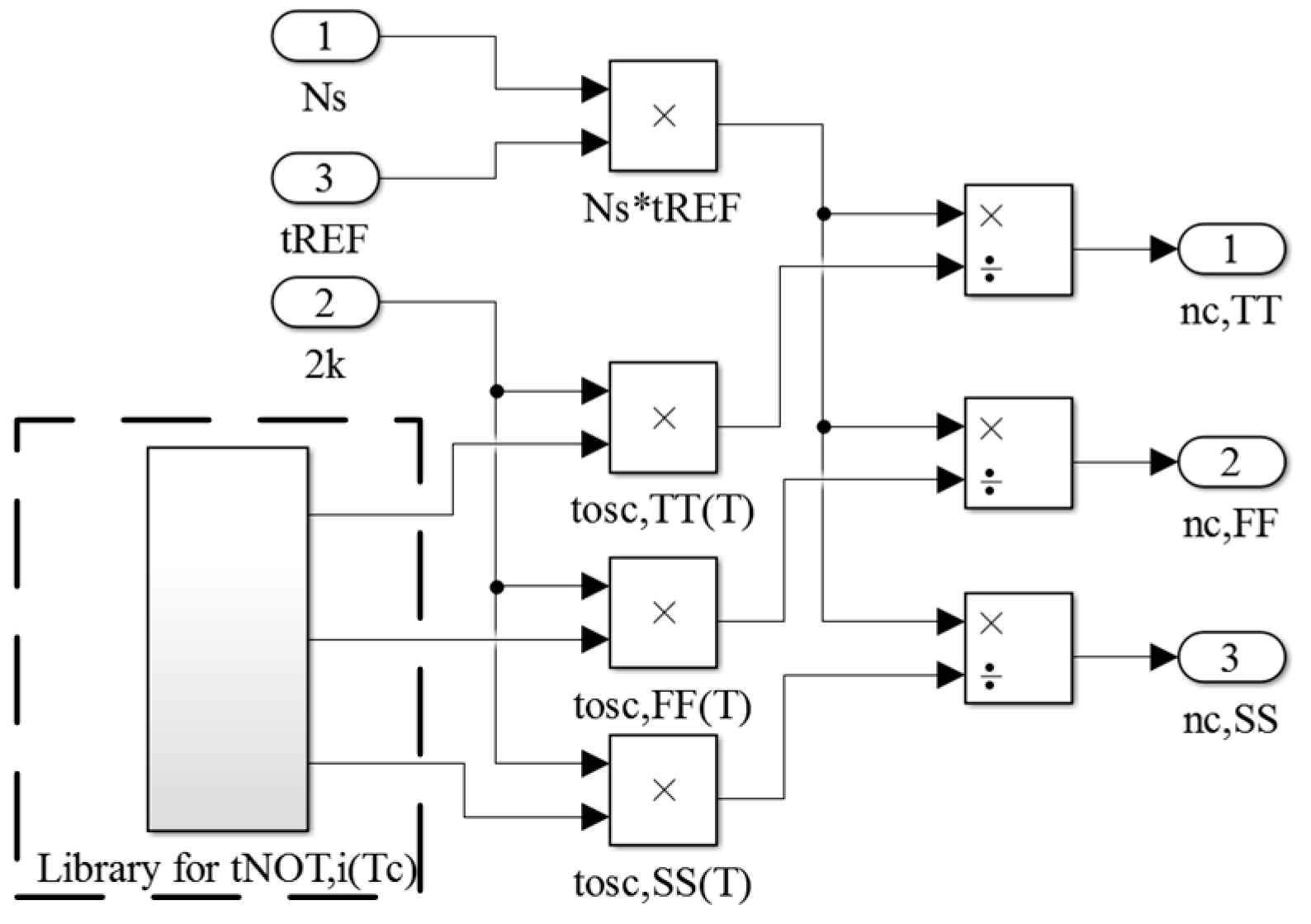

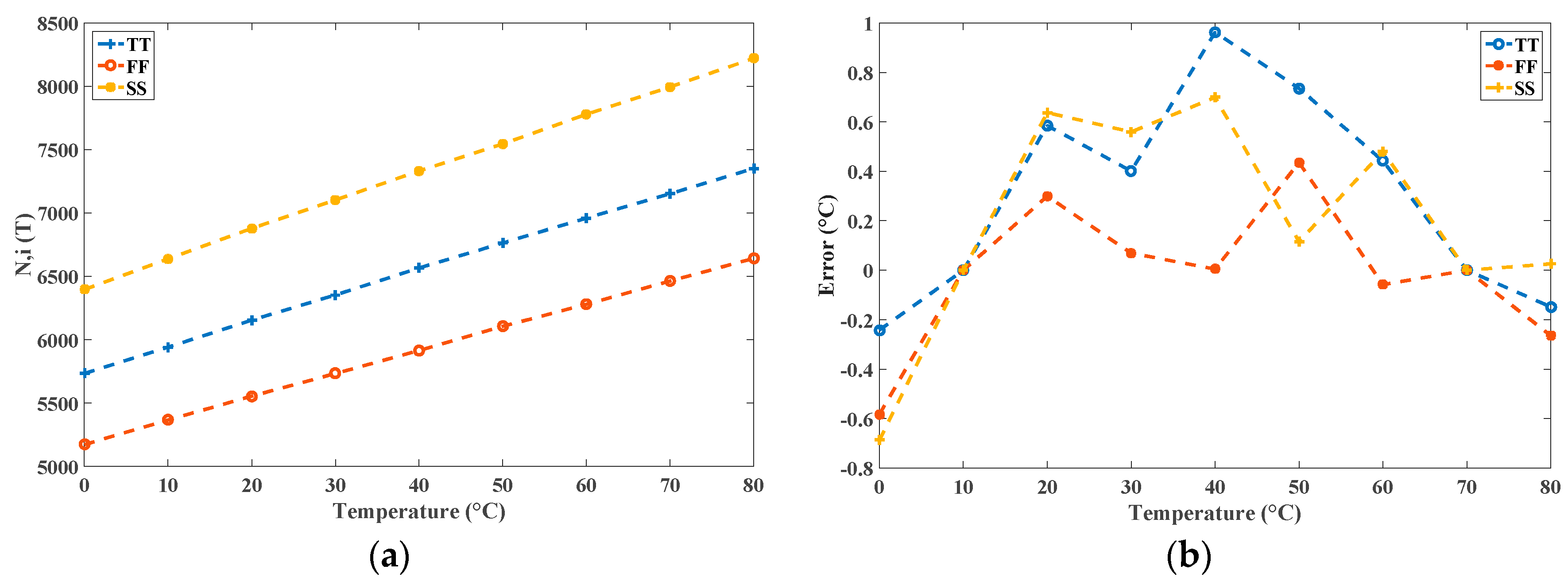

To validate the behavioral simulator, behavioral and transistor-level simulations were performed with the proposed simulator and HSPICE, respectively. A sufficiently wide tREF can effectively reduce the influence of the delay mismatch and delay variation along various signal paths, thereby improving the precision of the simulation. In addition, a low operational frequency can mitigate high power consumption. Thus, the design should specify relatively wide values of tREF and tOSC(T). For simplicity, tREF = 25 ns is given for all situations, and the TC is set to 40 °C (i.e., the median of 0–80 °C).

In the uncalibrated sensor, the value

k = 21 was set to achieve a relatively wide oscillation period width

tOSC(

T) (for example, 2 × 21 ×

tNOT,TT (40 °C) = 32.832 ns) for low power consumption. In additional, the fixed time gain

n = 5000 was set for a satisfactory

R. With the transistor-level simulations using HSPICE, the simulation time for the three process corners in 10 °C steps from 0 °C to 80 °C was around 27 hours to derive the results. By the contrast, under the same simulation setting, the total simulation time of the proposed system was only a few seconds, which saved a notable amount of time. After the proposed simulation generated the outcome of

Ni(

T), it was stored in

Ni(

T) .mat; the graphical output is presented in

Figure 7. MATLAB loaded the .m file, which contained the data of

Ni(

T), and produced figures depicting the linearity and the inaccuracies after two-point calibration, as shown in

Figure 8. Furthermore, the figure generation procedure was simplified considerably. Simultaneously, the proposed simulator calculated the

R values for the three process corners. For example, in TT mode,

N(0 °C) = 5735 and

N(80 °C) = 7352 were chosen with a temperature interval of 80 °C; the

R was calculated as approximately 0.05 °C. Moreover, the estimated conversion time at 80 °C can be calculated as 183.8 µs (7352 × 25 ns) and the lowest

CR is determined as 5.44 k samples/s in this TT mode. These operations demonstrated the functionality of the proposed simulator.

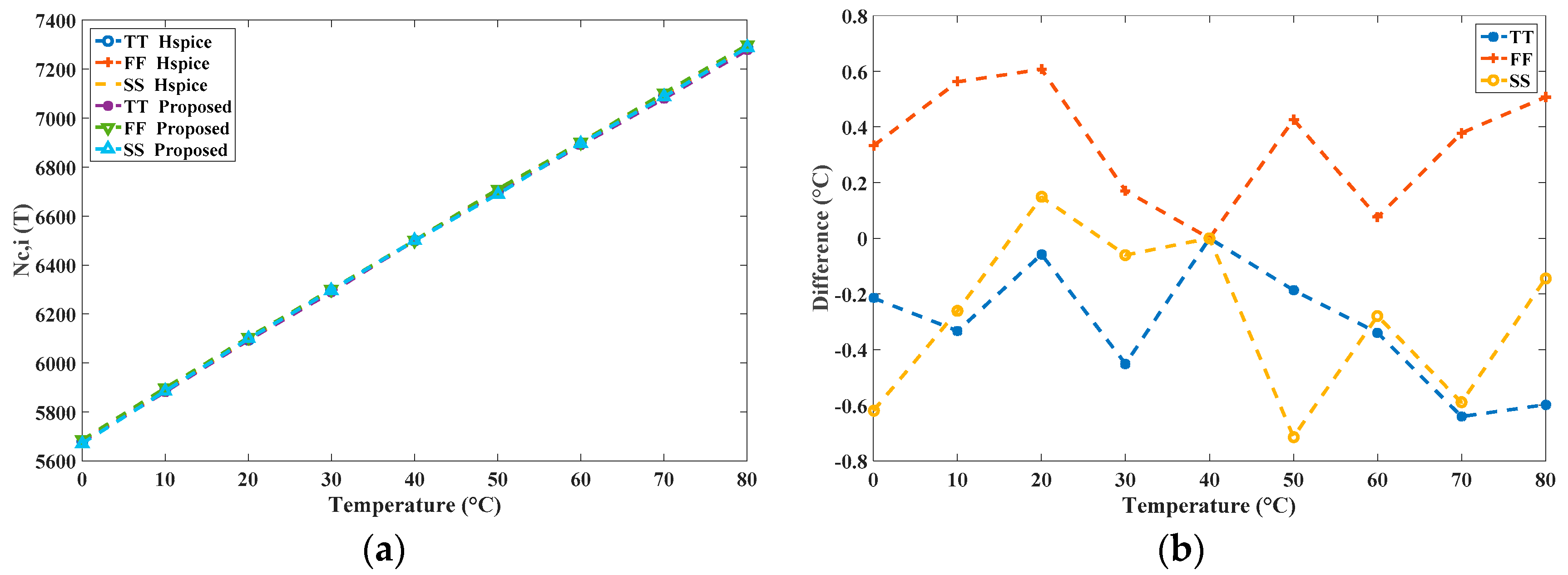

To further demonstrate the precision of the proposed simulator, the two simulation results

Ni(

T), and their differences in degrees Celsius, are presented in

Figure 9 for comparison. The highly similar conditions between the behavioral and transistor-level simulators are shown. The maximal difference is within −0.8 °C~0.35 °C only, which verifies the functionality of the proposed simulator.

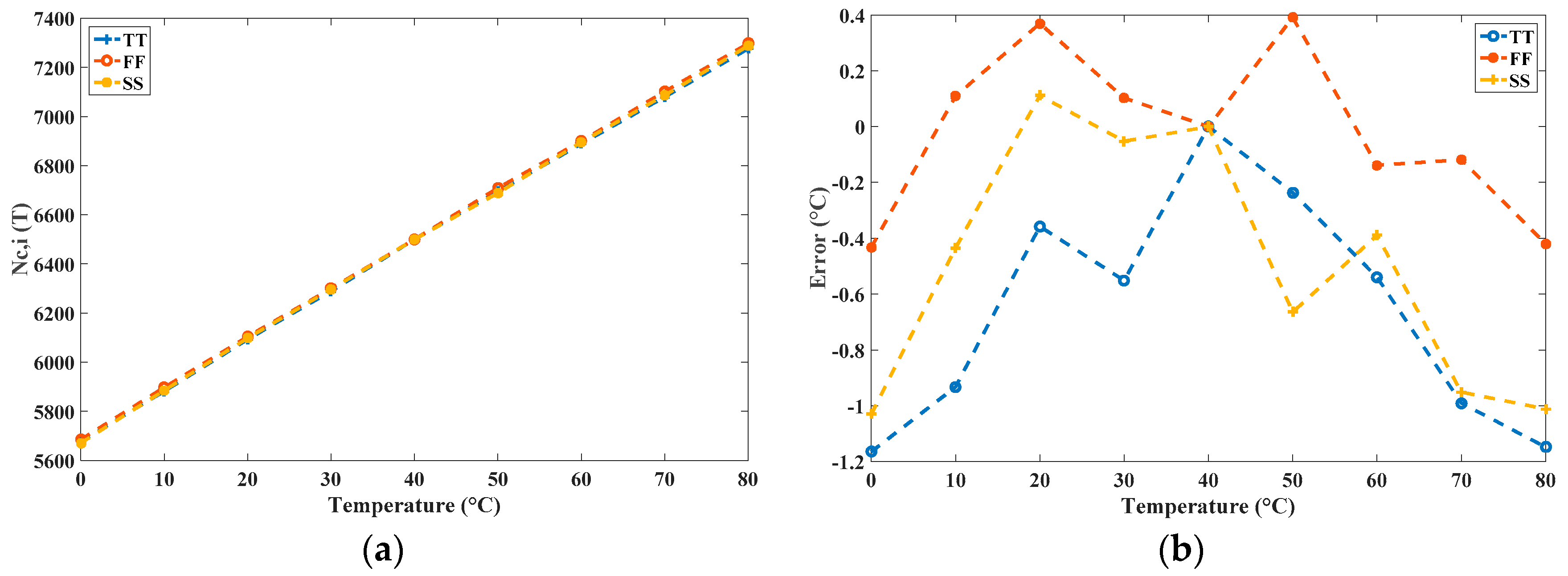

To perform the process-variation calibration, the value of

NS = 6500 was set to

TC = 40 °C to realize a calibrated

R of approximately 0.05 °C. The same values of

k = 21 and

tREF = 25 ns were selected and the model

tNOT,i(40 °C) was used to determine the

nC,i for the three process corners. With the same operation as that of the uncalibrated sensor, the calibrated sensor attained the calibrated

NC,i(

T) in an extremely short time. The generated figures for the simulated

NC,i(

T) after the calibration and for the corresponding inaccuracy after one-point calibration are shown in

Figure 10. The

NC,i(

T) values for the three corners nearly coincided and a stable

R was achieved, thereby validating the proposed one-point calibration.

To verify the precision, a calibration was executed using HSPICE for comparison; this required a substantial amount of simulation time. The HSPICE-simulated

nC,i were used as the corresponding time gain values to simulate a transistor-level calibrated sensor, and (predictably) the simulation time was very long. The simulation results

NC,i(

T) of the two simulators are shown in

Figure 11a and the maximal difference is in the range of −0.7 °C to 0.6 °C, as shown in

Figure 11b. The highly similar results of these tests validate the calibration of the proposed simulator. To further verify the effect of the voltage variation, we capture the models of the CMOS inverter from 3.1 V to 3.5 V and store them in the library. With the same operation,

Figure 12 shows the corresponding differences and presents the similar results, which validate the proposed simulator for the different-voltage operation.

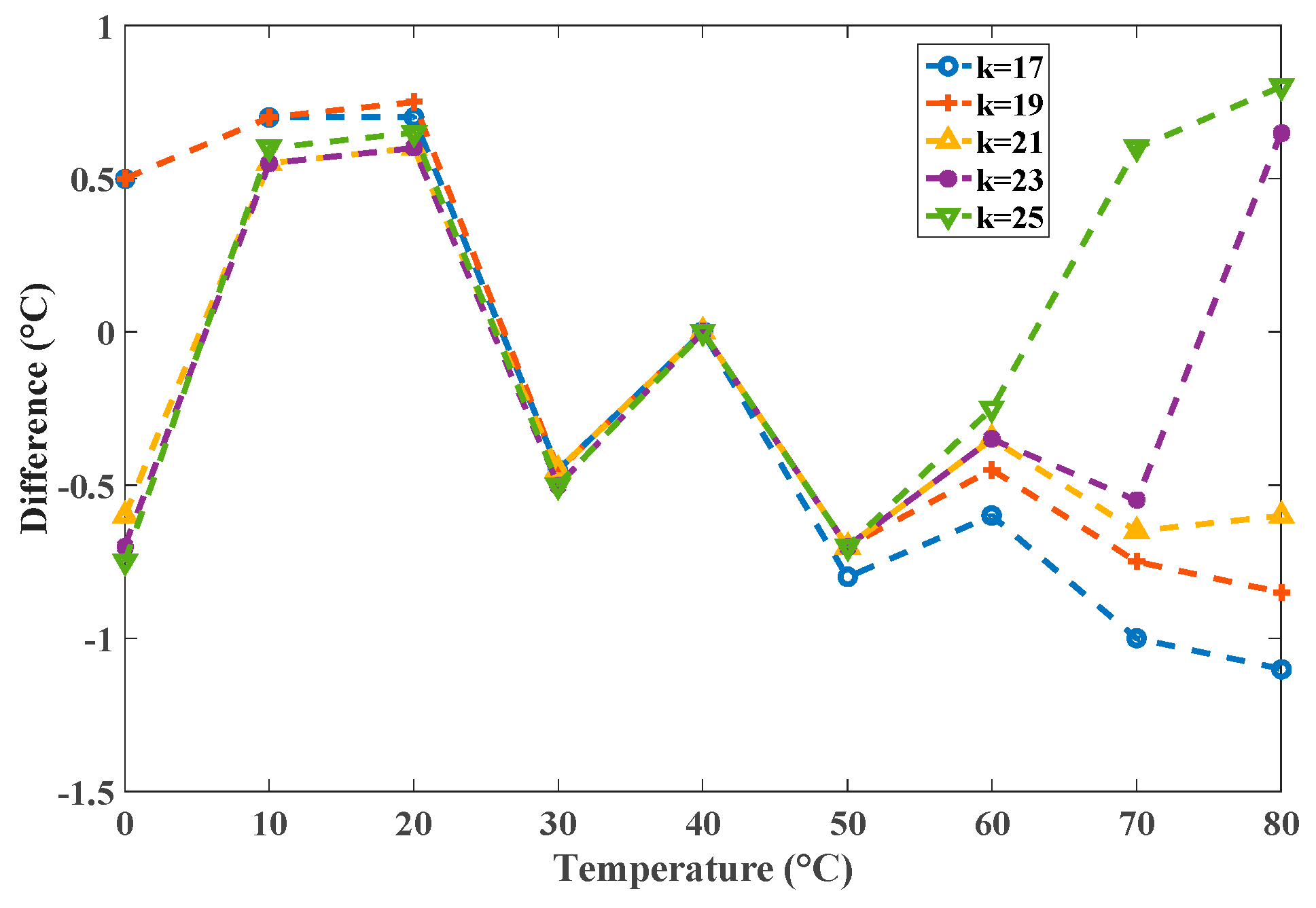

For precision considerations, the selected value of

k also determines the precision of the simulator because of the precision of the captured models. Using the models listed in

Table 1, simulations of the calibrated sensor were performed using the proposed system and HSPICE with values of

k that varied from 17 to 25 with increments of 2. The corresponding differences in degrees Celsius are presented in

Figure 13. The smallest difference was at

k = 21; both

k = 17 and 25 had larger differences than

k = 21 did. The greater the distance between

k and 21 was, the greater the difference was. This shows that the captured models for identical stages should be used to achieve the highest possible precision.

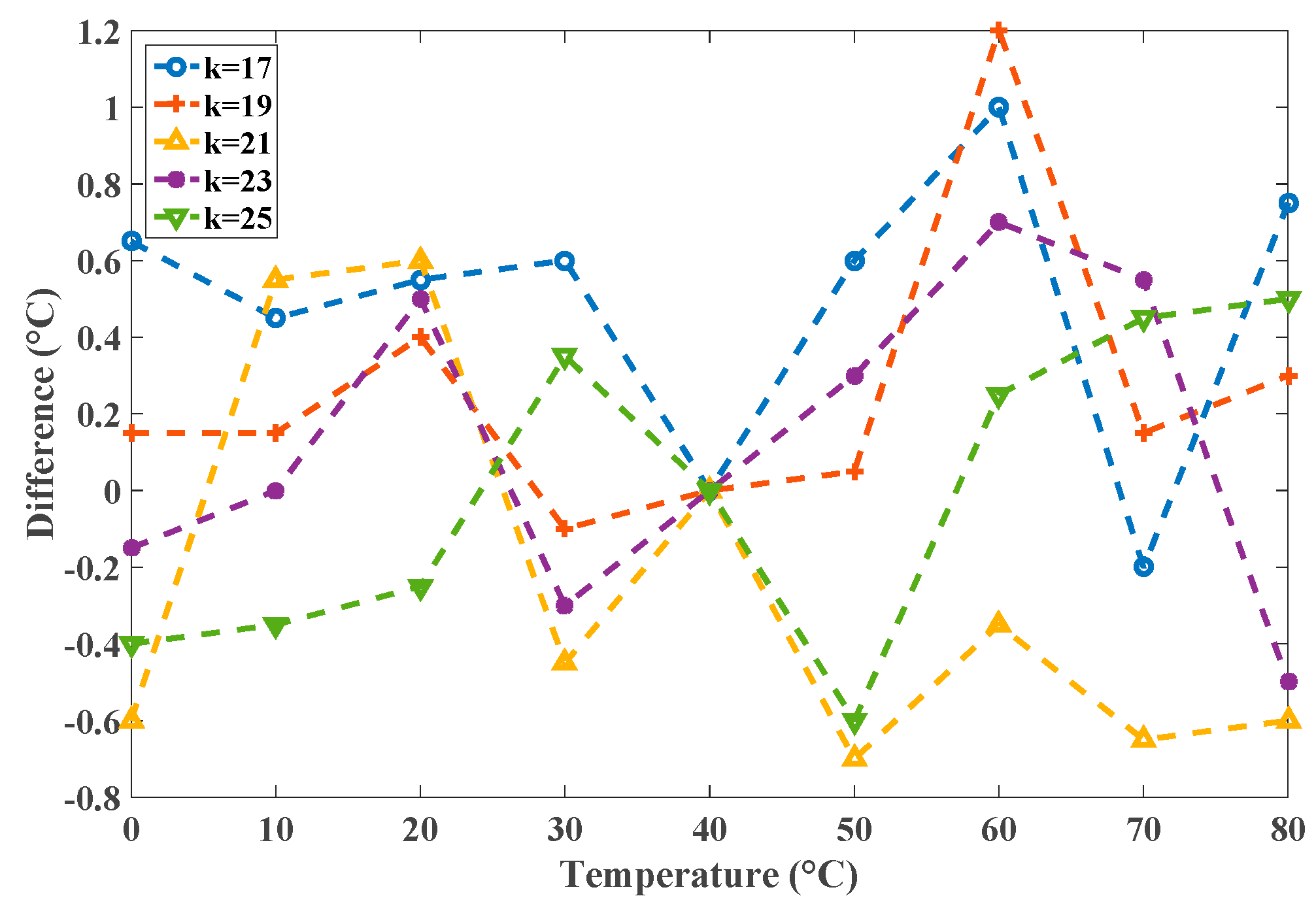

To improve the precision, the library was extended with models of the appropriate stages (

k = 17–25). For simplicity,

Figure 14 shows the extended library with three TT corner models. In addition to the extended models, the control logics for selecting the

k values and the corresponding switches were added to output the appropriate model for the oscillator. Additionally, the designer could input

k > 25 or

k < 17 and the system would automatically substitute the model for

k = 25 or

k = 17, respectively. The improvements from this modification are presented in

Figure 15. The precision values were obviously enhanced by this modified library. When necessary, the detailed models for every value of

k can be constructed to achieve high precision by increasing the library cost. The experiments show that the proposed simulator for all-digital CMOS TDSTSs can perform rapid simulations with accurate results.