BTI Aging Influence Analysis and Mitigation in Flash ADCs

Abstract

1. Introduction

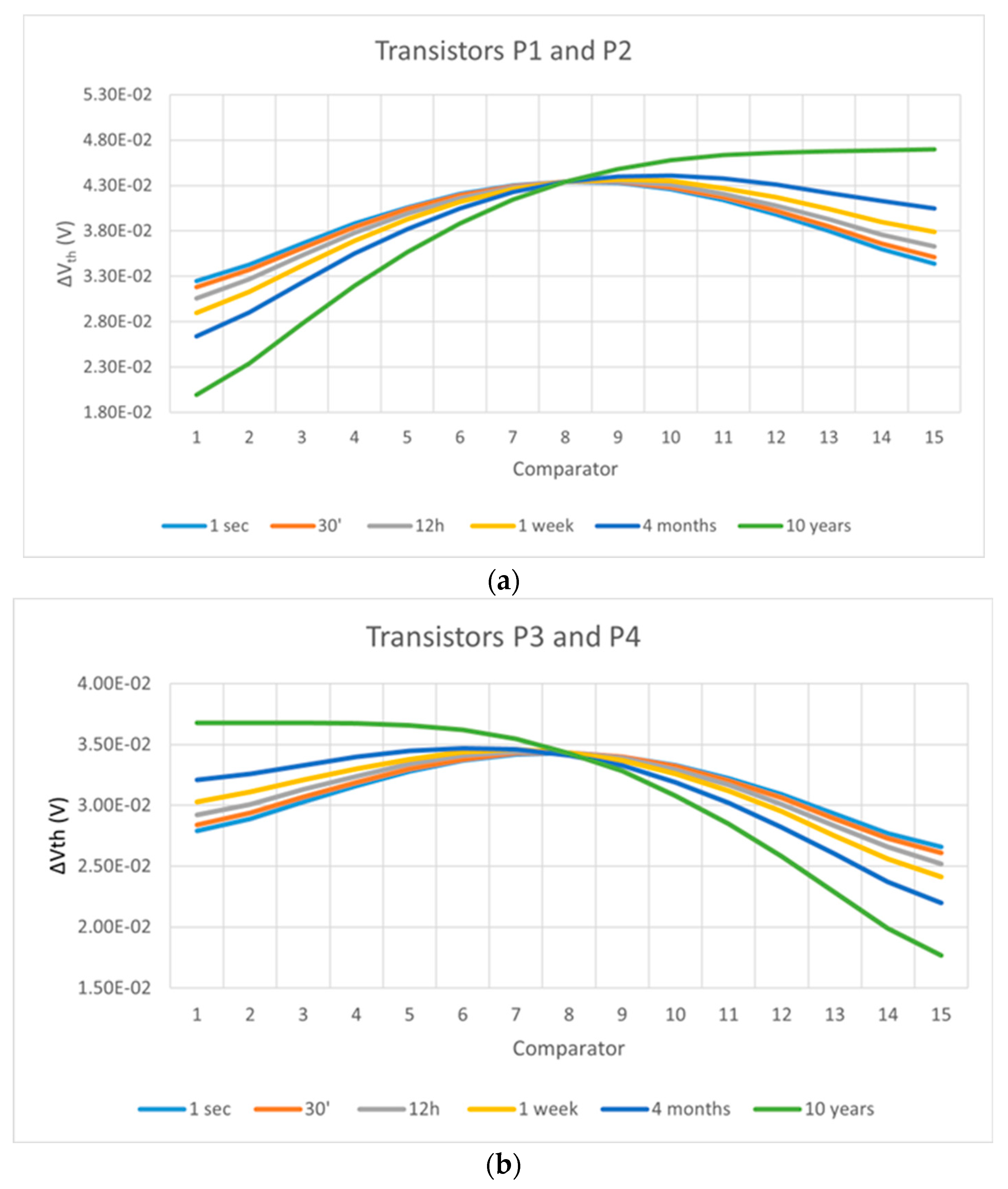

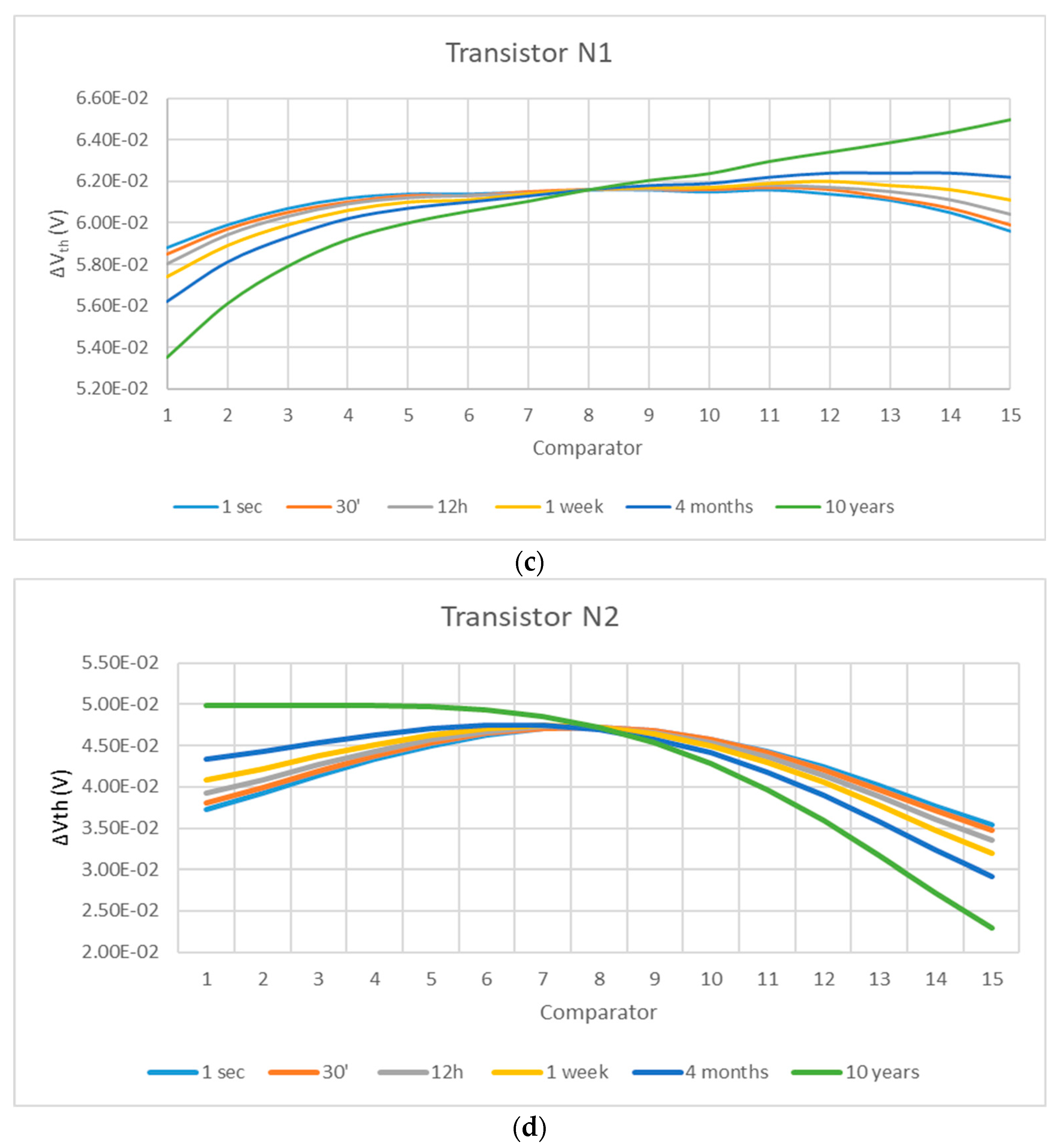

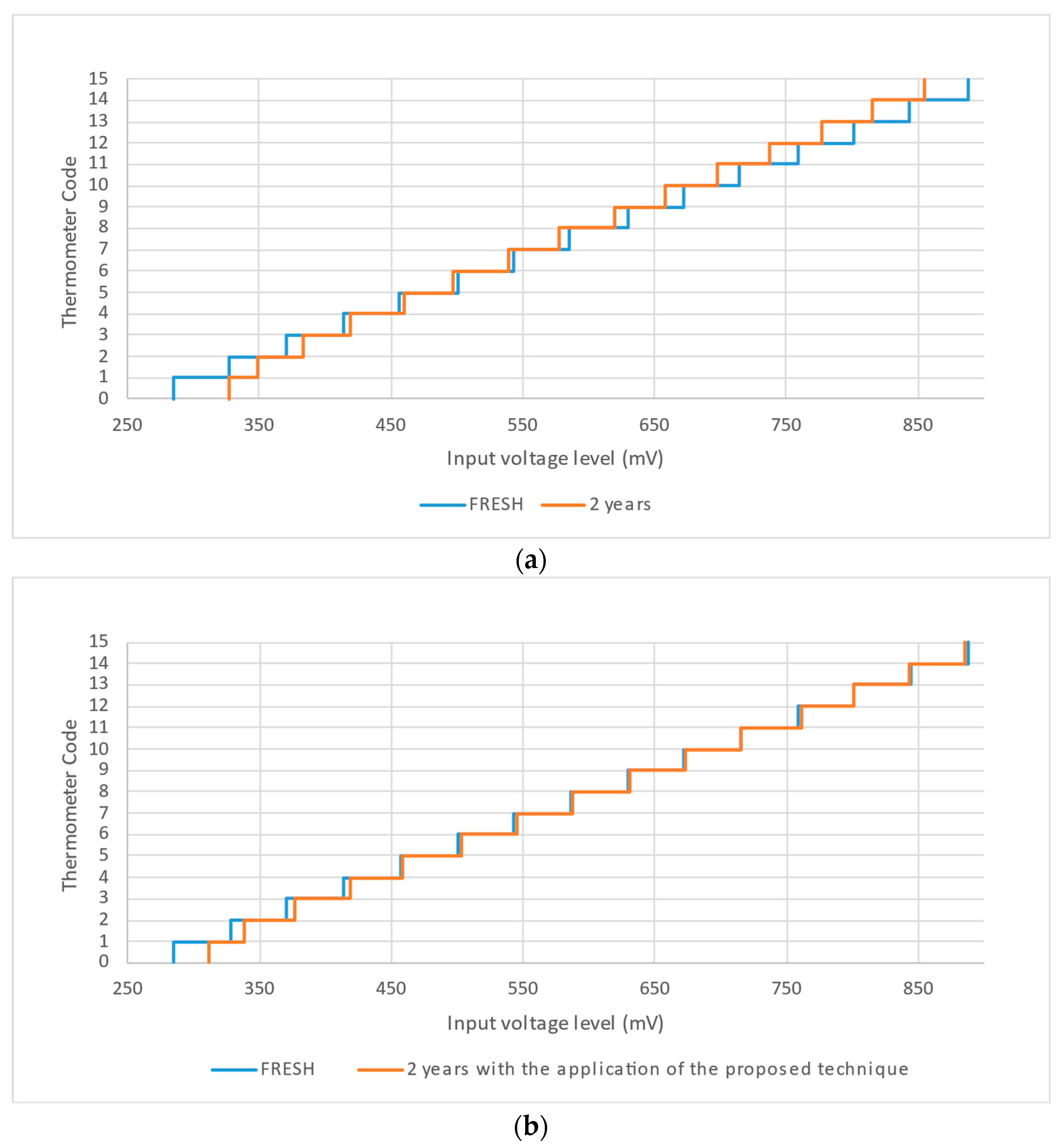

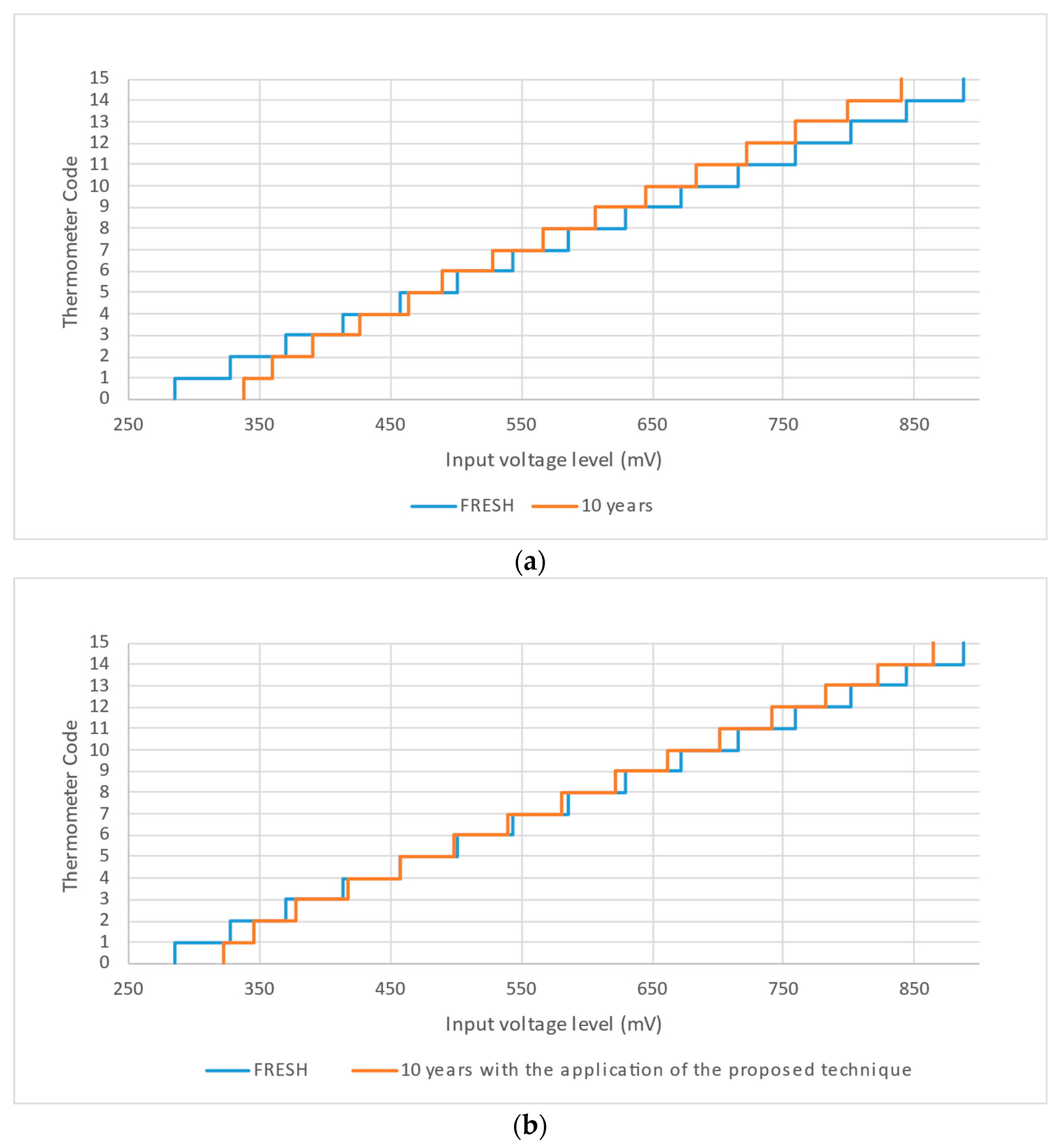

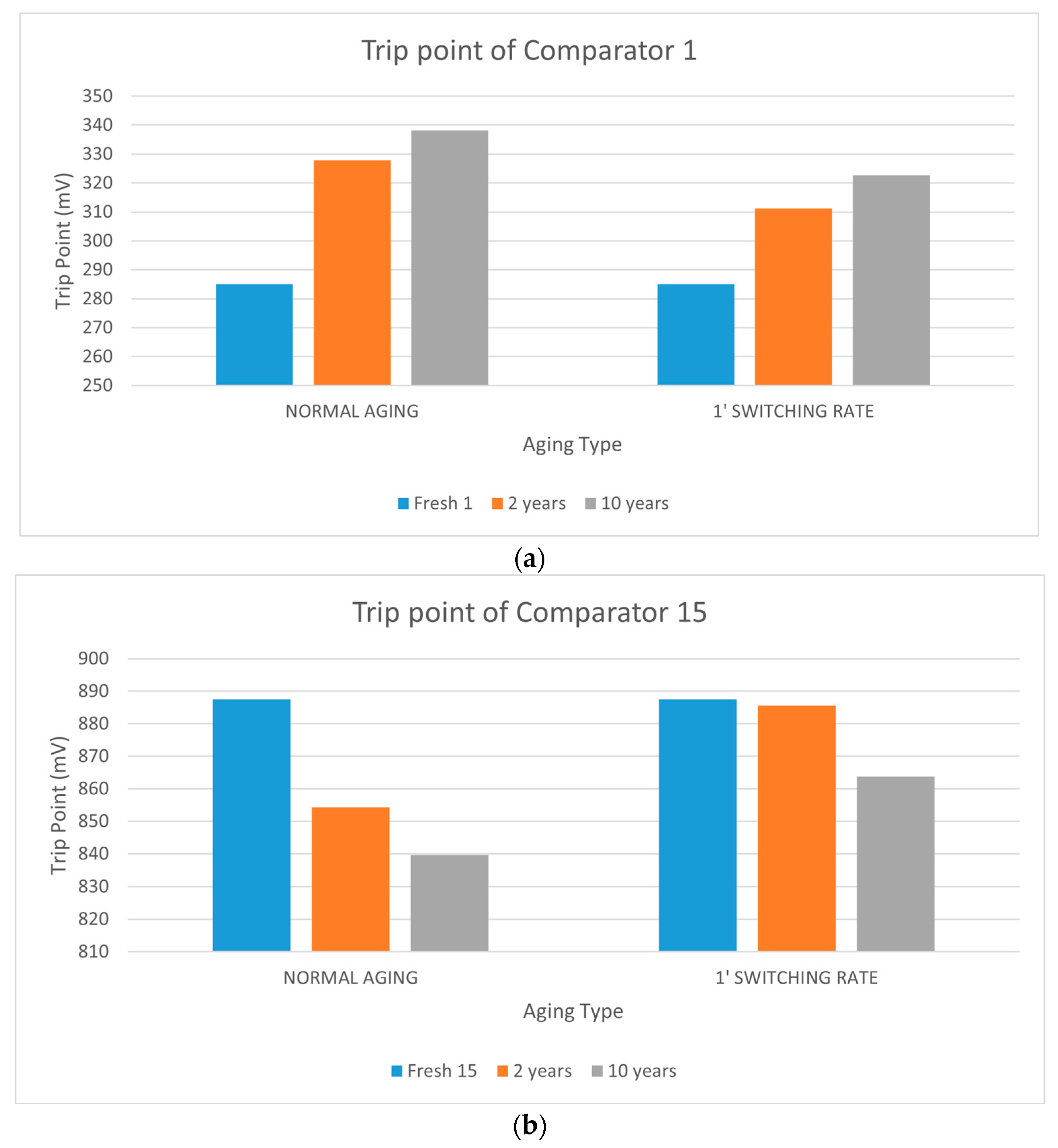

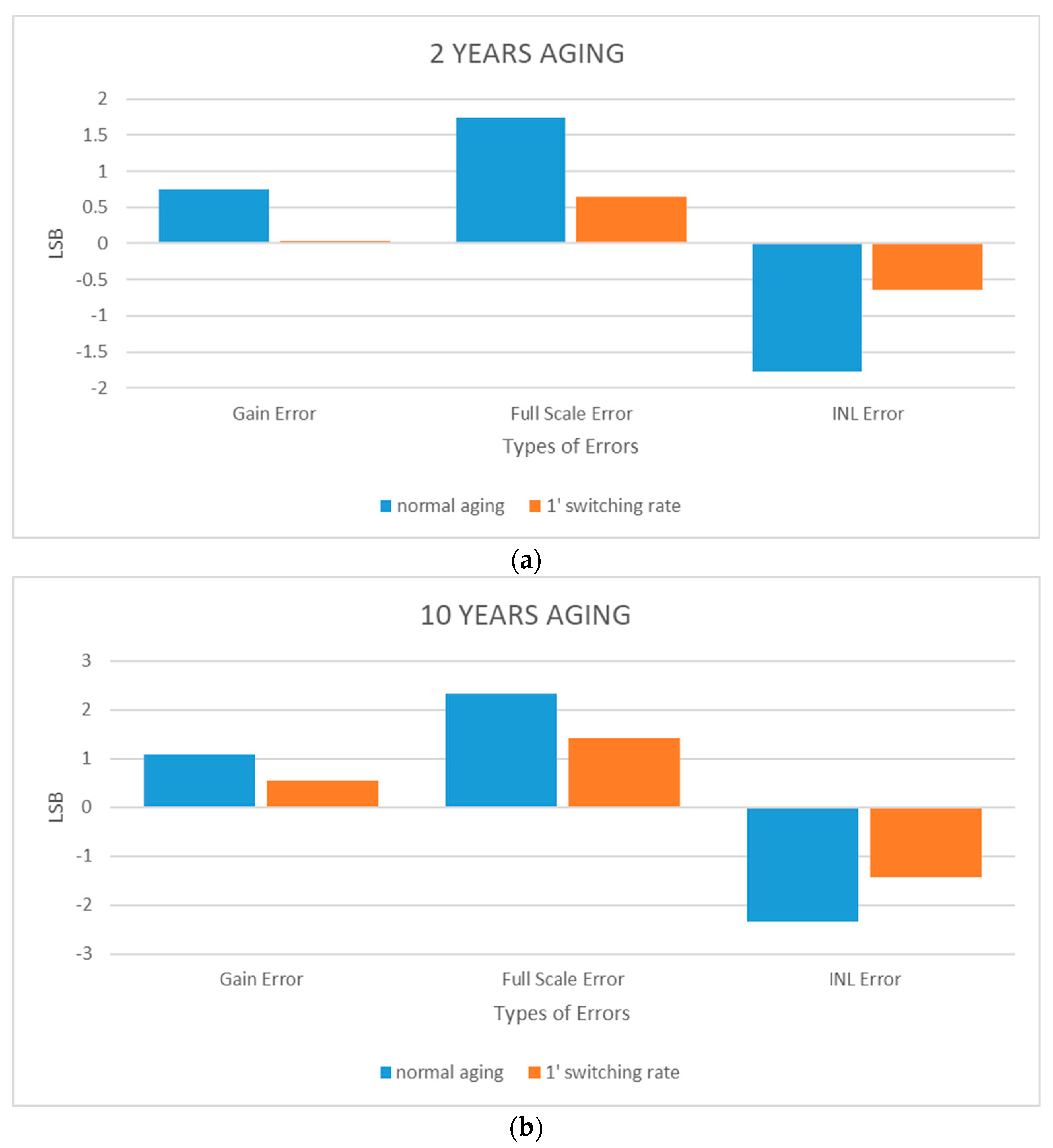

- Reduce the aging rate of the transistors in the comparators of the ADC and extend the operating lifetime of the circuit.

- Homogenize the transistors’ aging in all comparators, thus diminishing the shift in their trip point voltage, which seriously degrades ADC performance characteristics. Thus, the gradual increase in comparator offset voltage caused by aging is reduced.

2. Preliminaries

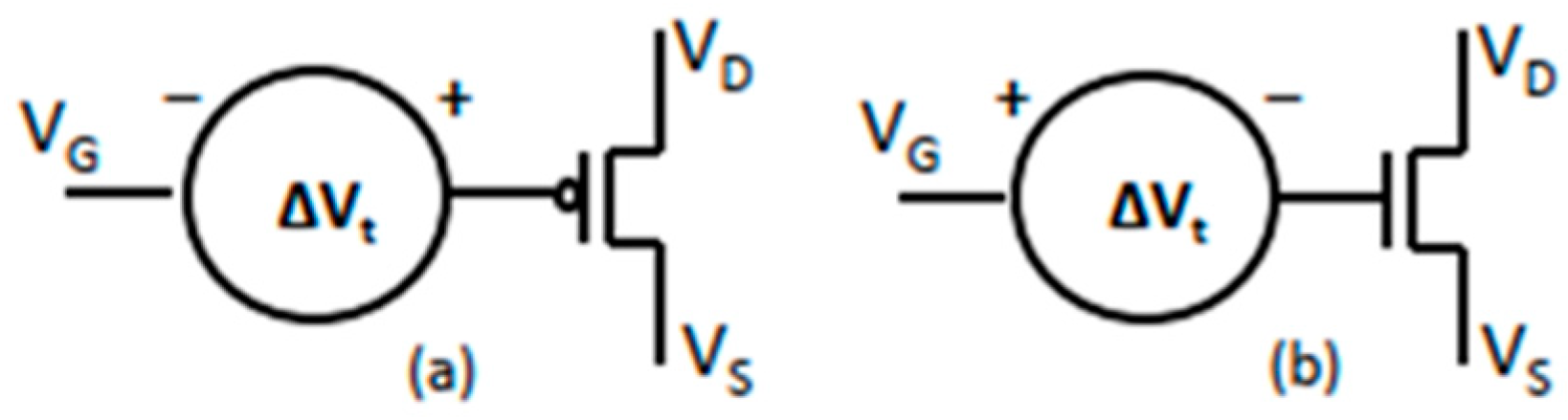

2.1. Bias Temperature Instability-Induced Aging

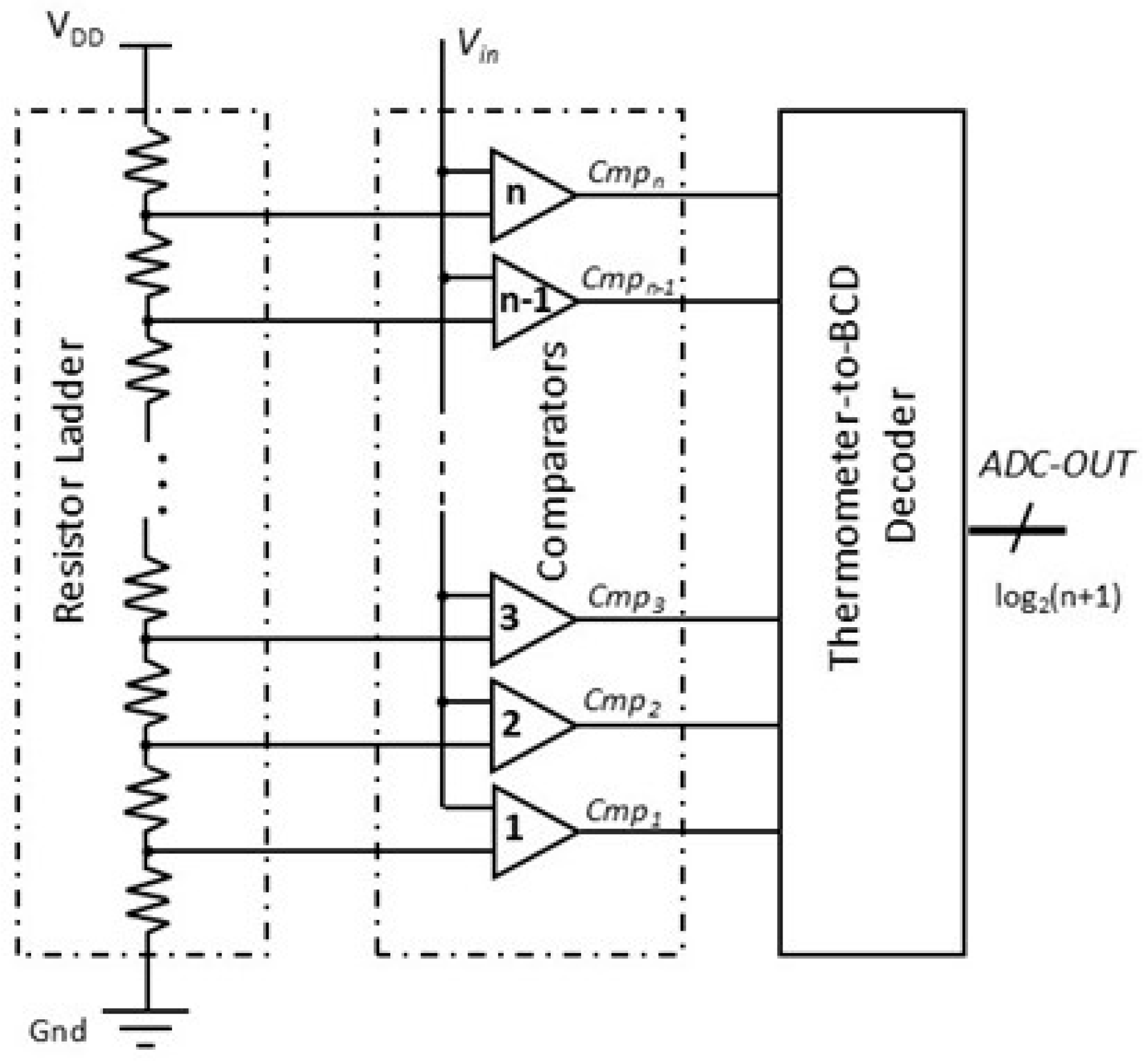

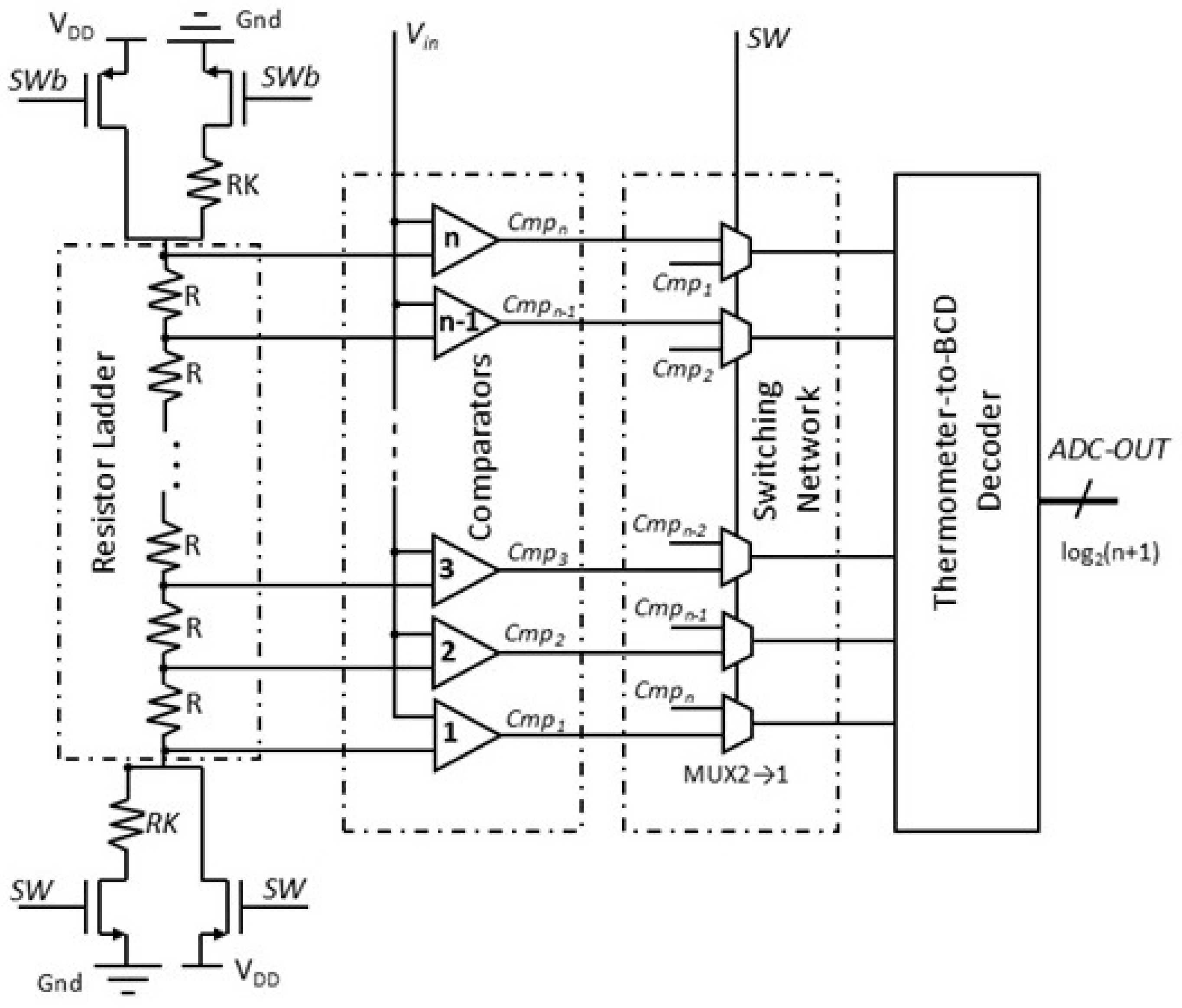

2.2. Flash Analog-to-Digital Converter

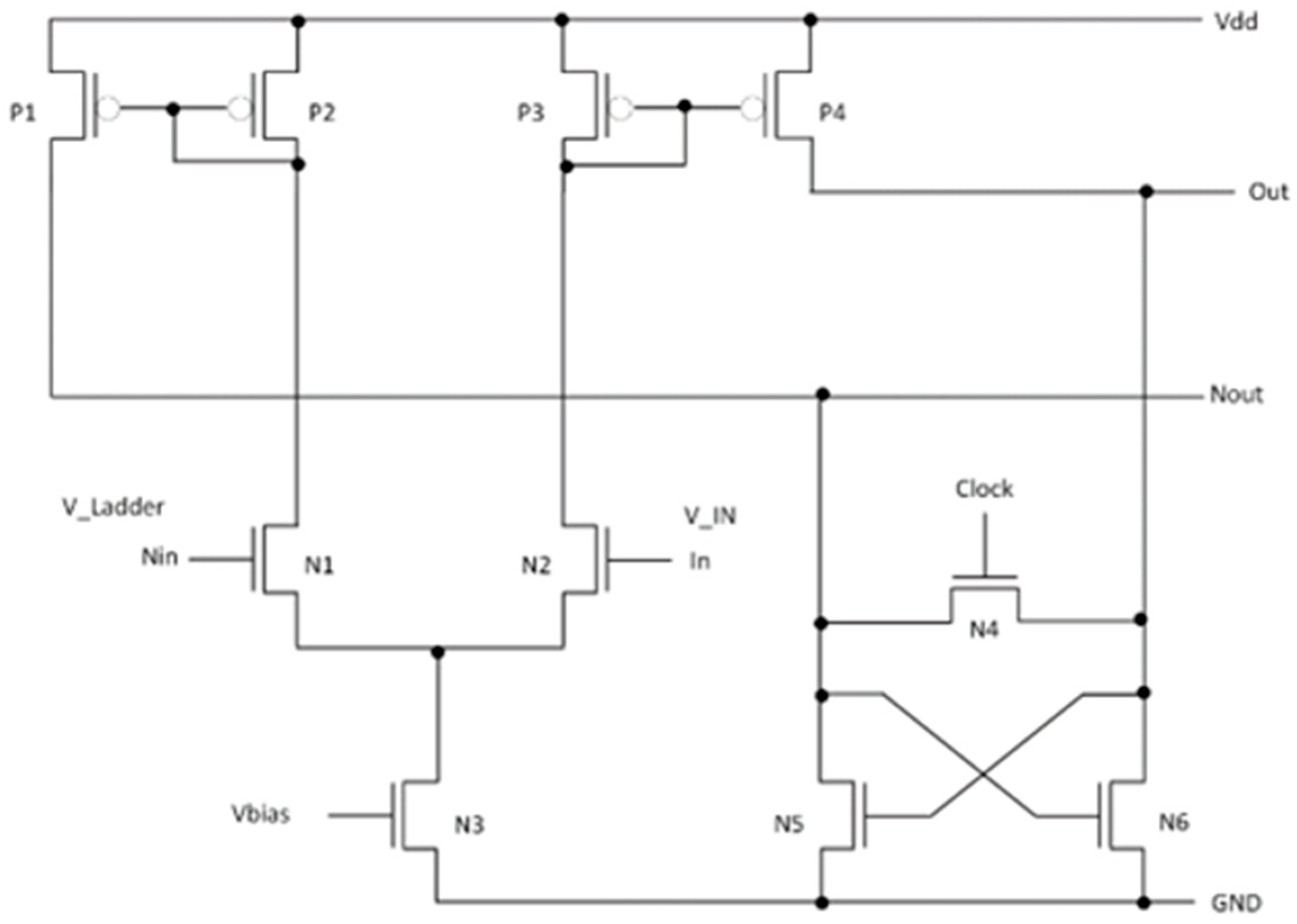

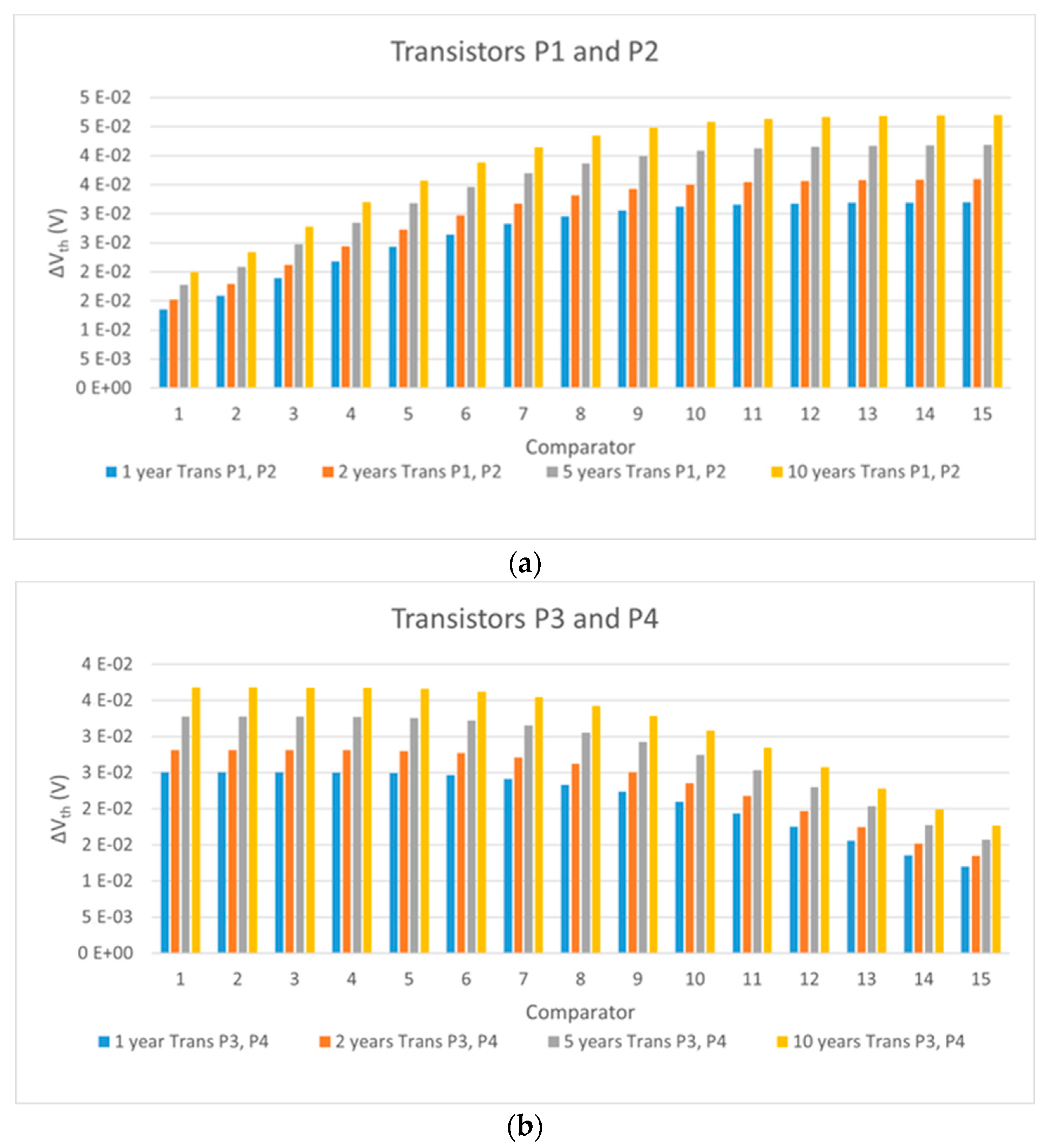

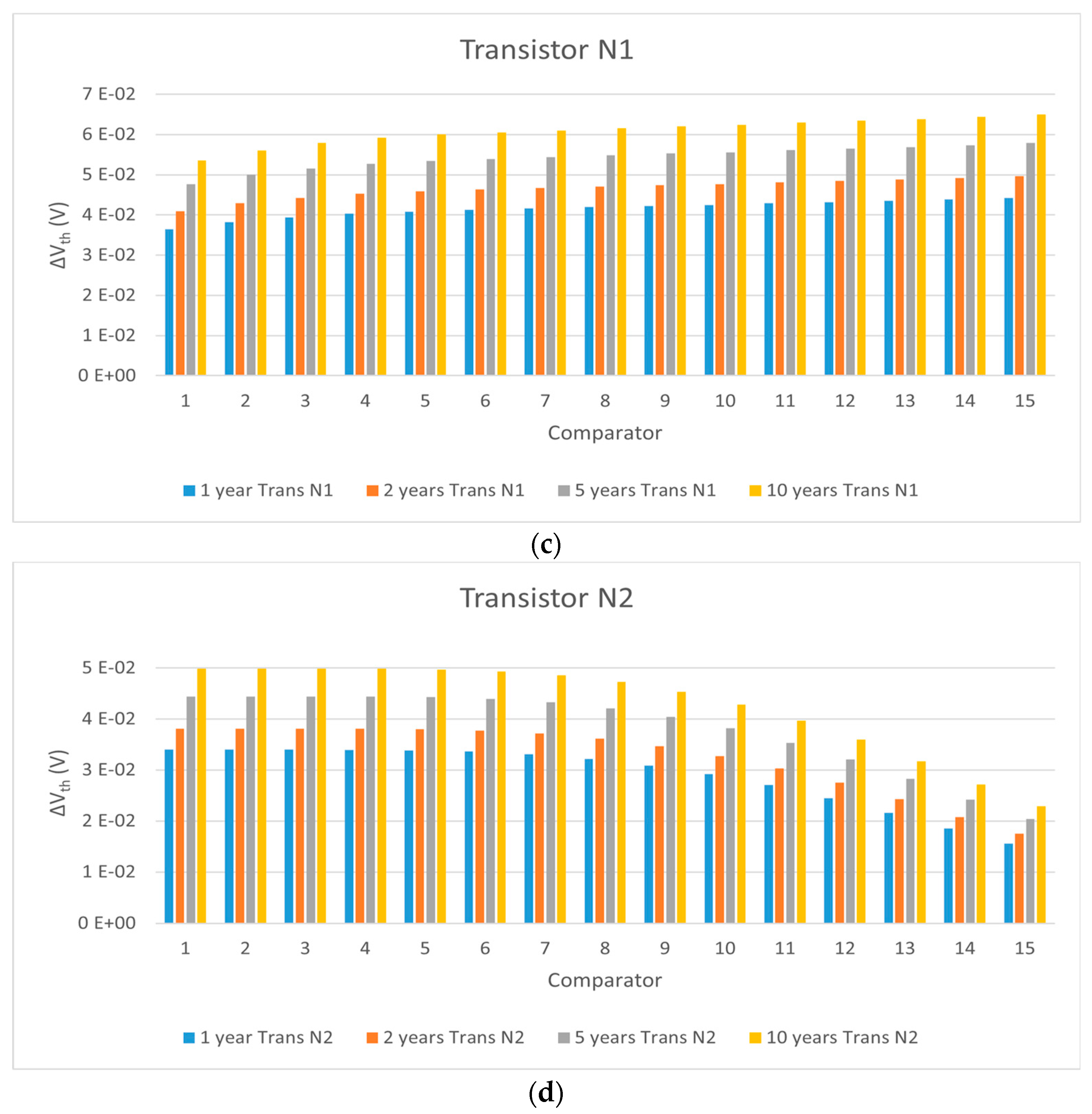

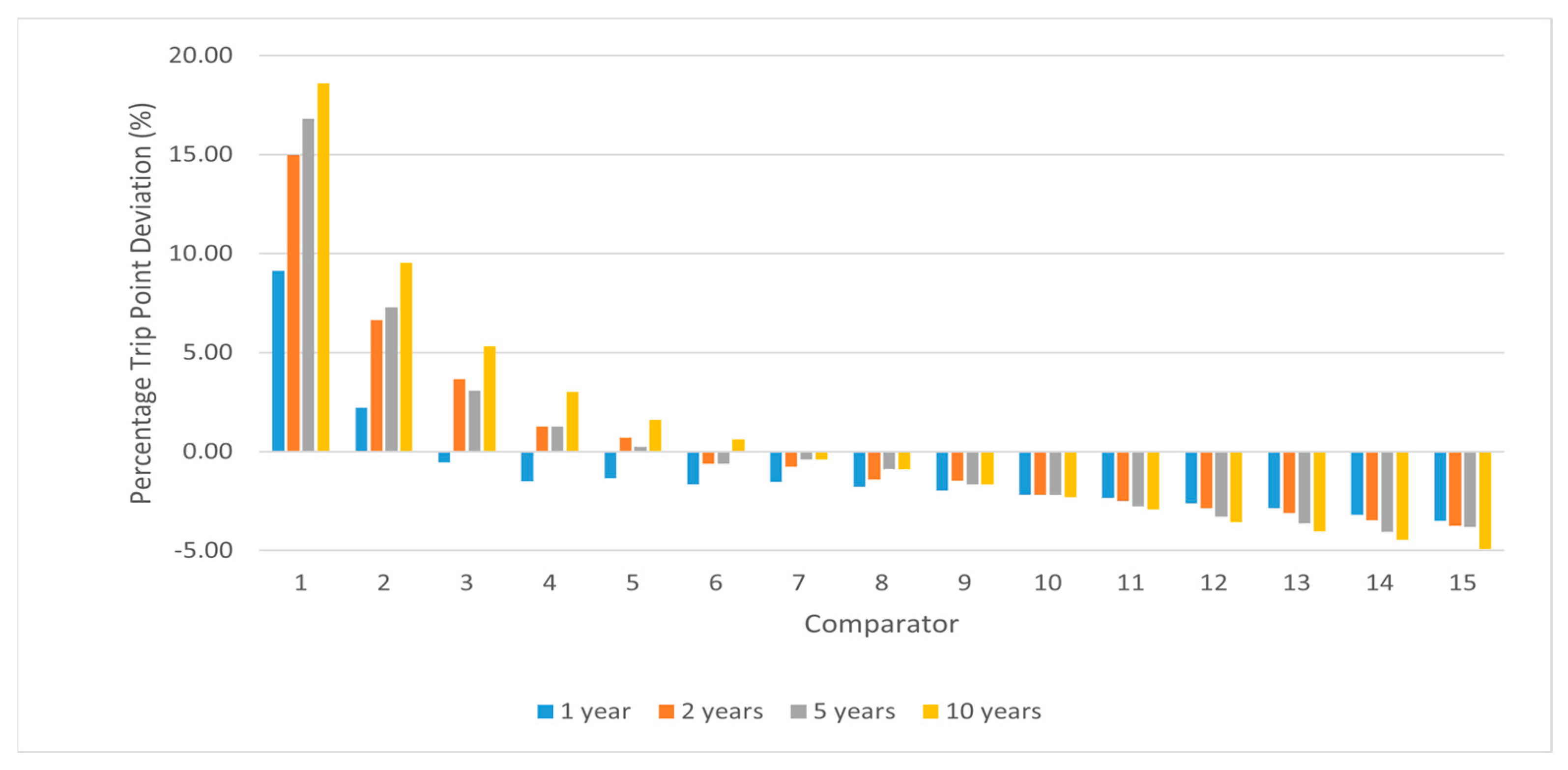

3. Influence of BTI-Induced Aging on Flash ADCs

4. Proposed Aging Mitigation Technique

- It initially aims to reduce the aging rate of the comparators’ transistors to extend the circuit’s operating lifetime;

- In parallel, it intends to equalize transistor aging across all comparators, aiming to homogenize and restrict the offset voltage developed over time due to aging, thereby diminishing trip point shifts and enhancing their reliability.

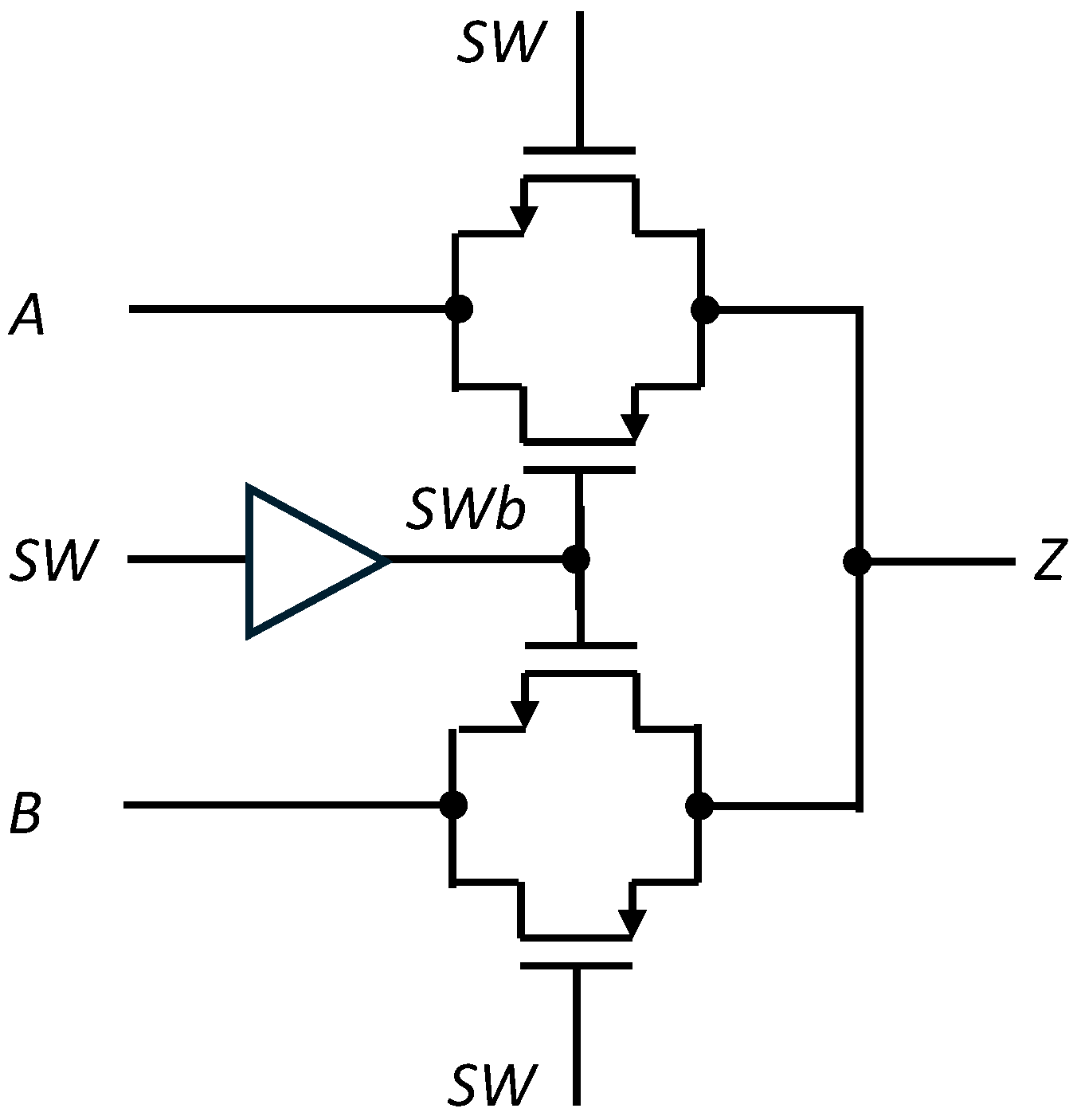

4.1. Design for Aging Mitigation

4.2. Simulation Results on Aging Mitigation

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Maricau, E.; Gielen, G. Analog IC Reliability in Nanometer CMOS; Springer: New York, NY, USA, 2013. [Google Scholar]

- Reis, R.; Cao, Y.; Wirth, G. Circuit Design for Reliability; Springer: New York, NY, USA, 2015. [Google Scholar]

- Panagopoulos, G.D. Variability and Reliability Issues in Mixed-Signal Circuits. In Mixed-Signal Circuits; CRC Press: Boca Raton, FL, USA, 2015; pp. 95–125. [Google Scholar]

- Park, G.; Kim, M.; Kim, C.H.; Kim, B.; Reddy, V. All-Digital PLL Frequency and Phase Noise Degradation Measurements Using Simple on-Chip Monitoring Circuits. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018. [Google Scholar] [CrossRef]

- Dhar, T.; Sapatnekar, S.S. Reliability Analysis of a Delay-Locked Loop Under HCI and BTI Degradation. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 31 March–4 April 2019; pp. 1–6. [Google Scholar]

- Reddy, V.; Martin, S.; Benaissa, K.; Chancellor, C.; Bhatia, K.; Srinivasan, V.; Rentala, V.; Krishnan, S.; Ondrusek, J. Challenges in Radio Frequency and Mixed-Signal Circuit Reliability. In Proceedings of the IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019. [Google Scholar] [CrossRef]

- Khan, M.A.; Kerkhoff, H.G. An Indirect Technique for Estimating Reliability of Analog and Mixed-Signal Systems during Operational Life. In Proceedings of the IEEE 16th International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS), Karlovy Vary, Czech Republic, 7–11 April 2013; pp. 159–164. [Google Scholar]

- Aragones, X.; Barajas, E.; Crespo-Yepes, A.; Mateo, D.; Rodriguez, R.; Martin-Martinez, J.; Nafria, M. Aging in CMOS RF Linear Power Amplifiers: An Experimental Study. IEEE Trans. Microw. Theory Tech. 2021, 69, 1453–1463. [Google Scholar] [CrossRef]

- Chouard, F.R.; More, S.; Fulde, M.; Schmitt-Landsiedel, D. An Aging Suppression and Calibration Approach for Differential Amplifiers in Advanced CMOS Technologies. In Proceedings of the ESSCIRC (ESSCIRC), Helsinki, Finland, 12–16 September 2011; pp. 251–254. [Google Scholar]

- Bhattacharjee, A.; Pradhan, S.N. Impact of Transistor Aging on the Reliability of the Analog Circuit. In Proceedings of the International Conference on Computational Performance Evaluation (ComPE), Shillong, India, 2–4 July 2020; pp. 212–216. [Google Scholar]

- Afacan, E.; Dündar, G.; Başkaya, F.; Pusane, A.E.; Yelten, M.B. On Chip Reconfigurable CMOS Analog Circuit Design and Automation Against Aging Phenomena: Sense and React. ACM Trans. Des. Autom. Electron. Syst. 2019, 24, 1–22. [Google Scholar] [CrossRef]

- Wan, J.; Kerkhoff, H.G. Reliability of SAR ADCs and Associated Embedded Instrument Detection. In Proceedings of the IEEE 20th International Mixed-Signals Testing Workshop (IMSTW), Paris, France, 24–26 June 2015; pp. 1–5. [Google Scholar]

- Lajmi, R.; Cacho, F.; David, O.; Blanc, J.-P.; Rouat, E.; Haendler, S.; Benech, P.; Larroze, E.L.; Bourdel, S. Reliability Assessment of 4GSP/s Interleaved SAR ADC. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15March 2018; pp. P-CR.5-1–P-CR.5-6. [Google Scholar]

- Choi, W.H.; Kim, H.; Kim, C.H. Circuit Techniques for Mitigating Short-Term Vth Instability Issues in Successive Approximation Register (SAR) ADCs. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), San Jose, CA, USA, 28–30 September 2015; pp. 1–4. [Google Scholar]

- Park, G.; Kim, M.; Pande, N.; Chiu, P.-W.; Song, J.; Kim, C.H. A Counter Based ADC Non-Linearity Measurement Circuit and Its Application to Reliability Testing. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 14–17 April 2019; pp. 1–4. [Google Scholar]

- Sharara, L.; Navidi, S.M.; Al Maharmeh, H.; Parekh, S.; Wehbi, A.; Alhawari, M.; Ismail, M. Analysis and Effects of Aging and Electromigration on Mixed-Signal ICs in 22nm FDSOI Technology. In Proceedings of the 29th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Glasgow, UK, 24–26 October 2022; pp. 1–4. [Google Scholar]

- Gielen, G.; Maricau, E. Stochastic Degradation Modeling and Simulation for Analog Integrated Circuits in Nanometer CMOS. In Proceedings of the Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 18–22 March 2013; pp. 326–331. [Google Scholar]

- Simicic, M.; Weckx, P.; Parvais, B.; Roussel, P.; Kaczer, B.; Gielen, G. Understanding the Impact of Time-Dependent Random Variability on Analog ICs: From Single Transistor Measurements to Circuit Simulations. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2019, 27, 601–610. [Google Scholar] [CrossRef]

- Xu, X.; Li, M.; Shi, Y.; Li, Y.; Zhu, H.; Sun, Q. Aging Analysis and Anti-Aging Circuit Design of Strong-Arm Latch Circuits in 14 Nm FinFET Technology. Electronics 2025, 14, 772. [Google Scholar] [CrossRef]

- Omana, M.; Rossi, D.; Edara, T.; Metra, C. Impact of Aging Phenomena on Latches’ Robustness. IEEE Trans. Nanotechnol. 2016, 15, 129–136. [Google Scholar] [CrossRef]

- Toledano-Luque, M.; Kaczer, B.; Franco, J.; Roussel, P.J.; Grasser, T.; Hoffmann, T.Y.; Groeseneken, G. From Mean Values to Distributions of BTI Lifetime of Deeply Scaled FETs through Atomistic Understanding of the Degradation. In Proceedings of the Symposium on VLSI Technology–Digest of Technical Papers, Kyoto, Japan, 14–16 June 2011; pp. 152–153. [Google Scholar]

- Singh, H.; Mahmoodi, H. Analysis of SRAM Reliability under Combined Effect of NBTI, Process and Temperature Variations in Nano-Scale CMOS. In Proceedings of the 5th International Conference on Future Information Technology, Busan, Republic of Korea, 21–23 February 2010; pp. 1–4. [Google Scholar]

- Ahmed, F.; Milor, L. Online Measurement of Degradation Due to Bias Temperature Instability in SRAMs. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2016, 24, 2184–2194. [Google Scholar] [CrossRef]

| Vdd = 1 V | ESPOX = 3.9 | |

|---|---|---|

| nMOS Transistors | pMOS Transistors | |

| Nominal threshold voltage | Vth0n = 1 mV | Vth0p = 58.1 mV |

| Carrier mobility | Uon = 0.23 m2/(V·s) | Uop = 9.26 m2/(V·s) |

| Gate oxide thickness | Toxn = 2.25 nm | Toxp = 2.45 nm |

| nMOS Transistors | pMOS Transistors |

|---|---|

| Length = 160 nm | Length = 160 nm |

| Width = 720 nm | Width = 720 nm |

| Bulk @ GND | Bulk @ Vdd |

| nMOS Transistors | pMOS Transistors |

|---|---|

| Length = 160 nm | Length = 160 nm |

| Width = 2 μm | Width = 2 μm |

| Bulk @ GND | Bulk @ Vdd |

| nMOS Transistors | pMOS Transistors |

|---|---|

| Length = 80 nm | Length = 80 nm |

| Width = 240 nm | Width = 120 nm |

| Bulk @ GND | Bulk @ Vdd |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mylona, K.; Dounavi, H.-M.; Tsiatouhas, Y. BTI Aging Influence Analysis and Mitigation in Flash ADCs. Chips 2025, 4, 36. https://doi.org/10.3390/chips4030036

Mylona K, Dounavi H-M, Tsiatouhas Y. BTI Aging Influence Analysis and Mitigation in Flash ADCs. Chips. 2025; 4(3):36. https://doi.org/10.3390/chips4030036

Chicago/Turabian StyleMylona, Konstantina, Helen-Maria Dounavi, and Yiorgos Tsiatouhas. 2025. "BTI Aging Influence Analysis and Mitigation in Flash ADCs" Chips 4, no. 3: 36. https://doi.org/10.3390/chips4030036

APA StyleMylona, K., Dounavi, H.-M., & Tsiatouhas, Y. (2025). BTI Aging Influence Analysis and Mitigation in Flash ADCs. Chips, 4(3), 36. https://doi.org/10.3390/chips4030036