A CMOS 12-Bit 3MS/s Rad-Hard Digital-to-Analog Converter Based on a High-Linearity Resistor String Poly-Matrix

Abstract

1. Introduction

2. Rad-Hard Digital-to-Analog Converters

- Type 1—resistive (resistors, switches, and logic ports);

- Type 2—capacitive (capacitors, switches, and logic ports);

- Type 3—current steering (current generators, switches, and logic ports).

2.1. Resistor String Rad-Hard DACs in the Literature

2.2. Current-Steering Rad-Hard DACs in the Literature

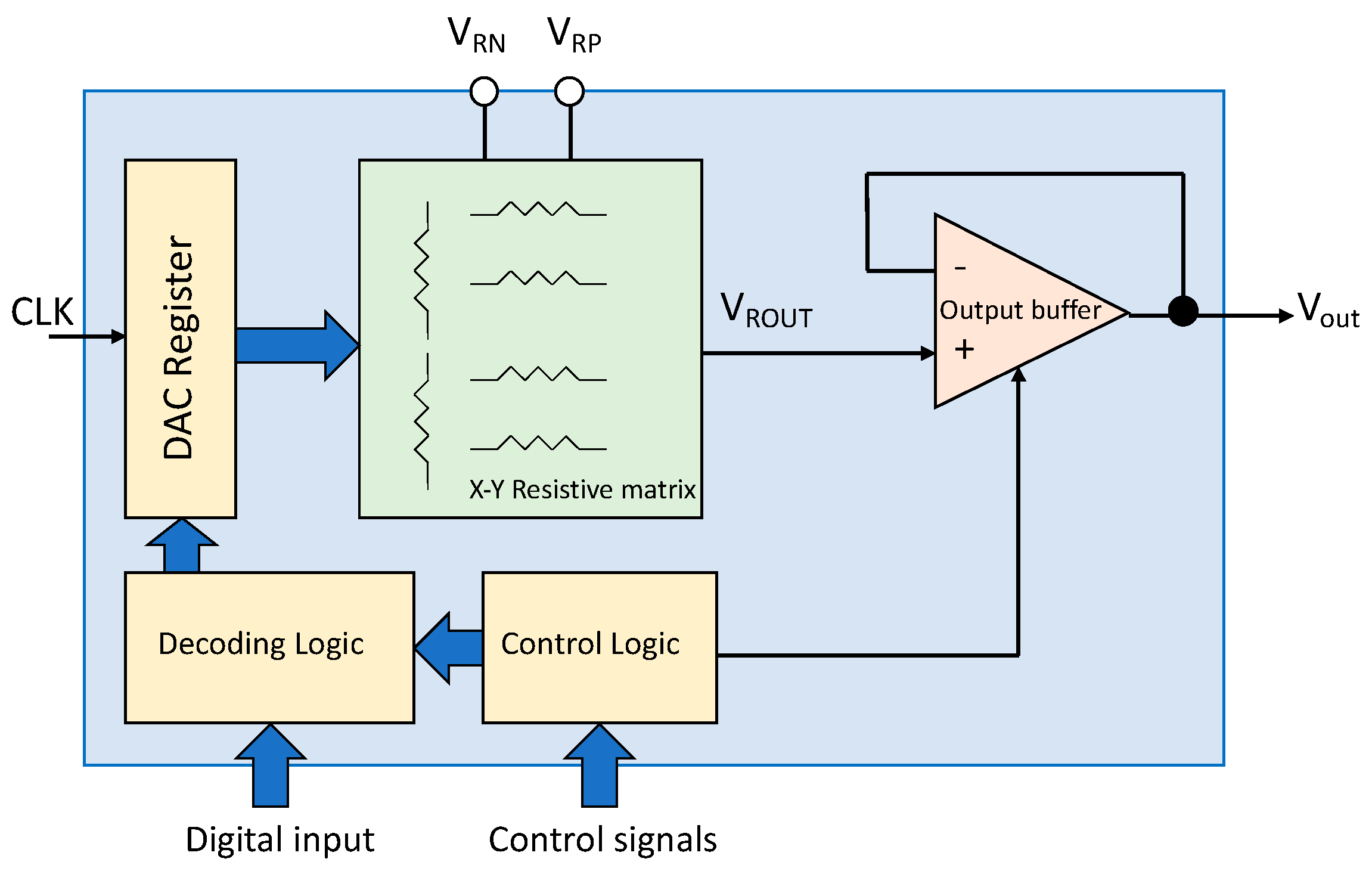

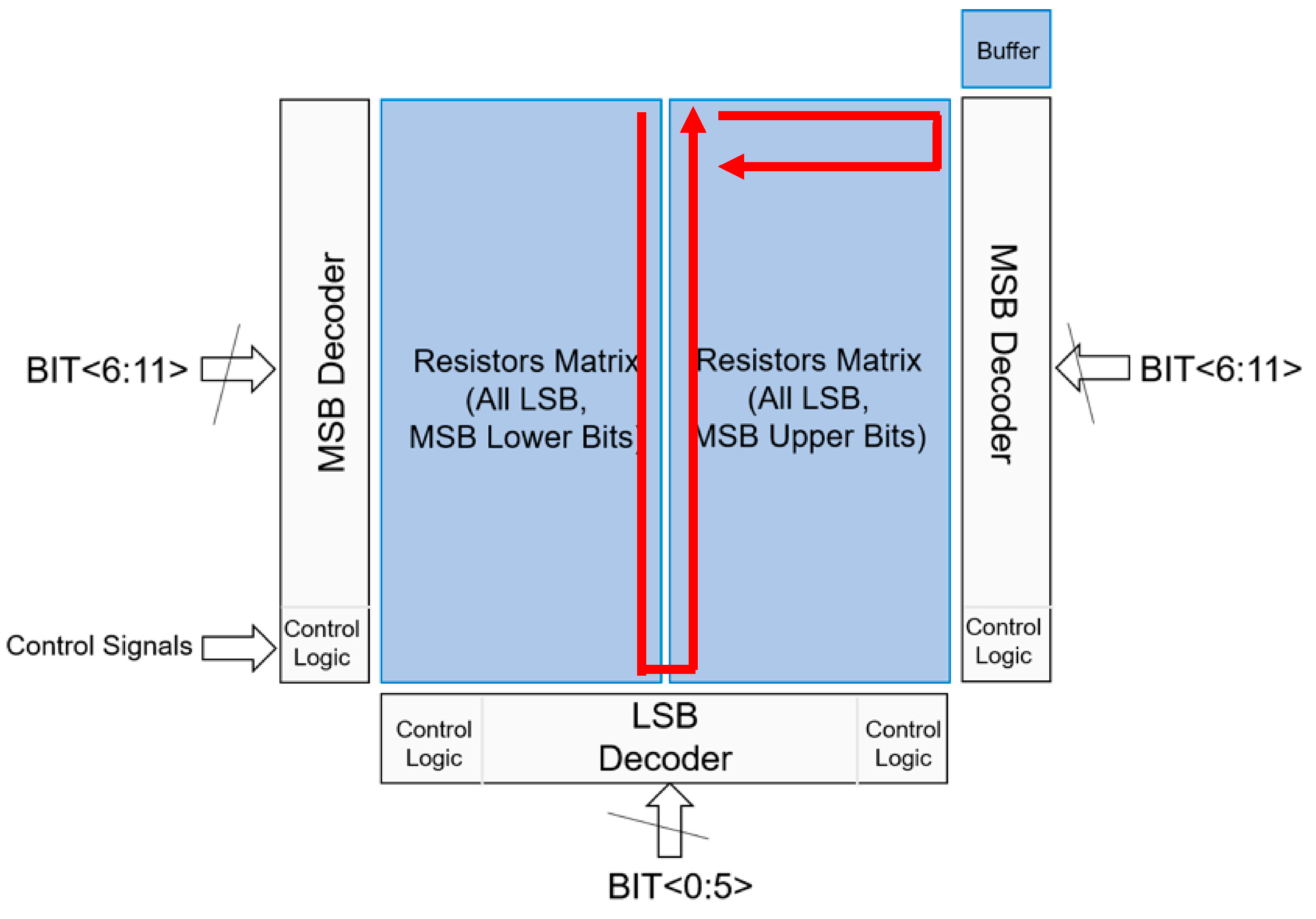

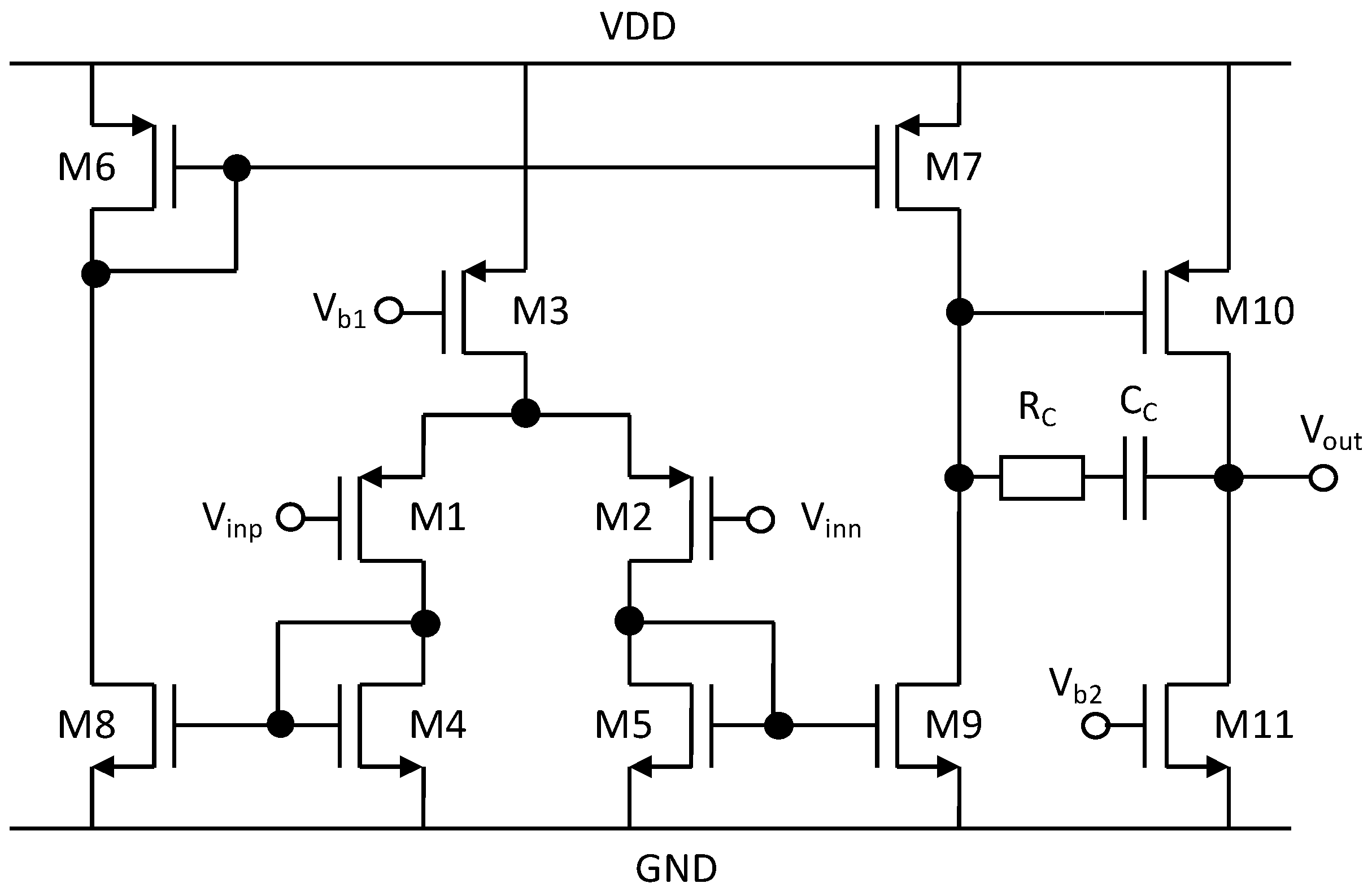

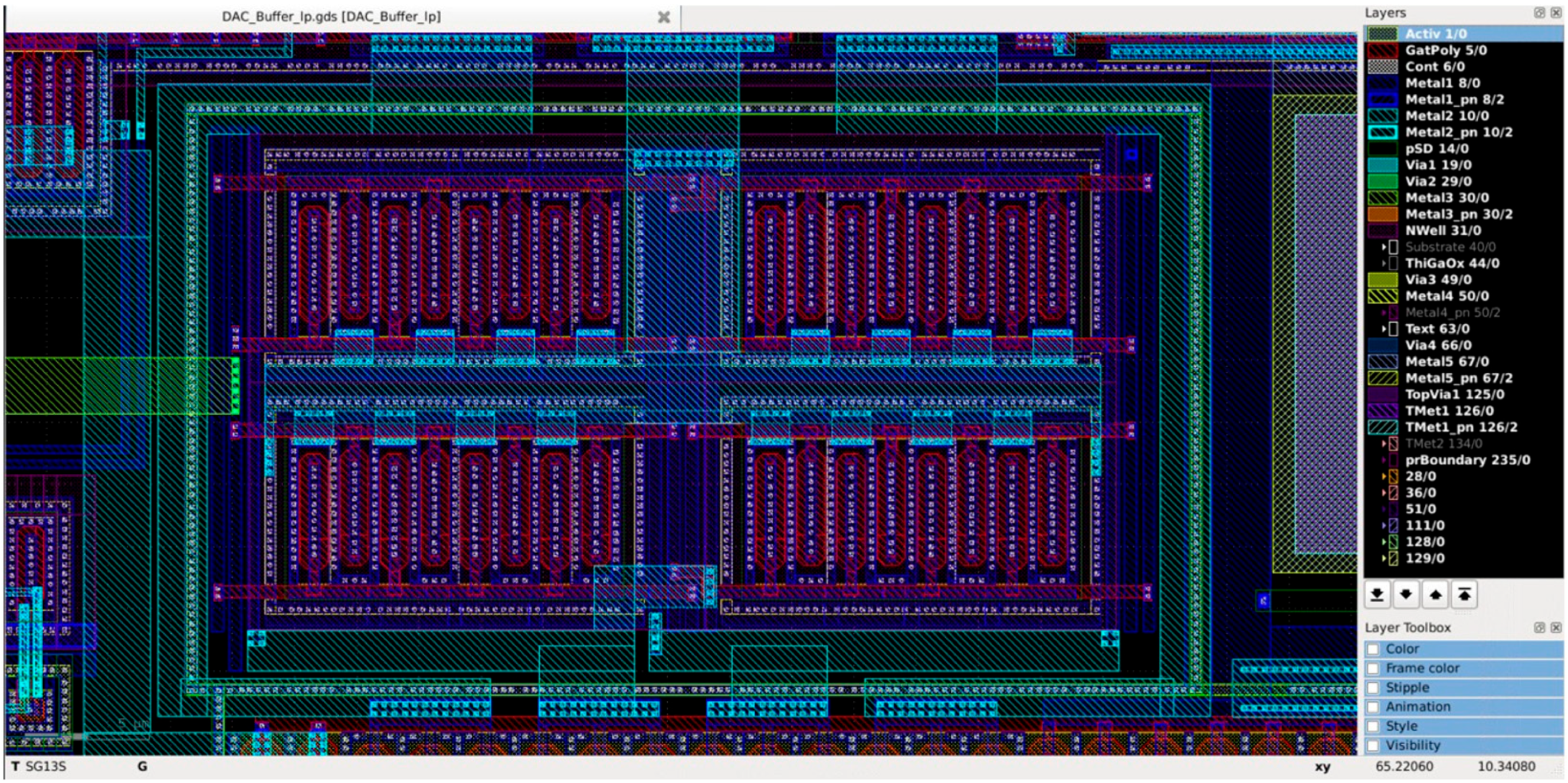

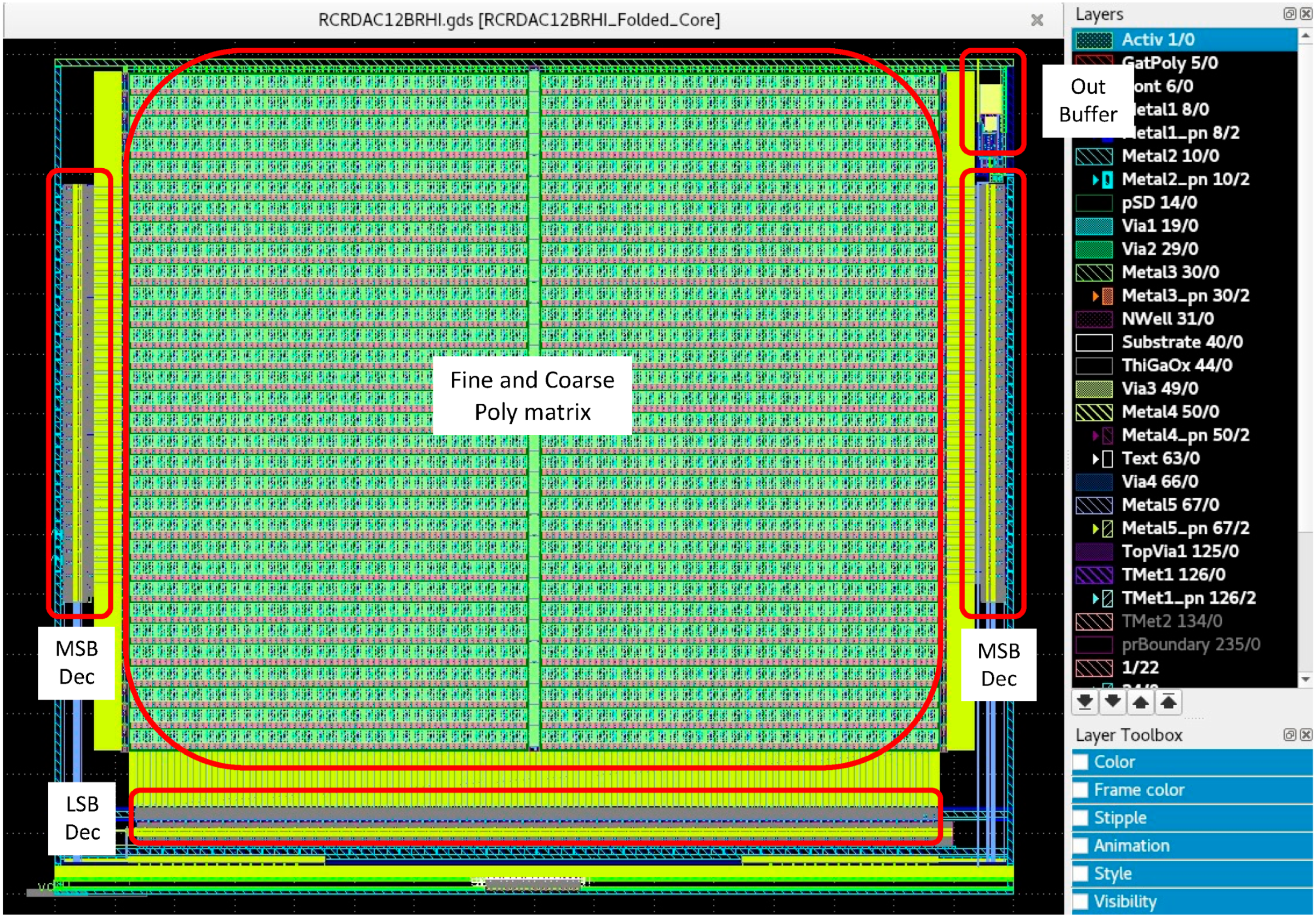

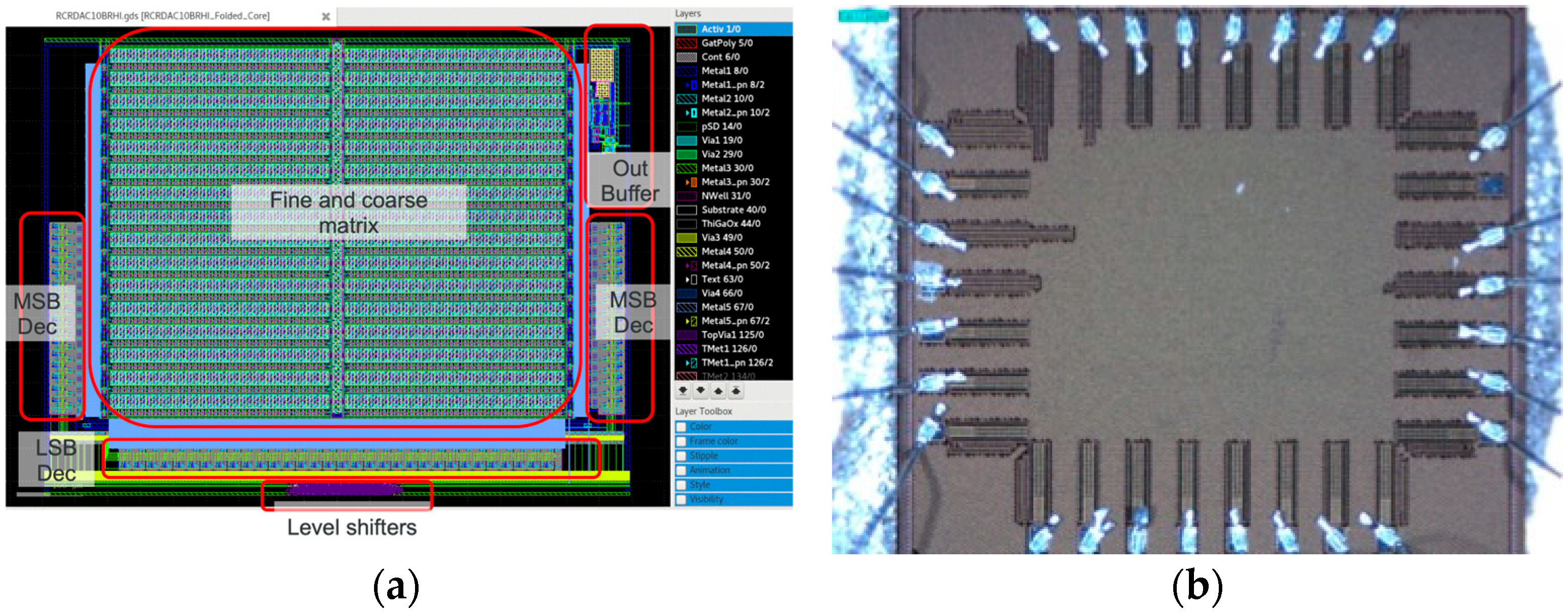

3. 3 MS/S 12-Bit Poly-Resistor Rad-Hard DAC

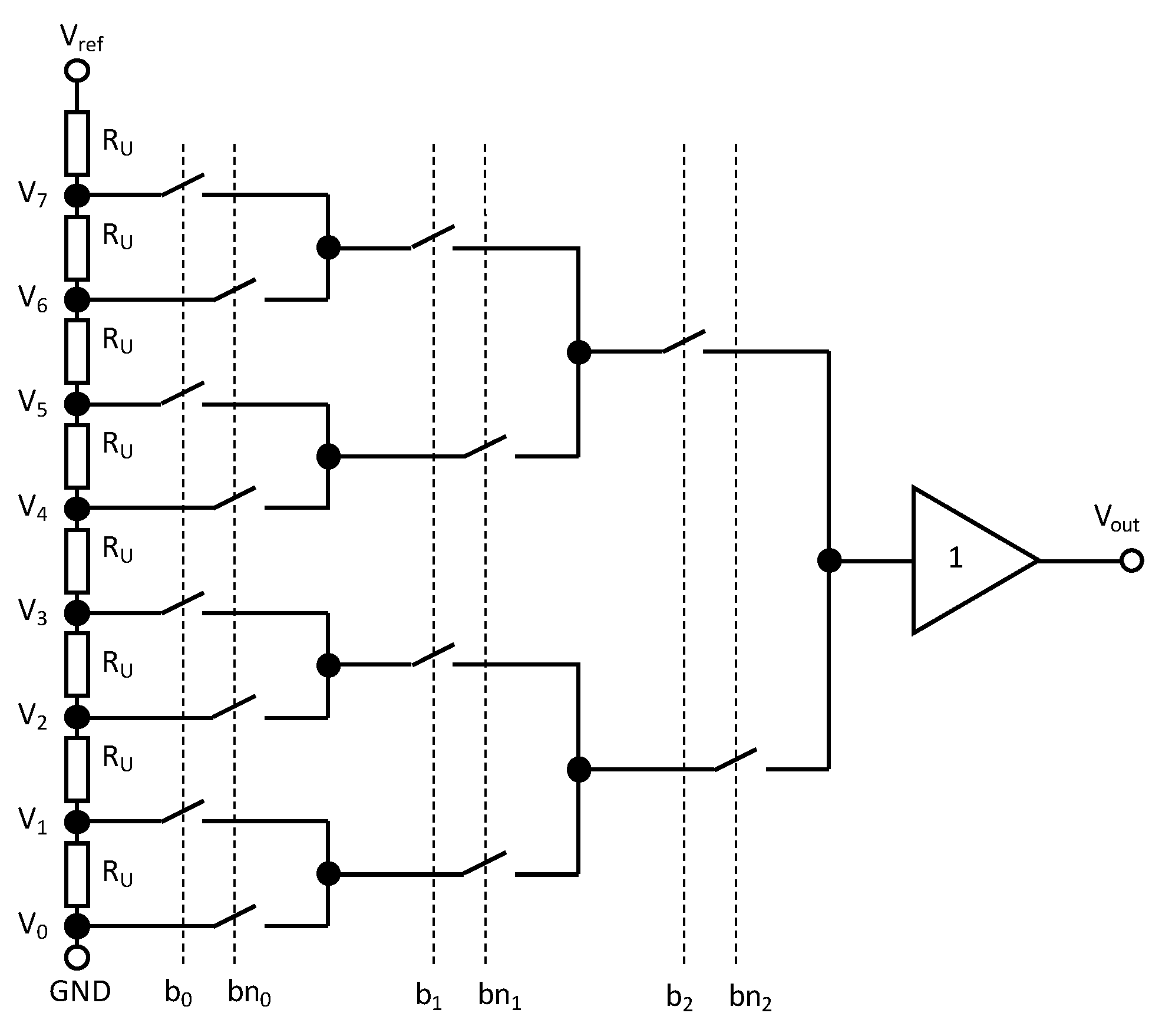

3.1. Starting Architectures

- The number of bits in the control lines is reduced;

- It is possible to keep low the time constant of the resistor matrix without using low-value unity resistors.

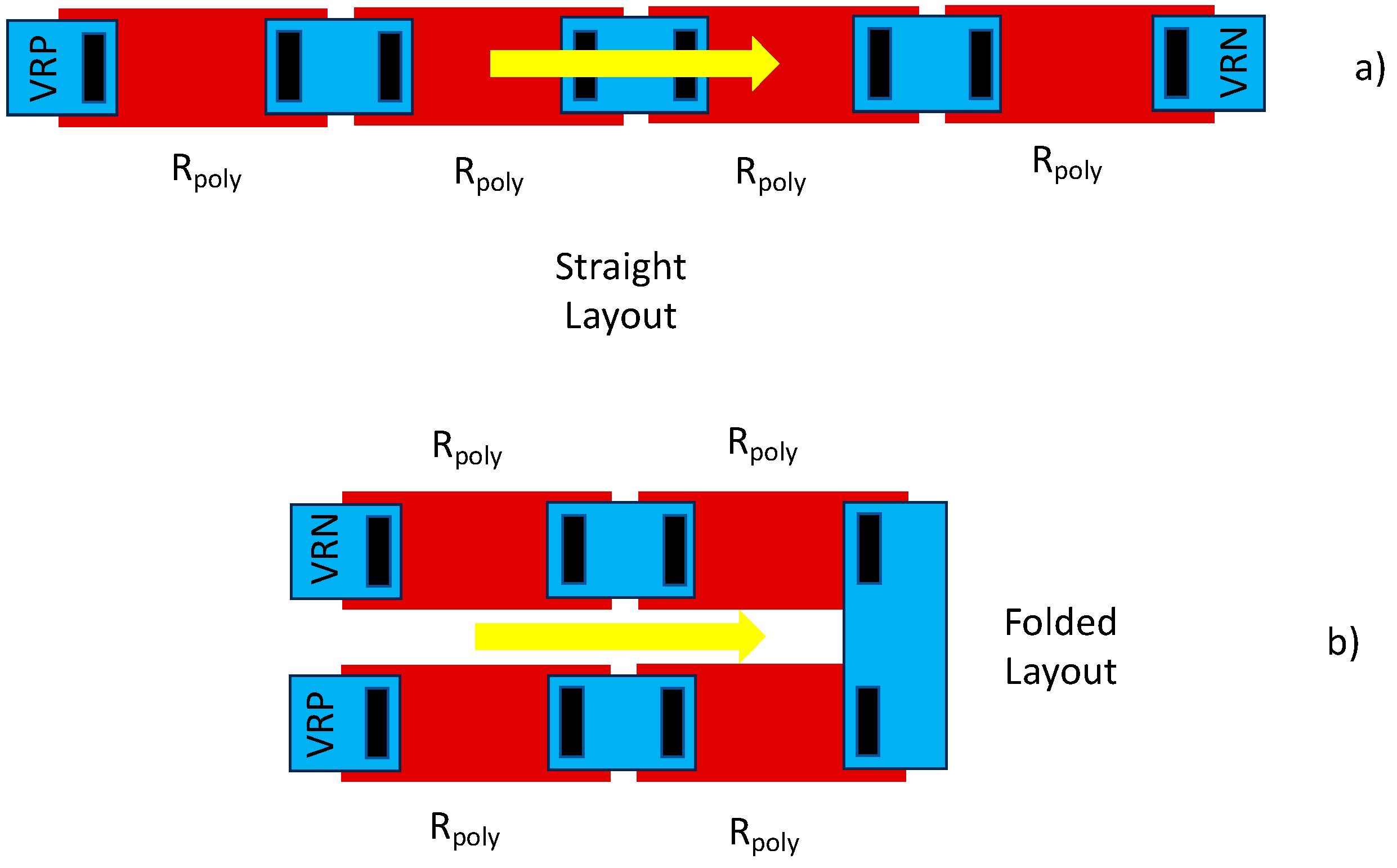

3.2. Design Strategy

- Resistor matching data;

- Resistor value;

- Radiation resiliency.

- Rhigh (high-ohmic poly-Si resistor);

- Rppd (medium-resistance poly-Si resistor);

- Rsil (salicided poly-Si resistor).

- Switches on-resistance shall be kept low (i.e., a W/L ratio higher than the minimum) for increasing speed;

- Switches’ size (W and L) shall be small for a reduced parasitic capacitance;

- Length L shall be higher than the minimum lithographic, or an ELT shape shall be adopted [23] to improve resiliency.

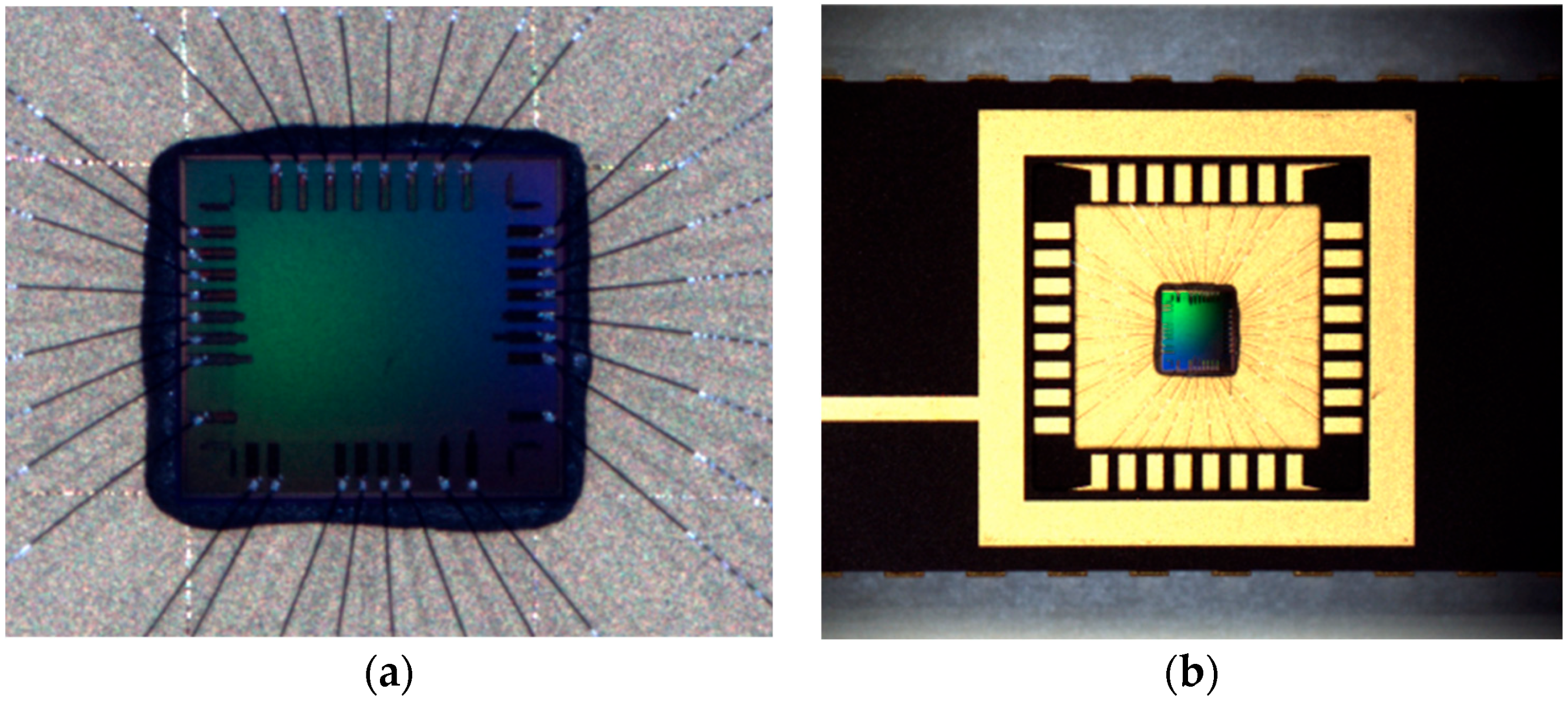

4. Test Results

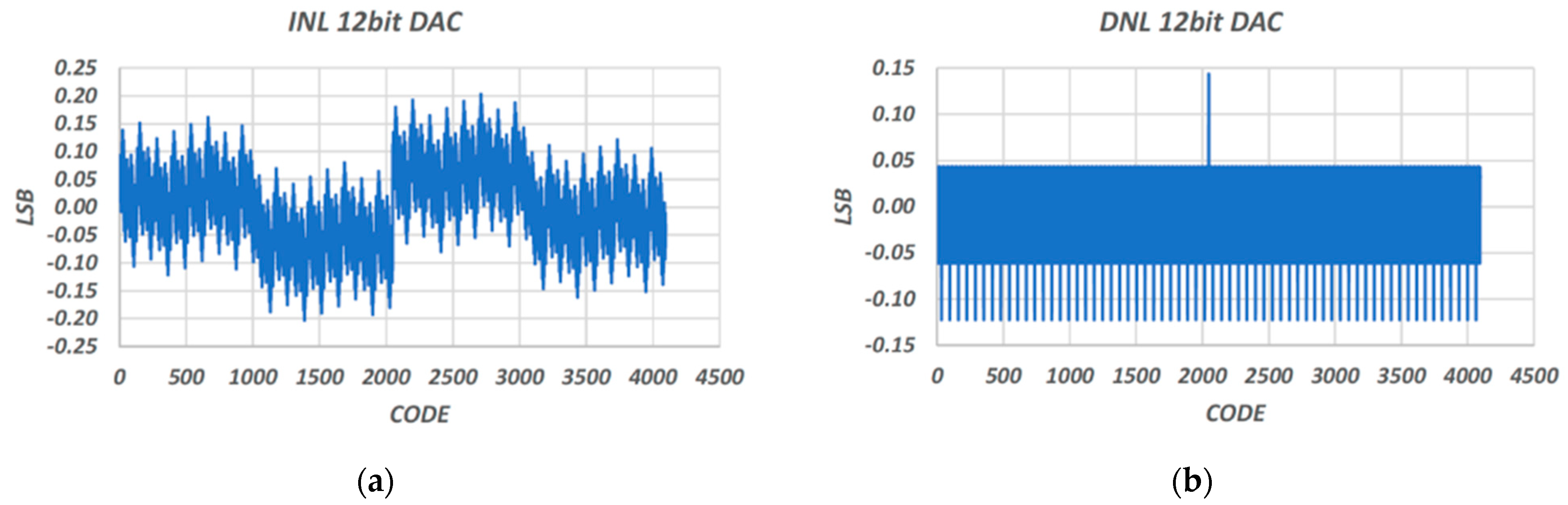

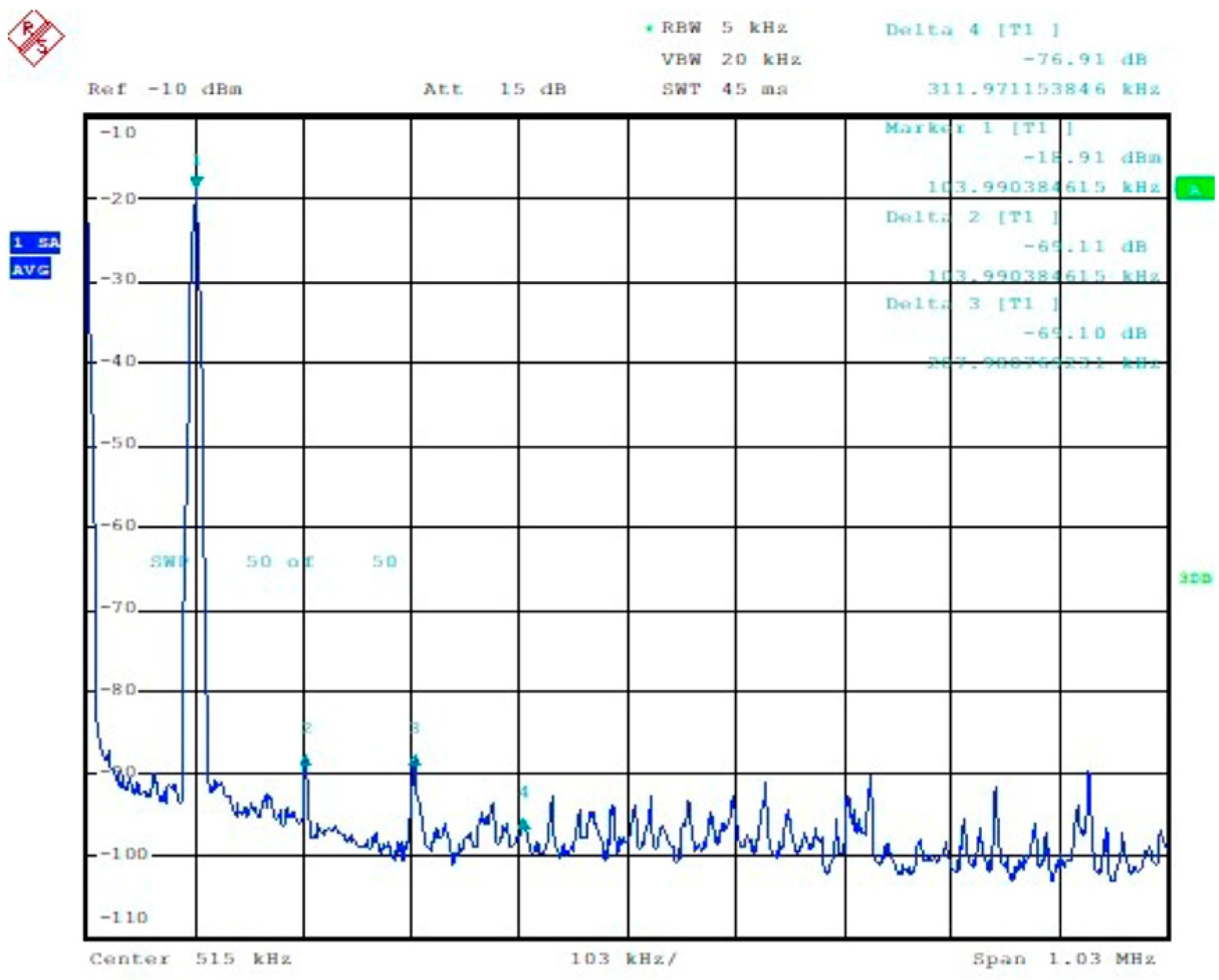

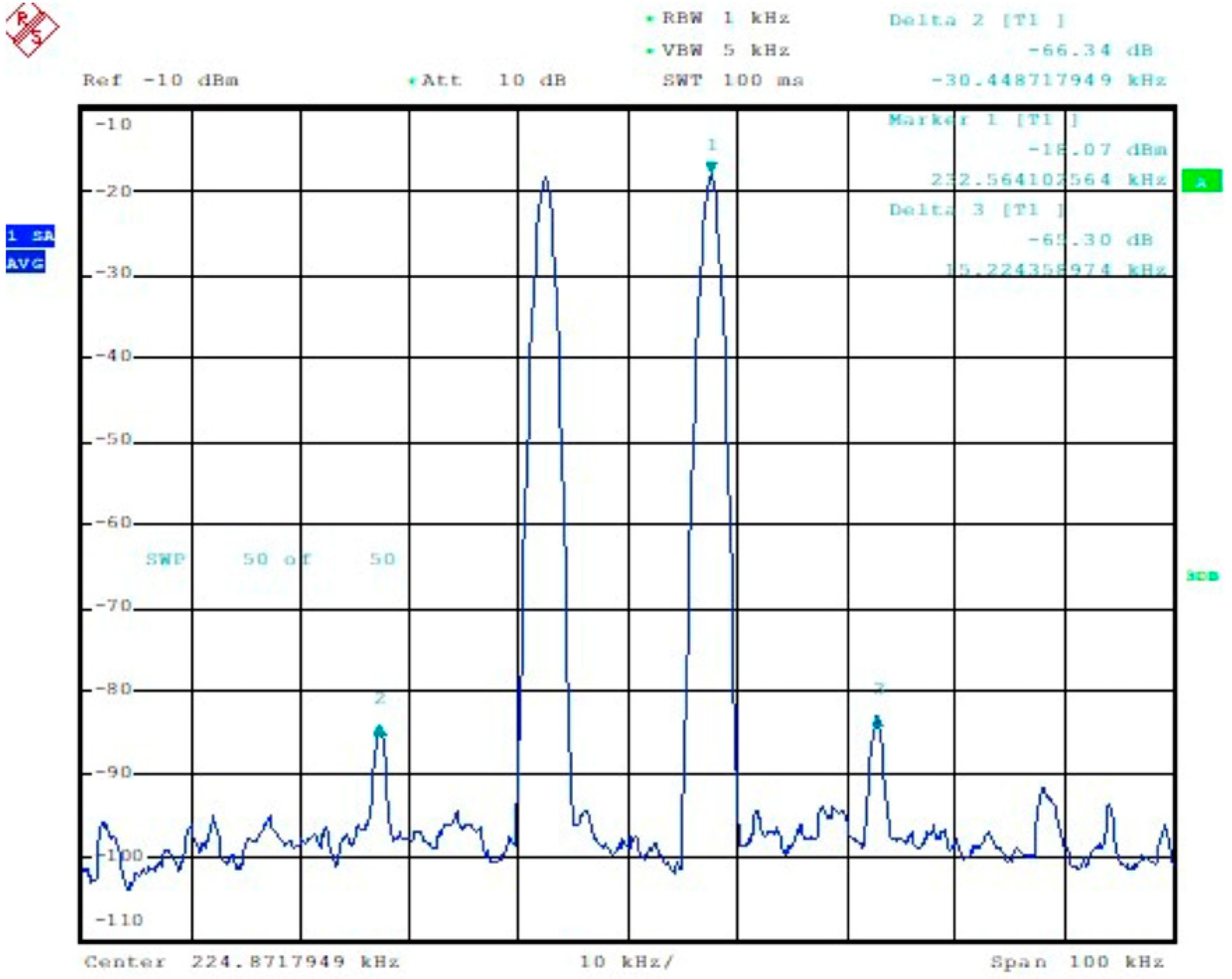

4.1. In-Lab Measurements

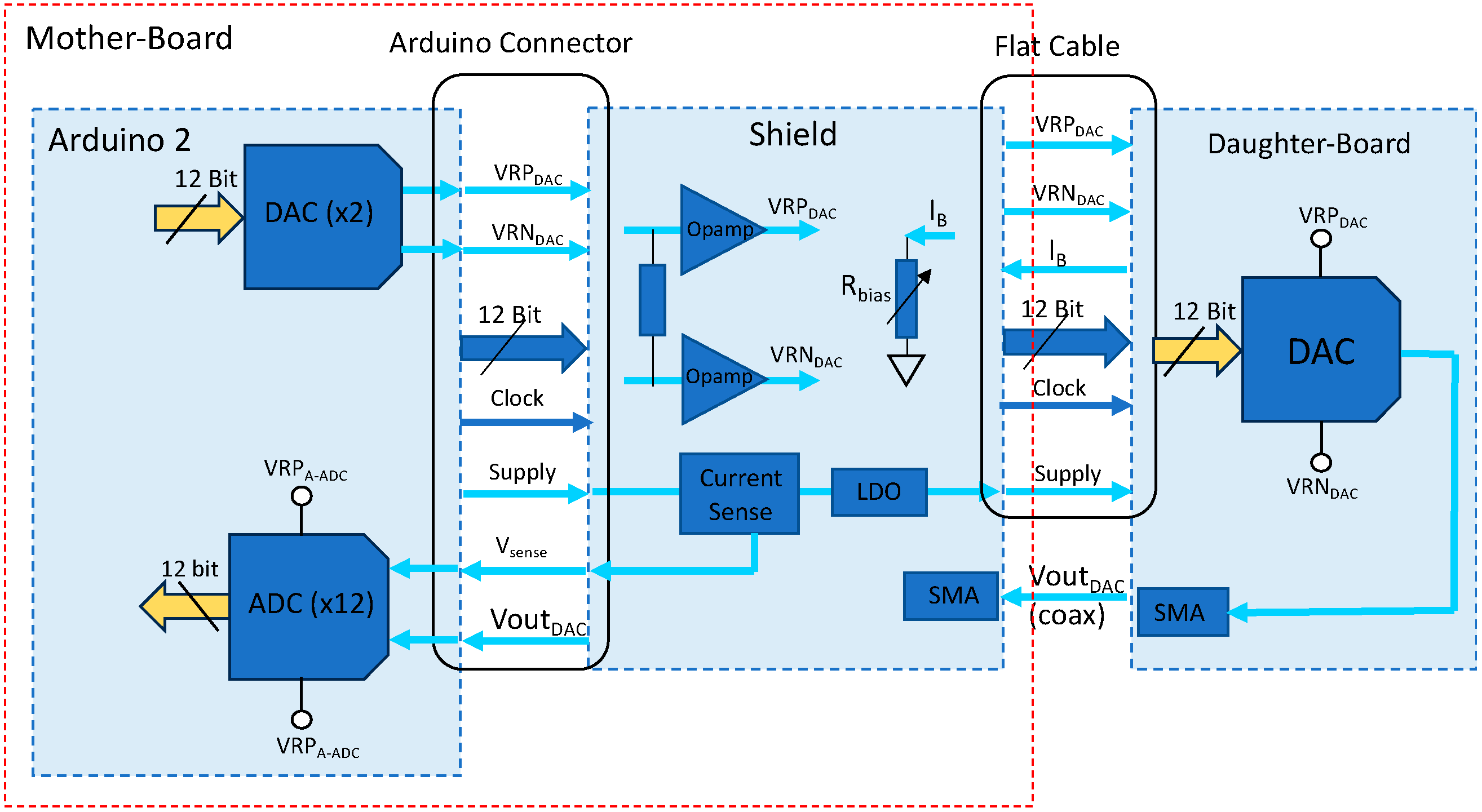

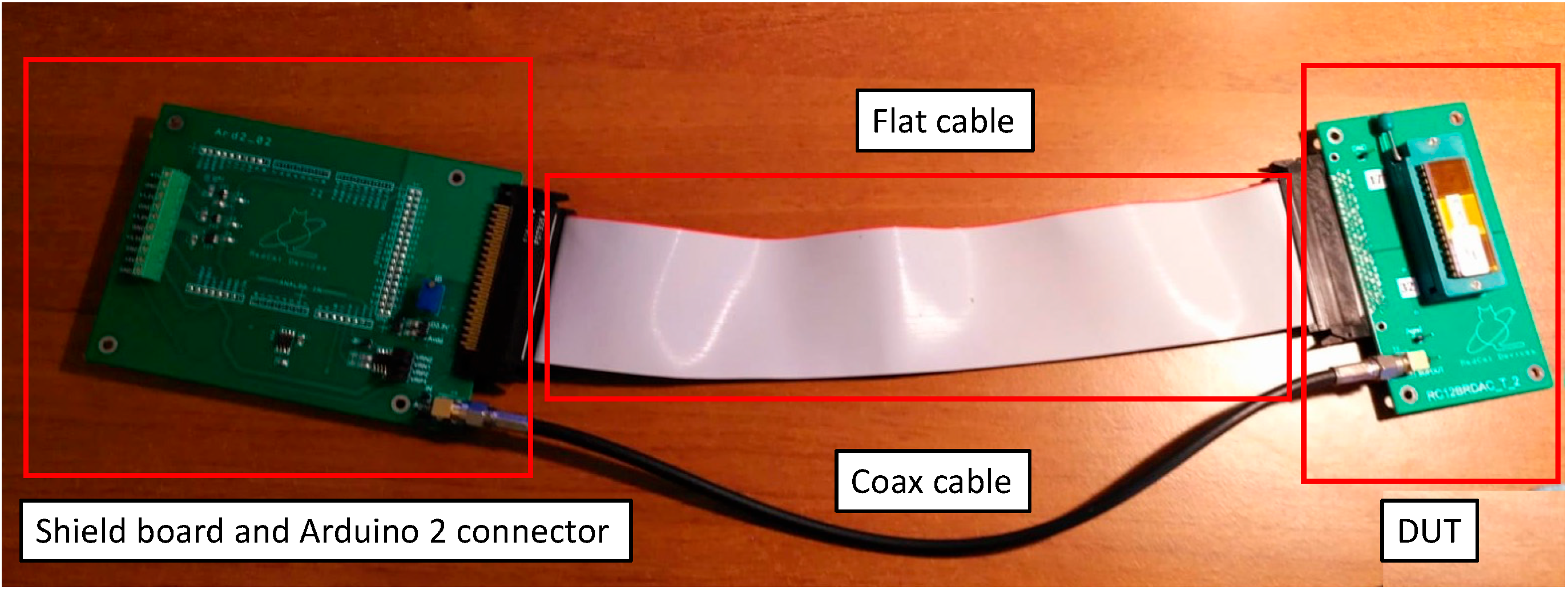

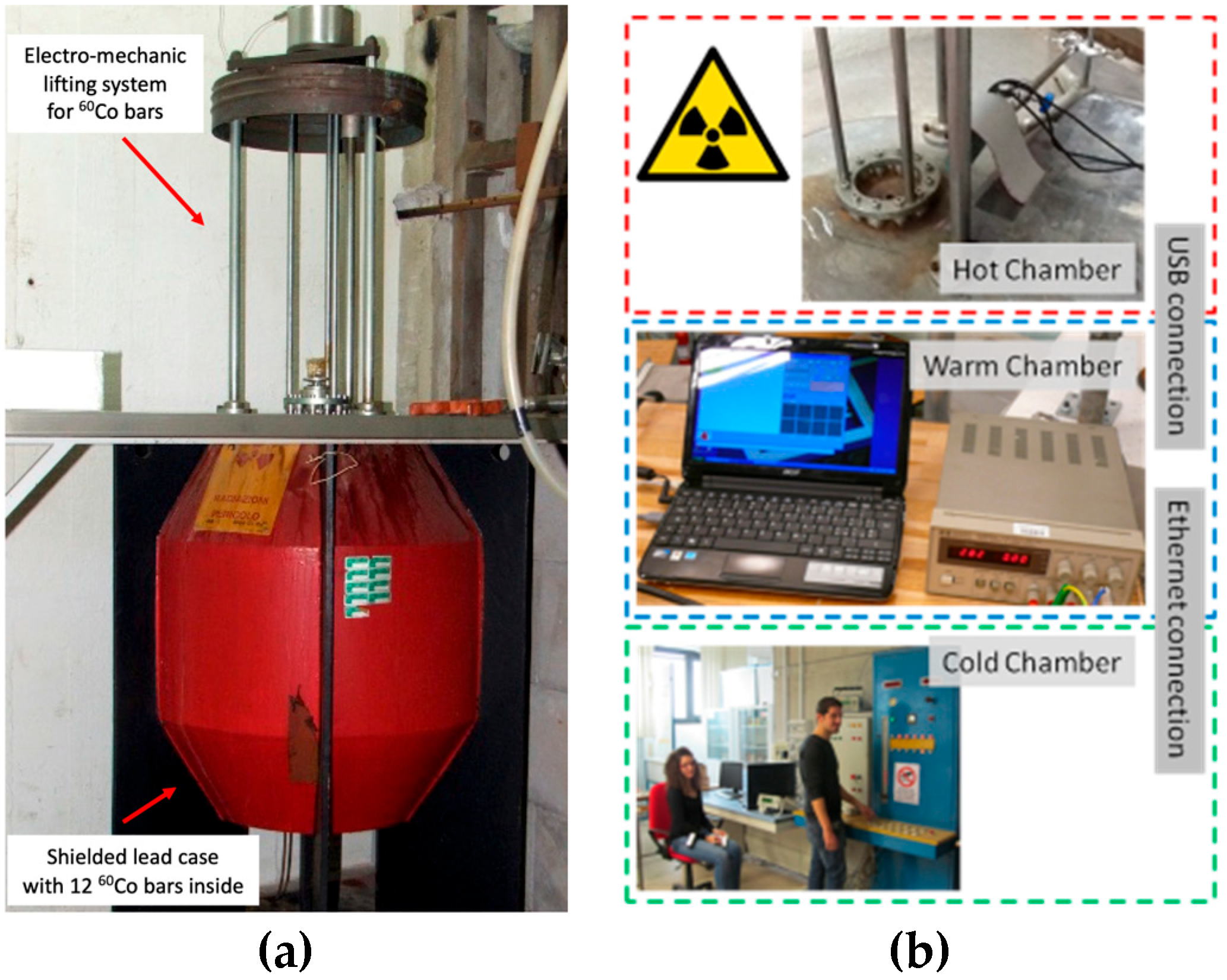

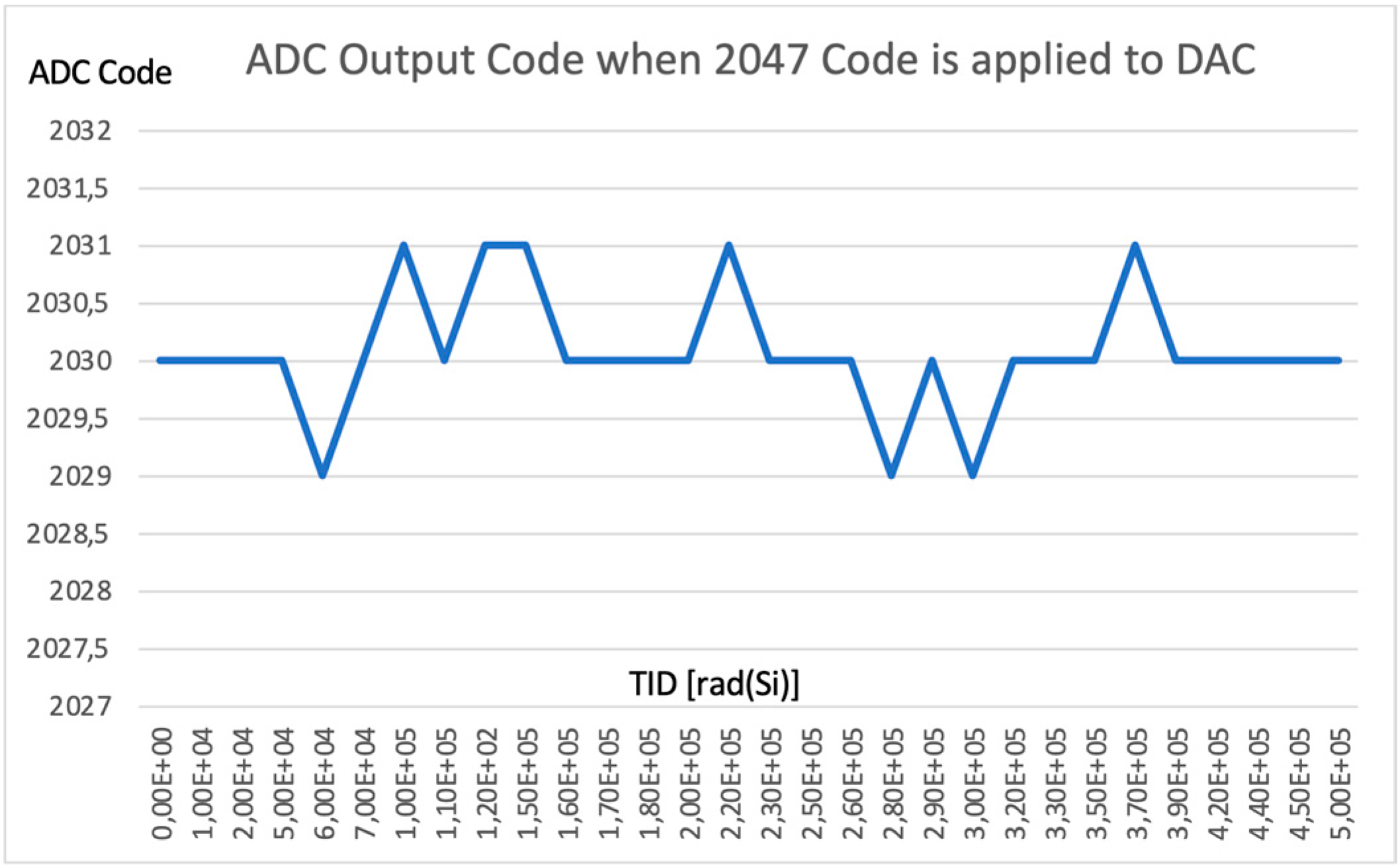

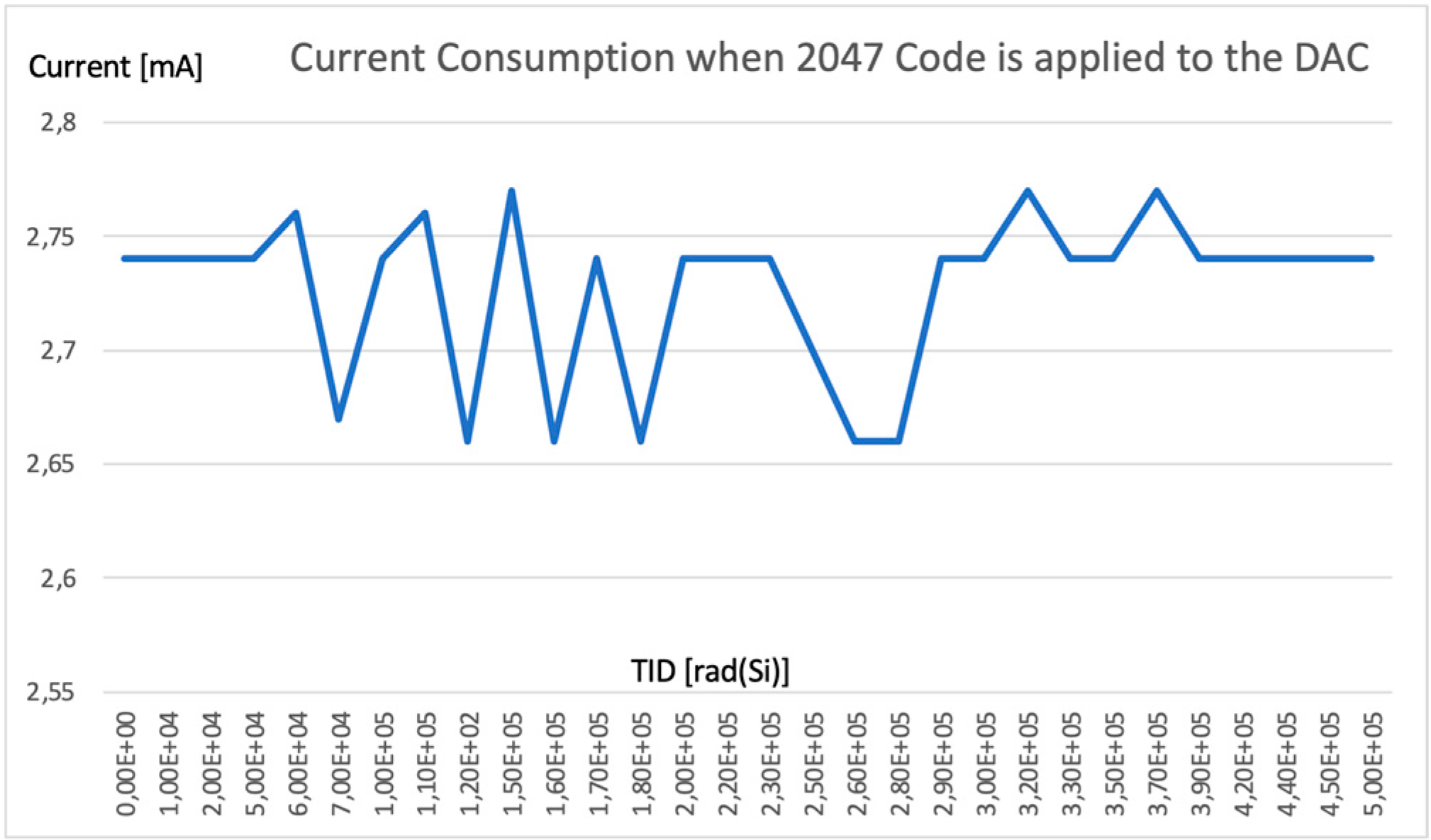

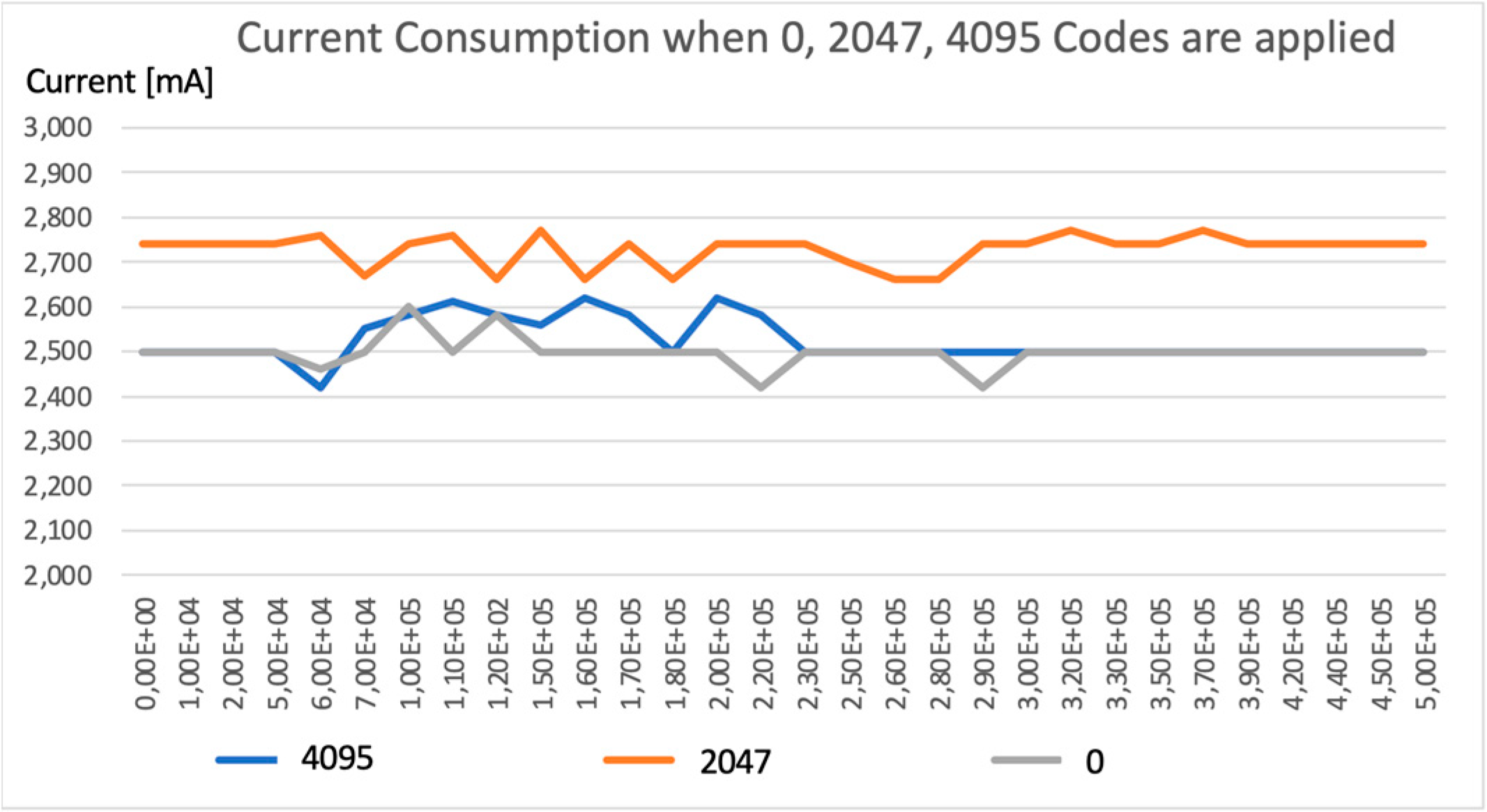

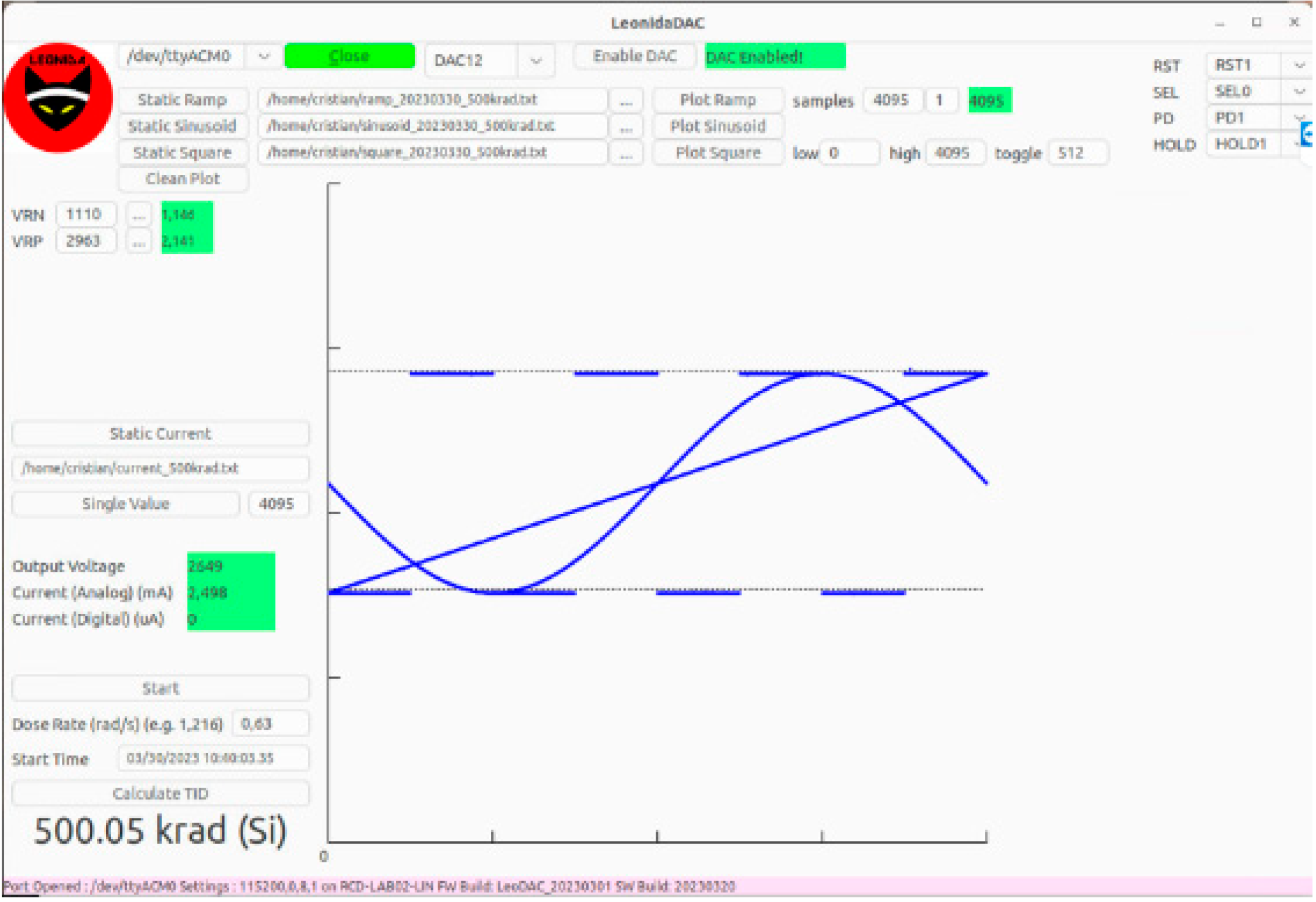

4.2. Measurements under Radiation

- A motherboard (MB), which hosts the signal generation, data acquisition system, and auxiliary circuitry;

- A daughterboard (DB) with the DUT only.

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Bourdarie, S.; Xapsos, M. The near-earth space radiation environment. IEEE Trans. Nucl. Sci. 2008, 55, 1810–1832. [Google Scholar] [CrossRef]

- Calligaro, C.; Gatti, U. Rad-Hard Semiconductor Memories; River Publisher: Nordjylland, Denmark, 2018; ISBN 9788770220200. [Google Scholar]

- Calligaro, C.; Arbat, A.; Roizin, Y.; Nahmad, D. A 15 Mrad (Si) 512Kbit Rad-Hard SRAM in a standard 0.18um CMOS technology. In Proceedings of the 3th European Conference on Radiation and its Effects on Components and Systems (RADECS) 2012, Biarritz, France, 24–28 September 2012. [Google Scholar]

- Mueller, S.; Weigel, R.; Koelpin, A. A Survey on Analog-to-Digital Converter Performance with Respect to Ionizing Radiation. In Proceedings of the 2017 17th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Geneva, Switzerland, 2–6 October 2017; pp. 1–4. [Google Scholar]

- Calligaro, C.; Gatti, U. A CMOS 10-Bit 3MS/s Rad-Hard DAC Based on Resistor String Poly-Matrix. In Proceedings of the 2021 IEEE 32nd International Conference on Microelectronics (MIEL), Nis, Serbia, 12–14 September 2021. [Google Scholar]

- Tsiligiannis, G.; Makris, K.; Lambaounas, T.; Fragopoulos, D.; Anagnostopoulos, P.; Papadas, C.; Schoellkopf, J.P.; Glass, B. A Very High Resolution DAC at 1kHz for Space Applications. In Proceedings of the 2010 NASA/ESA Conference on Adaptive Hardware and Systems, Anaheim, CA, USA, 15–18 June 2010. [Google Scholar]

- Karaolis, M.; Stafylidis, A.; Dokianaki, O.; Papathanasiou, K.; Makris, K.; Fragopoulos, D.; Papadas, C.; Glass, B. High Resolution Radiation Hardened DAC in CMOS-SOI Featuringa Return-to-Zero Matrix. In Proceedings of the AMICSA 2016, Gothenburg, Sweden, 12–16 June 2016. [Google Scholar]

- Cressler, G.; Mantooth, H. (Eds.) Extreme Environment Electronics; CRC Press: Boca Raton, FL, USA, 2013. [Google Scholar]

- Axness, C.L.; Riewe, L.; Reber, R.A.; Liang, A.Y.; Ang, S.S.; Brown, W.D. Radiation Characteristics of SIPOS and Polysilicon Resistors. IEEE Trans. Nucl. Sci. 1991, 38, 1365–1369. [Google Scholar] [CrossRef]

- Irom, F.; Agarwal, S.G. Compendium of Single-Event Latchup and Total Ionizing Dose Test Results of Commercial Digital to Analog Converters. In Proceedings of the. 2015 IEEE Radiation Effects Data Workshop (REDW), Boston, MA, USA, 13–17 July 2015. [Google Scholar]

- Stone, S.E.; Lombardi, R.E.; Seehra, S.S.; Likar, J.J.; Begovic, J.; Herschitz, R. Single Event Effects Characterization of Maxwell 7846B DAC. In Proceedings of the 2012 IEEE Radiation Effects Data Workshop, Miami, FL, USA, 16–20 July 2012. [Google Scholar]

- Karakozov, A.B.; Nekraso, P.V.; Bobrovsky, D.V.; Sorokoumov, G.S.; Telets, V.A. Single Event Effects and Total Dose Testing of Digital to Analog Converters. In Proceedings of the 17th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Geneva, Switzerland, 2–6 October 2017. [Google Scholar]

- Daniel, A.C.; Vartanian, S.; Allen, G.R. Radiation Effects Characterization of Commercial Multi-Channel Digital to Analog Converters for Spaceflight Applications. In Proceedings of the 2019 IEEE Radiation Effects Data Workshop, San Antonio, TX, USA, 8–12 July 2019. [Google Scholar]

- Kruckmeyer, K.; Prater, J.S.; Brown, B.; Trinh, T. Analysis of Low Dose Rate Effects on Parasitic Bipolar Structures in CMOS Processes for Mixed-Signal Integrated Circuits. IEEE Trans. Nucl. Sci. 2011, 58, 1023–1031. [Google Scholar] [CrossRef]

- Fan, H.; Li, D.; Zhang, K.; Cen, Y.; Feng, Q.; Qiao, F.; Heidari, H. A 4-Channel 12-Bit High-Voltage Radiation-Hardened Digital-to-Analog Converter for Low Orbit Satellite Applications. IEEE Trans. Circuits Syst.–I 2018, 65, 3698–3706. [Google Scholar] [CrossRef]

- Chen, Z.; Dai, F.F. A 3mW 8-Bit Radiation-hardened-by-design DAC for Ultra-wide Temperature Range from −180 °C to 120 °C. In Proceedings of the 2011 IEEE International Symposium of Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, 15–18 May 2011; pp. 997–1000. [Google Scholar]

- Kim, D.; Kwon, I.; Kim, C.-H. A 10-bit Radiation-Hardened R-2R Digital-to-Analog Converter for Nuclear Power Plant Applications. In Proceedings of the Transactions of the Korean Nuclear Society Spring Meeting, Jeju, Republic of Korea, 23–24 May 2019. [Google Scholar]

- Yao, Y.; Dai, F.; Jaeger, R.C.; Cressler, J.D. A 12-Bit Cryogenic and Radiation-Tolerant Digital-to-Analog Converter for Aerospace Extreme Environment Applications. IEEE Trans. Ind. Electron. 2008, 55, 2810–2818. [Google Scholar]

- Kunnath, A.T.; Sahoo, B. A Digitally Assisted Radiation Hardened Current Steering DAC. In Proceedings of the 2016 29th International Conference on VLSI Design and 2016 15th International Conference on Embedded Systems (VLSID), Kolkata, India, 4–8 January 2016; pp. 559–560. [Google Scholar]

- Dugoujon, L.; Papadas, C.; Sinnis, B. A 0.13 µm CMOS Rad-hard proven technology with associated mixed mode circuit design approaches for space applications. In Proceedings of the AMICSA, Xanthi, Greece, 2–3 October 2006. [Google Scholar]

- Haddad, N.F.; Kelly, A.T.; Lawrence, R.K.; Li, B.; Rodgers, J.C.; Ross, J.F.; Warren, K.M.; Weller, R.A.; Mendenhall, M.H.; Reed, R.A. Incremental enhancement to SEU hardened 90 nm CMOS memory cell. In Proceedings of the RADECS 2010, Längenfeld, Austria, 20–24 September 2010. [Google Scholar]

- Clark, L.T.; Mohr, K.C.; Holbert, K.E.; Yao, X.; Knudsen, J.; Shah, H. Optimizing Radiation Hard by Design SRAM Cells. IEEE Trans. Nucl. Sci. 2007, 54, 2028–2036. [Google Scholar] [CrossRef]

- Anelli, G.; Campbell, M.; Delmastro, M.; Faccio, F.; Floria, S.; Giraldo, A.; Heijne, E.; Jarron, P.; Kloukinas, K.; Marchioro, A.; et al. Radiation Tolerant VLSI Circuits in Standard Deep Submicron CMOS Technologies for the LHC Experiments: Practical Design Aspects. IEEE Trans. Nucl. Sci. 1999, 46, 1690–1696. [Google Scholar] [CrossRef]

- Jacob Baker, R. (Ed.) CMOS Circuit Design, Layout, and Simulation; IEEE Press: Piscataway, NJ, USA, 1998. [Google Scholar]

- Pelgrom, M. A 50 MHz 10-bit CMOS digital-to-analog converter with 75 Ω buffer. J. Solid-State Circuits 1990, 25, 1347–1352. [Google Scholar] [CrossRef]

- Gatti, U.; Calligaro, C.; Pikhay, E.; Roizin, Y. Radiation-hardening methodologies for Flash ADC. Analog Integr. Circuits Signal Process. 2016, 87, 141–154. [Google Scholar] [CrossRef]

- Maloberti, F. Analog Design for CMOS VLSI Systems; Springer: Berlin/Heidelberg, Germany, 2001. [Google Scholar]

- Vergine, T.; De Matteis, M.; Michelis, S.; Traversi, G.; De Canio, F.; Baschirotto, A. A 65 nm Rad-Hard Bandgap Voltage Reference for LHC Environment. IEEE Trans. Nucl. Sci. 2016, 63, 1762–1767. [Google Scholar] [CrossRef]

- Verbeeck, J.; Leroux, P.; Steyaert, M. Radiation effects upon the mismatch of identically laid out transistor pairs. In Proceedings of the 2011 IEEE ICMTS International Conference on Microelectronic Test Structures, Amsterdam, The Netherlands, 4–7 April 2011; pp. 194–197. [Google Scholar]

- Burns, M.; Roberts, G.W. An Introduction to Mixed-Signal IC Test and Measure; Oxford University Press: Oxford, UK, 2001. [Google Scholar]

- Available online: https://docs.arduino.cc/hardware/due/ (accessed on 18 April 2023).

- Kuentzer, F.; Tittlebach-Helmrich, K.; Cueto, J.; Garcia Donday, F.; Schmidt, M.; Schommer, B.; Ferdinand, C.; Soding-Freiherr von Blomberg, A.; Calligaro, C.; Gatti, U. Rad-hard Microcontroller with Open Access ISA for Space Applications. In Proceedings of the 9th International Workshop on Analogue and Mixed-Signal Integrated Circuits for Space Applications, Madrid, Spain, 31 May–3 June 2022. [Google Scholar]

| Resistive | Capacitive | Curr. Steer. | |

|---|---|---|---|

| TID | K | K | Λ |

| SET | ϑ | Λ | ϑ |

| SEL | K | K | K |

| RHBD-AL | Low | High | High |

| RHBD-CL | Medium | Medium | High |

| RHBD-LL | Medium | Medium | Medium |

| This Work | [15] | [18] | [16] | [17] ** | [19] | |

|---|---|---|---|---|---|---|

| Resolution | 12 bits | 12 bits | 8 bits | 12 bits | 12 bits | 10 bits |

| Technology | 130 nm CMOS | 0.5 um BiCMOS | 0.5 um SiGe BiCMOS | 0.5 um SiGe BiCMOS | 65 nm CMOS | 130 nm CMOS |

| Architecture | X-Y R Matrix | R-2R | R-2R | Segmented Current Steering | Current Steering | Current Steering |

| Data Rate | 3 MS/s | 100 kS/s | 10 MS/s | 80 MS/s | NA | 15 MS/s |

| DNL | ±0.15 LSB | ±0.23 LSB | ±0.2 LSB | NA | NA | NA |

| INL | ±0.2 LSB | ±0.67 LSB | ±0.3 LSB | NA | NA | NA |

| SFDR | 69 dBc | NA | 55 dBc | 54 dBc | NA | NA |

| ENOB | 9.5 bits | NA | NA | NA | NA | 8.73 bits |

| TID | 500 krad (Si) | 20 krad (Si) | NA | 300 krad (Si) | 100 Mrad (Si) | NA |

| Supply | +3.3 V | ±15 V | +3.3 V | +3.3 V | +1.2 V | +1.2 V |

| Area | 2.24 mm2 | 20 mm2,* | 0.25 mm2 | 6.3 mm2,*** | NA | NA |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Calligaro, C.; Gatti, U. A CMOS 12-Bit 3MS/s Rad-Hard Digital-to-Analog Converter Based on a High-Linearity Resistor String Poly-Matrix. Chips 2024, 3, 129-152. https://doi.org/10.3390/chips3020006

Calligaro C, Gatti U. A CMOS 12-Bit 3MS/s Rad-Hard Digital-to-Analog Converter Based on a High-Linearity Resistor String Poly-Matrix. Chips. 2024; 3(2):129-152. https://doi.org/10.3390/chips3020006

Chicago/Turabian StyleCalligaro, Cristiano, and Umberto Gatti. 2024. "A CMOS 12-Bit 3MS/s Rad-Hard Digital-to-Analog Converter Based on a High-Linearity Resistor String Poly-Matrix" Chips 3, no. 2: 129-152. https://doi.org/10.3390/chips3020006

APA StyleCalligaro, C., & Gatti, U. (2024). A CMOS 12-Bit 3MS/s Rad-Hard Digital-to-Analog Converter Based on a High-Linearity Resistor String Poly-Matrix. Chips, 3(2), 129-152. https://doi.org/10.3390/chips3020006