Front-End Prototype ASIC with Low-Gain Avalanche Detector Sensors for the ATLAS High Granularity Timing Detector †

Abstract

1. Introduction

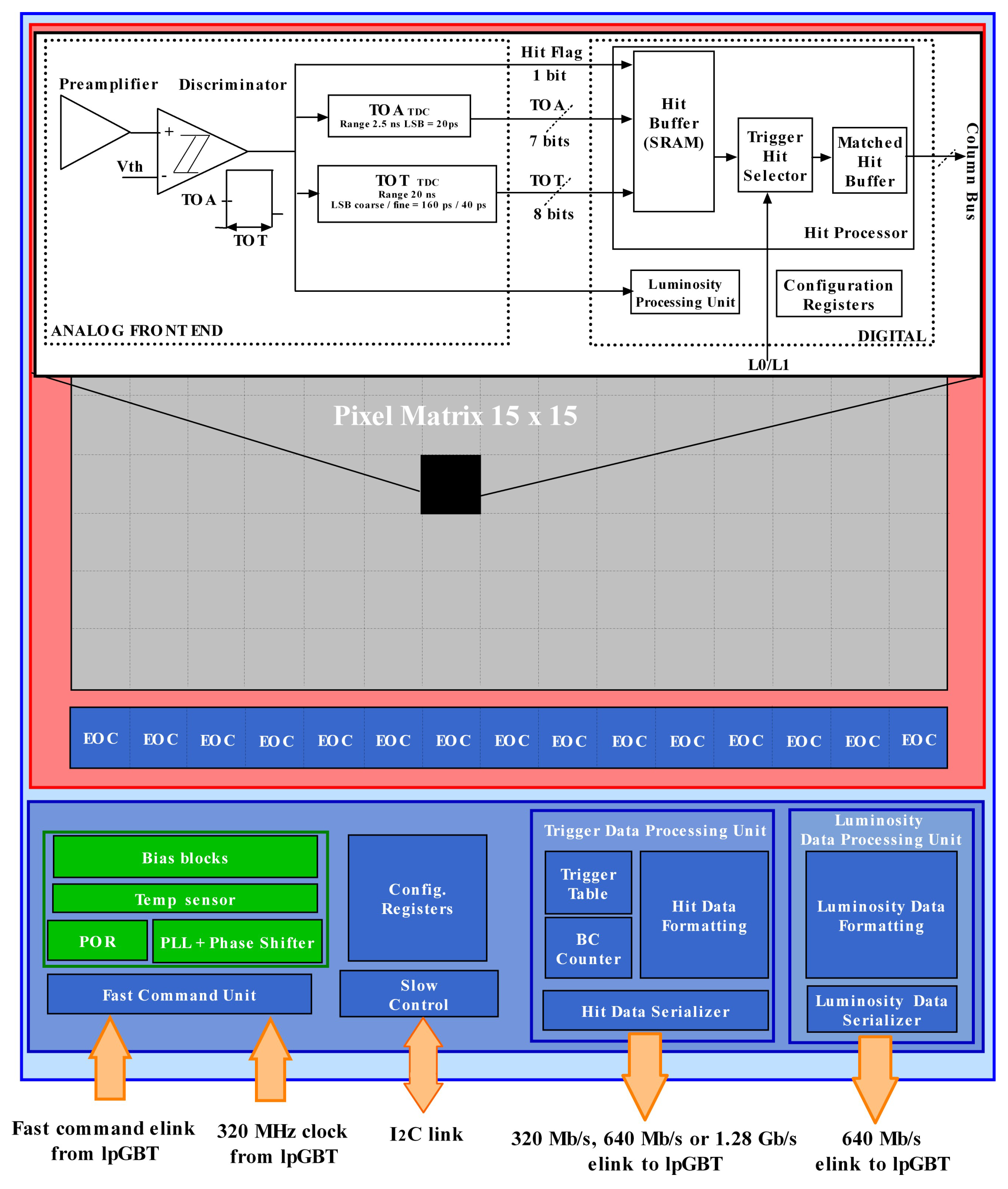

2. Front-End Readout System ASIC

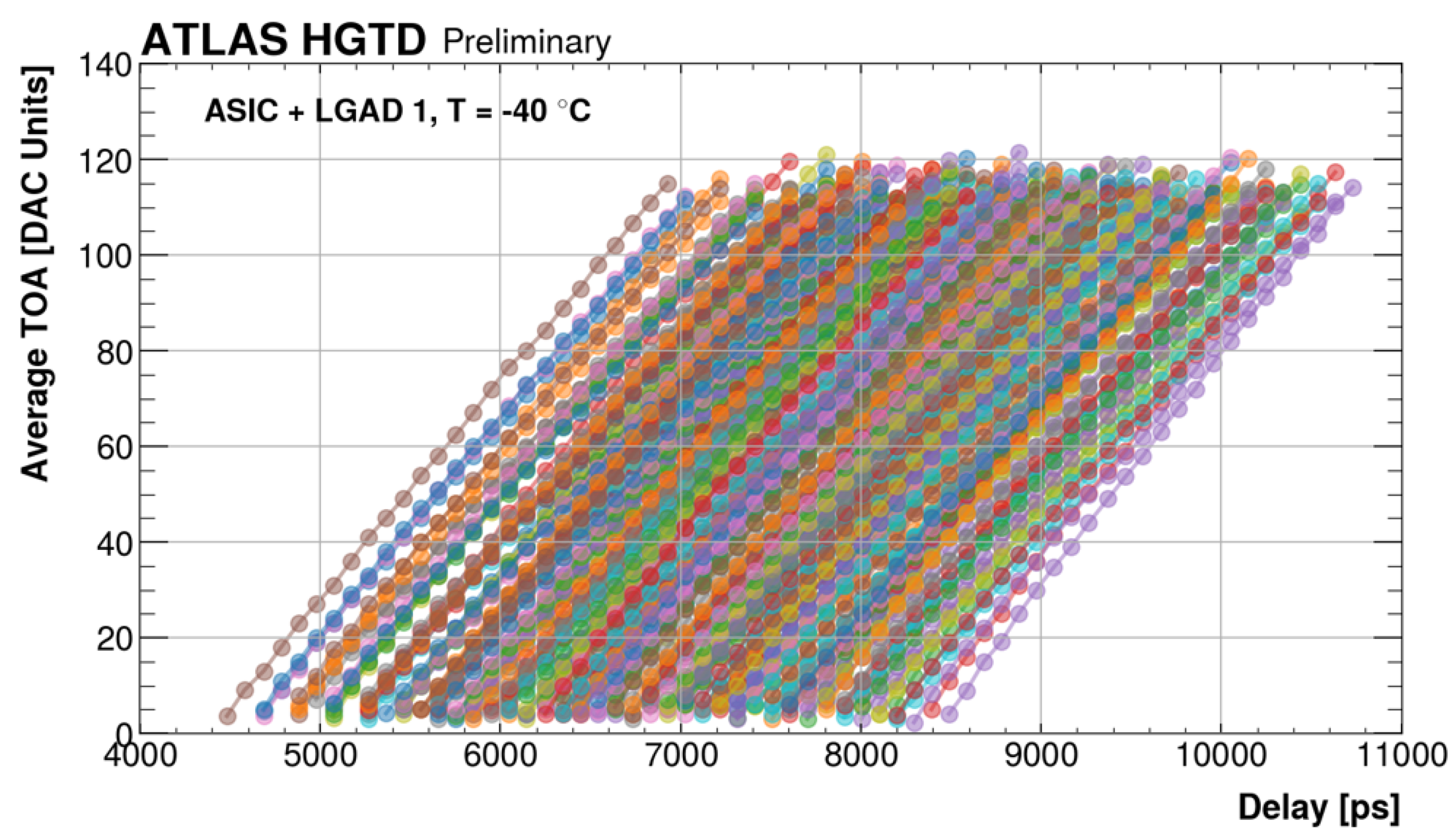

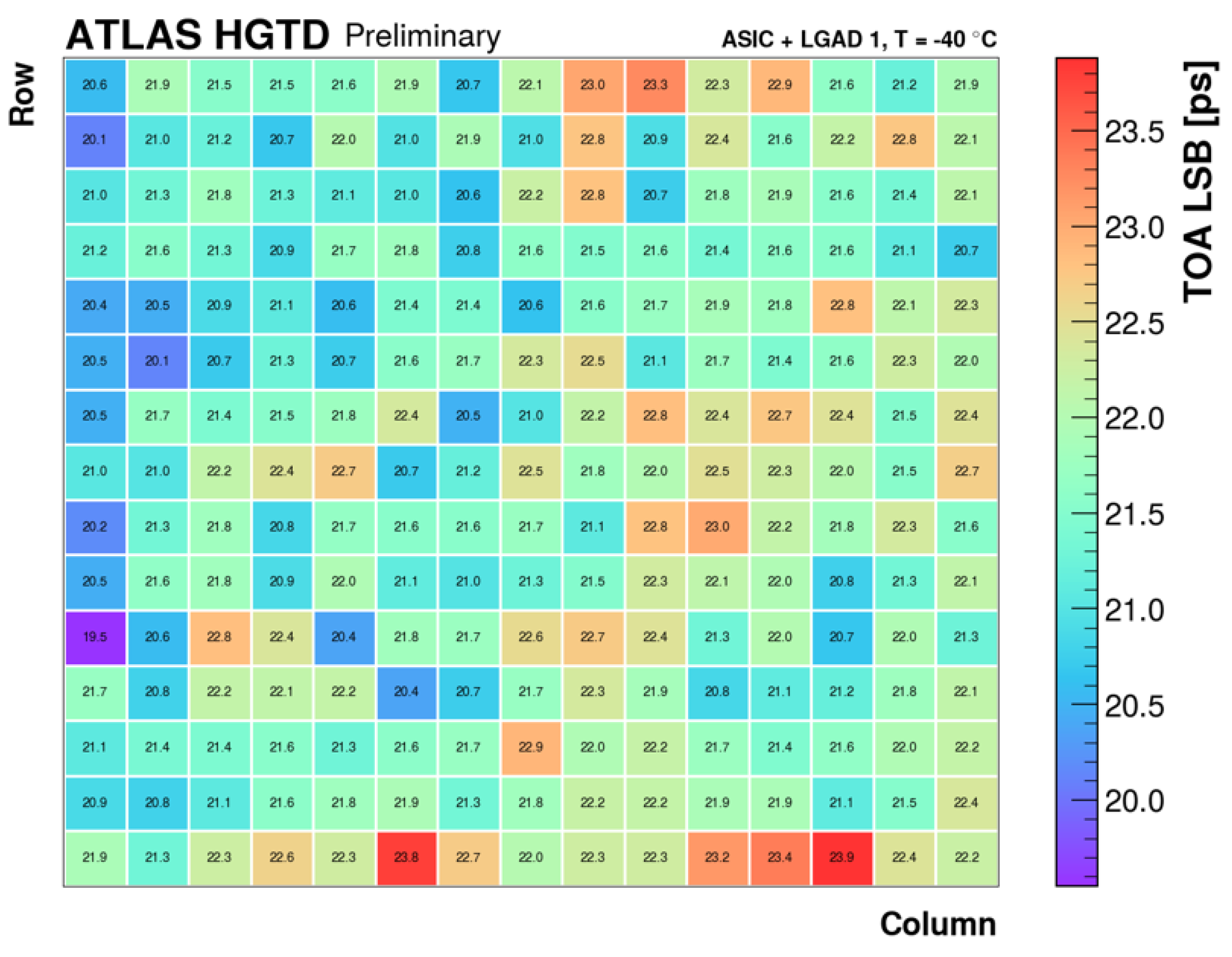

2.1. TOA TDC Calibration

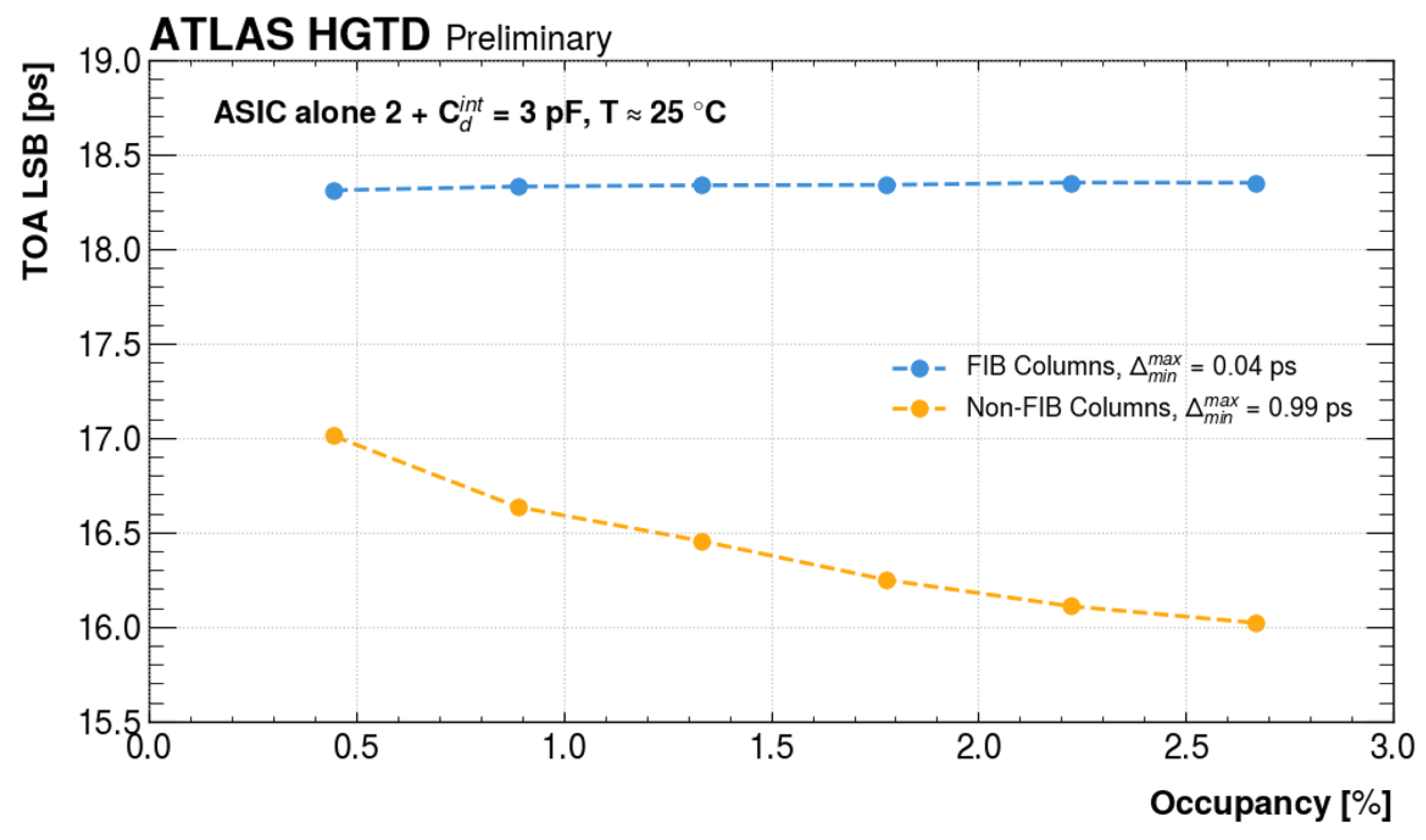

2.2. TOA LSB vs. Occupancy

- The column pattern, where we start by injecting in pixel i, then we keep adding pixels from the same column until we fill all of them, and then we move to the next column.

- The row pattern, where we start by injecting in pixel i, then we keep adding pixels from the same row until we fill all of them, and then we move to the next row.

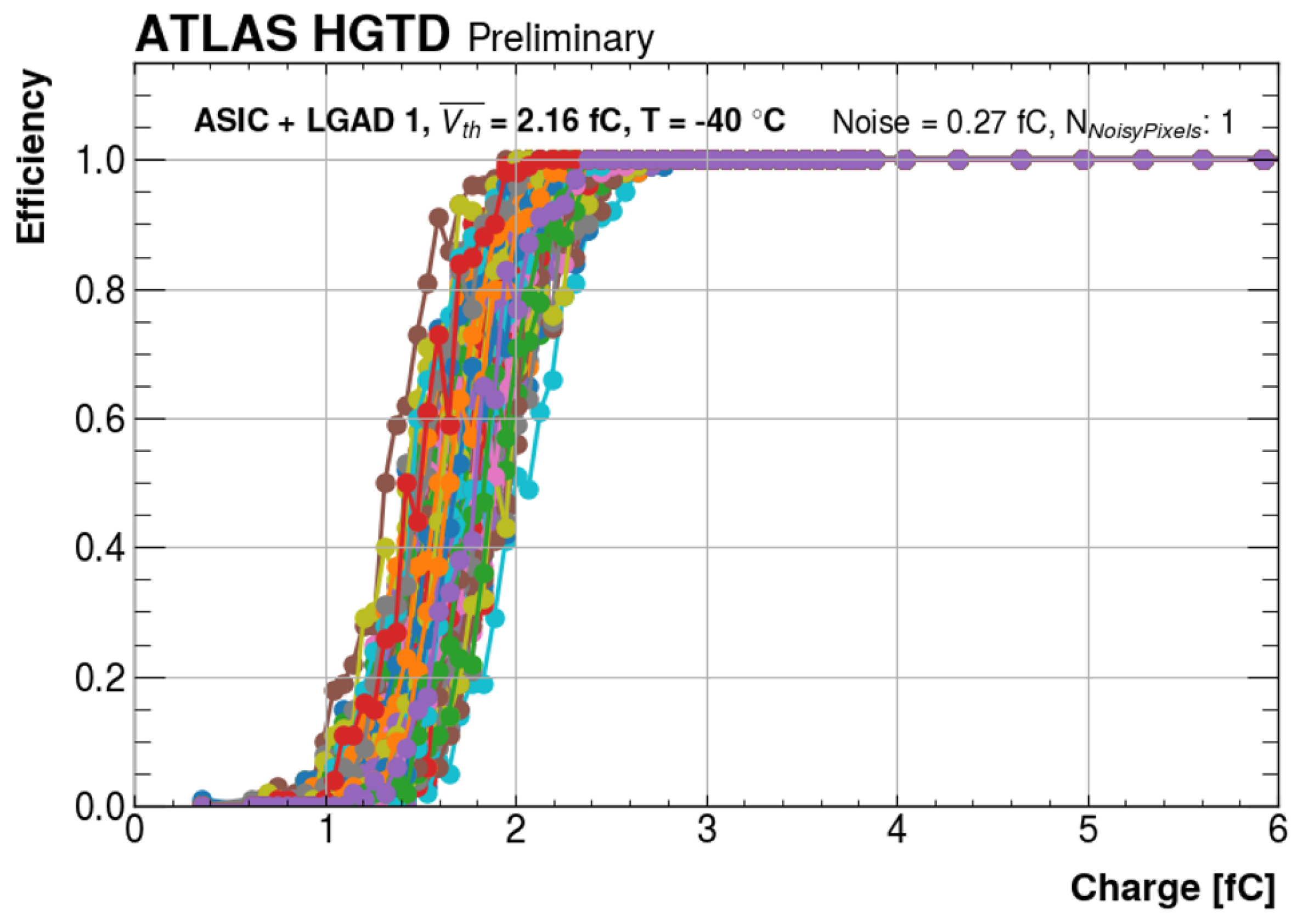

2.3. Minimal Detectable Charge

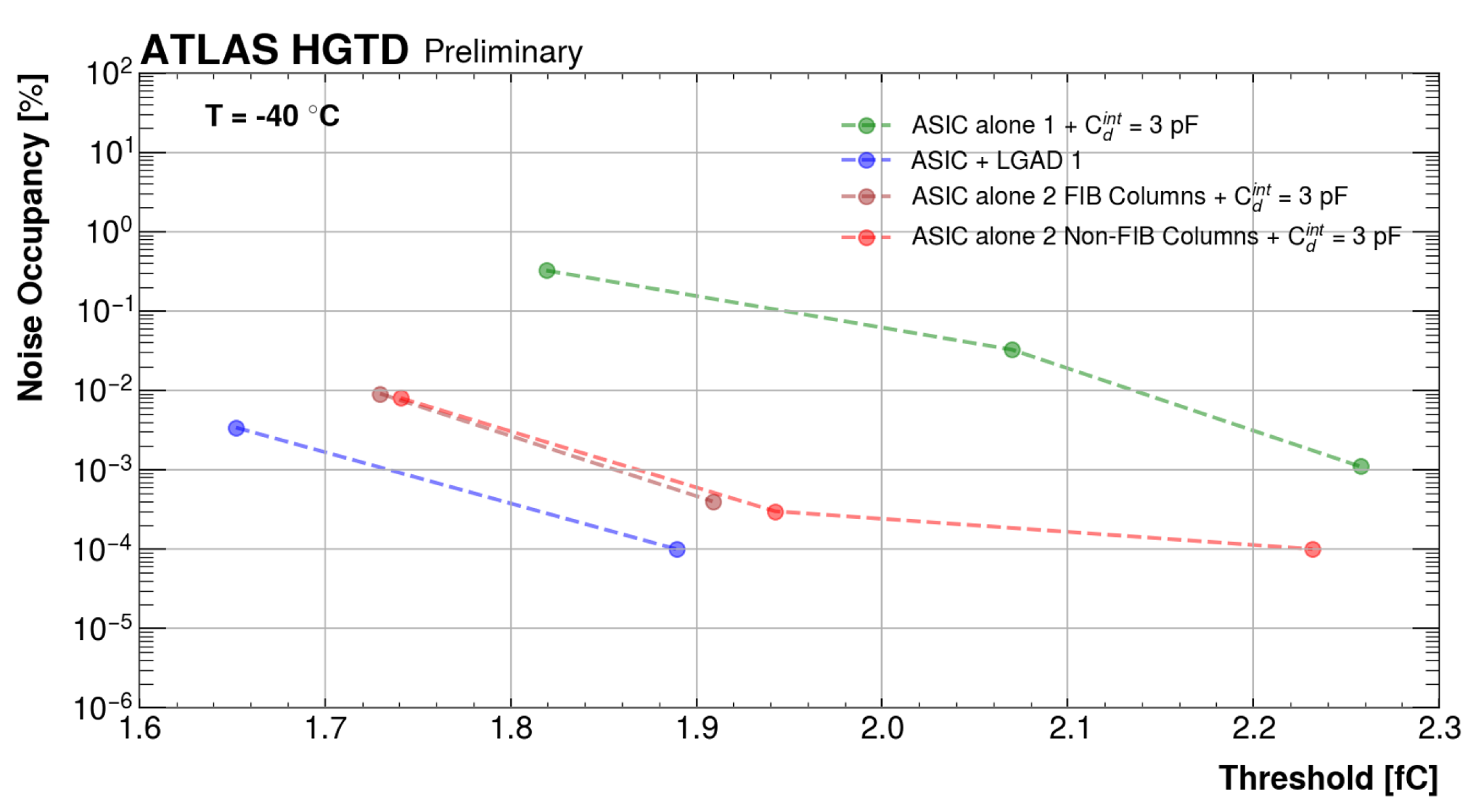

2.4. Noise

2.5. Jitter

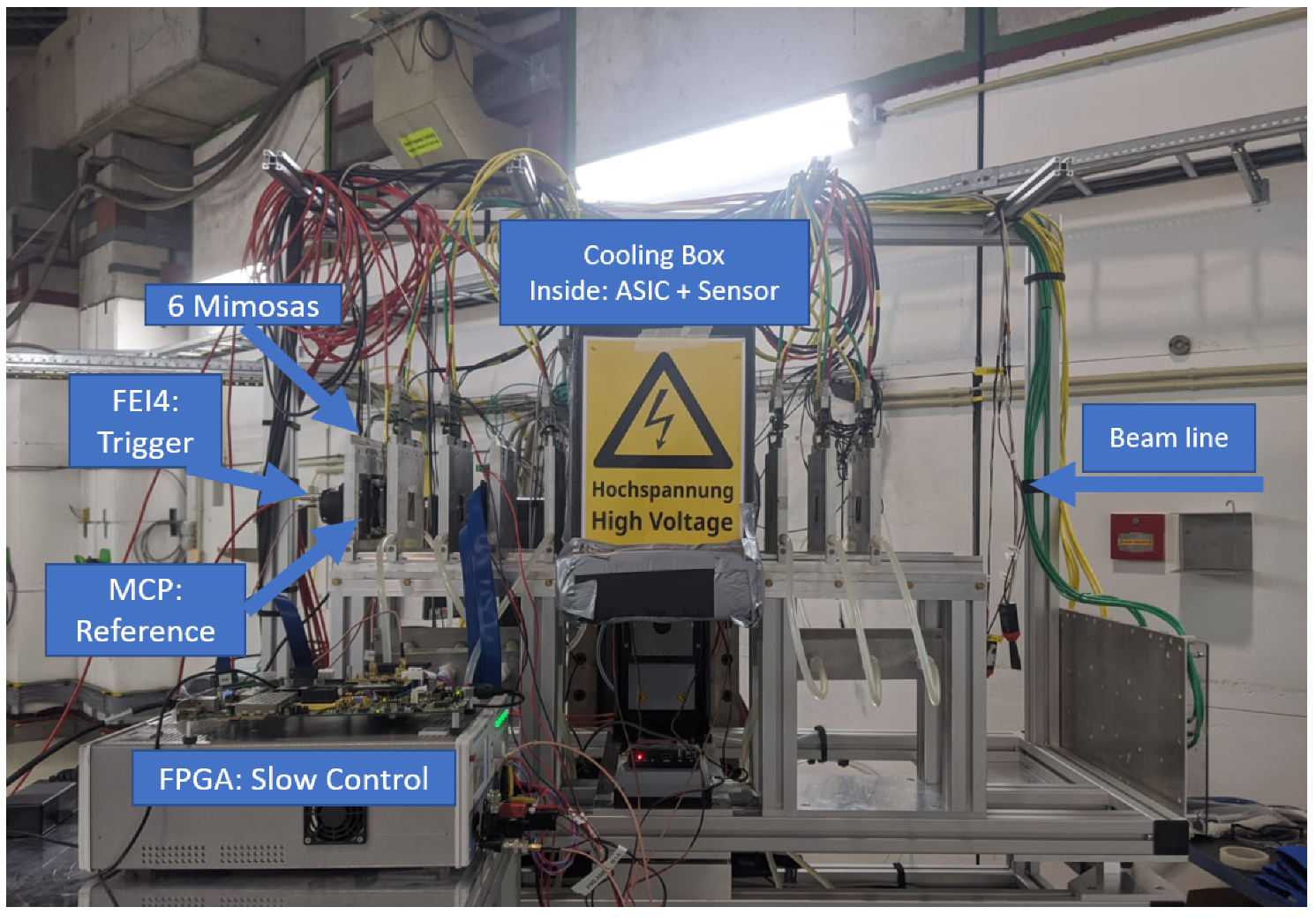

3. Test Beam Measurements

3.1. Setup

- LSB is the least significant bit of the chosen pixel.

- TOA is the Time of Arrival.

- is the front end time of the 40 MHz clock signal.

- is the time of the MCP signal.

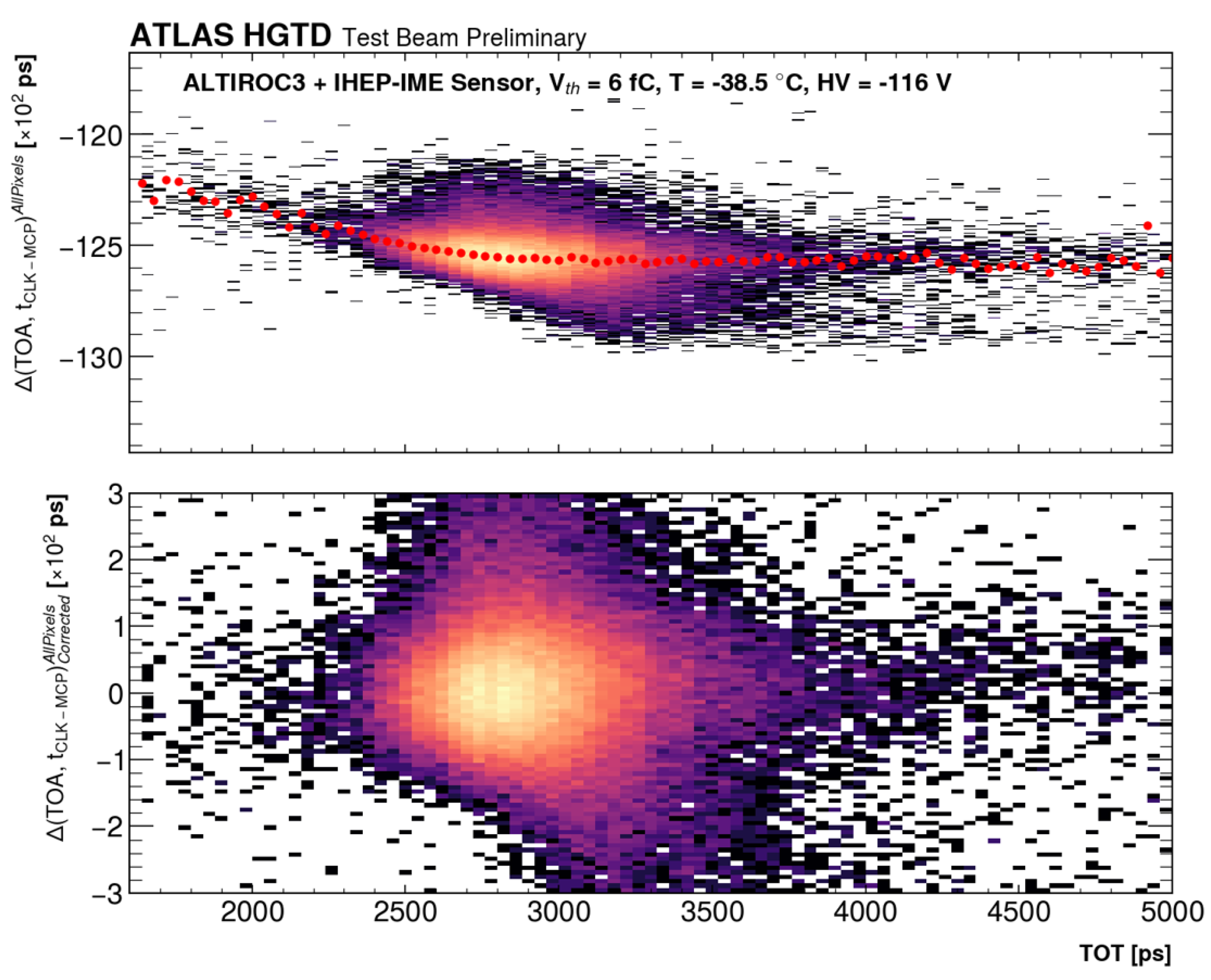

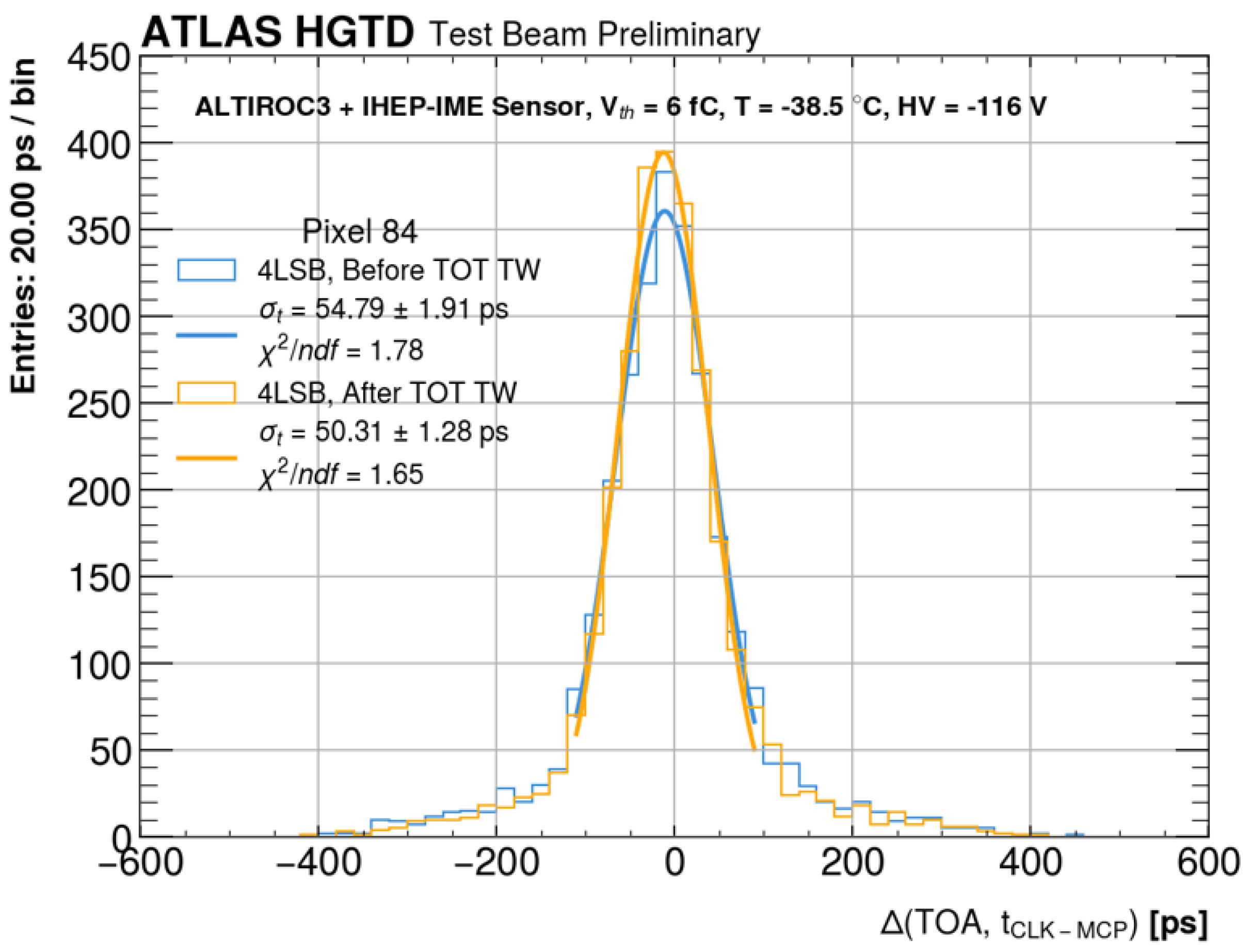

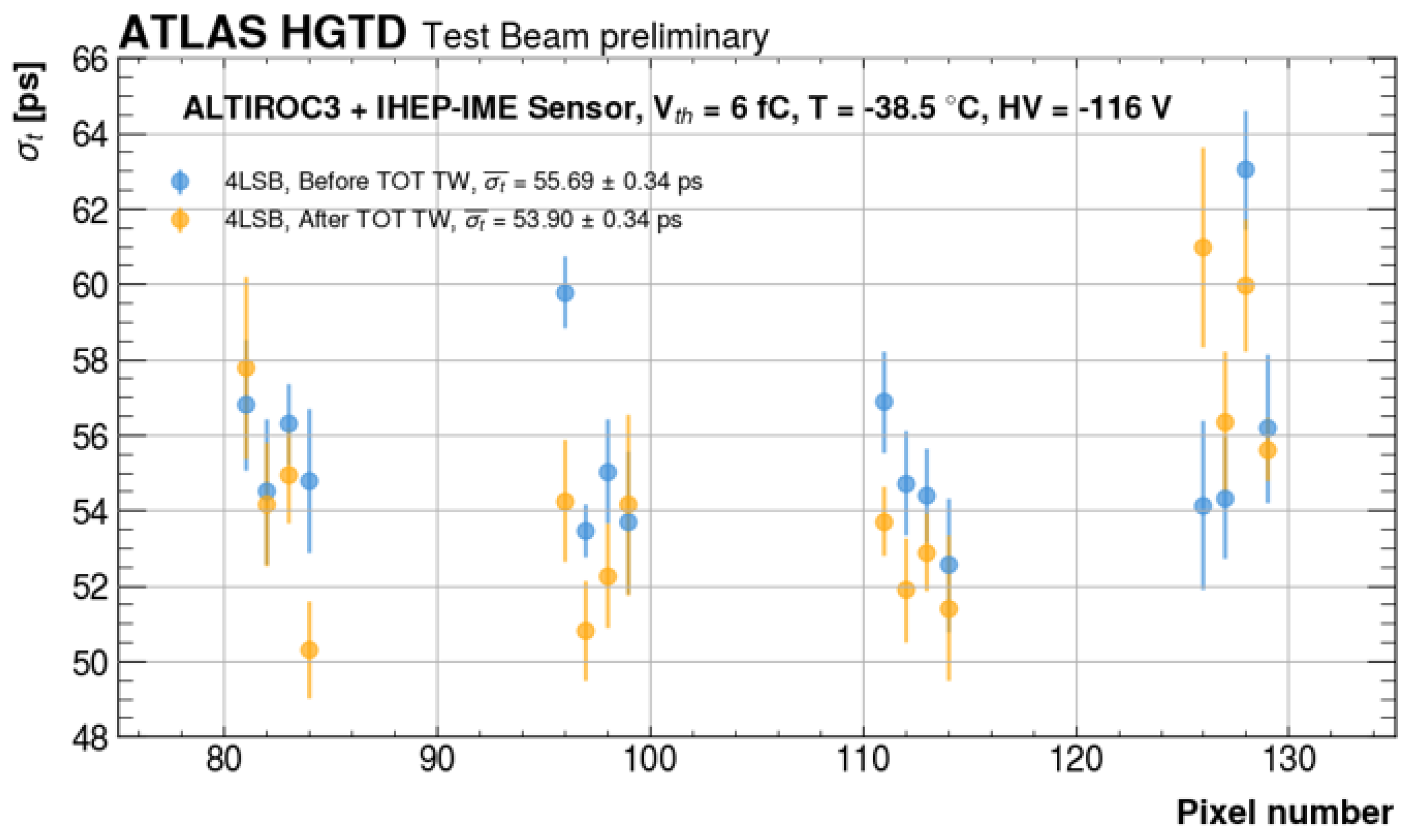

3.2. Time-Walk Correction

3.3. Time-Resolution

4. Summary

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- ATLAS Collaboration. The ATLAS Experiment at the CERN Large Hadron Collider. JINST 3 (2008) S08003. Available online: https://iopscience.iop.org/article/10.1088/1748-0221/3/08/S08003 (accessed on 1 June 2023).

- ATLAS Collaboration. Technical Design Report: A high Granularity Timing Detector for the ATLAS Phase-II Upgrade. Tech. Rep. CERN-LHCC-2020-007, ATLAS-TDR-031, CERN, Geneva. 2020. Available online: https://cds.cern.ch/record/2719855?ln=en (accessed on 1 May 2023).

- Sadrozinski, H.F.W.; Seiden, A.; Cartiglia, N. 4-Dimensional Tracking with Ultra-Fast Silicon Detectors. Rept. Prog. Phys. 2018, 81, 026101. [Google Scholar] [CrossRef] [PubMed]

- Description of the Jra1 Trigger Logic Unit (tlu), v0.2c. Tech. Rep. 2009. Available online: http://www.eudet.org/e26/e28/e42441/e57298/EUDET-MEMO-2009-04.pdf (accessed on 1 January 2024).

- Jansen, H.; Spannagel, S.; Behr, J.; Bulgheroni, A.; Claus, G.; Corrin, E.; Cussans, D.; Dreyling-Eschweiler, J.; Eckstein, D.; Eichhorn, T.; et al. Performance of the EUDET-type beam telescopes. EPJ Tech. Instrum. 2016, 3, 7. [Google Scholar] [CrossRef]

- Ronzhin, A.; Los, S.; Ramberg, E.; Apresyan, A.; Xie, S.; Spiropulu, M.; Kim, H. Study of the timing performance of micro-channel plate photomultiplier for use as an active layer in a shower maximum detector. Nucl. Instrum. Methods A 2015, 795, 288–292. [Google Scholar] [CrossRef]

- Albert, J.; Alex, M.; Alimonti, G.; Allport, P.; Altenheiner, S.; Ancu, L.S.; Andreazza, A.; Arguin, J.; Arutinov, D.; Backhaus, M.; et al. Prototype ATLAS IBL Modules using the FE-I4A Front-End Readout Chip. J. Instrum. 2012, 7, P11010. [Google Scholar]

- Leo, W.R. Techniques for Nuclear and Particle Physics Experiments, 2nd ed.; Springer: Berlin, Germany, 1994; ISBN 0-387-57280-5. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hammoud, S.E.D., on behalf of the ATLAS HGTD Group. Front-End Prototype ASIC with Low-Gain Avalanche Detector Sensors for the ATLAS High Granularity Timing Detector. Particles 2025, 8, 50. https://doi.org/10.3390/particles8020050

Hammoud SED on behalf of the ATLAS HGTD Group. Front-End Prototype ASIC with Low-Gain Avalanche Detector Sensors for the ATLAS High Granularity Timing Detector. Particles. 2025; 8(2):50. https://doi.org/10.3390/particles8020050

Chicago/Turabian StyleHammoud, Salah El Dine on behalf of the ATLAS HGTD Group. 2025. "Front-End Prototype ASIC with Low-Gain Avalanche Detector Sensors for the ATLAS High Granularity Timing Detector" Particles 8, no. 2: 50. https://doi.org/10.3390/particles8020050

APA StyleHammoud, S. E. D., on behalf of the ATLAS HGTD Group. (2025). Front-End Prototype ASIC with Low-Gain Avalanche Detector Sensors for the ATLAS High Granularity Timing Detector. Particles, 8(2), 50. https://doi.org/10.3390/particles8020050