A Methodology for Reconstructing DSET Pulses from Heavy-Ion Broad-Beam Measurements

Abstract

:1. Introduction

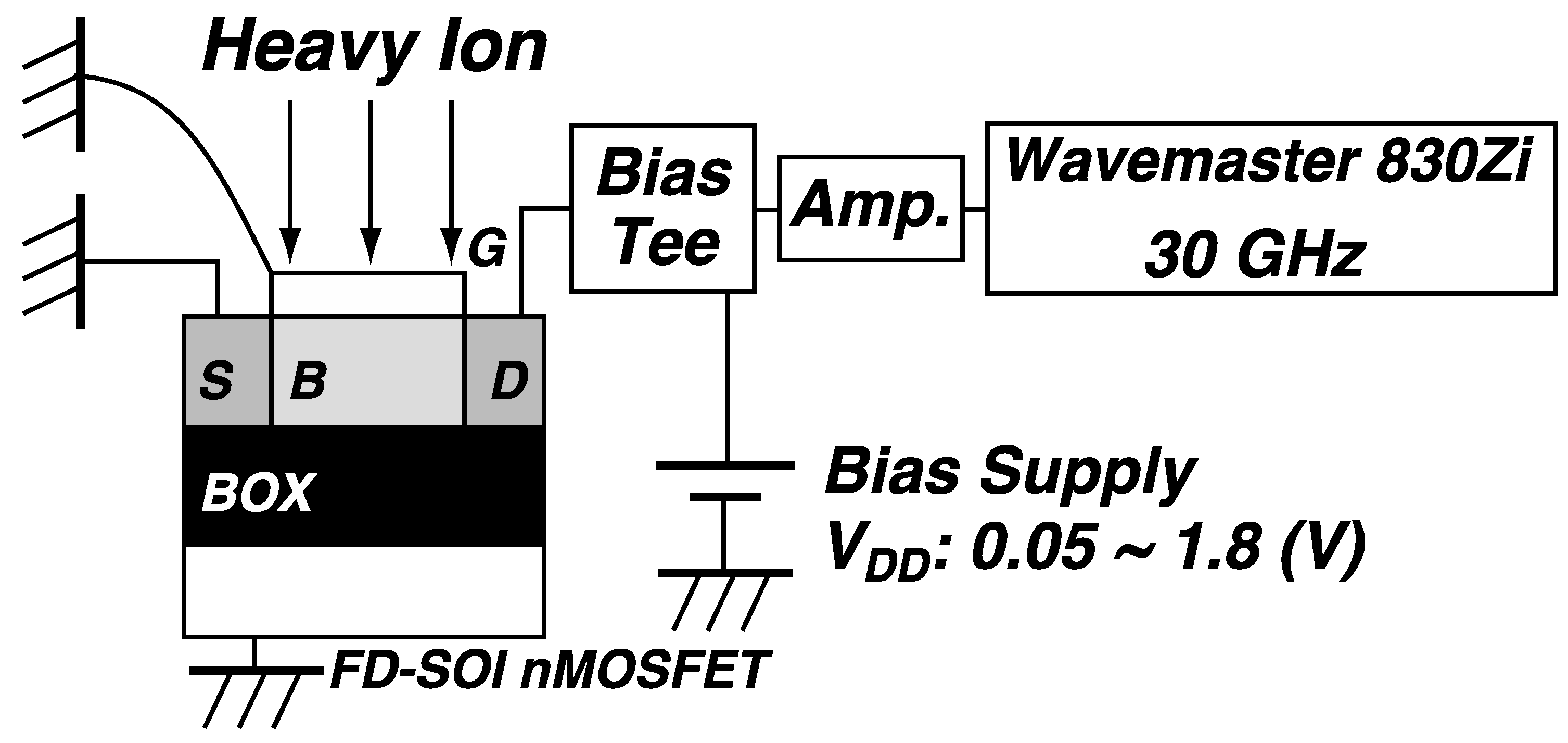

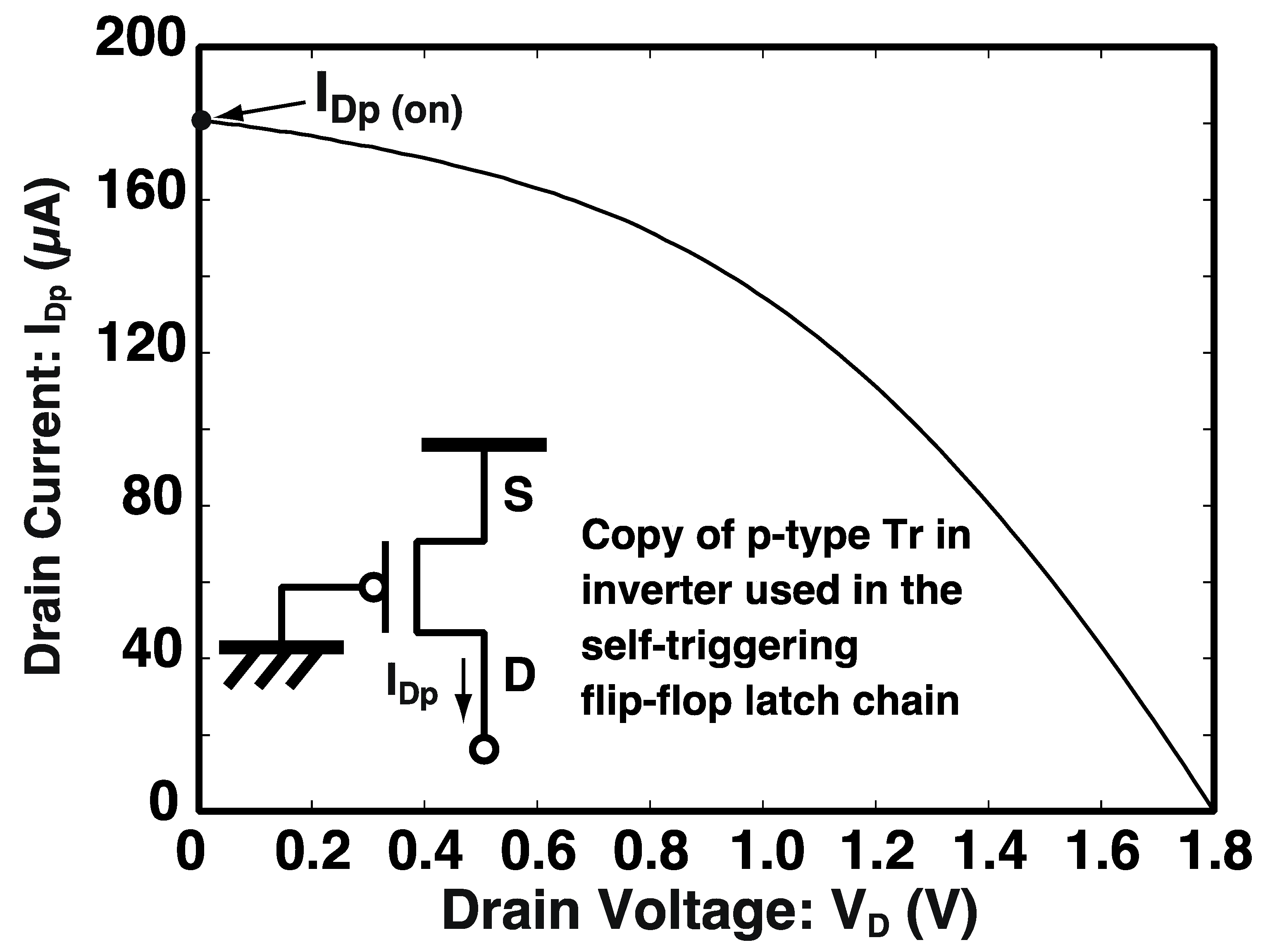

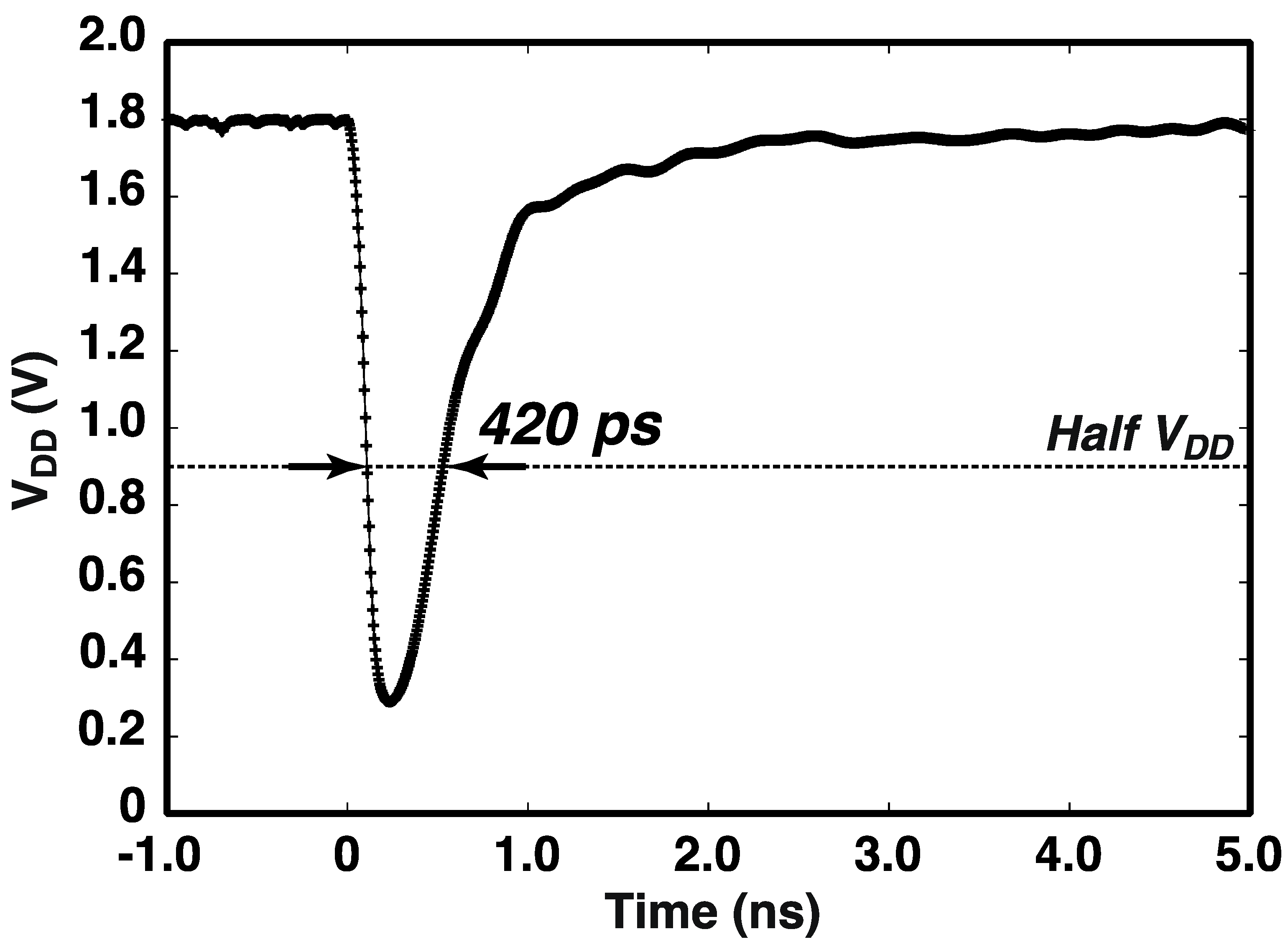

2. Experimental

3. Results and Discussion

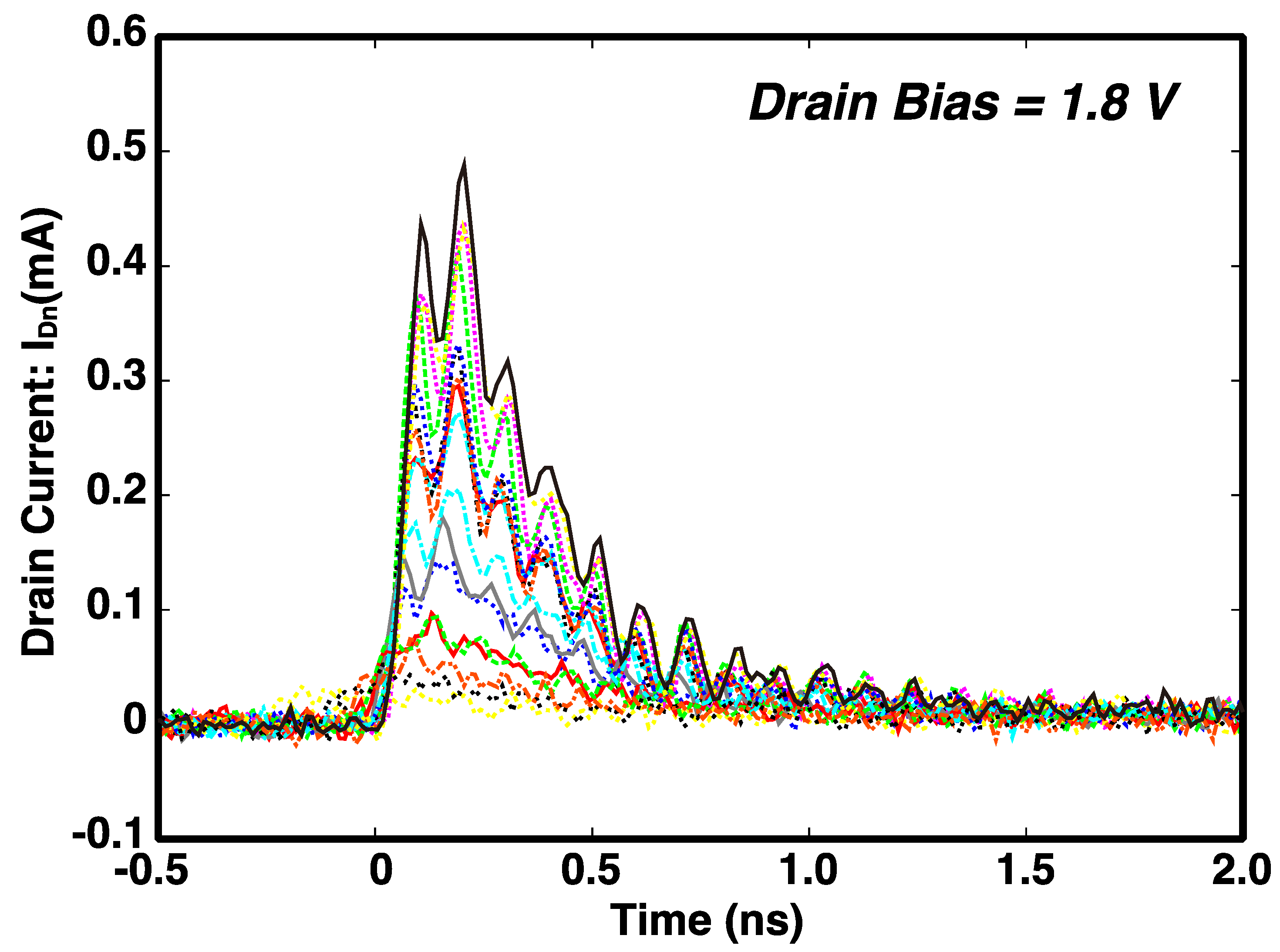

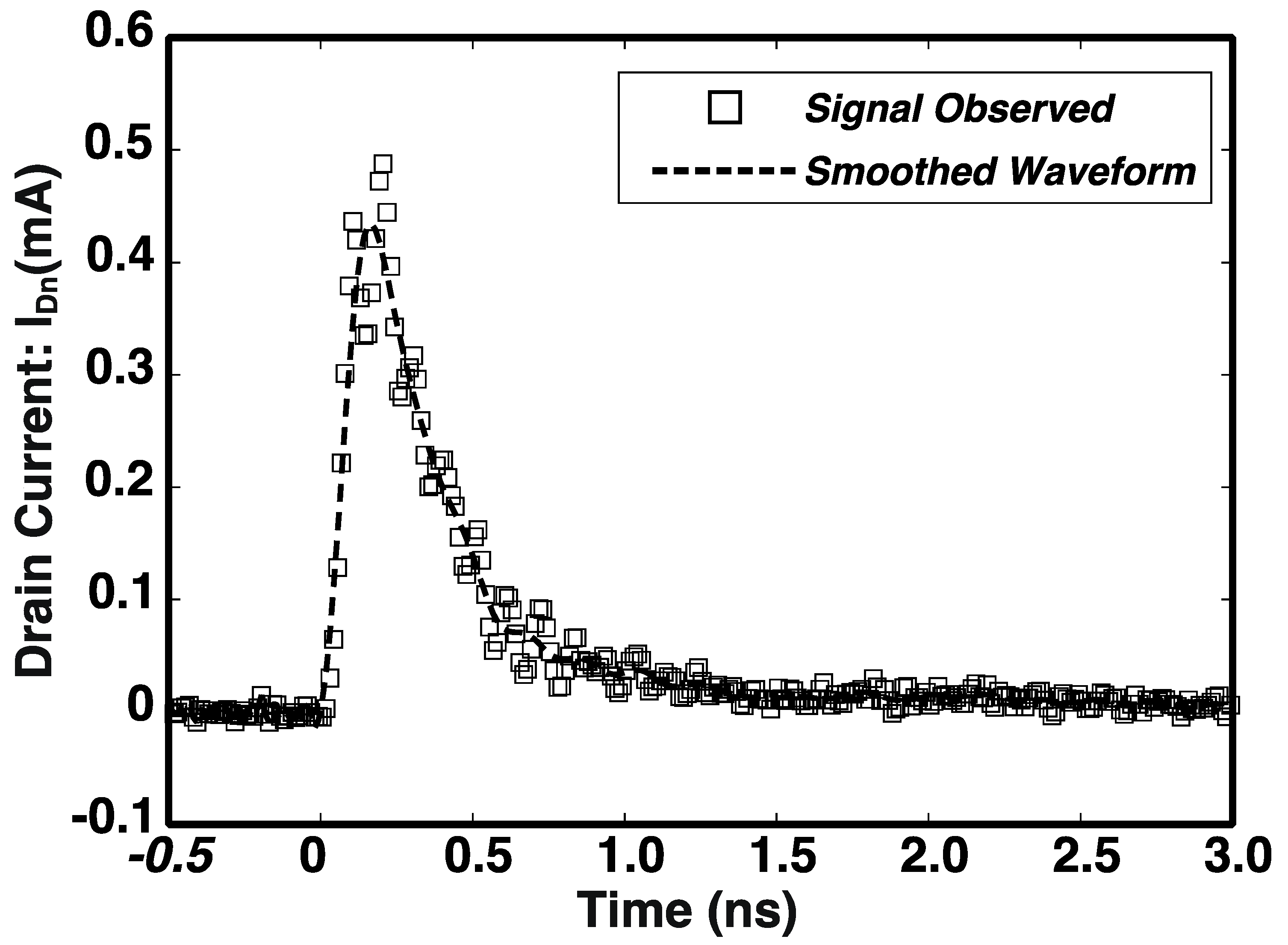

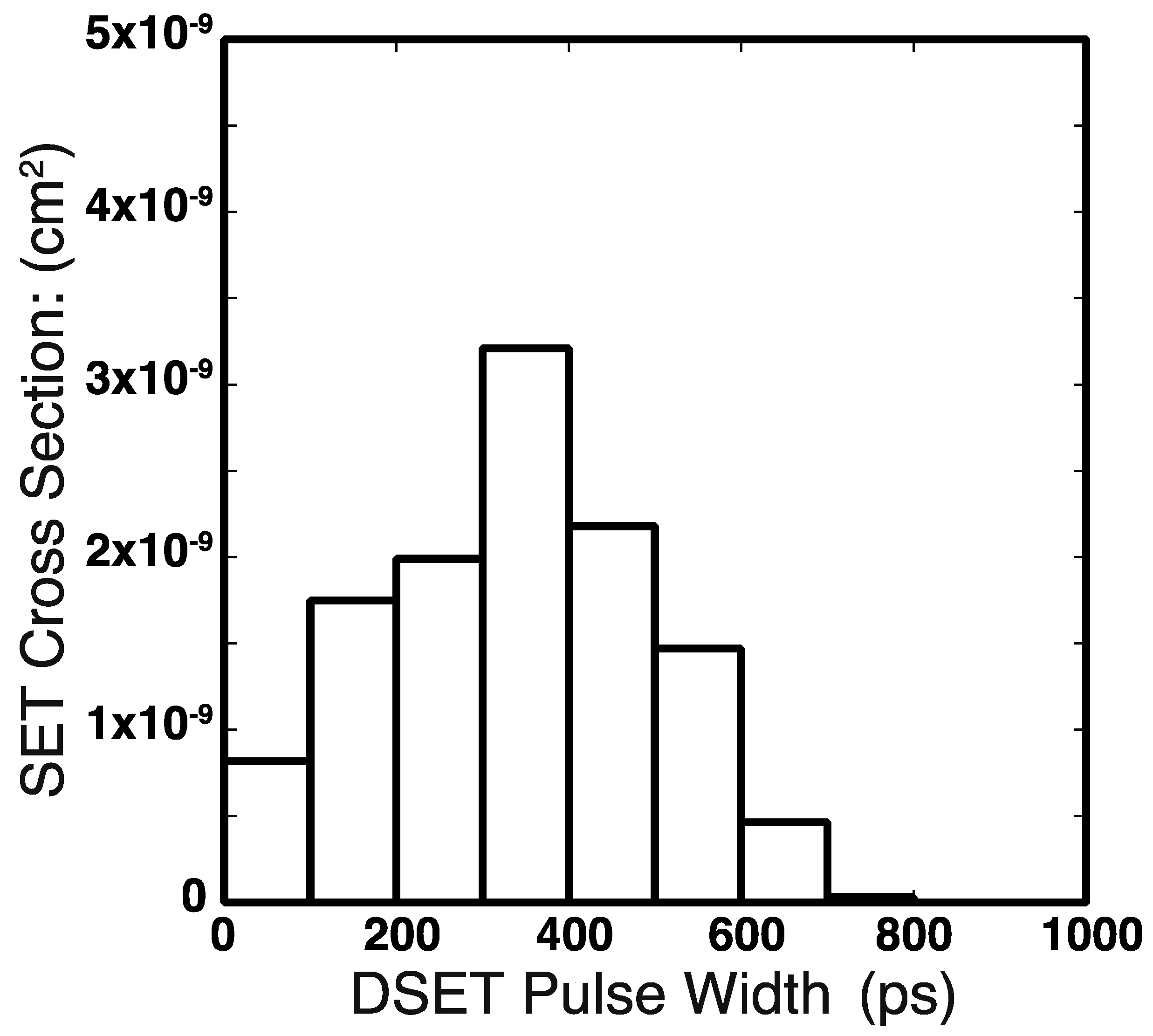

3.1. Experimental Results

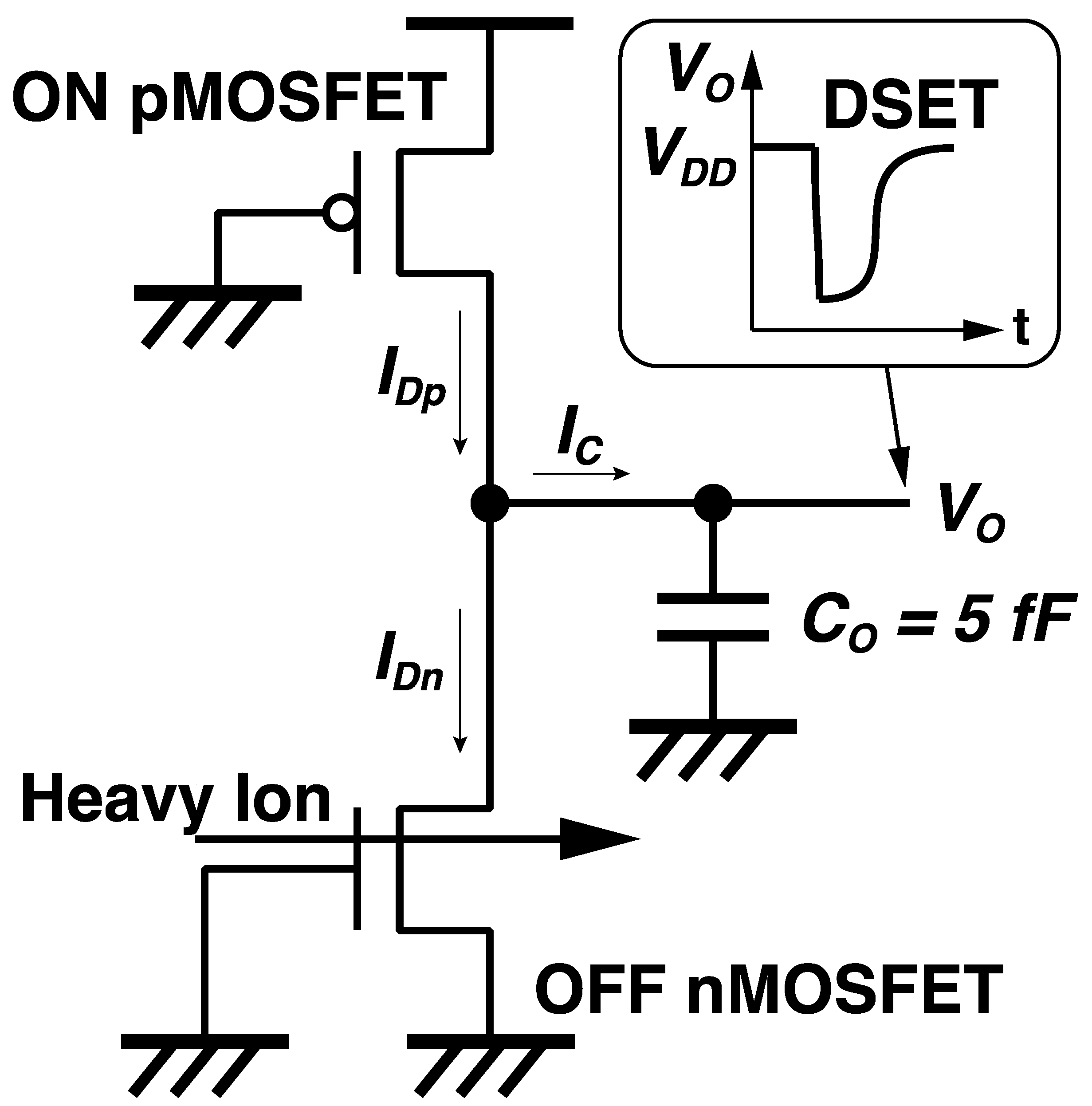

3.2. DSET Pulse-Width Estimation Methodology

3.3. DSET Pulse-Width Estimation Result

4. Conclusions

Author Contributions

Conflicts of Interest

References

- Buchner, S.; Baze, M.; Brown, D.; McMorrow, D.; Melinger, J. Comparison of error rates in combinational and sequential logic. IEEE Trans. Nucl. Sci. 1997, 44, 2209–2216. [Google Scholar] [CrossRef]

- Benedetto, J.M.; Eaton, P.H.; Mavis, D.G.; Gadlage, M.; Turflinger, T. Variation of digital SET pulse-widths and the implication for single event hardening of advanced CMOS processes. IEEE Trans. Nucl. Sci. 2005, 52, 2114–2119. [Google Scholar] [CrossRef]

- Yanagawa, Y.; Hirose, K.; Saito, H.; Kobayashi, D.; Fukuda, S.; Ishii, S.; Takahashi, D.; Kuroda, Y. Direct measurement of SET pulse width in 0.2-µm SOI logic cells irradiated by heavy ion. IEEE Trans. Nucl. Sci. 2006, 53, 3575–3578. [Google Scholar] [CrossRef]

- Narasimham, B.; Bhuva, B.L.; Schrimpf, R.D.; Massengill, L.W.; Gadlage, M.J.; Amusan, O.A.; Holman, W.T.; Witulski, A.F.; Robinson, W.H.; Benedetto, J.M.; et al. Characterization of digital single event transient pulse-widths in 130-nm and 90-nm CMOS Technologies. IEEE Trans. Nucl. Sci. 2007, 54, 2506–2511. [Google Scholar] [CrossRef]

- Ferlet-Cavrois, V.; Paillet, P.; McMorrow, D.; Fel, N.; Baggio, J.; Girard, S.; Duhamel, O.; Melinger, J.S.; Gaillardin, M.; Schwank, J.R.; et al. New insight into single event transient propagation in chains of inverters -Evidence for propagation-induced pulse broadening. IEEE Trans. Nucl. Sci. 2007, 54, 2338–2346. [Google Scholar] [CrossRef]

- Ferlet-Cavrois, V.; Pouget, V.; McMorrow, D.; Schwank, J.R.; Fel, N.; Essely, F.; Flores, R.S.; Paillet, P.; Gaillardin, M.; Kobayashi, D.; et al. Investigation of the propagation induced pulse broadening (PIPB) effect in SOI and bulk inverter chains. IEEE Trans. Nucl. Sci. 2008, 55, 2842–2853. [Google Scholar] [CrossRef]

- Makino, T.; Kobayashi, D.; Hirose, K.; Yanagawa, Y.; Saito, H.; Ikeda, H.; Takahashi, D.; Ishii, S.; Kusano, M.; Onoda, S.; et al. LET dependence of single event transient pulse-width in SOI logic cell. IEEE Trans. Nucl. Sci. 2009, 56, 202–207. [Google Scholar] [CrossRef]

- Gadlage, M.J.; Gouker, P.; Bharat, B.L.; Narasimham, B.; Schrimpf, R.D. Heavy-ion-induced digital single event transients in a 180 nm fully depleted SOI process. IEEE Trans. Nucl. Sci. 2009, 56, 3483–3488. [Google Scholar] [CrossRef]

- Makino, T.; Kobayashi, D.; Hirose, K.; Takahashi, D.; Ishii, S.; Kusano, M.; Onoda, S.; Hirao, T.; Ohshima, T. Soft-error rate in a logic LSI estimated from SET pulse-width measurements. IEEE Trans. Nucl. Sci. 2009, 56, 3180–3184. [Google Scholar] [CrossRef]

- Yanagawa, Y.; Kobayashi, D.; Hirose, K.; Makino, T.; Saito, H.; Ikeda, H.; Onoda, S.; Hirao, T.; Ohshima, T. Experimental verification of scan-architecture-based evaluation technique of SET and SEU soft-error rates at each flip-flop in logic LSI systems. IEEE Trans. Nucl. Sci. 2009, 56, 1958–1963. [Google Scholar] [CrossRef]

- Kobayashi, D.; Hirose, K.; Ikeda, H.; Saito, H. Fast and physically-accurate estimation of single event transient pulses from radiation-induced transient currents measured in a single MOSFET: A simulation-based case study in bulk CMOS logic circuit. In Proceedings of the 2007 IEEE Workshop on Silicon Errors in Logic--System Effects (SELSE3), Austin, TX, USA, 3–4 April 2007. [Google Scholar]

- Kobayashi, D.; Saito, H.; Hirose, K. Estimation of single event transient voltage pulses in LSI circuits from heavy-ion-induced transient currents measured in a single MOSFET. IEEE Trans. Nucl. Sci. 2007, 54, 1037–1041. [Google Scholar] [CrossRef]

- Kobayashi, D.; Hirose, K.; Makino, T.; Ikeda, H.; Saito, H. Feasibility study of a table-based SET-pulse estimation in logic cell from heavy-ion-induced transient current measured in a single MOSFET. IEEE Trans. Nucl. Sci. 2007, 54, 2347–2354. [Google Scholar] [CrossRef]

- Kobayashi, D.; Hirose, K.; Ferlet-Cavrois, V.; McMorrow, D.; Makino, T.; Ikeda, H.; Arai, Y.; Ohno, M. Waveform observation of digital single-event transients employing monitoring transistor technique. IEEE Trans. Nucl. Sci. 2008, 55, 2872–2879. [Google Scholar] [CrossRef]

- Hirose, K.; Saito, H.; Kuroda, Y.; Ishii, S.; Fukuoka, Y.; Takahashi, D. SEU resistance in advanced SOI-SRAMs fabricated by commercial technology using a rad-hard circuit design. IEEE Trans. Nucl. Sci. 2002, 49, 2965–2968. [Google Scholar] [CrossRef]

- Zigler, J.F. Program SRIM/TRIM. Available online: http://www.srim.org (accessed on 2 March 2020).

- Ferlet-Cavrois, V.; Paillet, P.; Gaillardin, M.; Lambert, D.; Baggio, J.; Schwank, J.R.; Vizkelethy, G.; Shaneyfelt, M.R.; Hirose, K.; Blackmore, E.W.; et al. Statistical analysis of the charge collected in SOI and bulk devices under heavy ion irradiation -- implications for digital SETs. IEEE Trans. Nucl. Sci. 2006, 53, 3242–3252. [Google Scholar] [CrossRef]

- Castellani-Coulie, K.; Munteanu, D.; Ferlet-Cavrois, V.; Autran, J.L. Simulation analysis of the bipolar amplification in fully-depleted SOI technologies under heavy-ion irradiation. IEEE Trans. Nucl. Sci. 2005, 52, 1474–1479. [Google Scholar] [CrossRef]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Makino, T.; Onoda, S.; Ohshima, T.; Kobayashi, D.; Ikeda, H.; Hirose, K. A Methodology for Reconstructing DSET Pulses from Heavy-Ion Broad-Beam Measurements. Quantum Beam Sci. 2020, 4, 15. https://doi.org/10.3390/qubs4010015

Makino T, Onoda S, Ohshima T, Kobayashi D, Ikeda H, Hirose K. A Methodology for Reconstructing DSET Pulses from Heavy-Ion Broad-Beam Measurements. Quantum Beam Science. 2020; 4(1):15. https://doi.org/10.3390/qubs4010015

Chicago/Turabian StyleMakino, Takahiro, Shinobu Onoda, Takeshi Ohshima, Daisuke Kobayashi, Hirokazu Ikeda, and Kazuyuki Hirose. 2020. "A Methodology for Reconstructing DSET Pulses from Heavy-Ion Broad-Beam Measurements" Quantum Beam Science 4, no. 1: 15. https://doi.org/10.3390/qubs4010015

APA StyleMakino, T., Onoda, S., Ohshima, T., Kobayashi, D., Ikeda, H., & Hirose, K. (2020). A Methodology for Reconstructing DSET Pulses from Heavy-Ion Broad-Beam Measurements. Quantum Beam Science, 4(1), 15. https://doi.org/10.3390/qubs4010015