A Current-Mode Optoelectronic Receiver IC for Short-Range LiDAR Sensors in 180 nm CMOS

Abstract

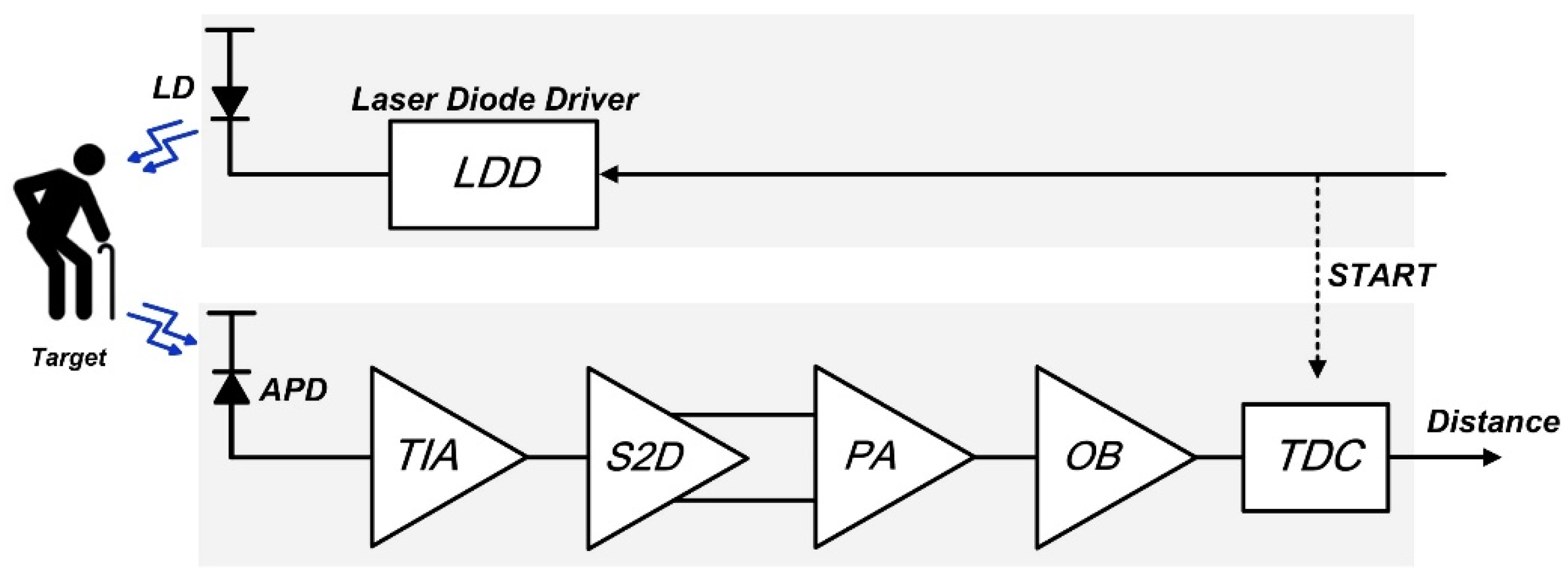

1. Introduction

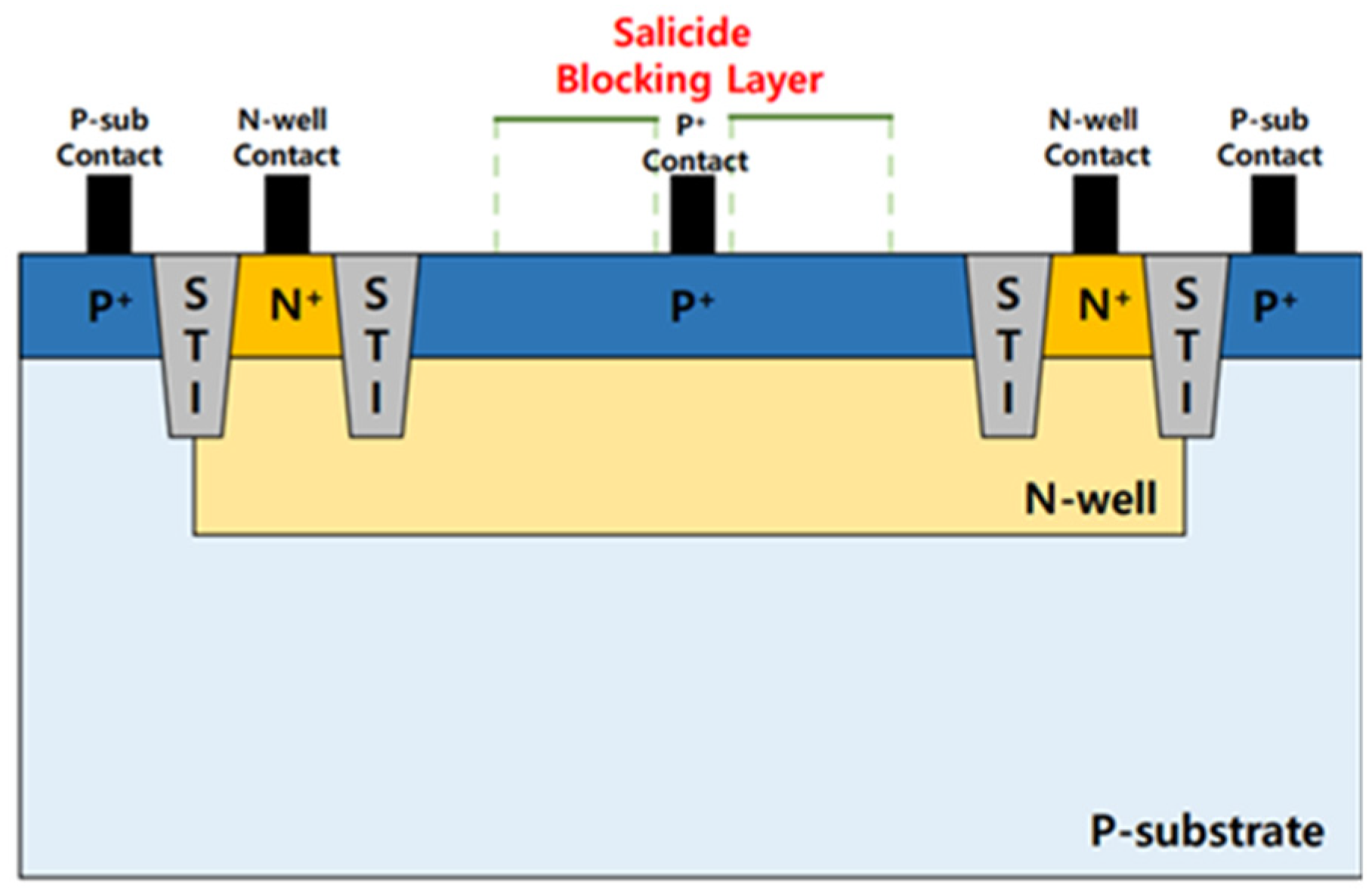

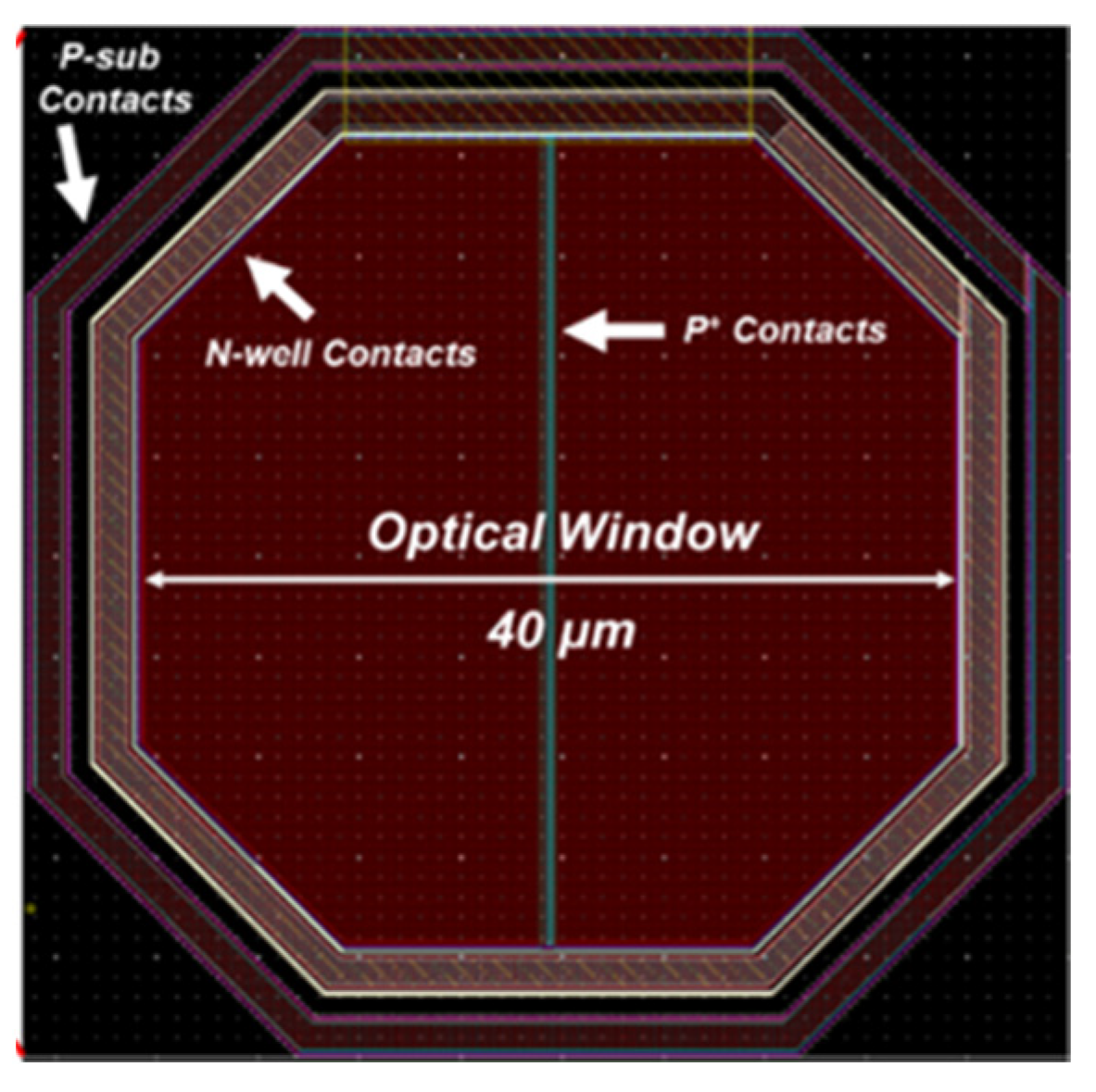

2. On-Chip CMOS APDs

2.1. P+/N-Well APD

2.2. P+/Deep N-Well APD

2.3. P+/N-Well/Deep N-Well APD

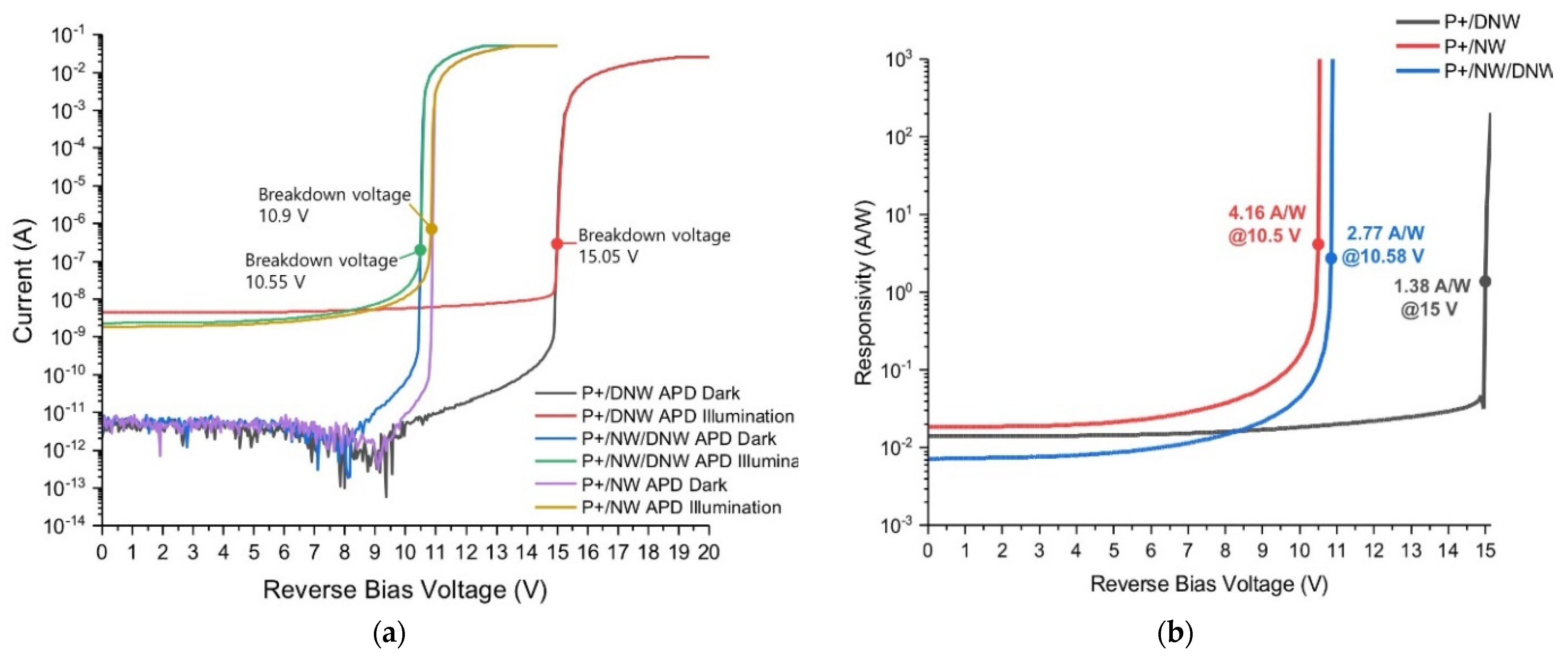

2.4. Measured Results

3. Voltage-Mode Optoelectronic Receiver (V-OER)

3.1. Experimental Methods

3.2. Measured Results

4. Proposed Current-Mode Optoelectronic Receiver (C-OER)

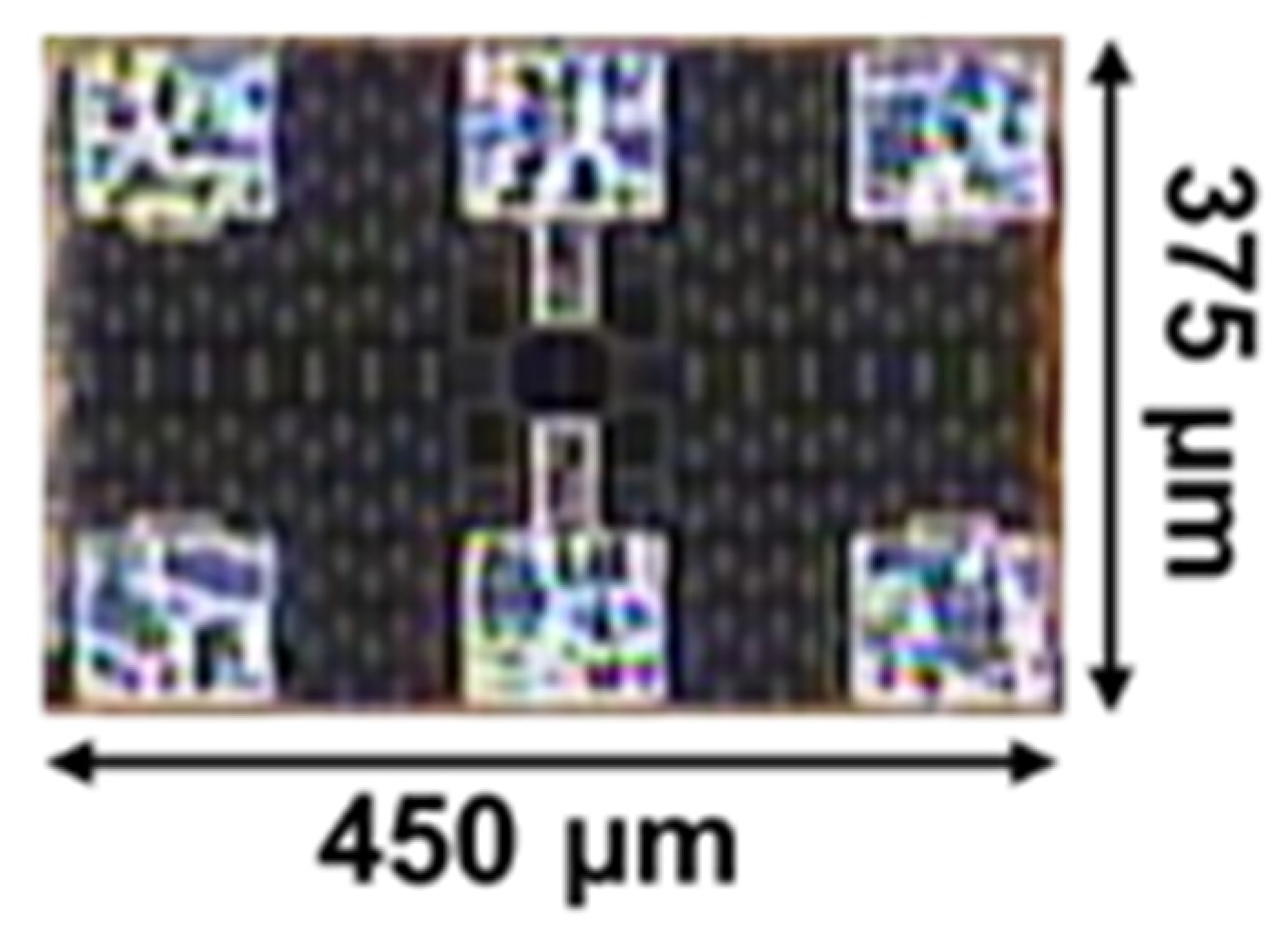

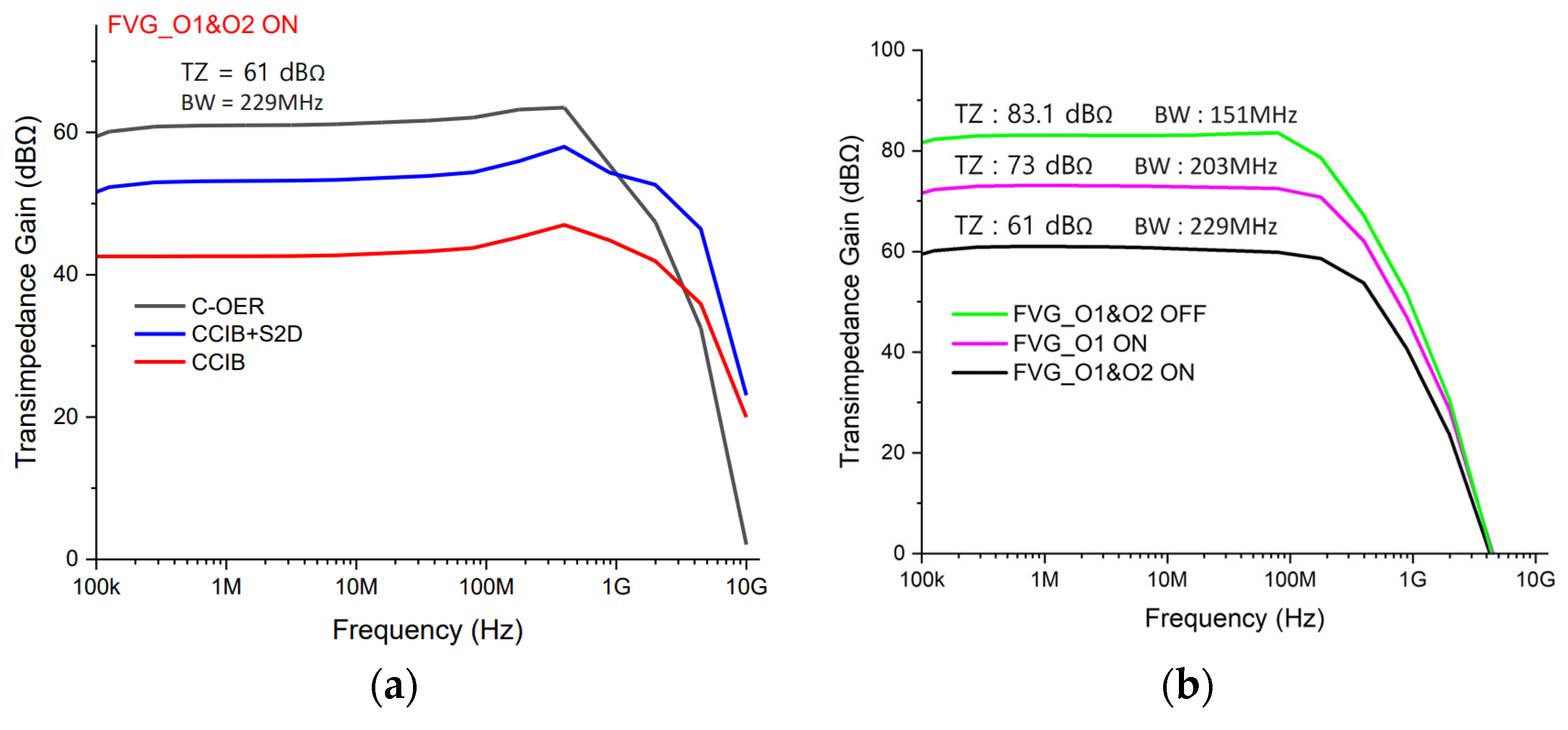

5. Measured Results of the Proposed C-OER

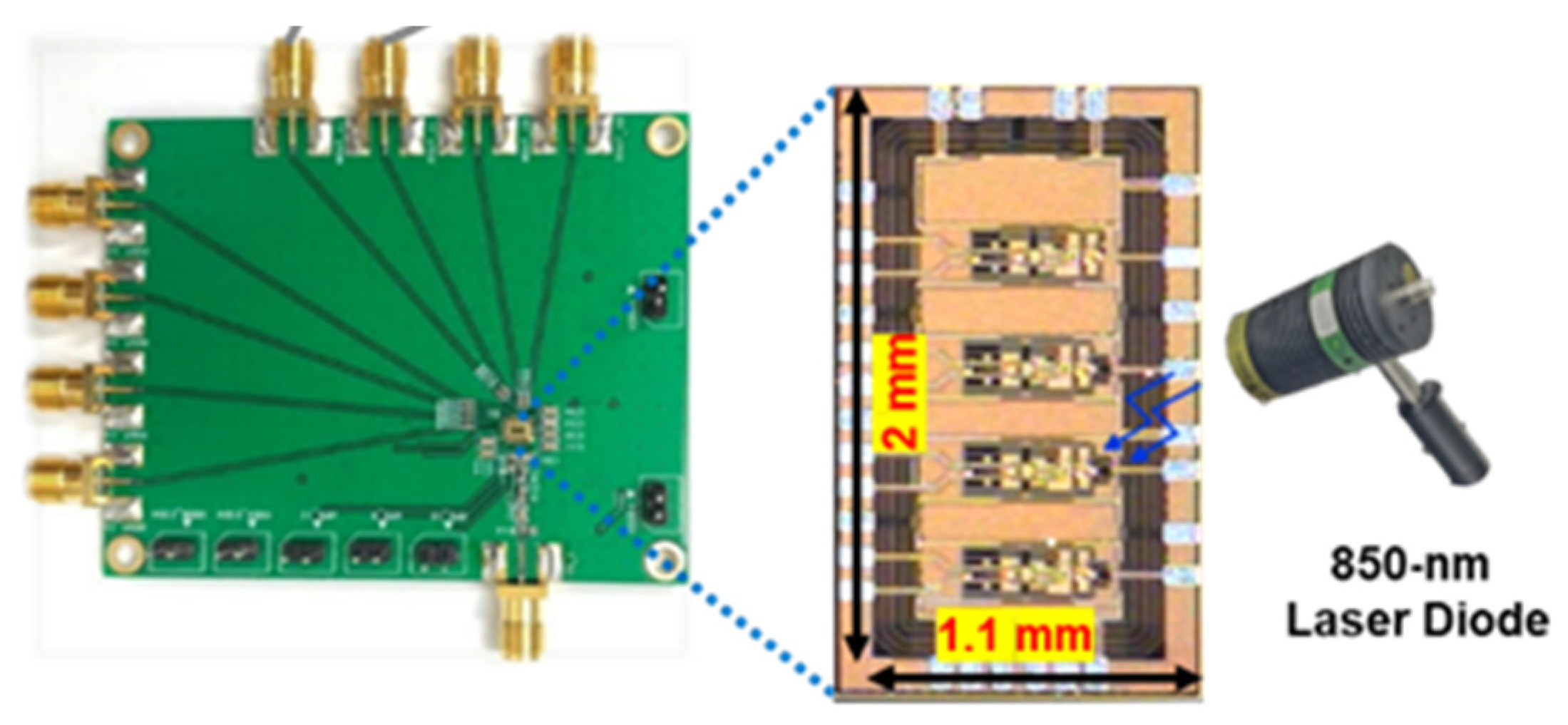

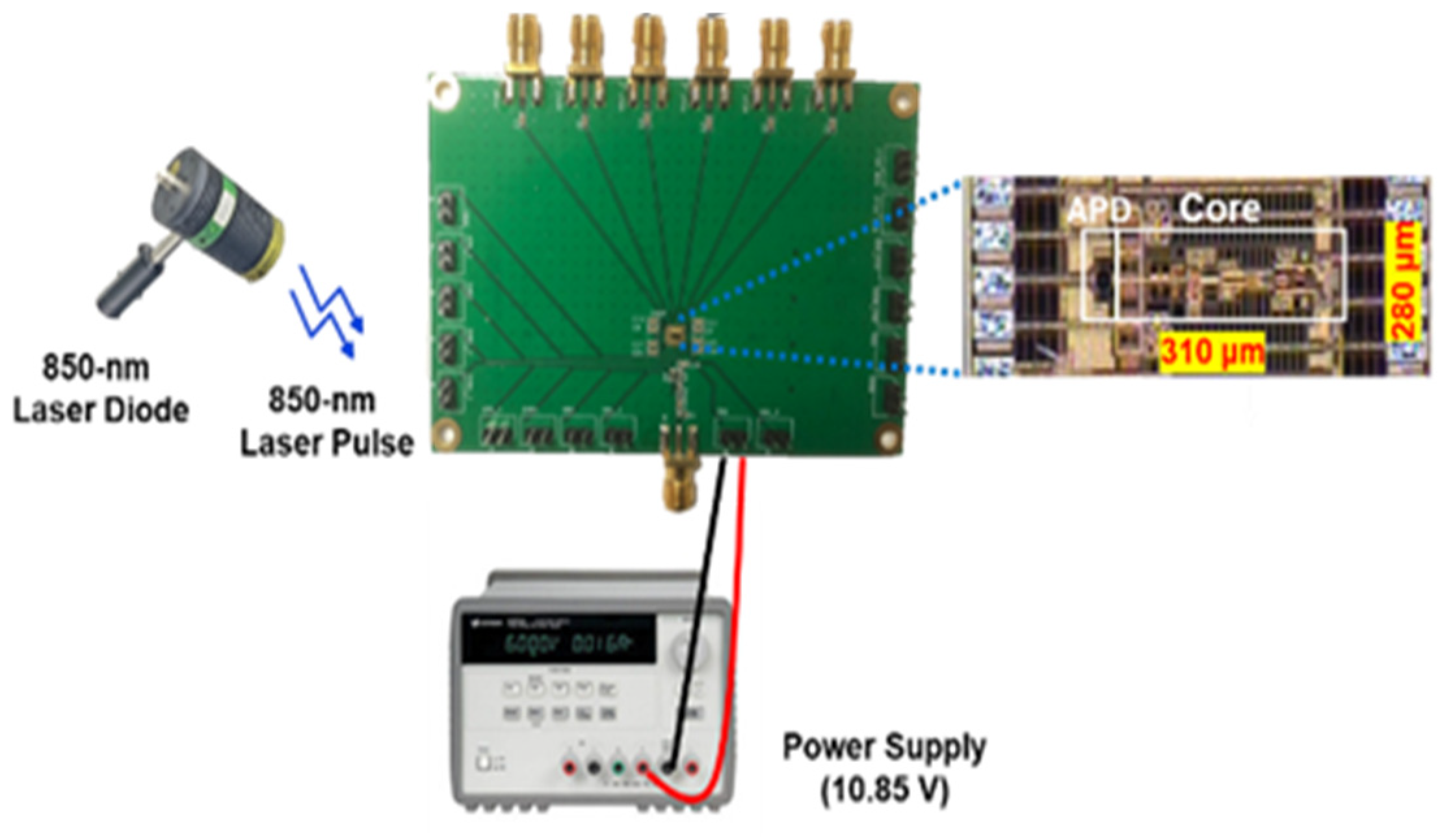

5.1. Experimental Methods

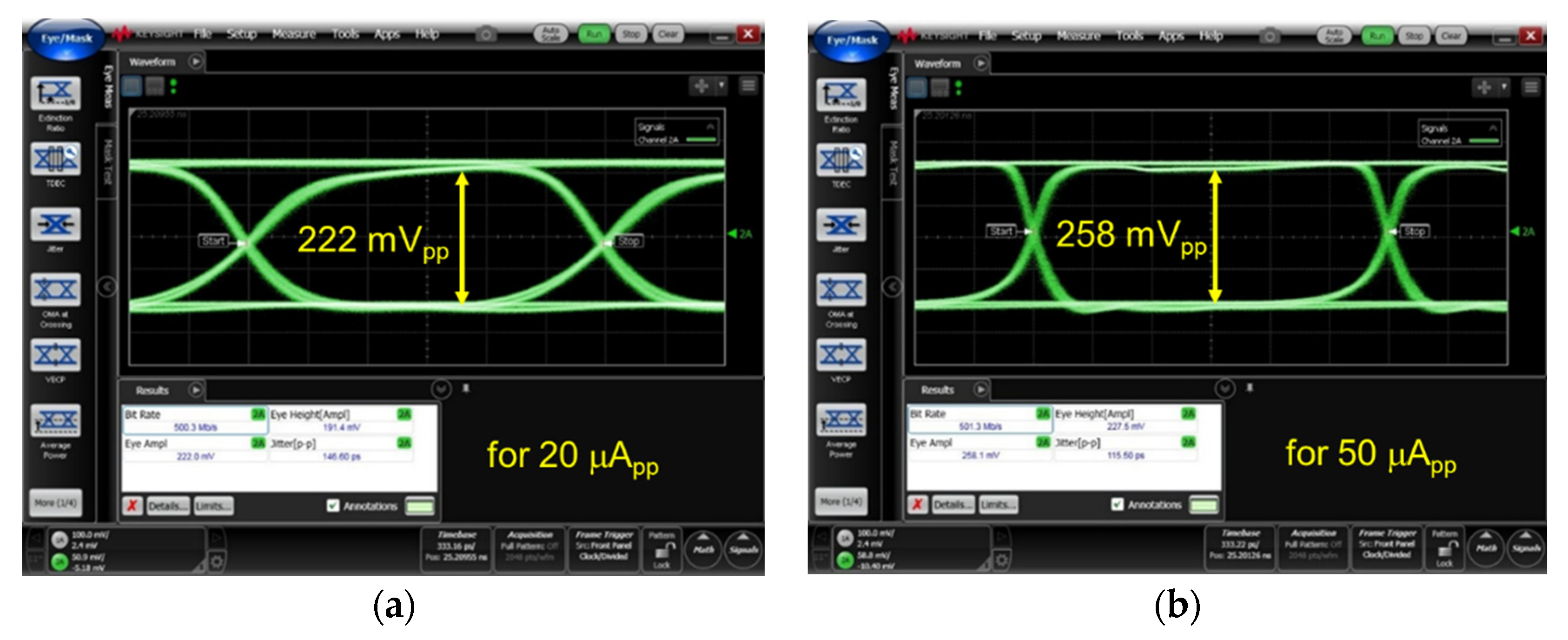

5.2. Measured Results

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Han, J.; Choi, B.; Seo, M.; Yun, J.; Lee, D.; Kim, T.; Eo, Y.; Park, S.M. A 20-Gb/s Transformer-Based Current-Mode Optical Receiver in 0.13-μm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2010, 57, 348–352. [Google Scholar]

- Lee, D.; Han, J.; Han, G.; Park, S.M. An 8.5-Gb/s fully integrated CMOS optoelectronic receiver using slope-detection adaptive equalizer. IEEE J. Solid-State Circuits 2010, 45, 2861–2873. [Google Scholar] [CrossRef]

- Zimmermann, H.; Heide, T. A monolithically integrated 1-Gb/s optical receiver in 1-μm CMOS technology. IEEE Photonics Technol. Lett. 2001, 13, 711–713. [Google Scholar] [CrossRef]

- Joo, J.-E.; Lee, M.-J.; Park, S.M. A CMOS optoelectronic receiver IC with an on-chip avalanche photodiode for home-monitoring LiDAR sensors. Sensors 2021, 21, 4364. [Google Scholar] [CrossRef] [PubMed]

- Hu, Y.; Joo, J.-E.; Lee, M.-J.; Park, S.M. An Optoelectronic Transimpedance Amplifier in 180-nm CMOS for Short-range LiDAR Sensors. J. Semicond. Technol. Sci. 2022, 22, 275–281. [Google Scholar] [CrossRef]

- Lee, M.-J.; Choi, W.-Y. Performance comparison of two types of silicon avalanche photodetectors based on N-well/P-substrate and P+/N-well junctions fabricated with standard CMOS technology. J. Opt. Soc. Korea 2011, 15, 1–3. [Google Scholar] [CrossRef]

- Lee, M.-J.; Choi, W.-Y. Effects of parasitic resistance on the performance of silicon avalanche photodetectors in standard CMOS technology. IEEE Electron Device Lett. 2015, 37, 60–63. [Google Scholar] [CrossRef]

- Lee, M.-J.; Choi, W.-Y. Area-dependent photodetection frequency response characterization of silicon avalanche photodetectors fabricated with standard CMOS technology. IEEE Trans. Electron Devices 2013, 60, 998–1004. [Google Scholar] [CrossRef]

- Park, Y.; Park, S.M. A dual-feedback folded-cascode fully differential transimpedance amplifier in 65-nm CMOS. J. Semicond. Technol. Sci. 2020, 20, 281–287. [Google Scholar] [CrossRef]

- Yoon, D.; Joo, J.-E.; Park, S.M. Mirrored Current-Conveyor Transimpedance Amplifier for Home Monitoring LiDAR Sensors. IEEE Sens. J. 2020, 21, 5589–5597. [Google Scholar] [CrossRef]

- Kurtti, S.; Jansson, J.-P.; Kostamovaara, J. A CMOS receiver–TDC chip set for accurate pulsed TOF laser ranging. IEEE Trans. Instrum. Meas. 2019, 69, 2208–2217. [Google Scholar] [CrossRef]

- Wang, X.; Ma, R.; Li, D.; Zheng, H.; Liu, M.; Zhu, Z. A low walk error analog front-end circuit with intensity compensation for direct ToF LiDAR. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 4309–4321. [Google Scholar] [CrossRef]

- Zheng, H.; Ma, R.; Liu, M.; Zhu, Z. A linear-array receiver analog front-end circuit for rotating scanner LiDAR application. IEEE Sens. J. 2019, 19, 5053–5061. [Google Scholar] [CrossRef]

- Zheng, H.; Ma, R.; Liu, M.; Zhu, Z. High Sensitivity and Wide Dynamic Range Analog Front-End Circuits for Pulsed TOF 4-D Imaging LADAR Receiver. IEEE Sens. J. 2018, 18, 3114–3124. [Google Scholar] [CrossRef]

- Hong, C.; Kim, S.-H.; Kim, J.-H.; Park, S.M. A linear-mode LiDAR sensor using a multi-channel CMOS transimpedance amplifier array. IEEE Sens. J. 2018, 18, 7032–7040. [Google Scholar] [CrossRef]

- Cho, H.-S.; Kim, C.-H.; Lee, S.-G. A high-sensitivity and low-walk error LADAR receiver for military application. IEEE Trans. Circuits Syst. I Regul. Pap. 2014, 61, 3007–3015. [Google Scholar] [CrossRef]

- Chen, R.Y.; Yang, Z.-Y. CMOS transimpedance amplifier for gigabit-per-second optical wireless communications. IEEE Trans. Circuits Syst. II Express Briefs 2015, 63, 418–422. [Google Scholar] [CrossRef]

| PARAMETERS | [4] | [11] | [12] | [13] | V-OER |

|---|---|---|---|---|---|

| CMOS technology (nm) | 180 | 350 | 180 | 180 | 180 |

| APD | On-chip | Off-chip | Off-chip | Off-chip | On-chip |

| Input configuration | VCF | SF | SF with FC | SF | VCF |

| Bandwidth (MHz) | 790 | 230 | 281 | 450 | 608 |

| TZ gain (dBΩ) | 93.4 | 100 | 86 | 100 | 95.1 |

| Noise current spectral density (pA/sqrt(Hz)) | 12 | 6.32 | 4.68 | 2.59 | 4.54 |

| Min. detectable current (mApp) | 6.74 (SNR = 10) | 1.0 (SNR = 5) | 2.0 (SNR = 25) | 2.5 (SNR = 5) | 2.38 (SNR = 10) |

| Single-pulse width | 25 ms | 3 ns | 3 ns | 2 ns | 5 ns |

| Optically measured pulse (mVpp) | 8 | 200 | 110 | 300 | 200 |

| Power dissipation (mW) | 56.5 (w/OB) | 180 (w/TDC) | 200 (w/PA) | 6.6 (w/o OB) | 39.3 (w/OB) |

| Core area (mm2) | 0.09 | 14 | 2.20 | 4.08 | 0.068 |

| PARAMETERS | [14] | [15] | [16] | [17] | V-OER | C-OER |

|---|---|---|---|---|---|---|

| CMOS technology (nm) | 180 | 180 | 350 | 180 | 180 | 180 |

| Supply (V) | 3.3 | 1.8 | 3.3 | 1.8/3.3 | 1.8 | 1.8/3.3 |

| APD | On-chip | Off-chip | On-chip | Off-chip | On-chip | On-chip |

| Input configuration | CM + SF | VCF | CF | CAF | VCF | CCIB |

| Output signaling | single-ended | differential | single-ended | differential | differential | differential |

| Bandwidth (MHz) | 153 | 720 | 160 | 1000 | 608 | 151~229 |

| TZ gain (dBΩ) | 106 | 76.3 | 78~110 | 56.8~69.3 | 95.1 | 61~83.1 |

| Gain control | External | Auto | External | External | No | Auto |

| Max. detectable current (mApp) | 5.0 | 1.1 | 0.022 | 0.083 | 0.05 | 1.0 |

| Min. detectable current (mApp) | 0.5 (SNR = 5) | 1.14 (SNR = 12) | 0.053 (SNR = 3.3) | 23 (SNR = 14) | 2.38 (SNR = 10) | 5.0 (SNR = 14) |

| Power dissipation (mW) | 16.5(w/o OB) | 29.8 | 79 | 6.6(w/o OB) | 39.3(w/OB) | 47.8 |

| Core area (mm2) | 1.2 × 1.13 | 5.0 × 1.1 | 1.0 × 1.2 | 0.1 × 0.075 | 0.068 | 0.28 × 0.31 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hu, Y.; Joo, J.-E.; Zhang, X.; Chon, Y.; Choi, S.; Lee, M.-J.; Park, S.-M. A Current-Mode Optoelectronic Receiver IC for Short-Range LiDAR Sensors in 180 nm CMOS. Photonics 2023, 10, 746. https://doi.org/10.3390/photonics10070746

Hu Y, Joo J-E, Zhang X, Chon Y, Choi S, Lee M-J, Park S-M. A Current-Mode Optoelectronic Receiver IC for Short-Range LiDAR Sensors in 180 nm CMOS. Photonics. 2023; 10(7):746. https://doi.org/10.3390/photonics10070746

Chicago/Turabian StyleHu, Yu, Ji-Eun Joo, Xinyue Zhang, Yeojin Chon, Shinhae Choi, Myung-Jae Lee, and Sung-Min Park. 2023. "A Current-Mode Optoelectronic Receiver IC for Short-Range LiDAR Sensors in 180 nm CMOS" Photonics 10, no. 7: 746. https://doi.org/10.3390/photonics10070746

APA StyleHu, Y., Joo, J.-E., Zhang, X., Chon, Y., Choi, S., Lee, M.-J., & Park, S.-M. (2023). A Current-Mode Optoelectronic Receiver IC for Short-Range LiDAR Sensors in 180 nm CMOS. Photonics, 10(7), 746. https://doi.org/10.3390/photonics10070746