Analysis of a PWM Converter with Less Current Ripple, Wide Voltage Operation and Zero-Voltage Switching

Abstract

:1. Introduction

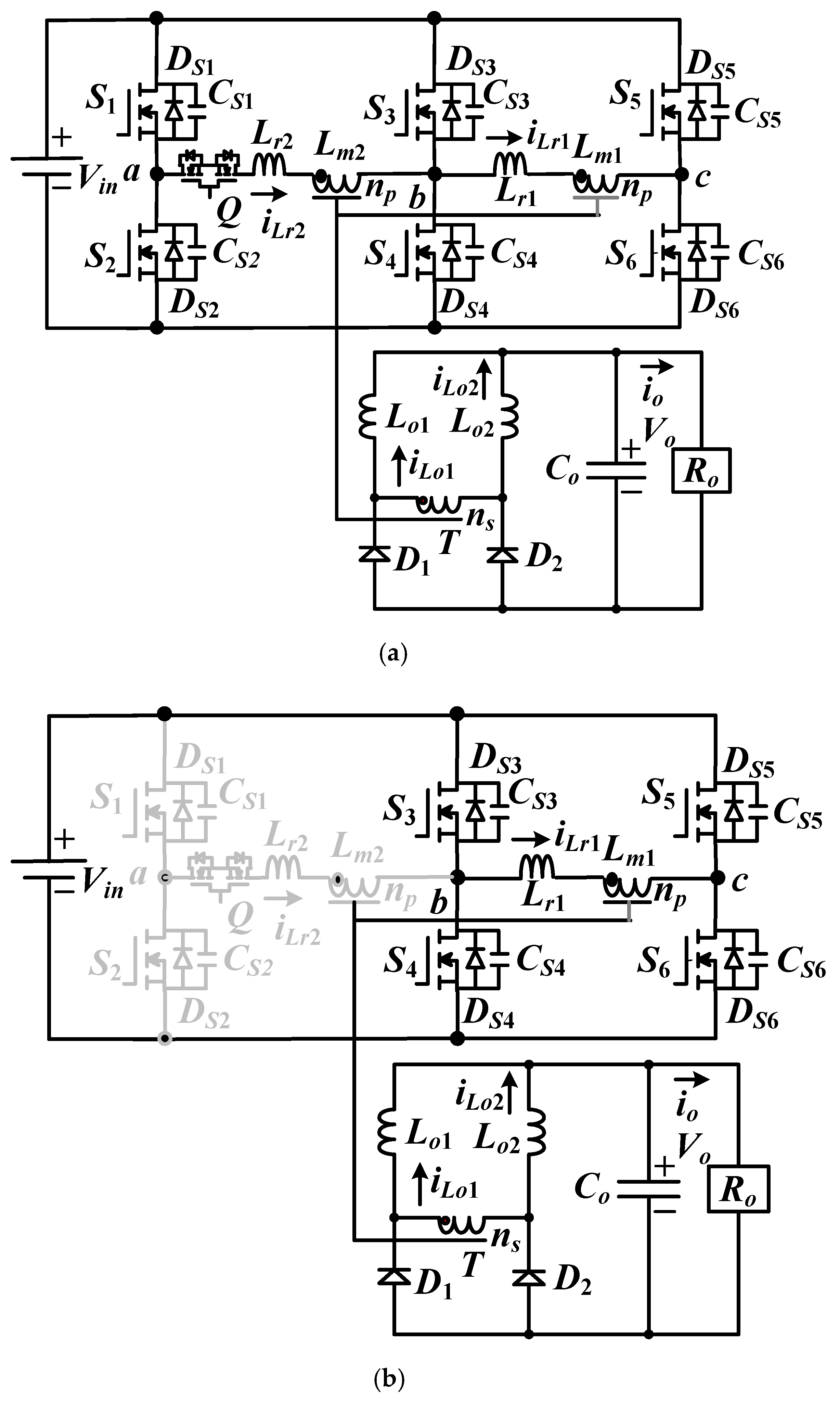

2. Proposed Converter

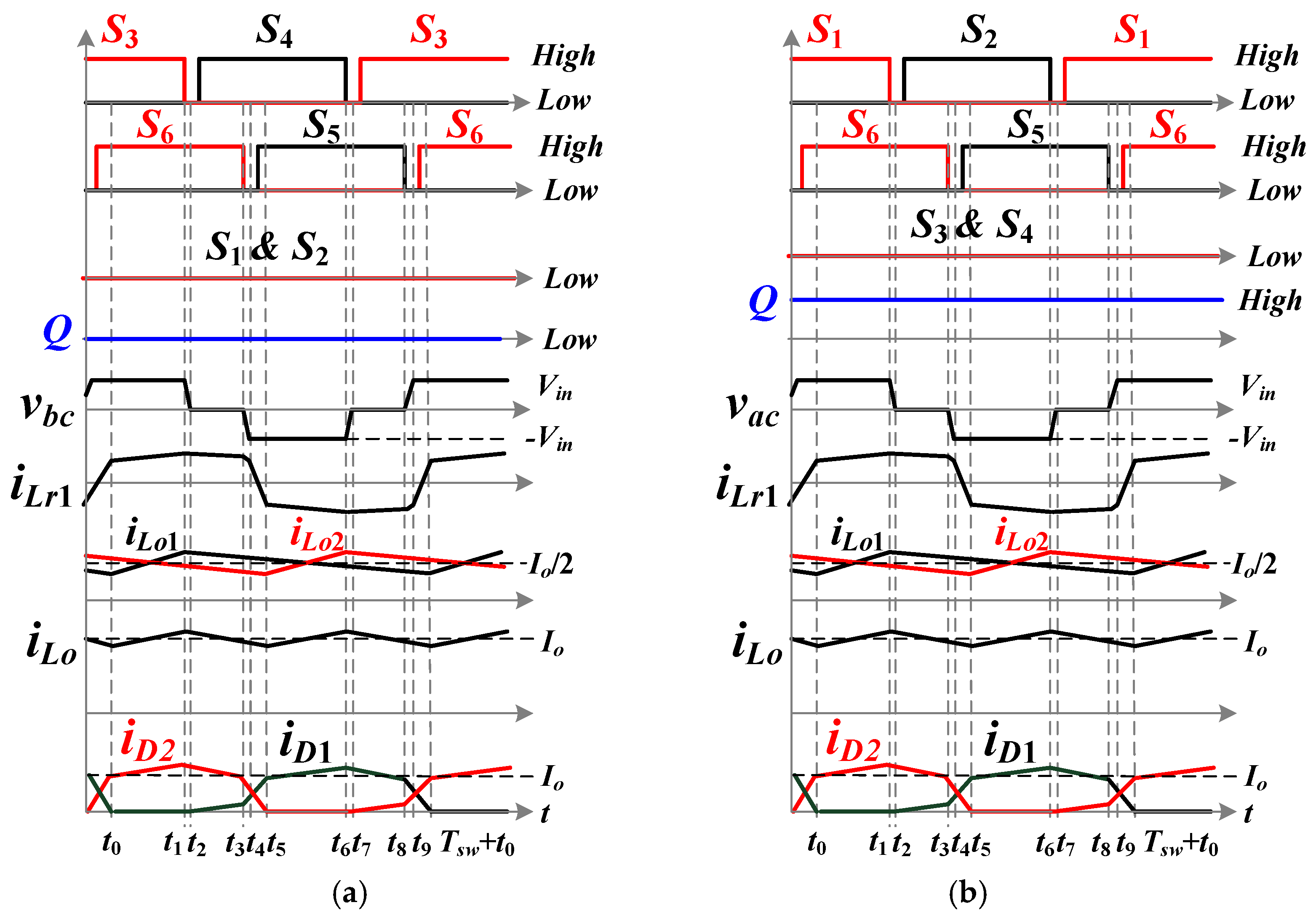

3. Principle of Operation

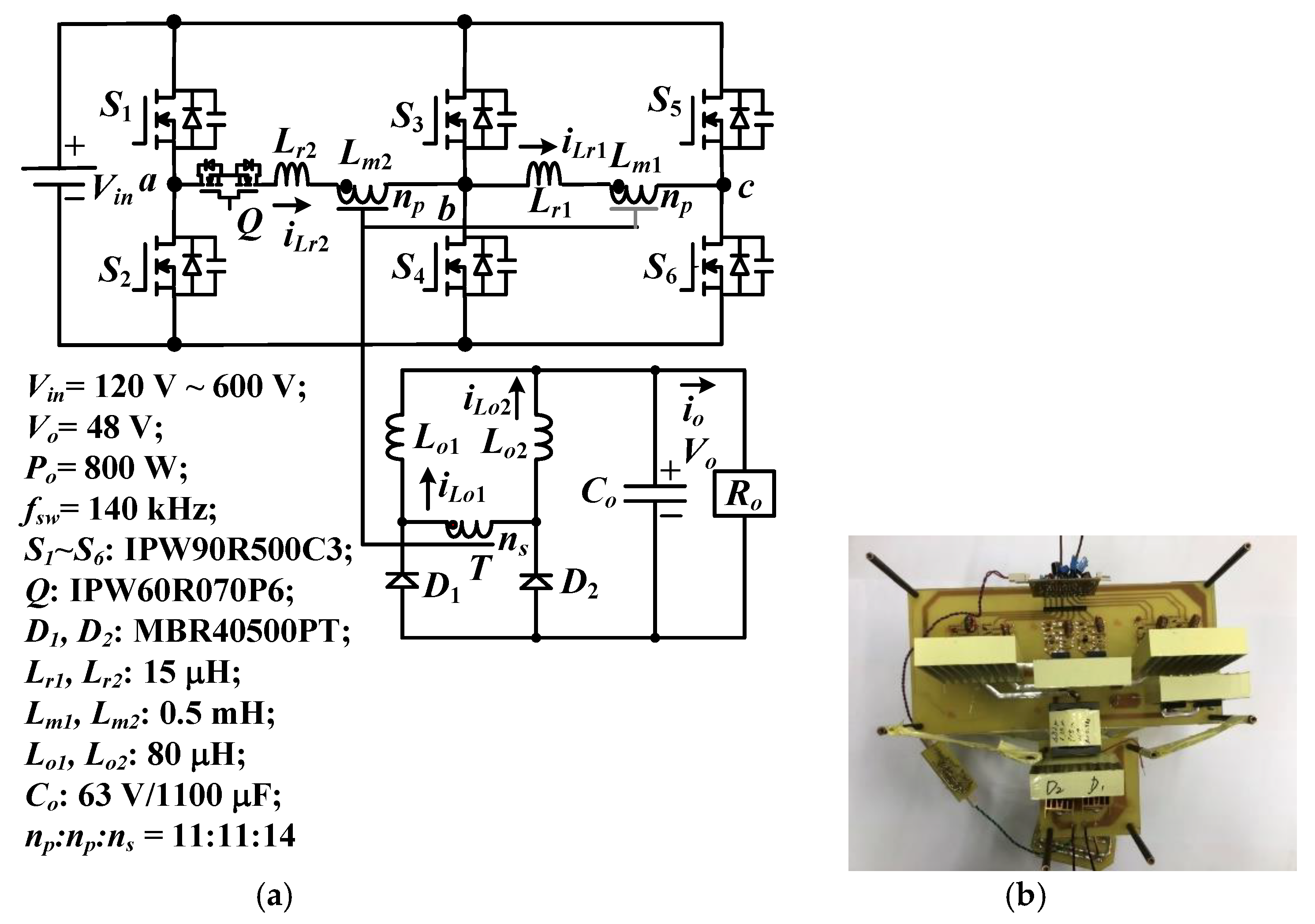

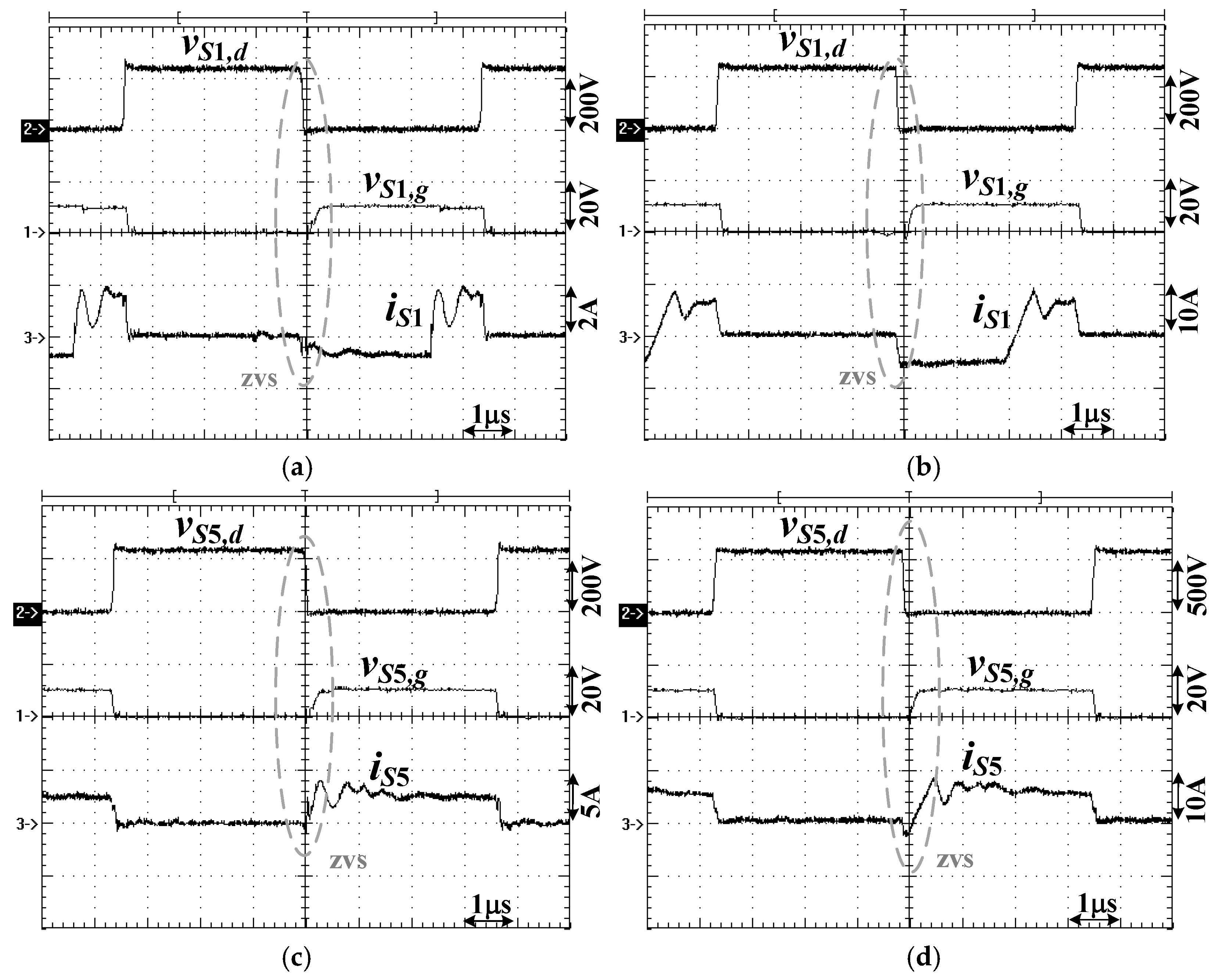

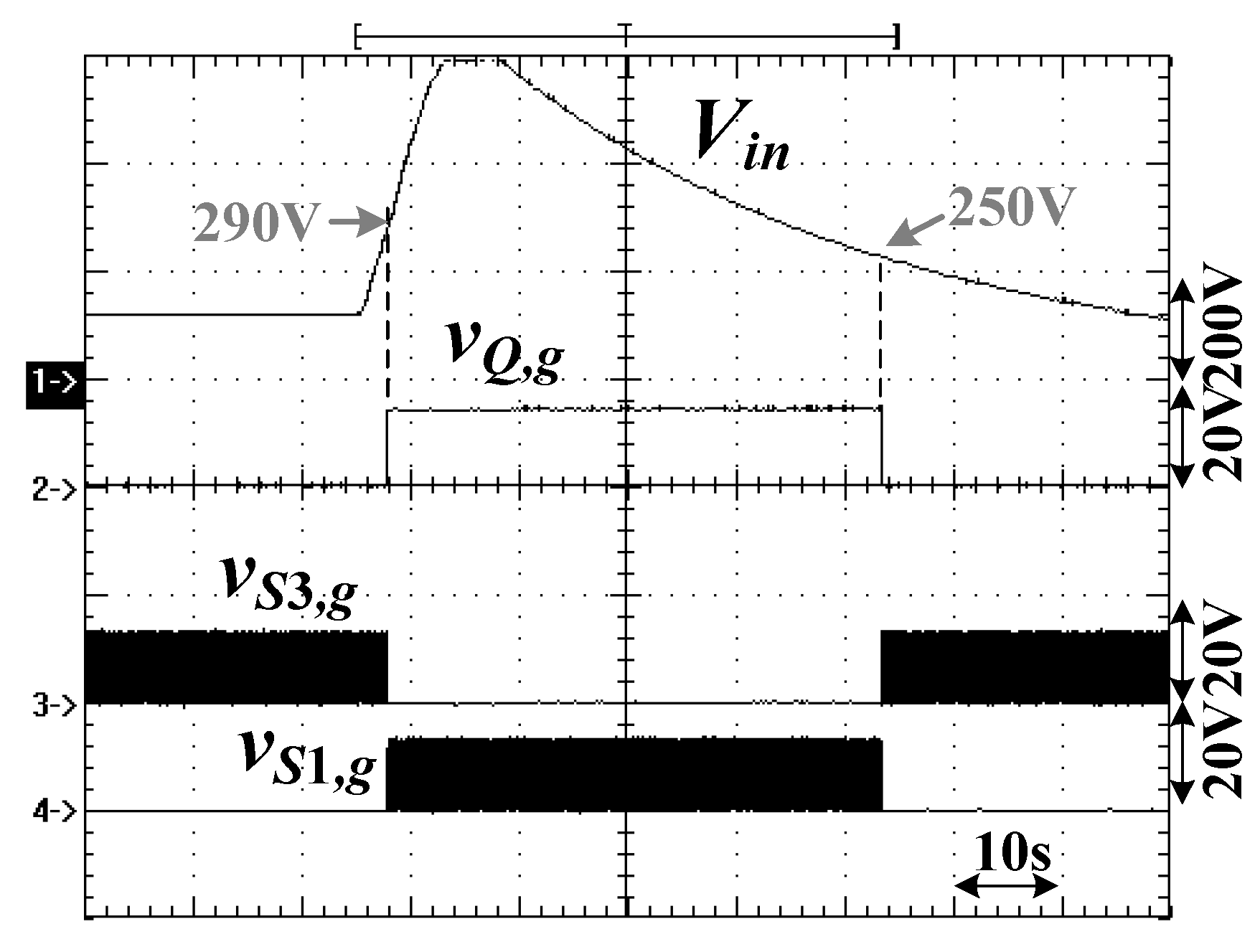

4. Steady State Analysis

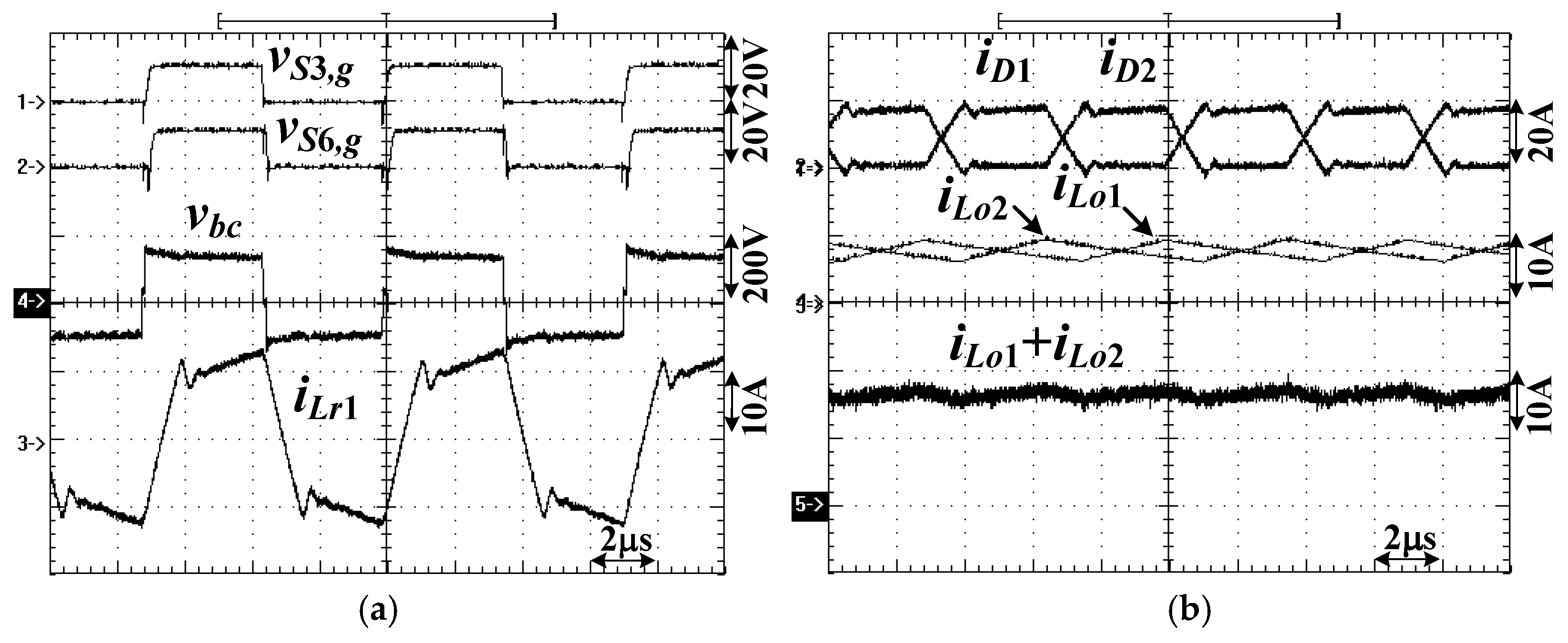

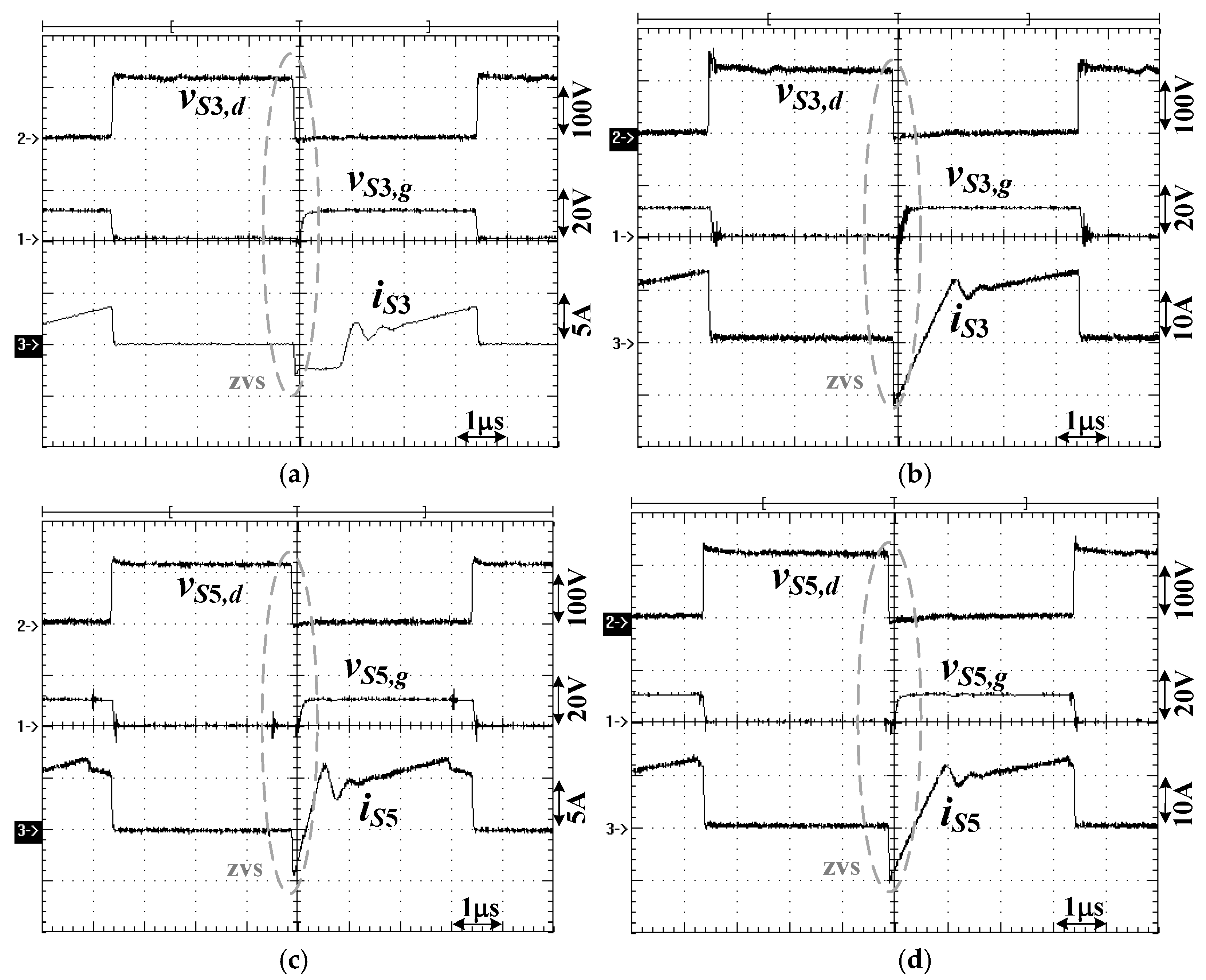

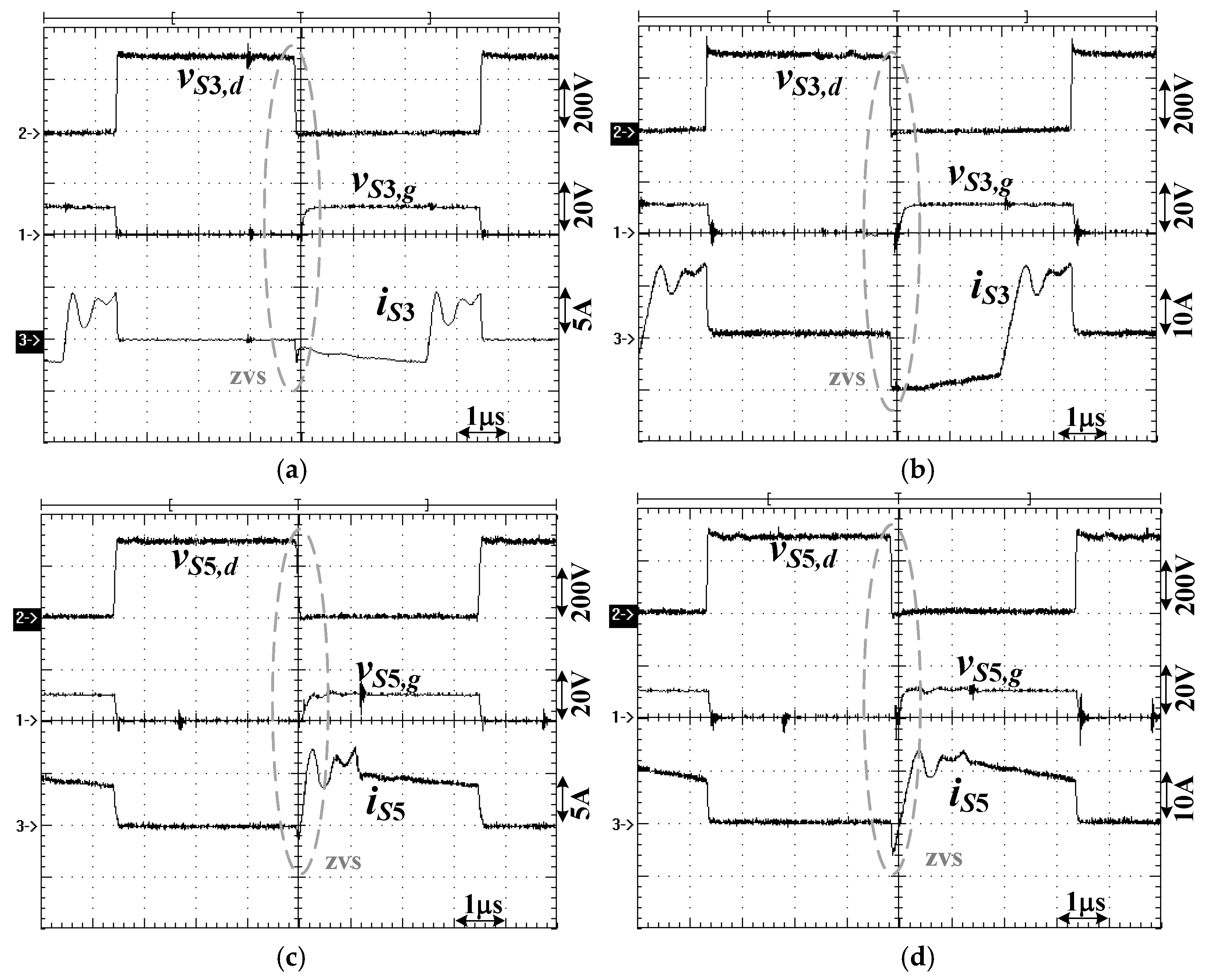

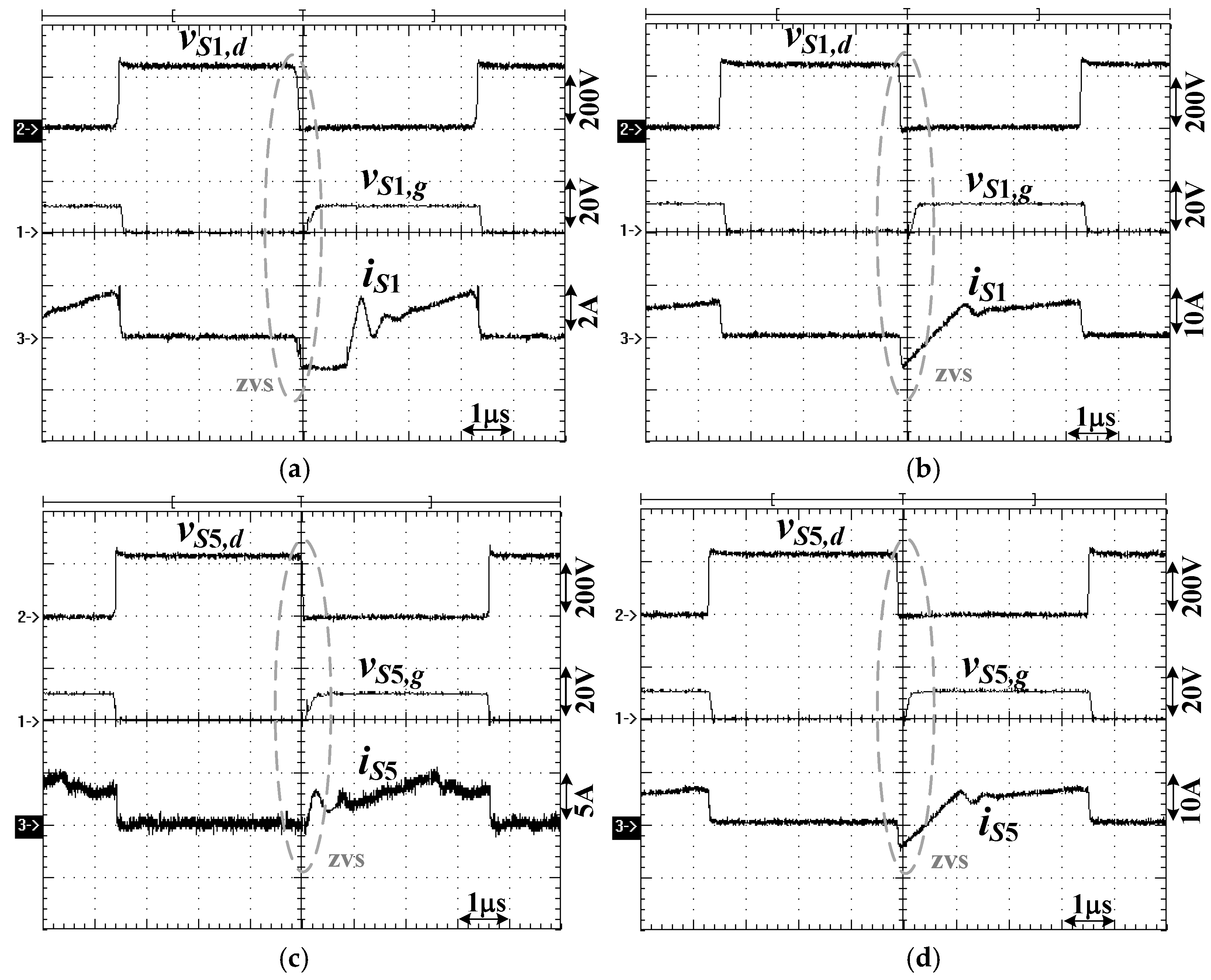

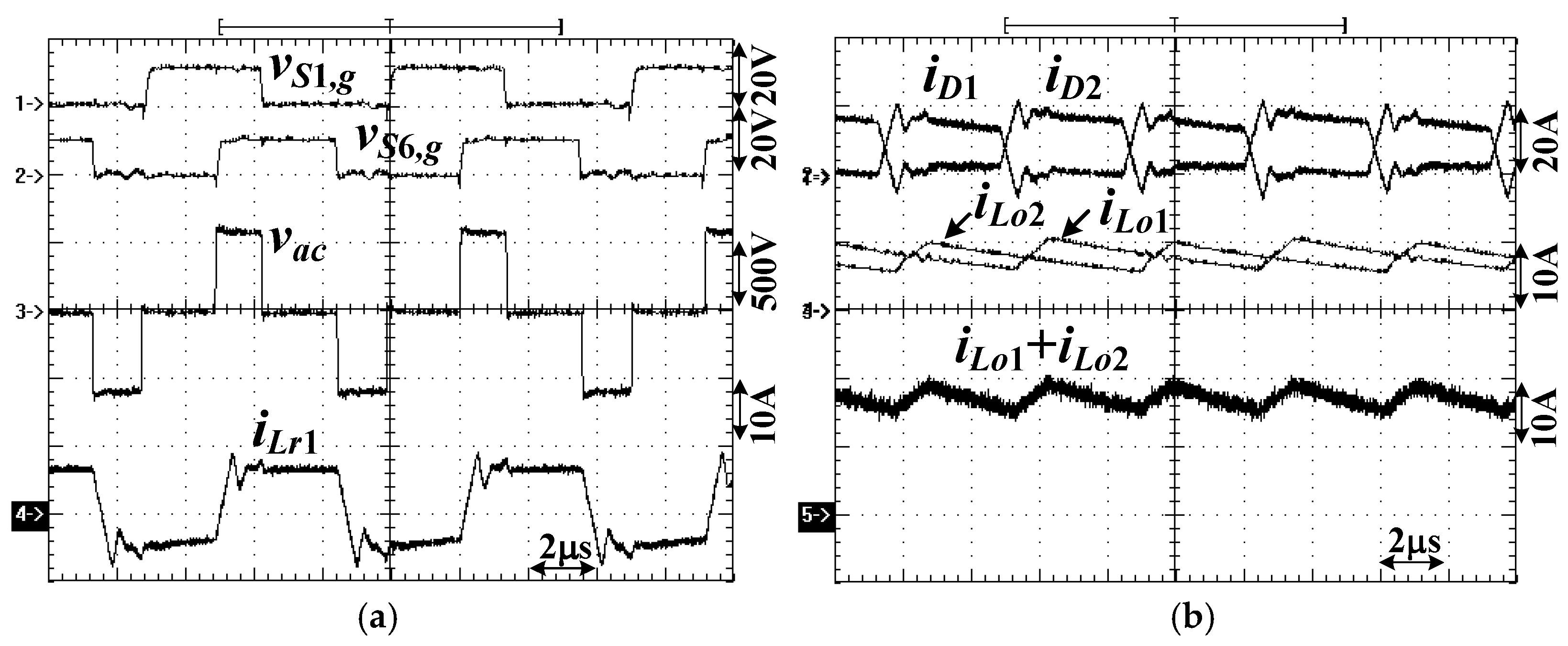

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Jumani, T.A.; Mustafa, M.W.; Rasid, M.M.; Anjum, W.; Ayub, S. Salp Swarm Optimization Algorithm-Based Controller for Dynamic Response and Power Quality Enhancement of an Islanded Microgrid. Processes 2019, 7, 840. [Google Scholar] [CrossRef] [Green Version]

- Nasir, M.; Iqbal, S.; Khan, H.A.; Guerrero, J.M. Sustainable Rural Electrification Through Solar PV DC Microgrids—An Architecture-Based Assessment. Processes 2020, 8, 1417. [Google Scholar] [CrossRef]

- Luo, Z.; Zhu, Z.; Zhang, Z.; Qin, J.; Wang, H.; Gao, Z.; Yang, Z. Multi-Time-Scale Rolling Optimal Dispatch for Grid-Connected AC/DC Hybrid Microgrids. Processes 2019, 7, 961. [Google Scholar] [CrossRef] [Green Version]

- Sheng, W.; Hong, Y.; Wu, M.; Ji, Y. A Cooperative Control Scheme for AC/DC Hybrid Autonomous Microgrids. Processes 2020, 8, 311. [Google Scholar] [CrossRef] [Green Version]

- Jiang, Y.; Jin, X.; Wang, H.; Fu, Y.; Ge, W.; Yang, B.; Yu, T. Optimal Nonlinear Adaptive Control for Voltage Source Converters via Memetic Salp Swarm Algorithm: Design and Hardware Implementation. Processes 2019, 7, 490. [Google Scholar] [CrossRef] [Green Version]

- Ali, H.G.; Arbos, R.V.; Herrera, J.; Peláez-Restrepo, J. Non-Linear Sliding Mode Controller for Photovoltaic Panels with Maximum Power Point Tracking. Processes 2020, 8, 108. [Google Scholar]

- Lin, B.R. Hybrid dc/dc Converter Based on Dual Three-Level Circuit and Half-Bridge Circuit. IET Power Electron. 2016, 9, 817–824. [Google Scholar] [CrossRef]

- Safaee, A.; Jain, P.; Bakhshai, A. A ZVS Pulsewidth Modulation Full-Bridge Converter with a Low rms Current Resonant Auxiliary Circuit. IEEE Trans. Power Electron. 2016, 31, 4031–4047. [Google Scholar] [CrossRef]

- Ren, R.; Liu, B.; Jones, E.A.; Wang, F.F.; Zhang, Z.; Costinett, D. Capacitor-Clamped, Three-Level Gan-Based dc-dc Converter with Dual Voltage Outputs for Battery Charger Applications. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 841–853. [Google Scholar] [CrossRef]

- Steigerwald, R.L. A Comparison of Half-Bridge Resonant Converter Topologies. IEEE Trans. Power Electron. 1988, 3, 174–182. [Google Scholar] [CrossRef]

- Lin, B.R.; Chu, C.W. Hybrid Full-Bridge and LLC Converter with Wide ZVS Range and Less Output Inductance. IET Power Electron. 2016, 9, 377–384. [Google Scholar] [CrossRef]

- Lee, J.B.; Kim, J.K.; Baek, J.I.; Kim, J.H.; Moon, G.W. Resonant Capacitor on/off Control of Half-Bridge LLC Converter for High Efficiency Server Power Supply. IEEE Trans. Ind. Electron. 2016, 63, 5410–5415. [Google Scholar] [CrossRef]

- Jeong, Y.; Kim, J.K.; Lee, J.B.; Moon, G.W. An Asymmetric Half-Bridge Resonant Converter Having a Reduced Conduction Loss for DC/DC Power Applications with a Wide Range of Low Input Voltage. IEEE Trans. Power Electron. 2017, 32, 7795–7804. [Google Scholar] [CrossRef]

- Zhang, Y.; Fu, C.; Sumner, M.; Wang, P. A Wide Input-Voltage Range Quasi-Z-Source Boost DC–DC Converter with High-Voltage Gain for Fuel Cell Vehicles. IEEE Trans. Ind. Electron. 2018, 65, 5201–5212. [Google Scholar] [CrossRef] [Green Version]

- Wang, P.; Zhou, L.; Zhang, Y.; Li, J.; Sumner, M. Input-Parallel Output-Series DC-DC Boost Converter with a Wide Input Voltage Range, for Fuel Cell Vehicles. IEEE Trans. Veh. Tech. 2017, 66, 7771–7781. [Google Scholar] [CrossRef]

- Wang, X.; Tian, F.; Batarseh, I. High Efficiency Parallel Post Regulator for Wide Range Input DC-DC Converter. IEEE Trans. Power Electron. 2008, 23, 852–858. [Google Scholar] [CrossRef]

- Lu, J.; Kumar, A.; Afridi, K.K. Step-Down Impedance Control Network Resonant DC-DC Converter Utilizing an Enhanced Phase-Shift Control for Wide-Input-Range Operation. IEEE Trans. Ind. Appl. 2018, 54, 4523–4536. [Google Scholar] [CrossRef]

- Li, W.; Zong, S.; Liu, F.; Yang, H.; He, X.; Wu, B. Secondary-Side Phase-Shift-Controlled ZVS DC/DC Converter with Wide Voltage Gain for High Input Voltage Applications. IEEE Trans. Power Electron. 2013, 28, 5128–5139. [Google Scholar] [CrossRef]

- Kim, B.; Kim, S.; Hun, D.Y.; Choi, J.H.; Kim, M. Hybrid Resonant Half-Bridge DC/DC Converter with Wide Input Voltage Range. In Proceedings of the IEEE APEC Conference, San Antonio, TX, USA, 4–8 March 2018; pp. 1876–1881. [Google Scholar]

- Hu, H.; Fang, X.; Chen, F.; Shen, Z.J.; Batarseh, I. A Modified High-Efficiency LLC Converter with Two Transformers for Wide Input-Voltage Range Applications. IEEE Trans. Power Electron. 2013, 28, 1946–1960. [Google Scholar] [CrossRef]

- Lin, B.R.; Liu, Y.C. Analysis of a Wide Voltage Hybrid Soft Switching Converter. Electronics 2021, 10, 473. [Google Scholar] [CrossRef]

- Lin, B.R.; Ko, M.C. Investigation of a hybrid converter with 16:1 wide voltage operation. IET Proc. Electron. Lett. 2021, 57, 74–77. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lin, B.-R.; Peng, Y.-H. Analysis of a PWM Converter with Less Current Ripple, Wide Voltage Operation and Zero-Voltage Switching. Processes 2021, 9, 580. https://doi.org/10.3390/pr9040580

Lin B-R, Peng Y-H. Analysis of a PWM Converter with Less Current Ripple, Wide Voltage Operation and Zero-Voltage Switching. Processes. 2021; 9(4):580. https://doi.org/10.3390/pr9040580

Chicago/Turabian StyleLin, Bor-Ren, and Yi-Hao Peng. 2021. "Analysis of a PWM Converter with Less Current Ripple, Wide Voltage Operation and Zero-Voltage Switching" Processes 9, no. 4: 580. https://doi.org/10.3390/pr9040580

APA StyleLin, B.-R., & Peng, Y.-H. (2021). Analysis of a PWM Converter with Less Current Ripple, Wide Voltage Operation and Zero-Voltage Switching. Processes, 9(4), 580. https://doi.org/10.3390/pr9040580