Three-Phase Transformerless Buck-Inverter Topologies for PV Grid-Tied Systems: A Review

Abstract

1. Introduction

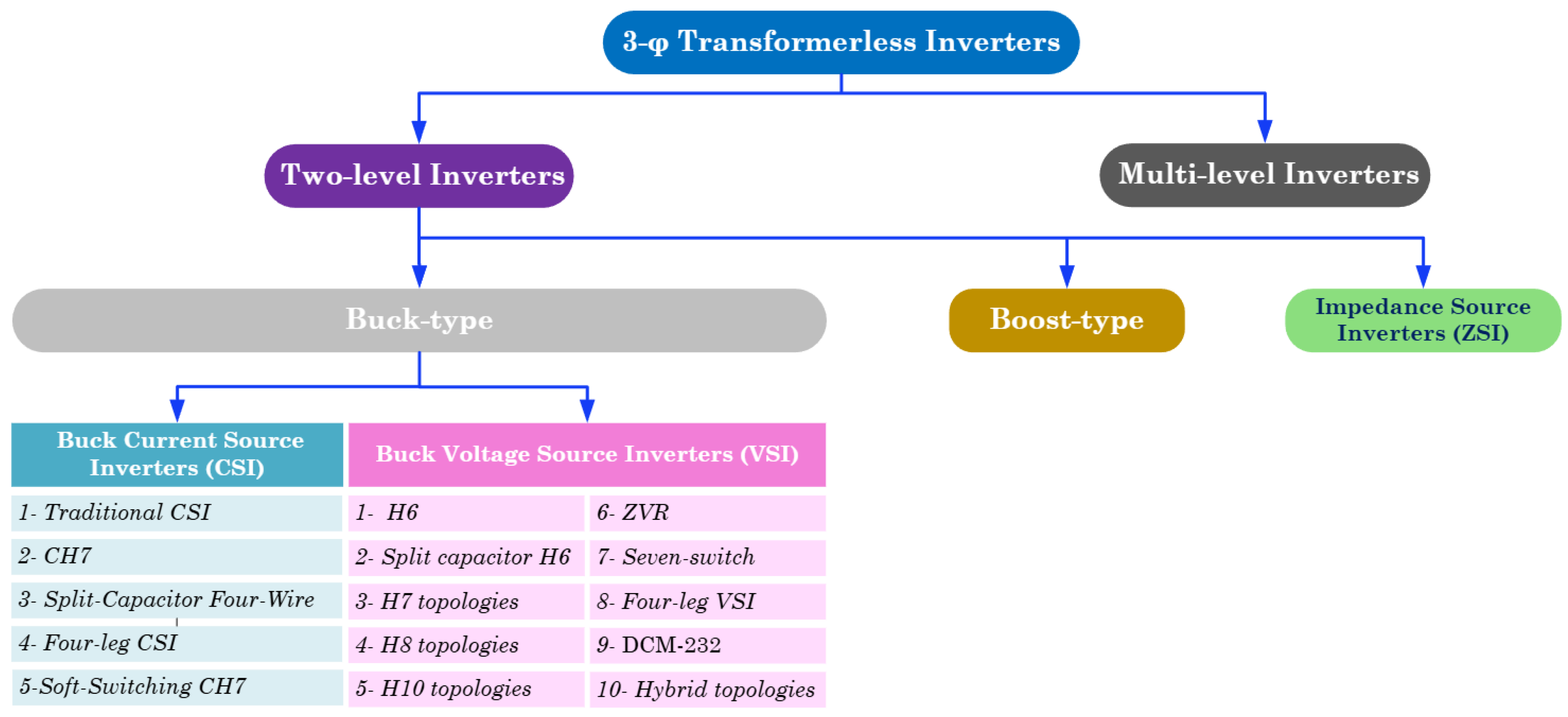

- Provides a comprehensive analysis: In contrast to previous evaluations that mostly concentrate on VSIs, it offers a thorough and parallel analysis of both three-phase buck voltage-source inverters (VSIs) and buck current-source inverters (CSIs).

- Targets a crucial niche: It provides a targeted resource that is unavailable in more general surveys that include boost and multilevel topologies by providing a detailed, specialized examination of two-level buck inverters for CMV reduction.

- Features new advanced topologies: It includes a detailed explanation and categorization of new and uncommon topologies that were left out or not fully discussed in previous comparison studies, including H10, four-leg, ZVR, DCM-232, and hybrid configurations.

2. Preliminary of Three-Phase Transformerless PV Inverters

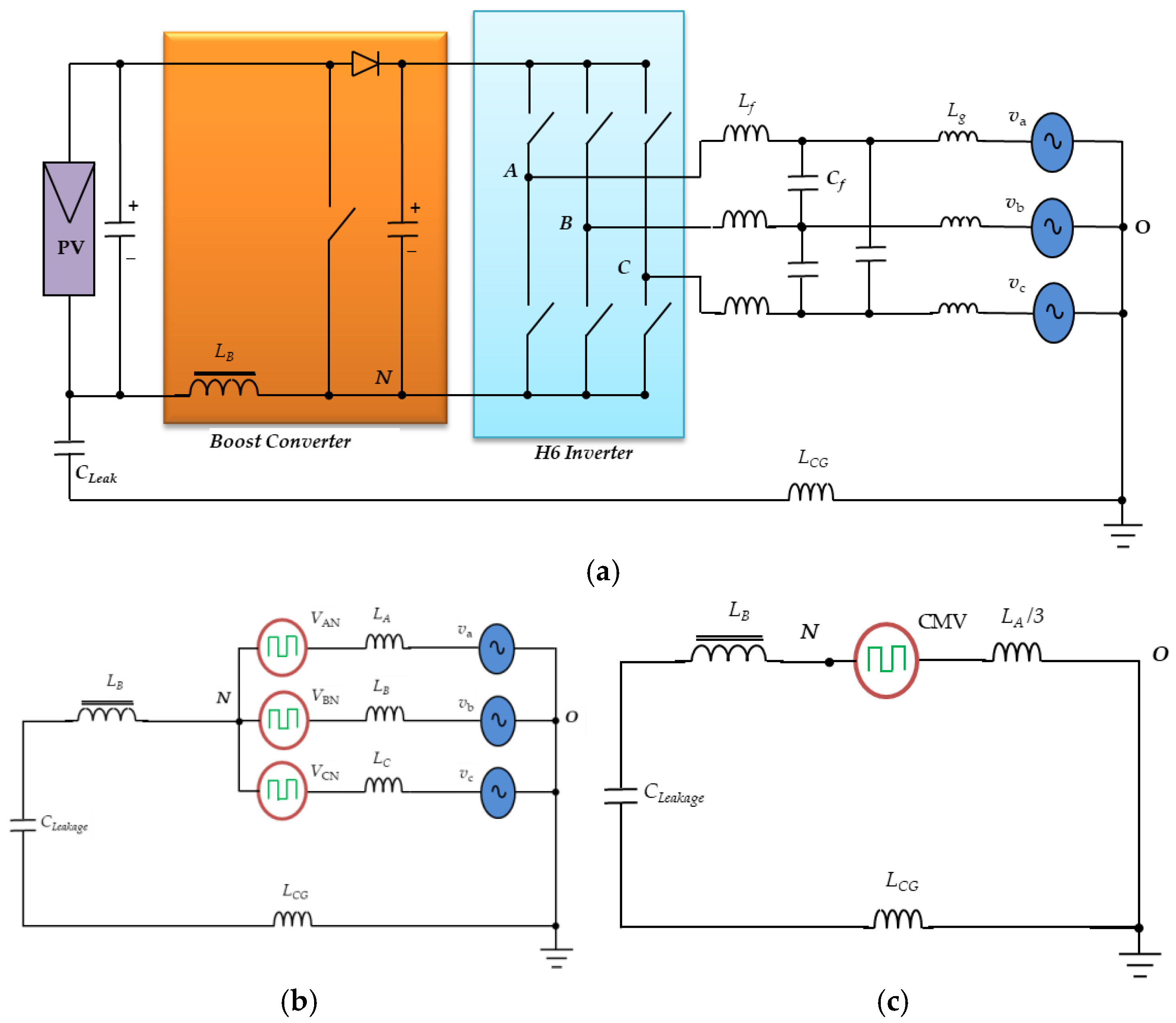

2.1. Common-Mode Voltage and Leakage Current Concerns

2.2. Utility Constraints and Standards

2.3. Clarification of Common-Mode Voltage and Leakage Current Relationship

3. Three-Phase Transformerless PV Inverter Topologies

3.1. Buck Voltage Source Inverter Topologies

3.1.1. Three-Phase Full Bridge (H6)

3.1.2. Three-Phase Full Bridge with Split Capacitor (NPC H6)

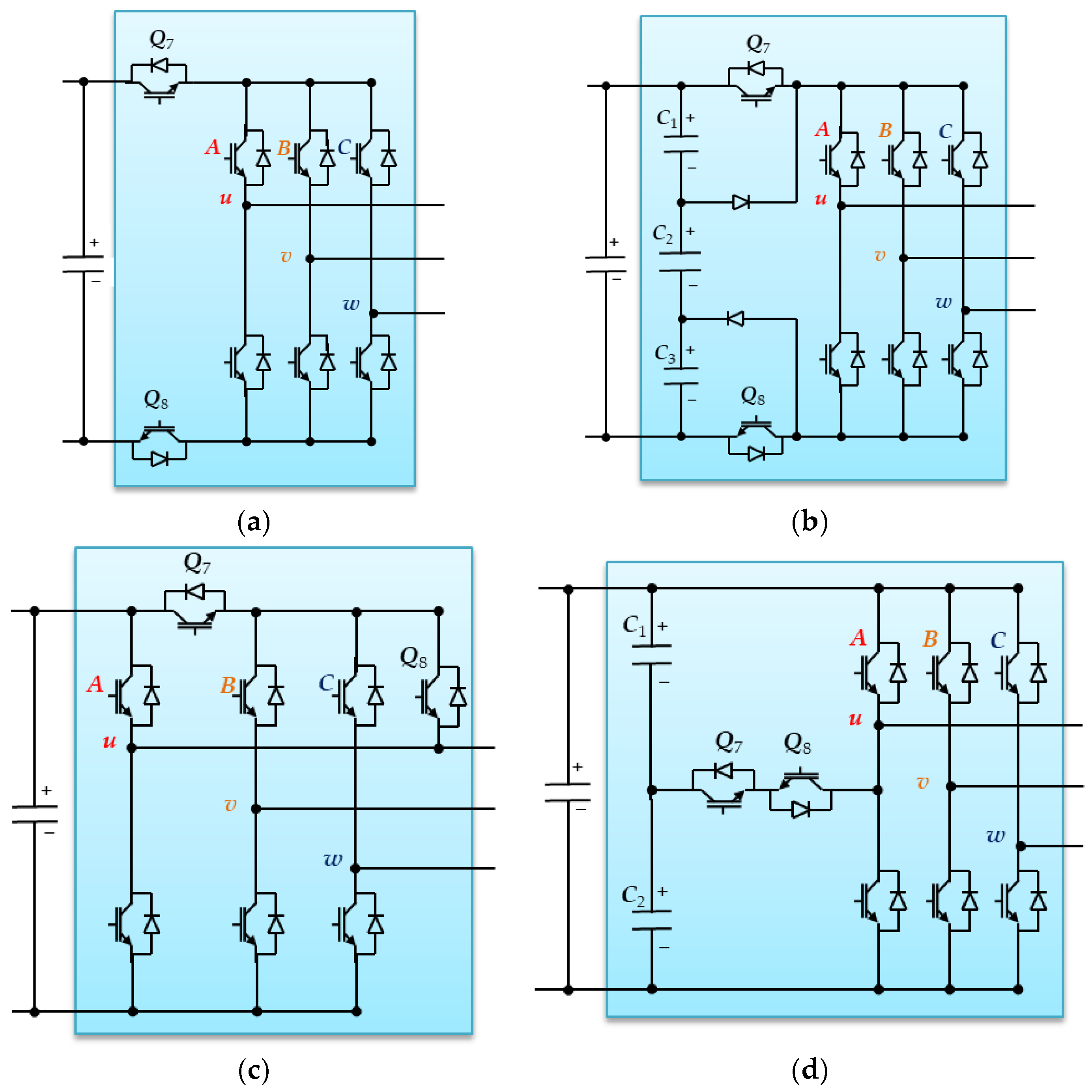

3.1.3. Three-Phase H7 Topologies

3.1.4. Three-Phase H8 Topologies

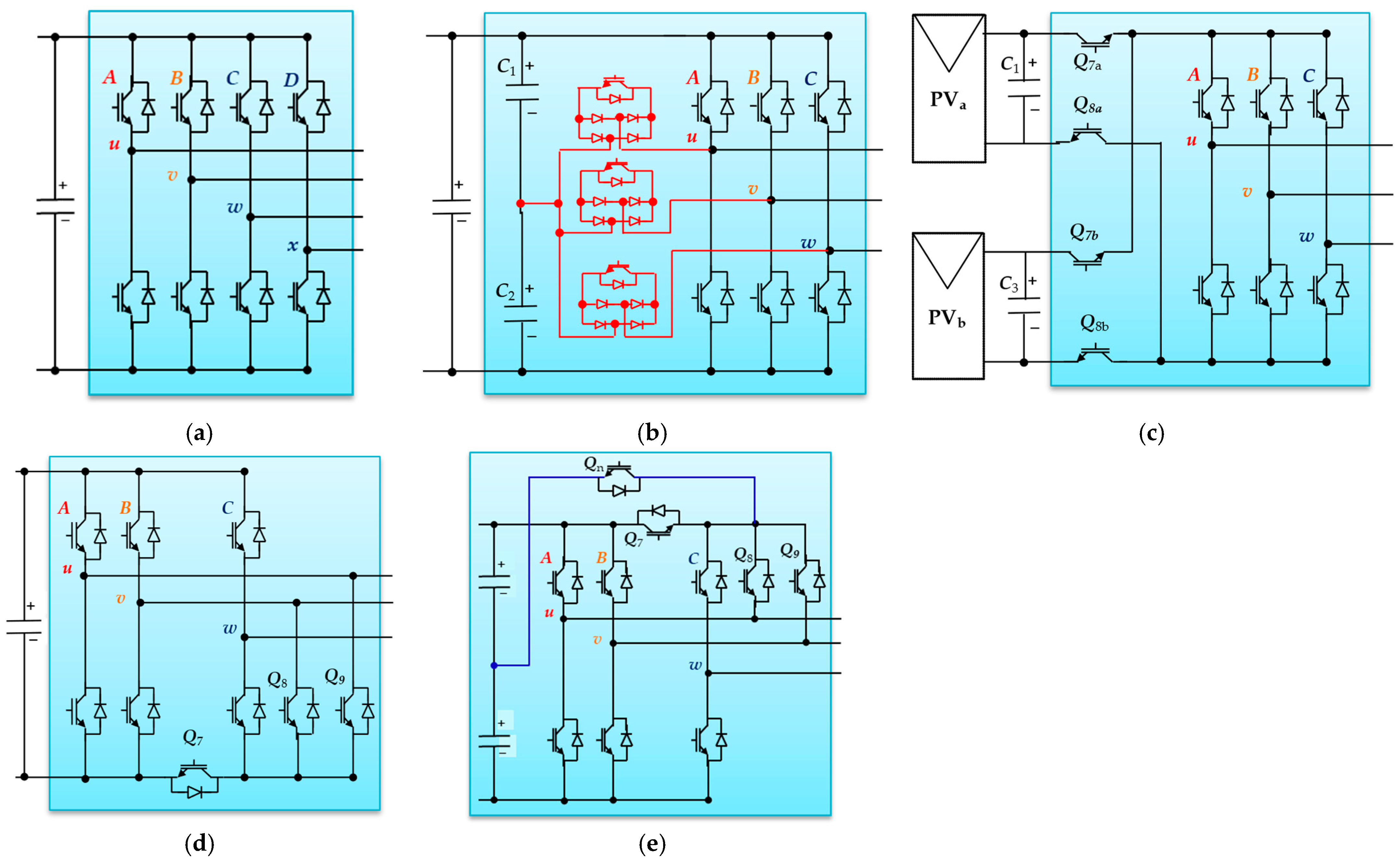

3.1.5. Three-Phase H10 Topologies

3.1.6. Three-Phase Four-Leg Topology

3.1.7. Three-Phase ZVR Topology

3.1.8. Three-Phase DCM-232 Topology

3.1.9. Three-Phase Hybrid Transformerless Inverter Topologies

3.2. Current-Source Topologies

3.2.1. Traditional CSI Topology

3.2.2. H7 CSI Topology or CH7

3.2.3. Split-Capacitor Four-Wire CSI Topology

3.2.4. Four Leg CSI Topology

3.3. Modulation Strategies for CMV and Leakage Current Suppression

- Active Zero-Vector Modulation: This technique substitutes opposing active vectors that provide the same output voltage but a different CMV for the conventional zero vectors (V0, V7). For example, to synthesize a zero vector while keeping the CMV at a constant, lowered level, V4 (110) and V1 (100) can be utilized in combination rather than V0 (000) [17,36]. Although very successful, this may result in higher switching losses.

- Near-State Modulation: This method effectively prevents big CMV jumps by limiting the selection of switching vectors to those that are adjacent to one another in the space vector hexagon. The dv/dt across the parasitic capacitance is directly limited by the peak-to-peak CMV, which is greatly decreased by never, for instance, changing from an “all-high” state to an “all-low” state [35].

- Discontinuous PWM (DPWM): For 120° intervals per basic cycle, the DPWM family, which includes particular variations like DPWM0, DPWM1, and DPWM2, intentionally clamps each phase to the positive or negative DC rail. When compared to continuous PWM, this clamping reduces the average switching frequency and, consequently, switches losses by up to 33% by eliminating all switching events during the clamped phase [28,29]. The particular clamping pattern affects the CMV spectrum even though it is largely a loss-reduction technique.

- Modified Discontinuous PWM (MDPWM): This sophisticated DPWM technique maximizes the clamping period for both CMV reduction and loss minimization. MDPWM can maintain the CMV within a narrower band (e.g., Vdc/3 to 2 Vdc/3) while maintaining its low-loss characteristics by carefully choosing the clamping instants based on the common-mode voltage of the active vectors. This makes it especially appropriate for high-efficiency transformerless PV applications [28,29].

- Randomized PWM (RPWM): RPWM distributes the harmonic energy of the CMV over a continuous band by randomizing the switching frequency rather than concentrating on the CMV magnitude. This “spread-spectrum” method lowers peak electromagnetic interference (EMI) and removes the high-frequency tonal noise that comes with fixed-frequency PWM, both of which are advantageous for meeting EMC regulations [20].

4. Conclusions

- VSI Topologies: Although straightforward and reasonably priced, the traditional H6 inverter naturally generates large CMV fluctuations, which result in leakage currents that frequently fall short of safety requirements. Advanced topologies, like H8 and H10, exhibit better balance between complexity and performance, especially in their optimized configurations. These topologies successfully limit the CMV to a range of Vdc/3 to 2 Vdc/3 by incorporating extra switching states. They significantly reduce switching loss and leakage current when combined with sophisticated modulation techniques, particularly MDPWM, reducing the latter down to levels allowed by international standards.

- CSI Topologies: Because of their topological features, which inherently restrict CMV dynamics, transformerless CSIs have an intrinsic advantage in suppressing leakage current. They are therefore a strong option in terms of EMI and safety. Practical disadvantages, such as increased cost, increased size and weight because of the necessary DC-link inductors, and more complicated control and MPPT interfacing, offset this advantage. In contrast to the more established VSI alternatives, these issues have restricted their commercial penetration.

- Overall Trade-off: In the end, choosing the best topology involves a definite engineering trade-off. In terms of peak conversion efficiency, component maturity, and cost-effectiveness, VSI-based architectures are currently at the forefront. On the other hand, CSI-based architectures are superior in terms of fault tolerance, short-circuit protection, and leakage current suppression.

- Intelligent Control and Modulation: To further optimize the trade-off between CMV suppression, switching loss, and output power quality, adaptive, real-time modulation techniques that can react dynamically to shifting grid conditions, PV array impedance, and component aging are being developed.

- Integration of WBG Semiconductors: SiC and GaN device research is essential, especially for high-frequency VSIs and CSIs. Complex, high-performance topologies can become more feasible with WBG technology’s ability to significantly lower switching losses, allow greater switching frequencies to reduce the bulk of passive components, and possibly push peak efficiency above 99%.

- Optimizing Multilevel and Hybrid Architectures: In order to better balance performance and the quantity of active components, future research should concentrate on improving the previously suggested hybrid and NPC-hybrid inverters. Additionally, with specialized modulation methods, the potential of four-leg topologies to manage unbalanced loads and deliver a constant CMV should be further explored.

- Expanded System-Level Analysis: This work should be expanded upon in future reviews by delving deeply into one-stage boost-derived topologies (such as Z-source and quasi-switched boost inverters), sophisticated soft-switching strategies to reduce losses, and the unique control difficulties associated with integrating these transformerless systems into distorted and weak grids.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Nomenclature

| Acronym | Definition |

| PV | Photovoltaic |

| CMV | Common-Mode Voltage |

| CMC | Common-Mode Current |

| DMV | Differential-Mode Voltage |

| THD | Total Harmonic Distortion |

| DC | Direct Current |

| AC | Alternating Current |

| VSI | Voltage Source Inverter |

| CSI | Current Source Inverter |

| PWM | Pulse Width Modulation |

| SPWM | Sinusoidal Pulse Width Modulation |

| SVPWM | Space Vector Pulse Width Modulation |

| RSPWM | Randomized Sinusoidal Pulse Width Modulation |

| MDPWM | Modified Discontinuous Pulse Width Modulation |

| MPPT | Maximum Power Point Tracking |

| DCM | Discontinuous Conduction Mode |

| HERIC | Highly Efficient and Reliable Inverter Concept |

| WBG | Integration of Wide-Bandgap |

| H5/H6/H7/H8/H9/H10 | Transformerless inverter topologies (numbers denote number of switches) |

| oH6/oH8 | Optimized or modified versions of H6 and H8 topologies |

| FC-H10 | Forward-Clamped H10 Inverter |

| RC-H10 | Reverse-Clamped H10 Inverter |

| NPC | Neutral Point Clamped |

| EMI | Electromagnetic Interference |

| LCL | Inductor–Capacitor–Inductor filter |

| P&O | Perturb and Observe (MPPT algorithm) |

| DC-Link | Intermediate link between the PV array and the inverter |

| η | Efficiency |

| IEEE/IET | Institute of Electrical and Electronics Engineers/Institution of Engineering and Technology |

| Vdc | DC-link voltage |

| VAN, VBN, VCN | Phase voltages with respect to the neutral point |

| VAO, VBO, VCO | Pole voltages of inverter legs |

| VCMV | Common-mode voltage |

| VMN | Voltage between the inverter midpoint (M) and neutral (N) |

| Ileak | Leakage current |

| ia, ib, ic | Phase currents |

| LCG | Parasitic capacitance between the PV array and the ground |

| ω | Angular frequency (rad/s) |

| ZA, ZB, ZC | Phase impedances |

| XB | Branch impedance affecting leakage current |

| Ts | Switching period |

| Tl, Tm, Tn | Dwell times of space vectors |

| mpq | Switching function variable (1 if ON, 0 if OFF) |

| x, y | Reference vector coordinates in SVPWM analysis |

| k | CMV index in SVPWM sequence |

| dv/dt | Voltage rate of change (slope of voltage transitions) |

| η | Efficiency of the inverter (%) |

| Cf, Lf | Filter capacitor and inductor, respectively |

| M | Modulation index |

References

- Blaabjerg, F.; Teodorescu, T.; Liserre, M.; Timbus, A.V. Overview of control and grid synchronization for distributed power generation systems. IEEE Trans. Ind. Electron. 2006, 53, 1398–1409. [Google Scholar] [CrossRef]

- Our World in Data. Installed Solar PV Capacity. Available online: https://ourworldindata.org/grapher/installed-solar-pv-capacity (accessed on 26 September 2025).

- International Energy Agency Photovoltaic Power Systems Programme (IEA-PVPS). Trends in Photovoltaic Applications 2024. Available online: https://iea-pvps.org/wp-content/uploads/2024/10/IEA-PVPS-Task-1-Trends-Report-2024.pdf (accessed on 21 April 2025).

- International Renewable Energy Agency (IRENA). Solar Energy Technology Brief. Available online: https://www.irena.org/Energy-Transition/Technology/Solar-energy (accessed on 26 September 2025).

- Freddy, T.K.S.; Rahim, N.A. Photovoltaic inverter topologies for grid integration applications. In Advances in Solar Photovoltaic Power Plants; Springer: Berlin/Heidelberg, Germany, 2016; pp. 13–42. [Google Scholar]

- Kjaer, S.B.; Pedersen, J.K.; Blaabjerg, F. A review of single-phase grid-connected inverters for photovoltaic modules. IEEE Trans. Ind. Appl. 2005, 41, 1292–1306. [Google Scholar] [CrossRef]

- Xiao, H.; Xie, S.; Chen, Y.; Huang, R. An optimized transformerless photovoltaic grid-connected inverter. IEEE Trans. Ind. Electron. 2011, 58, 1887–1895. [Google Scholar] [CrossRef]

- Meneses, D.; Blaabjerg, F.; García, Ó.; Cobos, J.A. Review and comparison of step-up transformerless topologies for photovoltaic AC-module applications. IEEE Trans. Power Electron. 2013, 28, 2649–2663. [Google Scholar] [CrossRef]

- Zaid, S.A.; Kassem, A.M. Review, analysis and improving the utilization factor of a PV-grid connected system via HERIC transformerless approach. Renew. Sustain. Energy Rev. 2017, 73, 1061–1069. [Google Scholar] [CrossRef]

- National Renewable Energy Laboratory (NREL). A Review of PV Inverter Technology Cost and Performance Projections. Available online: https://docs.nrel.gov/docs/fy06osti/38771.pdf (accessed on 5 January 2006).

- Kibria, M.F.; Elsanabary, A.; Tey, K.S.; Mubin, M.; Mekhilef, S. A comparative review on single-phase transformerless inverter topologies for grid-connected photovoltaic systems. Energies 2023, 16, 1363. [Google Scholar] [CrossRef]

- Gonzalez, R.; Lopez, J.; Sanchis, P.; Marroyo, L. Transformerless inverter for single-phase photovoltaic systems. IEEE Trans. Power Electron. 2007, 22, 693–697. [Google Scholar] [CrossRef]

- Kerekes, T.; Teodorescu, R.; Rodríguez, P.; Vázquez, G.; Aldabas, E. A new high-efficiency single-phase transformerless PV inverter topology. IEEE Trans. Ind. Electron. 2011, 58, 184–191. [Google Scholar] [CrossRef]

- VDE 0126-1-1-2006; Automatic Disconnection Device Between a Generator and the Public Low-Voltage Grid. EnergyVille: Genk, Belgium, 2008.

- Elbalawi, H.; Zaid, S.A. H5 transformerless inverter for grid-connected PV system with improved utilization factor and simple maximum power point algorithm. Energies 2018, 11, 2912. [Google Scholar] [CrossRef]

- Freddy, T.K.S.; Rahim, N.A.; Hew, W.; Che, H.S. Comparison and analysis of single-phase transformerless grid-connected PV inverters. IEEE Trans. Power Electron. 2014, 29, 5358–5369. [Google Scholar] [CrossRef]

- Hou, C.; Shih, C.; Cheng, P.; Hava, A.M. Common-mode voltage reduction pulse-width modulation techniques for three-phase grid-connected converters. IEEE Trans. Power Electron. 2013, 28, 1971–1979. [Google Scholar] [CrossRef]

- Guo, X.; Wei, B.; Zhu, T.; Lu, Z.; Tan, L. Leakage current suppression of three-phase flying-capacitor PV inverter with new carrier modulation and logic function. IEEE Trans. Power Electron. 2018, 33, 2127–2135. [Google Scholar] [CrossRef]

- Guo, X.; He, R.; Jian, J.; Lu, Z.; Sun, X. Leakage current elimination of four-leg inverter for transformerless three-phase PV systems. IEEE Trans. Power Electron. 2016, 31, 1841–1846. [Google Scholar] [CrossRef]

- Hasanzad, F.; Rastegar, H.; Pichan, M. Performance evaluation of space vector modulation techniques for reducing leakage current of a three-phase four-leg PV inverter. In Proceedings of the 2017 Iranian Conference on Electrical Engineering (ICEE), Tehran, Iran, 2–4 May 2017; pp. 1026–1031. [Google Scholar]

- Gupta, A.K.; Agrawal, H.; Agarwal, V. A novel three-phase transformerless H8 topology with reduced leakage current for grid-tied solar PV applications. IEEE Trans. Ind. Appl. 2019, 55, 1765–1774. [Google Scholar] [CrossRef]

- Morris, C.T.; Han, D.; Sarlioglu, B. Reduction of common-mode voltage and conducted EMI through three-phase inverter topology. IEEE Trans. Power Electron. 2017, 32, 1720–1724. [Google Scholar] [CrossRef]

- Hassan, J.; Minambres-Marcos, V.; Barrero-Gonzalez, F.; Alvi, A.A.; Malinowski, M.; Martinez-Caballero, L. A comparative study of three-phase inverter topologies for common-mode voltage reduction in photovoltaic applications. In Proceedings of the 2023 25th European Conference on Power Electronics and Applications (EPE’23 ECCE Europe), Aalborg, Denmark, 4–8 September 2023; pp. 1–8. [Google Scholar]

- Duong, T.D.; Nguyen, M.K.; Tran, T.T.; Vo, D.V.; Lim, Y.C.; Choi, J.H. Topology review of three-phase two-level transformerless photovoltaic inverters for common-mode voltage reduction. Energies 2022, 15, 3106. [Google Scholar] [CrossRef]

- Karneddi, H.; Ronanki, D.; Dekka, A. Leakage current analysis of grid-connected transformerless photovoltaic energy systems. In Proceedings of the 2022 IEEE 1st Industrial Electronics Society Annual On-Line Conference (ONCON), Kharagpur, India, 9–11 December 2022; pp. 1–6. [Google Scholar]

- Kolantla, D.; Mikkili, S.; Pendem, S.R.; Desai, A.A. Critical review on various inverter topologies for PV system architectures. IET Renew. Power Gener. 2020, 14, 3418–3438. [Google Scholar] [CrossRef]

- Rath, I.C.; Shukla, A. Review of three-phase transformerless PV converters. In Proceedings of the 2019 IEEE International Conference on Sustainable Energy Technologies and Systems (ICSETS), Bhubaneswar, India, 26 February–1 March 2019; pp. 63–68. [Google Scholar]

- Kumar, A.; Ramasamy, S.; Losito, M.; Gatto, G. Performance analysis of various three-phase hybrid transformerless inverter configurations. IET Power Electron. 2025, 18, e70107. [Google Scholar] [CrossRef]

- Ronanki, D.; Sang, P.H.; Sood, V.; Williamson, S.S. Comparative assessment of three-phase transformerless grid-connected solar inverters. In Proceedings of the 2017 IEEE International Conference on Industrial Technology (ICIT), Toronto, ON, Canada, 22–25 March 2017; pp. 66–71. [Google Scholar]

- Zhao, T.; Bhavaraju, V.; Nirantare, P.; Xu, J. Evaluation of commercial-scale transformerless solar inverter technology. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015; pp. 5342–5348. [Google Scholar]

- Bradaschia, F.; Cavalcanti, M.C.; Ferraz, P.E.; Neves, F.A.; Neto, C.M.D. Comparative study of topologies for three-phase transformerless photovoltaic systems. In Proceedings of the 2013 Brazilian Power Electronics Conference, Gramado, Brazil, 27–31 October 2013; pp. 493–500. [Google Scholar]

- Kerekes, T.; Teodorescu, R.; Liserre, M.; Klumpner, C.; Sumner, M. Evaluation of three-phase transformerless photovoltaic inverter topologies. IEEE Trans. Power Electron. 2009, 24, 2202–2211. [Google Scholar] [CrossRef]

- Guo, X.; Wang, N.; Wang, B.; Lu, Z.; Blaabjerg, F. Evaluation of three-phase transformerless DC-bypass PV inverters for leakage current reduction. IEEE Trans. Power Electron. 2020, 35, 5918–5927. [Google Scholar] [CrossRef]

- Petrone, G.; Spagnuolo, G.; Teodorescu, R.; Veerachary, M.; Vitelli, M. Reliability issues in photovoltaic power processing systems. IEEE Trans. Ind. Electron. 2008, 55, 2569–2580. [Google Scholar] [CrossRef]

- Concari, L.; Barater, D.; Buticchi, G.; Concari, C.; Liserre, M. H8 inverter for common-mode voltage reduction in electric drives. IEEE Trans. Ind. Appl. 2016, 52, 4010–4019. [Google Scholar] [CrossRef]

- Freddy, T.K.S.; Rahim, N.A.; Hew, W.; Che, H.S. Modulation techniques to reduce leakage current in three-phase transformerless H7 photovoltaic inverter. IEEE Trans. Ind. Electron. 2015, 62, 322–331. [Google Scholar] [CrossRef]

- Rahimi, R.; Farhadi, M.; Moradi, G.R.; Farhangi, B.; Farhangi, S. Three-phase filter-clamped transformerless inverter for grid-connected photovoltaic systems with low leakage current. IEEE Trans. Ind. Appl. 2020, 56, 1765–1774. [Google Scholar] [CrossRef]

- Atawi, I.; Zaid, S. Model predictive control of H7 transformerless inverter powered by PV. Intell. Autom. Soft Comput. 2022, 31, 449–469. [Google Scholar] [CrossRef]

- Sergent, J.S.; Coach, C.D.; Roux, R.J. National Electric Code Handbook; National Fire Protection Association: Quincy, MA, USA, 2011. [Google Scholar]

- DIN VDE 0126-1-1; DKE Deutsche Kommission Elektrotechnik Elektronik Informationstechnik im DIN und VDE. VDE: Bavaria, Germany, 2005.

- Kerekes, T.; Teodorescu, R.; Borup, U. Transformerless Photovoltaic Inverters Connected to the Grid. In Proceedings of the APEC 07—Twenty-Second Annual IEEE Applied Power Electronics Conference and Exposition, Anaheim, CA, USA, 25 February–1 March 2007; IEEE: Anaheim, CA, USA, 2007; pp. 1733–1737. [Google Scholar]

- Negesse, B.B.; Park, C.H.; Lee, S.H.; Hwang, S.W.; Kim, J.M. Optimized modulation method for common mode voltage reduction in H7 inverter. Energies 2021, 14, 6409. [Google Scholar] [CrossRef]

- Jeong, W.S.; Lee, Y.S.; Lee, J.H.; Lee, C.H.; Won, C.Y. Space vector modulation (SVM) based common mode current (CMC) reduction method of H8 inverter for permanent magnet synchronous motor (PMSM) Drives. Energies 2022, 15, 266. [Google Scholar] [CrossRef]

- Rahimi, R.; Farhangi, S.; Farhangi, B.; Moradi, G.R.; Afshari, E.; Blaabjerg, F. H8 inverter to reduce leakage current in transformerless three phase grid connected photovoltaic systems. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 910–918. [Google Scholar] [CrossRef]

- Arpan, H.; Vivek, A. Novel three phase H10 inverter topology with zero common mode voltage for three phase induction motor drive applications. IEEE Trans. Ind. Electron. 2022, 69, 7522–7525. [Google Scholar]

- Najafi, P.; Houshmand Viki, A.; Shahparasti, M.; Seyedalipour, S.S.; Pouresmaeil, E. A novel space vector modulation scheme for a 10 switch converter. Energies 2020, 13, 1855. [Google Scholar] [CrossRef]

- Guo, X.; Zhang, X.; Guan, H.; Kerekes, T.; Blaabjerg, F. Three phase ZVR topology and modulation strategy for transformerless PV system. IEEE Trans. Power Electron. 2019, 34, 1017–1021. [Google Scholar] [CrossRef]

- Guo, X.; Zhou, J.; He, R.; Jia, X.; Rojas, C.A. Leakage current attenuation of a three phase cascaded inverter for transformerless grid connected PV systems. IEEE Trans. Ind. Electron. 2018, 65, 676–686. [Google Scholar] [CrossRef]

- Tran, T.T.; Nguyen, M.K.; Duong, T.D.; Choi, J.H.; Lim, Y.C.; Zare, F. A switched capacitor voltage doubler-based boost inverter for common mode voltage reduction. IEEE Access 2019, 7, 98618–98629. [Google Scholar] [CrossRef]

- Tran, T.T.; Nguyen, M.K.; Ngo, V.Q.B.; Nguyen, H.N.; Duong, T.D.; Lim, Y.C.; Choi, J.H. A three phase constant common mode voltage inverter with triple voltage boost for transformerless photovoltaic system. IEEE Access 2020, 8, 166692–166702. [Google Scholar] [CrossRef]

- Hota, A.; Mohammad, M.Q.; Kirtley, J.L.; Vivek, A. Novel switched capacitor boost inverter configuration for three phase induction motor driven home appliances. IEEE Trans. Ind. Appl. 2021, 57, 1450–1458. [Google Scholar] [CrossRef]

- Hota, A.; Vivek, A. A Novel three phase induction motor drive with voltage boosting capability low current THD and low common-mode voltage. In Proceedings of the 2020 IEEE International Conference on the Power Electronics Drives and Energy Systems (PEDES), Jaipur, India, 16–19 December 2020; IEEE: Jaipur, India, 2020; pp. 1–4. [Google Scholar]

- Kharan, S.; Somasekhar, V.T. An Integrated Four-leg Three-phase Transformerless PV Inverter with Voltage Boosting Capability. In Proceedings of the 2020 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Jaipur, India, 16–19 December 2020; IEEE: Jaipur, India, 2020; pp. 1–5. [Google Scholar]

- Peng, F.Z. Z-source inverter. IEEE Trans. Ind. Appl. 2003, 39, 504–510. [Google Scholar] [CrossRef]

- Liu, Y.; Ge, B.; Abu, R.H.; Sun, D. Comprehensive modeling of single-phase quasi-Z-source photovoltaic inverter to investigate low frequency voltage and current ripple. IEEE Trans. Ind. Electron. 2015, 62, 4194–4202. [Google Scholar] [CrossRef]

- Siwakoti, Y.P.; Peng, F.Z.; Blaabjerg, F.; Loh, P.C.; Town, G.E. Impedance-Source Networks for Electric Power Conversion Part I: A Topological Review. IEEE Trans. Power Electron. 2015, 30, 699–716. [Google Scholar] [CrossRef]

- Nguyen, M.K.; Lim, Y.C.; Park, S.J. A Comparison Between Single Phase Quasi Z Source and Quasi Switched Boost Inverters. IEEE Trans. Ind. Electron. 2015, 62, 6336–6344. [Google Scholar] [CrossRef]

- Duong, T.D.; Nguyen, M.K.; Lim, Y.C.; Choi, J.H.; Mahinda, D.V. A comparison between quasi Z source inverter and active quasi Z source inverter. In Proceedings of the 2019 10th International Conference on Power Electronics and ECCE Asia (ICPE 2019-ECCE Asia), Busan, Republic of Korea, 27–30 May 2019; IEEE: Busan, Republic of Korea, 2019; pp. 1–6. [Google Scholar]

- Nguyen, M.K.; Le, T.V.; Park, S.J.; Lim, Y.C. A Class of Quasi-Switched Boost Inverters. IEEE Trans. Ind. Electron. 2015, 62, 1526–1536. [Google Scholar] [CrossRef]

- Barath, J.N.; Soundarrajan, A.; Stepenko, S.; Husev, O.; Vinnikov, D.; Nguyen, M.K. Topological Review of Quasi-Switched Boost Inverters. Electronics 2021, 10, 1485. [Google Scholar] [CrossRef]

- Nguyen, M.K.; Duong, T.D.; Lim, Y.C.; Choi, J.H.; Vilathgamuwa, D.M.; Walker, G.R. DC-Link quasi-switched boost inverter with improved PWM strategy and its comparative evaluation. IEEE Access 2020, 8, 53857–53867. [Google Scholar] [CrossRef]

- Nguyen, M.K.; Choi, Y.O. Maximum boost control method for single-phase quasi-switched-boost and quasi-Z-source inverters. Energies 2017, 10, 553. [Google Scholar] [CrossRef]

- Nguyen, M.K.; Duong, T.D.; Lim, Y.C.; Kim, Y.G. Switched-Capacitor Quasi-Switched Boost Inverters. IEEE Trans. Ind. Electron. 2017, 65, 5105–5113. [Google Scholar] [CrossRef]

- Hossameldin, A.A.; Abdelsalam, A.K.; Ibrahim, A.A.; Williams, B.W. Enhanced Performance Modified Discontinuous PWM Technique for Three-Phase Z-Source Inverter. Energies 2020, 13, 578. [Google Scholar] [CrossRef]

- Duong, T.D.; Nguyen, M.K.; Lim, Y.C.; Choi, J.H.; Vilathgamuwa, D.M. SiC-Based Active Quasi-Z-Source Inverter with Improved PWM Control Strategy. IET Power Electron. 2019, 12, 3810–3821. [Google Scholar] [CrossRef]

- Nguyen, M.K.; Duong, T.D.; Lim, Y.C.; Choi, J.H. High Voltage Gain Quasi-Switched Boost Inverters with Low Input Current Ripple. IEEE Trans. Ind. Inform. 2018, 15, 4857–4866. [Google Scholar] [CrossRef]

- Erginer, V.; Sarul, M.H. A novel reduced leakage-current modulation technique for Z source inverter used in photovoltaic systems. IET Power Electron. 2014, 7, 496–502. [Google Scholar] [CrossRef]

- Guo, X.; Yang, Y.; He, R.; Wang, B.; Blaabjerg, F. Leakage current reduction of three phase Z source three level four leg inverter for transformerless PV system. IEEE Trans. Power Electron. 2019, 34, 6299–6308. [Google Scholar] [CrossRef]

- Guo, X.; Yang, Y.; He, R.; Wang, B.; Blaabjerg, F. Transformerless Z source four leg PV inverter with leakage current reduction. IEEE Trans. Power Electron. 2019, 34, 4343–4352. [Google Scholar] [CrossRef]

- Bradaschia, F.; Cavalcanti, M.C.; Ferraz, P.E.P.; Neves, F.A.S. Modulation for three phase transformerless Z source inverter to reduce leakage currents in photovoltaic systems. IEEE Trans. Ind. Electron. 2011, 58, 5385–5395. [Google Scholar] [CrossRef]

- Ferraz, P.E.P.; Bradaschia, F.; Cavalcanti, M.C.; Neves, F.A.S.; Azevedo, G.M.S. A modified Z-source inverter topology for stable operation of transformerless photovoltaic systems with reduced leakage currents. In Proceedings of the XI Brazilian Power Electronics Conference, Natal, Brazil, 11–15 September 2011; IEEE: Natal, Brazil, 2011; pp. 615–622. [Google Scholar]

- Liu, W.; Yang, Y.; Kerekes, T. Modified Quasi-Z-Source Inverter with Model Predictive Control for Constant Common-Mode Voltage. In Proceedings of the ICPE-ECCE Asia, Busan, Republic of Korea, 27–30 May 2019; IEEE: Busan, Republic of Korea, 2019; pp. 1–6. [Google Scholar]

- Liu, W.; Yang, Y.; Kerekes, T.; Liivik, E.; Vinnikov, D.; Blaabjerg, F. Common-Mode Voltage Analysis and Reduction for the Quasi-Z-Source Inverter with a Split Inductor. Appl. Sci. 2020, 10, 8713. [Google Scholar] [CrossRef]

- Noroozi, N.; Zolghadri, M.R. Three phase quasi Z source inverter with constant common mode voltage for photovoltaic application. IEEE Trans. Ind. Electron. 2018, 65, 4790–4798. [Google Scholar] [CrossRef]

- Noroozi, N.; Yaghoubi, M.; Zolghadri, M.R. A modulation method for leakage current reduction in a three phase grid tie quasi Z source inverter. IEEE Trans. Power Electron. 2019, 34, 5439–5450. [Google Scholar] [CrossRef]

- Duong, T.D.; Nguyen, M.K.; Tran, T.T.; Lim, Y.C.; Choi, J.H.; Wang, C. Modulation Techniques for a Modified Three-Phase Quasi-Switched Boost Inverter with Common-Mode Voltage Reduction. IEEE Access 2020, 8, 160670–160683. [Google Scholar] [CrossRef]

- Nguyen, M.K.; Choi, Y.O. Modulation Technique for Modified Active Quasi-Z-Source Inverter with Common-Mode Voltage Reduction. Electronics 2021, 10, 2968. [Google Scholar] [CrossRef]

- Duong, T.D.; Nguyen, M.K.; Tran, T.T.; Vo, D.V.; Lim, Y.C.; Choi, J.H. Three-Phase Impedance-Source Inverter with Common-Mode Voltage Reduction. IEEE Access 2021, 9, 164510–164519. [Google Scholar] [CrossRef]

- Kharan, S.; Akash, S.; Rajeev, K.S. Transformerless Common Ground Quasi-Z-Source Three Phase Inverter for PV Applications. In Proceedings of the IECON 2020 the 46th Annual Conference of the IEEE Industrial Electronics Society, Singapore, 18–21 October 2020; IEEE: Singapore, 2020; pp. 1935–1940. [Google Scholar]

- Chen, Y.; Smedley, K. Three-Phase Boost-Type Grid-Connected Inverter. IEEE Trans. Power Electron. 2008, 23, 2301–2309. [Google Scholar] [CrossRef]

- Guo, X.; Xu, D.; Wu, B. Three-phase seven-switch inverter with common mode voltage reduction for transformerless photovoltaic system. In Proceedings of the IECON 2014—40th Annual Conference of the IEEE Industrial Electronics Society, Dallas, TX, USA, 29 October–1 November 2014; IEEE: Dallas, TX, USA, 2014; pp. 2279–2284. [Google Scholar]

- Lorenzani, E.; Migliazza, G.; Immovilli, F.; Gerada, C.; Zhang, H.; Buticchi, G. Internal current return path for ground leakage current mitigation in current source inverters. IEEE Access 2019, 7, 96540–96548. [Google Scholar] [CrossRef]

- Guo, X. Three-phase ch7 inverter with a new space vector modulation to reduce leakage current for transformerless photovoltaic systems. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 708–712. [Google Scholar] [CrossRef]

- Wang, W.; Gao, F.; Yang, Y.; Blaabjerg, F. Operation and modulation of h7 current-source inverter with hybrid sic and si semiconductor switches. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 387–399. [Google Scholar] [CrossRef]

- Jeong, W.-S.; Kim, S.-H.; Yi, J.; Won, C.-Y. Finite Control Set–Model Predictive Control of H8 Inverter Considering Dead-Time Effect for PMSM Drive Systems with Reduced Conducted Common-Mode EMI and Current Distortions. IEEE Trans. Power Electron. 2022, 37, 5342–5356. [Google Scholar] [CrossRef]

- Xiang, Y.; Pei, X.; Wang, M.; Shi, P.; Kang, Y. An Improved H8 Topology for Common-Mode Voltage Reduction. IEEE Trans. Power Electron. 2019, 34, 5352–5361. [Google Scholar] [CrossRef]

- Zaid, S.A.; Albalawi, H.; AbdelMeguid, H.; Alhmiedat, T.A.; Bakeer, A. Performance Improvement of H8 Transformerless Grid-Tied Inverter Using Model Predictive Control Considering a Weak Grid. Processes 2022, 10, 1243. [Google Scholar] [CrossRef]

- Hota, A.; Agarwal, V. A New Three-Phase Inverter Topology for Reducing the dv/dt and Peak-to-Peak Value of Common Mode Voltage. IEEE Trans. Ind. Electron. 2022, 69, 11979–11986. [Google Scholar] [CrossRef]

- Ma, H.; Shao, P.; Lan, Z. Comparative analysis of leakage current suppression capability of forward-clamped and reverse-clamped H10 three-phase inverters. IET Power Electron. 2021, 14, 2563–2573. [Google Scholar] [CrossRef]

- Long, B.; Chen, Z.; Hu, C.; Yu, Y.; Rodriguez, J.; Guerrero, J.M. A nonclamped H10 topology to achieve leakage current reduction for transformerless grid-connected converter. IEEE J. Emerg. Sel. Top. Power Electron. 2024, 12, 1847–1858. [Google Scholar] [CrossRef]

- Tawfiq, K.B.; Zeineldin, H.; Al-Durra, A.; El-Saadany, E.F. Mitigation of Leakage Current and Current Harmonics in PV Grid-Connected Systems Using a New H10 Three-Phase Inverter. IEEE J. Emerg. Sel. Top. Power Electron. 2025, 13, 214–229. [Google Scholar] [CrossRef]

- Rojas, F.; Villalón, G.; Reyes, L.; Mora, A.; García, A.; Orellana, P. An Overview of Four-Leg Converters: Topologies, Modulations, Control and Applications. IEEE Access 2022, 10, 61277–61325. [Google Scholar] [CrossRef]

- Julian, A.; Lipo, T.; Oriti, G. Elimination of common-mode voltage in three-phase sinusoidal power converters. IEEE Trans. Power Electron. 1999, 14, 982–989. [Google Scholar] [CrossRef]

- Guo, X.; Xu, D.; Wu, B. New control strategy for DCM-232 three-phase PV inverter with constant common mode voltage and anti-islanding capability. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Dallas, TX, USA, 14–18 September 2014; IEEE: Dallas, TX, USA, 2014; pp. 5613–5617. [Google Scholar]

- Rodríguez, P.; Muñoz-Aguilar, R.S.; Vázquez, G.; Candela, I.; Aldabas, E.; Etxeberria-Otadui, I. Symmetrical ripple constant common mode voltage modulation strategy for DCM-232 three-phase PV topology. In Proceedings of the IECON 2011—37th Annual Conference of the IEEE Industrial Electronics Society, Melbourne, VIC, Australia, 7–10 November 2011; IEEE: Melbourne, VIC, Australia, 2011; pp. 2505–2510. [Google Scholar] [CrossRef]

- Roy, T.; Behera, R.K.; Panda, S.K. A Transformerless Single-Stage Three-Port Converter with Enhanced Efficiency for Hybrid PV-Battery Systems. IEEE Trans. Ind. Electron. 2024, 71, 354–365. [Google Scholar]

- Li, Y.; Wang, Y.; Wang, H.; Blaabjerg, F. A Family of Single-Phase Hybrid Transformerless Inverters with Leakage Current Elimination for PV Systems. IEEE Trans. Power Electron. 2023, 38, 10889–10903. [Google Scholar]

- Hossain, M.A.; Tummuru, N.R.; Mishra, M.K. A Switched-Capacitor Based Single-Stage Transformerless PV Inverter with Common-Mode Voltage Decoupling. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 11, 5422–5434. [Google Scholar]

- Alatai, S.; Salem, M.; Pedersen, D.A.G.; Al-Durra, A.; Kumar, Y.J. A Novel Modulation Technique for Common-Mode Voltage Reduction in Three-Level NPC Inverters: Analysis and Experimental Validation. IEEE Trans. Ind. Appl. 2024, 60, 884–895. [Google Scholar]

- Chen, J.; Wu, X.; Zhang, J.; Wang, G. Model Predictive Control with Common-Mode Voltage Injection for Leakage Current Suppression in Transformerless PV Inverters. IEEE Trans. Power Electron. 2024, 39, 978–992. [Google Scholar]

- Danapour, N.; Akbari, E.; Tarafdar-Hagh, M. A Review on the Power Circuit Topologies of Current Source Inverters in Photovoltaic Applications. Iran. J. Electr. Electron. Eng. 2022, 18, 110–134. [Google Scholar]

- Estévez-Bén, A.A.; Alvarez-Diazcomas, A.; Macias-Bobadilla, G.; Rodríguez-Reséndiz, J. Leakage Current Reduction in Single-Phase Grid-Connected Inverters—A Review. Appl. Sci. 2020, 10, 2384. [Google Scholar] [CrossRef]

- Marignetti, F.; Di Stefano, R.L.; Rubino, G.; Giacomobono, R. Current source inverter (CSI) power converters in photovoltaic systems: A comprehensive review of performance, control, and integration. Energies 2023, 16, 7319. [Google Scholar] [CrossRef]

- Araújo, S.V.; Zacharias, P.; Mallwitz, R. Highly efficient single-phase transformerless inverters for grid-connected photovoltaic systems. IEEE Trans. Ind. Electron. 2009, 57, 3118–3128. [Google Scholar] [CrossRef]

- Fidone, G.L.; Migliazza, G.; Carfagna, E.; Benatti, D.; Immovilli, F.; Buticchi, G.; Lorenzani, E. Common architectures and devices for current source inverter in motor-drive applications: A comprehensive review. Energies 2023, 16, 5645. [Google Scholar] [CrossRef]

- Orfanoudakis, G.I.; Koutroulis, E.; Sharkh, S.M.; Yuratich, M.A. An extended boost three-phase transformerless PV inverter for common-mode leakage current reduction. IEEE Trans. Ind. Appl. 2023, 60, 838–850. [Google Scholar] [CrossRef]

- Azizi, A.; Akhbari, M.; Danyali, S.; Tohidinejad, Z.; Shirkhani, M. A review on topology and control strategies of high-power inverters in large-scale photovoltaic power plants. Heliyon 2025, 11, e42334. [Google Scholar] [CrossRef]

- Gao, H. High-frequency common-mode voltage mitigation for current-source inverter in transformerless photovoltaic system using active zero-state space vector modulation. IET Electr. Power Appl. 2023, 17, 245–255. [Google Scholar] [CrossRef]

- Shehada, A.; Beig, A.R. An improved CSI fed induction motor drive. Int. J. Electr. Power Energy Syst. 2013, 46, 26–35. [Google Scholar] [CrossRef]

- Anand, S.; Gundlapalli, S.K.; Fernandes, B.G. Transformer-less grid feeding current source inverter for solar photovoltaic system. IEEE Trans. Ind. Electron. 2014, 61, 5334–5344. [Google Scholar] [CrossRef]

- Lorenzani, E.; Migliazza, G.; Immovilli, F.; Buticchi, G. CSI and CSI7 current source inverters for modular transformerless PV inverters. Chin. J. Electr. Eng. 2019, 5, 32–42. [Google Scholar] [CrossRef]

- Wang, W.; Mu, H.; Cao, Z.; Wang, C.; Gao, F. Soft-switching H7 current source inverter. In Proceedings of the IEEE 8th International Power Electronics and Motion Control Conference (IPEMC-ECCE Asia), Hefei, China, 22–26 May 2016; IEEE: Hefei, China, 2016; pp. 2243–2248. [Google Scholar]

- Huang, Z.; Li, Q.; Lee, F.C. Improved three-phase critical-mode-based soft-switching modulation technique with low leakage current for PV inverter application. In Proceedings of the 2019 IEEE Energy Conversion Congress and Exposition (ECCE), Baltimore, MD, USA, 29 September–October 2019; IEEE: Baltimore, MD, USA, 2019. [Google Scholar]

- Jayanth, K.G.; Boddapati, V.; Geetha, R.S. Comparative study between three-leg and four-leg current-source inverter for solar PV application. In Proceedings of the IEEE International Conference on Power, Instrumentation, Control and Computing (PICC), Thrissur, India, 18–20 January 2018; IEEE: Thrissur, India, 2018; p. 16. [Google Scholar]

- Sun, Y.; Liu, Y.; Su, M.; Han, H.; Li, X.; Li, X. Topology and Control of a Split-Capacitor Four-Wire Current Source Inverter With Leakage Current Suppression Capability. IEEE Trans. Power Electron. 2018, 33, 10803–10814. [Google Scholar] [CrossRef]

- Guo, X.; Xu, D.; Wu, B. Four-leg current-source inverter with a new space vector modulation for common-mode voltage suppression. IEEE Trans. Ind. Electron. 2015, 62, 6003–6007. [Google Scholar] [CrossRef]

| Typical Attribute | Transformer-Based | Transformerless | Remarks |

|---|---|---|---|

| Application Type | Suitable for all PV systems, especially utility-scale plants where galvanic isolation is required. | Predominantly used in residential and commercial PV systems where weight, cost, and efficiency are priorities. | - |

| Typical Power Level | 10 kW—several MW. | 1–100 kW (typically ≤ 50 kW per unit). | - |

| Control/Modulation Strategy | Standard PWM or SPWM; simpler control; slower dynamic response due to transformer delay. | Advanced SPWM/SVPWM, predictive, or hybrid modulation to minimize CMV and leakage currents. | - |

| Power Quality (THD) | Typically, <3%; the transformer acts as a natural filter. | THD < 3% achievable with proper LCL filters and modulation. | - |

| Efficiency | Moderate (80–95%). | High (up to 98%). | TL inverters are generally more efficient (~1–4%). |

| Cost and Maintenance | High initial and maintenance costs due to transformer materials, insulation, and cooling requirements. | Lower cost, fewer magnetic components, and simpler installation. | TL cheaper at the system level (typical installed-hardware cost reduction on the order of ~10–30% depending on scale and design choices). |

| Size and Weight | Bulky and heavy because of the transformer; reduced power density. | Compact and lightweight, high-power density enables wall-mounted residential units. | TL smaller/lighter (≈30–70% reduction in size/weight for comparable power classes). |

| Leakage currents/EMI/CMV | Negligible (due to galvanic isolation). | Requires mitigation; CMV and leakage are typically reduced using advanced topologies and modulation (≤50 mA achievable). | Leakage currents to ground from TL topologies can be avoided with careful topology selection and monitoring. |

| Complexity | Simple | Moderate | - |

| Isolation & safety | Ensure galvanic isolation | No isolation (requires safety measures) | Additional standards/certifications are required for installing TL inverters. |

| Refs. | Year | Topologies | Comments |

|---|---|---|---|

| [23] | 2023 | Only H8, H6, H7, and NPC |

|

| [24] | 2022 | Two-level VSIs (buck and boost) and ZSI |

|

| [25] | 2022 | Two-level buck VSIs |

|

| [26] | 2020 | Some 1-φ and 3-φ commercial topologies |

|

| [27] | 2019 | VSIs (buck and boost) and some MLIs |

|

| Our work | 2025 | Two-level buck VSIs and buck CSIs |

|

| Refs. | Year | Topologies | PWM | Compared Factors | Results and Comments |

|---|---|---|---|---|---|

| [28] | 2025 | Hybrid (I and II) + NPC-hybrid (I and II) | Modified discontinuous | Switching losses, CMV, device stress, reactive power, and Ileak | The study evaluated hybrid and NPC hybrid inverter topologies using the MDPWM technique. The NPC hybrid inverter topology II showed the least variation in CMV, maintaining the THD within the grid limit and limited Ileak, meeting the standards. |

| [29] | 2017 | H6 + H7 + H8 | Modified discontinuous | CMV and Ileak | It finds that DPWM1 of the H6 inverter performs best but has high leakage current, making it unsafe for grid-connected inverters. Comparative analysis of H7 and H8 inverters with various PWM methods suggests that the H8 topology with a suitable PWM method offers better performance. |

| [30] | 2015 | Commercial topologies | SVPWM and modified PWM | Efficiency, reliability, CMV, cost, power density, and Ileak | Commercial-scale PV TL systems (50–250 kW) are compared. The pros and cons of different topologies are declared. An improved CMV filter is proposed. |

| [31] | 2013 | Two-stage H6 + ZSI-D + ZSI-S | Specific PWM | Switching losses, CMV, and Ileak | The two-stage converter with a specific modulation technique showed the best performance in terms of efficiency, number of devices, voltage rating, and cost, confirming its feasibility. |

| [32] | 2009 | H6 + split-H6 + NPC | Classical and interleaved PWM | CMV and Ileak | It revealed that the split capacitor topology results in low ripple voltage and Ileak below the standard requirements. However, the neutral inductance can lead to higher Ileak. |

| [33] | 2019 | Clamping and unclamping | Classical PWM | THD, CMV, and Ileak | The impact of clamping and unclamping DC-bypass switches on Ileak reduction is analyzed. It finds that unclamped H8 is the best choice for Ileak reduction, and future research should focus on soft-switching operation. |

| Switching State | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Topology | (1001) | (0101) | (0011) | (1101) | (0111) | (1011) | (0000) | (1111) | ||

| VCMV/Vdc | 1/3 | 2/3 | 1/3 | 2/3 | 1/3 | 2/3 | 1/3 | |||

| H6 | VCMV/Vdc | 1/3 | 2/3 | 1/3 | 2/3 | 1/3 | 2/3 | 0 | 1 | |

| H7 | VCMV/Vdc | 1/3 | 2/3 | 1/3 | 2/3 | 1/3 | 2/3 | 3/4 | 1 | |

| H8 [33] | VCMV/Vdc | 1/3 | 2/3 | 1/3 | 2/3 | 1/3 | 2/3 | 1/2 | - | |

| Max. ILeak (mA) | tbreak (s) | tdis (s) |

|---|---|---|

| ILeak > 300 | 0.3 | 0.2 |

| ∆ILeak > 30 | 0.3 | - |

| ∆ILeak > 60 | 0.15 | - |

| ∆ILeak > 150 | 0.04 | 0.2 |

| Category | Topologies | Main Features | Section | |

|---|---|---|---|---|

| VSI | H6 (Full-Bridge) | H6 | Standard 6-switch inverter; high CMV | 3.1.1 |

| VSI | NPC-H6 (Split Capacitor) | NPC-H6 | Low CMV variation; split DC-link | 3.1.2 |

| VSI | H7 Topologies | H7, oH7, 7-switch | Extra DC-bus switch for decoupling | 3.1.3 |

| VSI | H8 Topologies | H8, oH8, 8-switch, new topology | Two DC-bypass switches; improved CMV | 3.1.4 |

| VSI | H10 Topologies | H10 (FC/RC/Non-clamped) | Clamping circuits for tight CMV control | 3.1.5 |

| VSI | Four-Leg | Four-Leg | Handles unbalanced loads; neutral control | 3.1.6 |

| VSI | ZVR Topology | ZVR | Introduce zero-voltage states to minimize CMV and leakage current and improve EMI performance | 3.1.7 |

| VSI | DCM-232 Topology | DCM-232 | offering improved CMV and EMI mitigation through innovative circuit structures. | 3.1.8 |

| VSI | Hybrid Topologies | Hybrid and NPC-Hybrid | Combines AC/DC decoupling paths | 3.1.9 |

| CSI | Conventional CSI | CSI | inherent CMV advantages | 3.2.1 |

| CSI | CH7 Topologies | CH7 and Soft-switched CH7 | H7-derived current-source version | 3.2.2 |

| CSI | Split capacitor CSI | Four-Wire CSI | Split capacitors raise CM path impedance for leakage suppression | 3.2.3 |

| CSI | Four-leg CSI | Avoids zero vectors to suppress CMV | 3.2.4 | |

| Topology | Number of Devices | PWM | CMV (Pu) | Decoupling Side | Efficiency | Ileak | Merits and Demerits | ||

|---|---|---|---|---|---|---|---|---|---|

| Q | D | From | To | ||||||

| H6 | 6 | 0 | SVPWM | 0 | 1 | - | ~97–98% | >300 mA | Simple and good THD, however, has high CMV variation and high Ileak that does not meet the standards. |

| NPC-H6 | 6 | 0 | SVPWM | 0 | 0.01 | - | - | <30 mA | It has relatively low CMV variation and acceptable Ileak that meet the standards. |

| H7 | 7 | 0 | SVPWM | 0 | 2/3 | DC | ~97.5–98.5% | ~50–100 mA | Lower number of devices with moderate CMV, Ileak value, and efficiency. |

| oH7 | 8 | 0 | SVPWM | 0 | 2/3 | DC | ~97% | ~70–120 mA | The performance is low compared to the increased number of devices. |

| Seven switch | 7 | 6 | SVPWM | 1/3 | 2/3 | AC | ~98% | <40 mA | Better CMV variation and lower Ileak and efficiency. |

| Topology | Number of Devices | PWM | CMV Variations | Decoupling | Performance Metrics (Typ.) | Merits and Demerits | ||

|---|---|---|---|---|---|---|---|---|

| Q | D | From | To | |||||

| H8 | 8 | 0 | SVPWM | 0 | 2/3 | DC | Efficiency: 98.5–99% Ileak: <30 mA THD: <3% | Increased gate drivers and possible higher losses; however, the Ileak is low. |

| oH8 | 8 | 2 | SVPWM | 1/3 | 2/3 | DC | Efficiency: ~97.5% I_leak: ~50 mA | Improved CMV, but higher losses and low efficiency; no significant decrease in Ileak. |

| Eight switch | 8 | 0 | SVPWM | 1/3 | 2/3 | hybrid | Efficiency: >98% Ileak: <30 mA | More complex, increased gate drivers, and possible higher losses; however, the Ileak is low. |

| [88] | 8 | 0 | Special PWM | 1/3 | 2/3 | DC | Efficiency: >98.5% Ileak: <25 mA THD: <2.5% | Lower total voltage rating, fewer driver requirements, and best efficiency with improved CMV. |

| Topology | Number of Devices | PWM | CMV (pu) | Decoupling Side | Performance Metrics (Typ.) | Merits and Demerits | ||

|---|---|---|---|---|---|---|---|---|

| Transistors | Capacitors | Range | dv/dt | |||||

| H10 | 10 | 0 | SVPWM | 1/3:2/3 | 1/3 | DC | Efficiency: ~98% Ileak: <35 mA | Simple and good THD, however, it has high CMV variation and high Ileak, which does not meet the standards. |

| FC-H10 | 10 | 3 | Special PWM | 1/3:2/3 | 1/3 | DC | Efficiency: ~98% Ileak: <20 mA | Has relatively low CMV variation and acceptable Ileak that meet the standards. |

| RC-H10 | 10 | 3 | Special PWM | 1/3:2/3 | 1/3 | DC | Efficiency: ~98.2% Ileak: <15 mA | Low number of devices with moderate CMV, Ileak value, and efficiency. |

| [91] | 10 | 2 | Special PWM | 1/3:2/3 | 1/6 | DC | Efficiency: 98.5% Ileak: <10 mA THD: <2% | Better CMV variation and lower Ileak and efficiency. |

| Collective | States | CMV (VCMV/Vdc) |

|---|---|---|

| 1 | 222 | 1 |

| 2 | 221, 212, 122 | 5/6 |

| 3 | 220, 202, 022, 211, 121, 112 | 2/3 |

| 4 | 210, 201, 120, 102, 012, 021, 111 | 1/2 |

| 5 | 110, 101, 011, 200, 020, 002 | 1/3 |

| 6 | 100, 010, 001 | 1/6 |

| 7 | 000 | 0 |

| Collective | States | CMV (VCMV/Vdc) |

|---|---|---|

| 1 | 222, 210, 201, 120, 102, 012, 021, 111, 000 | 1 |

| 2 | 221, 212, 122, 220, 202, 022, 211, 121, 112 | 2/3 |

| 3 | 110, 101, 011, 200, 020, 002, 100, 010, 001 | 1/3 |

| Topology | Number of Devices | PWM | CMV Variations | Performance Metrics (Typ.) | Decoupling | Merits and Demerits | ||

|---|---|---|---|---|---|---|---|---|

| Q | D | Range | dv/dt | |||||

| Four-Leg | 8 | 0 | RSPWM | Const. @ 1/2 | 1/3 | Ileak: <10 mA THD (Unbalanced): <4% | AC | Improves handling of unbalanced loads and control of the neutral point while reducing CMV and leakage current. However, this requires more switches and gate drivers, which raises costs, control complexity, and losses. Consequently, despite their benefits in Ileak suppression and grid adaptability, higher hardware and control demands hinder widespread adoption compared to simpler TL designs. |

| ZVR | 9 | 12 | SPWM | Const. | 0 | Efficiency: ~97% Ileak: ~5 mA | AC | Eliminates the CMV during zero states, which greatly suppresses Ileak and improves electromagnetic compatibility. They also maintain good efficiency and reliability by avoiding extra high-frequency switches compared to some other Ileak reduction methods. However, it adds circuit complexity and more sophisticated modulation/control strategies, which slightly raise system cost. |

| DCM-232 | 10 | 0 | SVPWM | Const.@ 0 | 0 | Ileak: <7 mA | DC | Effectively suppresses CMV and Ileak by using a decoupled common-mode approach, which improves safety and reduces electromagnetic compatibility (EMI) issues in PV grid-connected systems. Their main drawbacks are higher circuit complexity and additional switching devices, which increase cost and control effort compared with simpler TL inverter topologies. |

| Non-NPC hybrid | 9 | 0 | MDPWM | 1/3:2/3 | 1/6 | Efficiency: 98–98.7% Ileak: <25 mA | AC | Reduces CMV dv/dt by ~50%, lowering leakage and EMI further. However, it is a more complex modulation and design and still requires more switches than the simplest structures. |

| NPC hybrid | 9 | 0 | MDPWM | Const. | 1/6 | Efficiency: 97.5–98.2% Ileak: <15 mA | hybrid | Better than a non-NPC hybrid. However, it is a more complex modulation and design and still requires more switches than the simplest structures. |

| Factor | Typical % Difference (TL-VSI × TL-CSI) | Comments |

|---|---|---|

| Conversion efficiency (AC out/PV DC in) | TL-VSI is better by ~+1% to +4% | Modern transformerless TL-VSI topologies tend to reach slightly higher peak efficiencies because CSIs incur additional inductor conduction/switching losses and more complex commutation [104] |

| Cost (inverter + typical BOS impact) | TL-VSI is cheaper by ~10% to 40% | VSIs are mass-produced and simpler (no large DC inductor, simpler MPPT interfacing). TL-CSI’s bulky inductors raise hardware cost; some CSI implementations can reduce protection/BOS costs (but rarely enough to beat VSI at small/medium scale) [104] |

| Size & weight | TL-VSI is smaller/lighter by ~20% to 60% | CSI requires a relatively large DC-link inductor, which increases volume/mass; with wide-bandgap switches, this can shrink, but VSI typically remains more compact [105] |

| Leakage/common-mode (CM) current to ground | TL-CSI is better (lower leakage) by ~40% to 90% (i.e., TL-CSI reduces leakage compared to conventional boost/VSI baselines) | Several transformerless TL-CSI and modified boost/extended topologies explicitly target CM-current suppression—reported reductions vary widely (40–90% depending on design). This is a principal TL-CSI advantage in transformerless PV [106] |

| Power quality (THD, harmonic injection) | TL-VSI is slightly better by ~0% to +20% (topology dependent) | Multilevel TL-VSIs (NPC/T-type/ANPC, CHB) obtain very low THD; TL-CSIs can also achieve good waveforms but require different modulation and larger filter designs. The advantage size depends on the level count and control [107] |

| Control complexity & MPPT interfacing | TL-VSI is simpler (better) by ~+20% to +60% (qualitative) | PV arrays are naturally voltage-source-like; MPPT and DC-side control are straightforward with TL-VSIs. CSI requires converting PV voltage source behavior to behave like a controlled current source (extra interfacing/boost stages or hybrids), increasing control/auxiliary hardware complexity [101]. |

| EMI/dv/dt and filtering needs | TL-CSI may be better for CM but needs larger filters: overall difference ~±10–30% | TL-CSI’s lower common-mode can reduce EMI related to leakage, but bulky inductors and switching can create other EMI challenges; VSIs use dv/dt mitigation and filters—the net advantage is topology dependent [108] |

| Reliability and fault behavior | CSI may be better by ~+5% to +20% for short-circuit/robustness | TL-CSI has inherent current-limiting behavior and a robust DC-link inductor (less dependency on electrolytic DC capacitors), providing some robustness and fault-tolerance advantages in certain installations [109,110,111] |

| Market adoption/maturity | TL-VSI is vastly ahead (TL-VSI “better” by >90% in market share) | Practically all residential/commercial transformerless PV inverters are TL-VSI-based; TL-CSIs are niche/research/commercial trials in PV [102] |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zaid, S.A.; Samkari, H.S.; Allehyani, M.F. Three-Phase Transformerless Buck-Inverter Topologies for PV Grid-Tied Systems: A Review. Processes 2025, 13, 3667. https://doi.org/10.3390/pr13113667

Zaid SA, Samkari HS, Allehyani MF. Three-Phase Transformerless Buck-Inverter Topologies for PV Grid-Tied Systems: A Review. Processes. 2025; 13(11):3667. https://doi.org/10.3390/pr13113667

Chicago/Turabian StyleZaid, Sherif A., Husam S. Samkari, and Mohammed F. Allehyani. 2025. "Three-Phase Transformerless Buck-Inverter Topologies for PV Grid-Tied Systems: A Review" Processes 13, no. 11: 3667. https://doi.org/10.3390/pr13113667

APA StyleZaid, S. A., Samkari, H. S., & Allehyani, M. F. (2025). Three-Phase Transformerless Buck-Inverter Topologies for PV Grid-Tied Systems: A Review. Processes, 13(11), 3667. https://doi.org/10.3390/pr13113667