Mitigation and Predictive Assessment of SET Immunity of Digital Logic Circuits for Space Missions

Abstract

1. Introduction

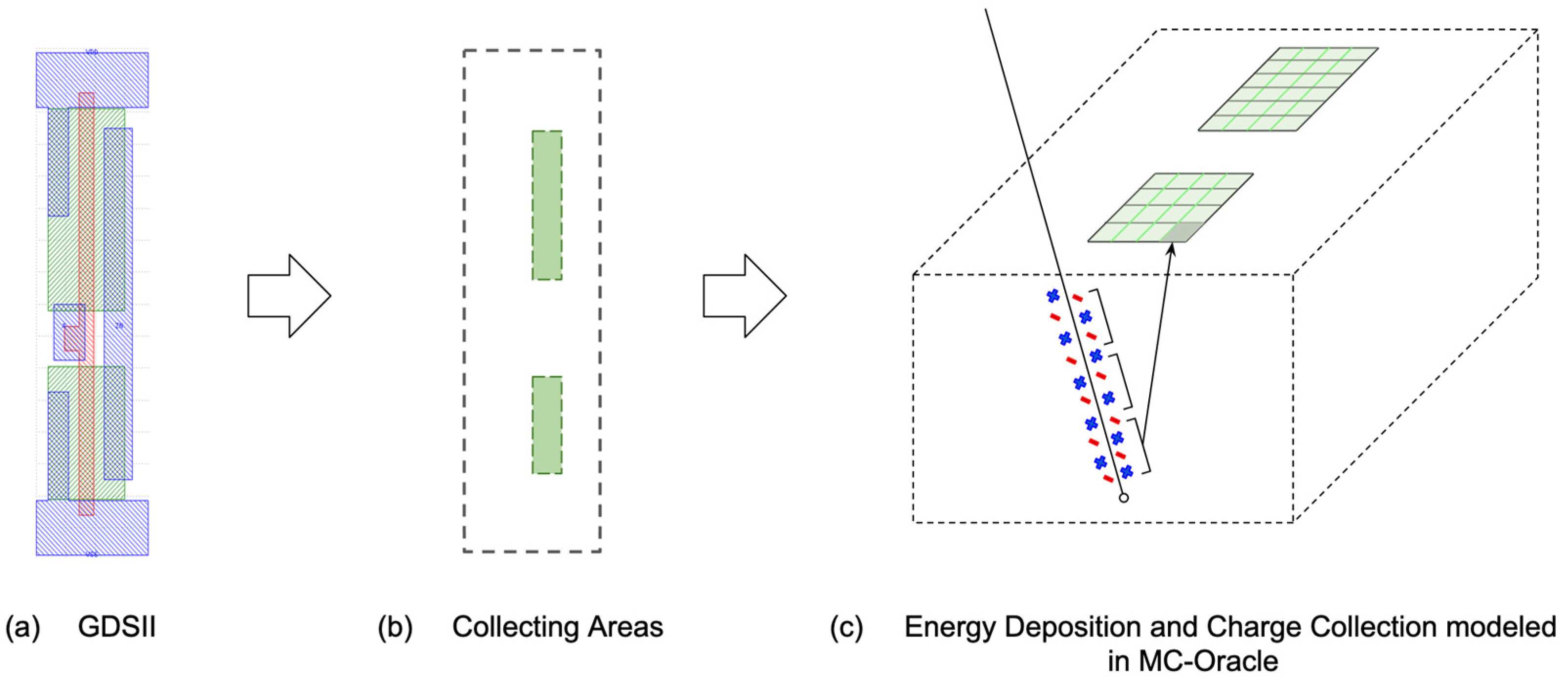

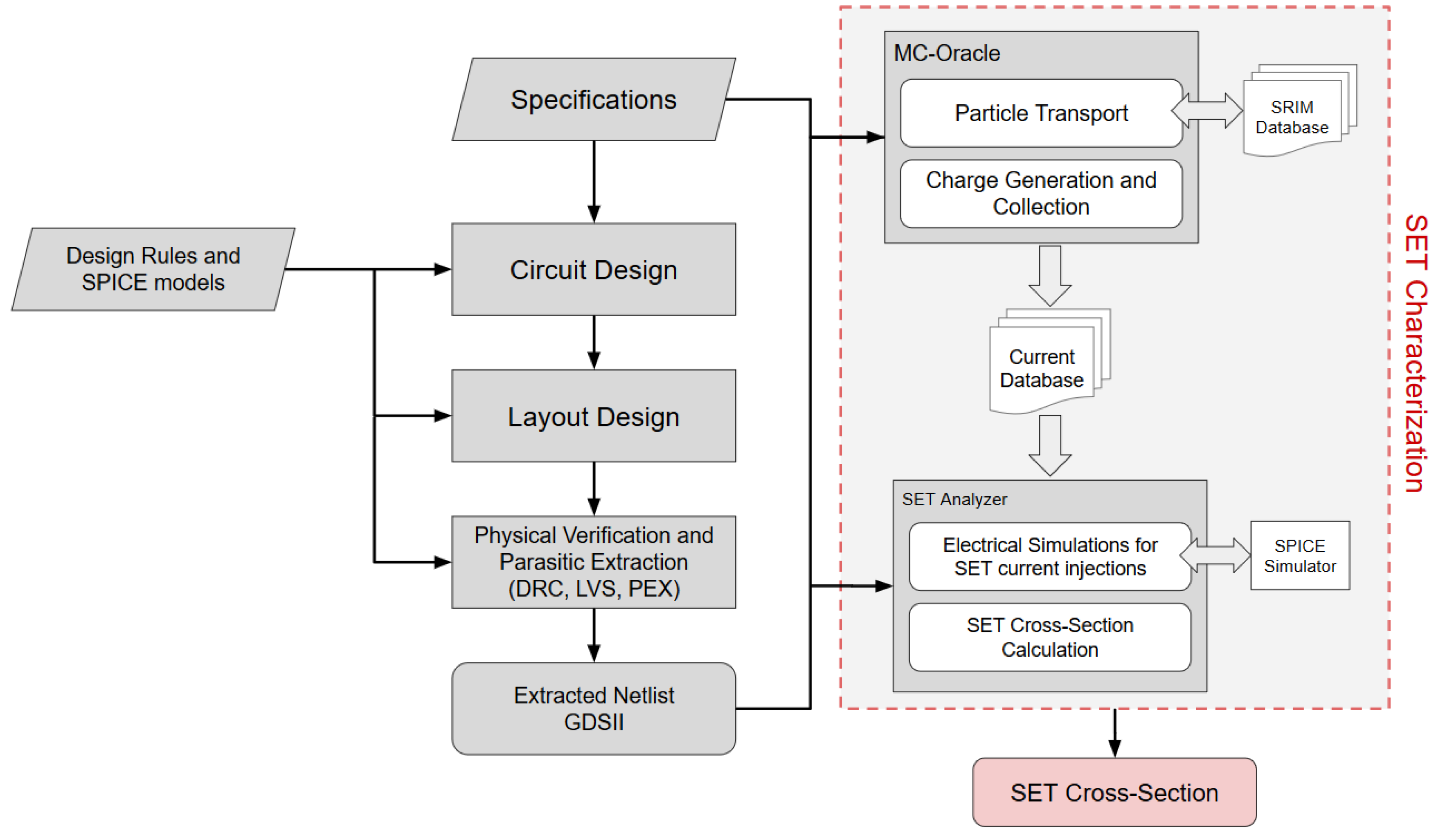

2. Prediction Methodology Based on the Mc-Oracle Tool

3. Results and Discussions

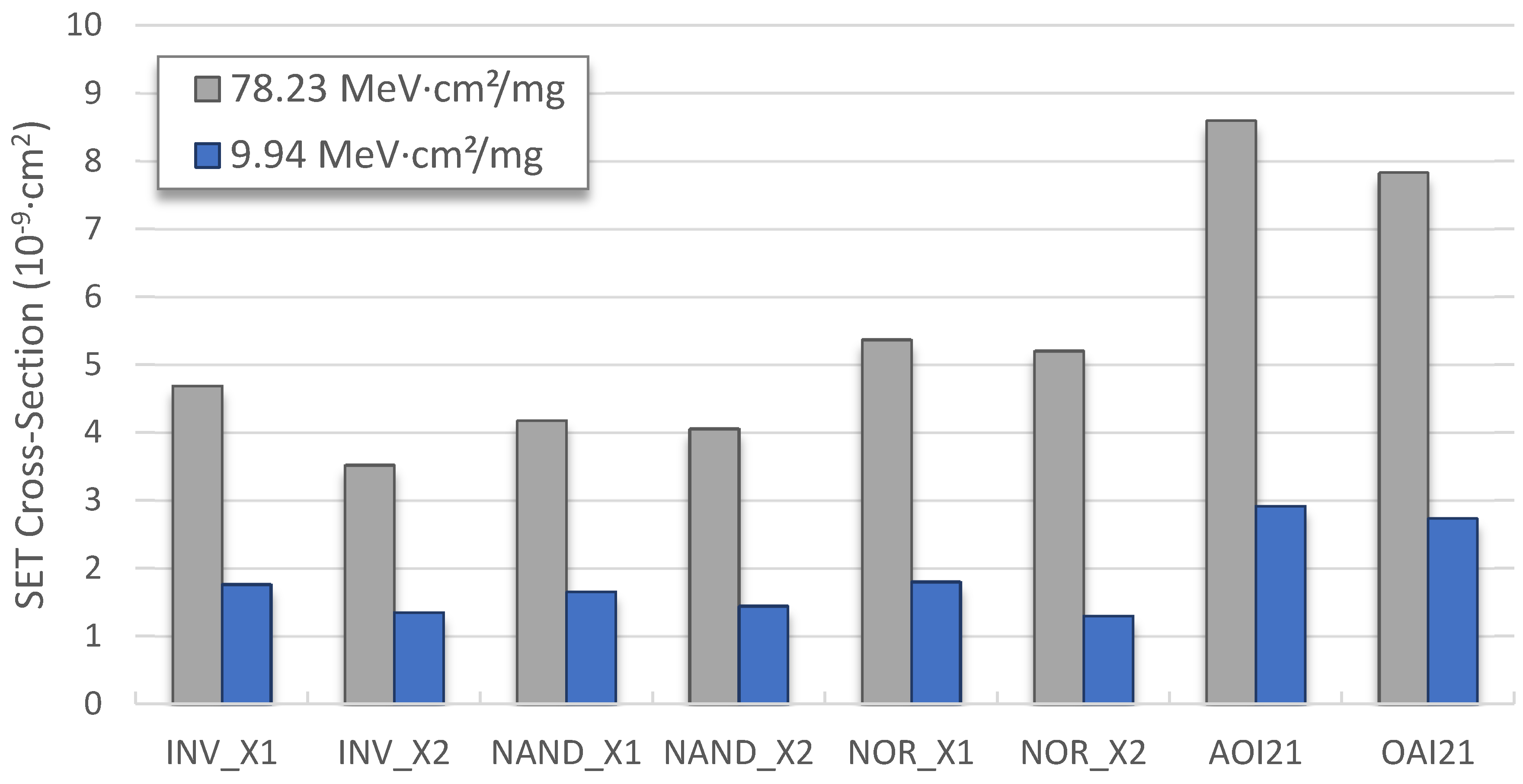

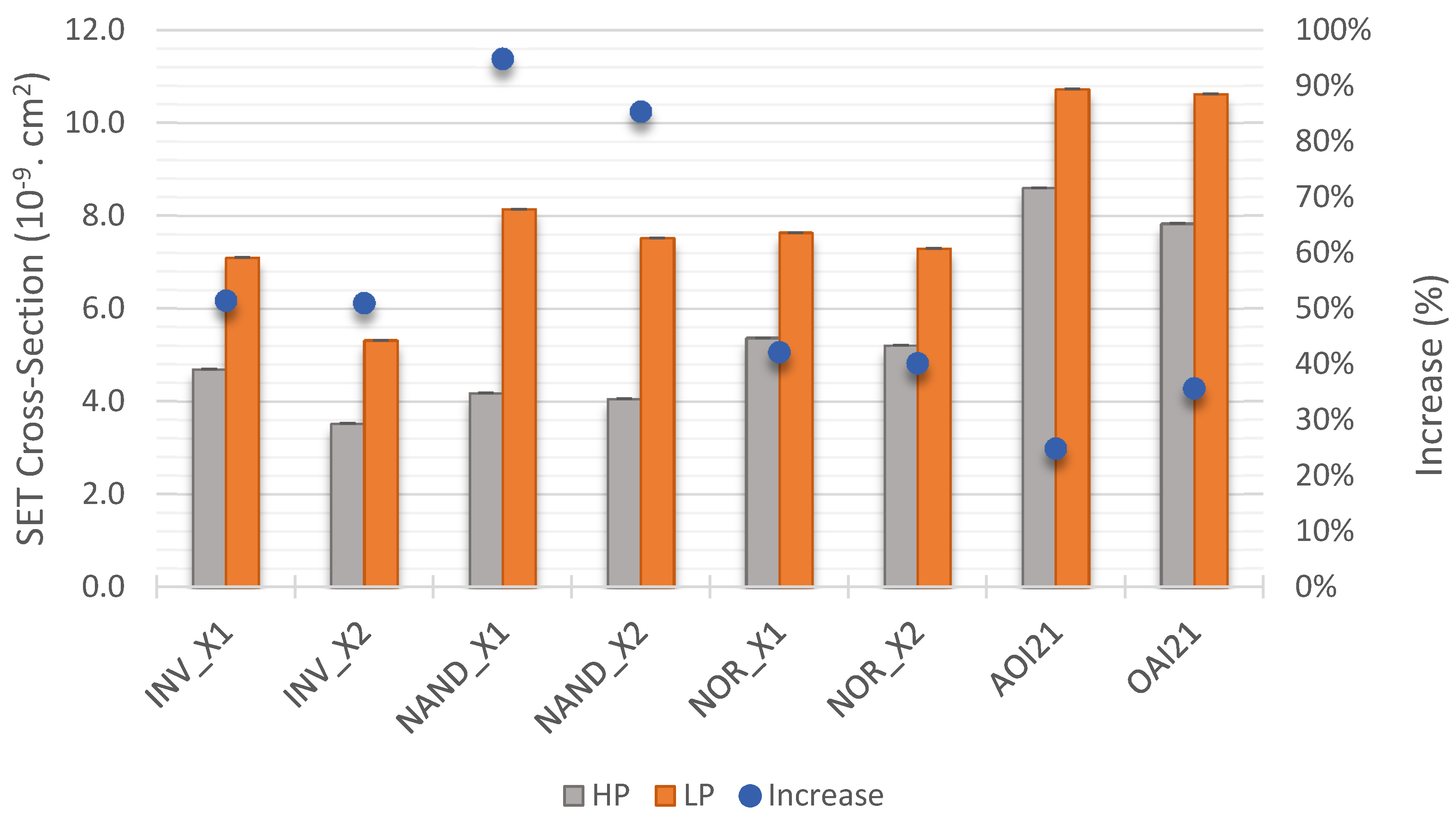

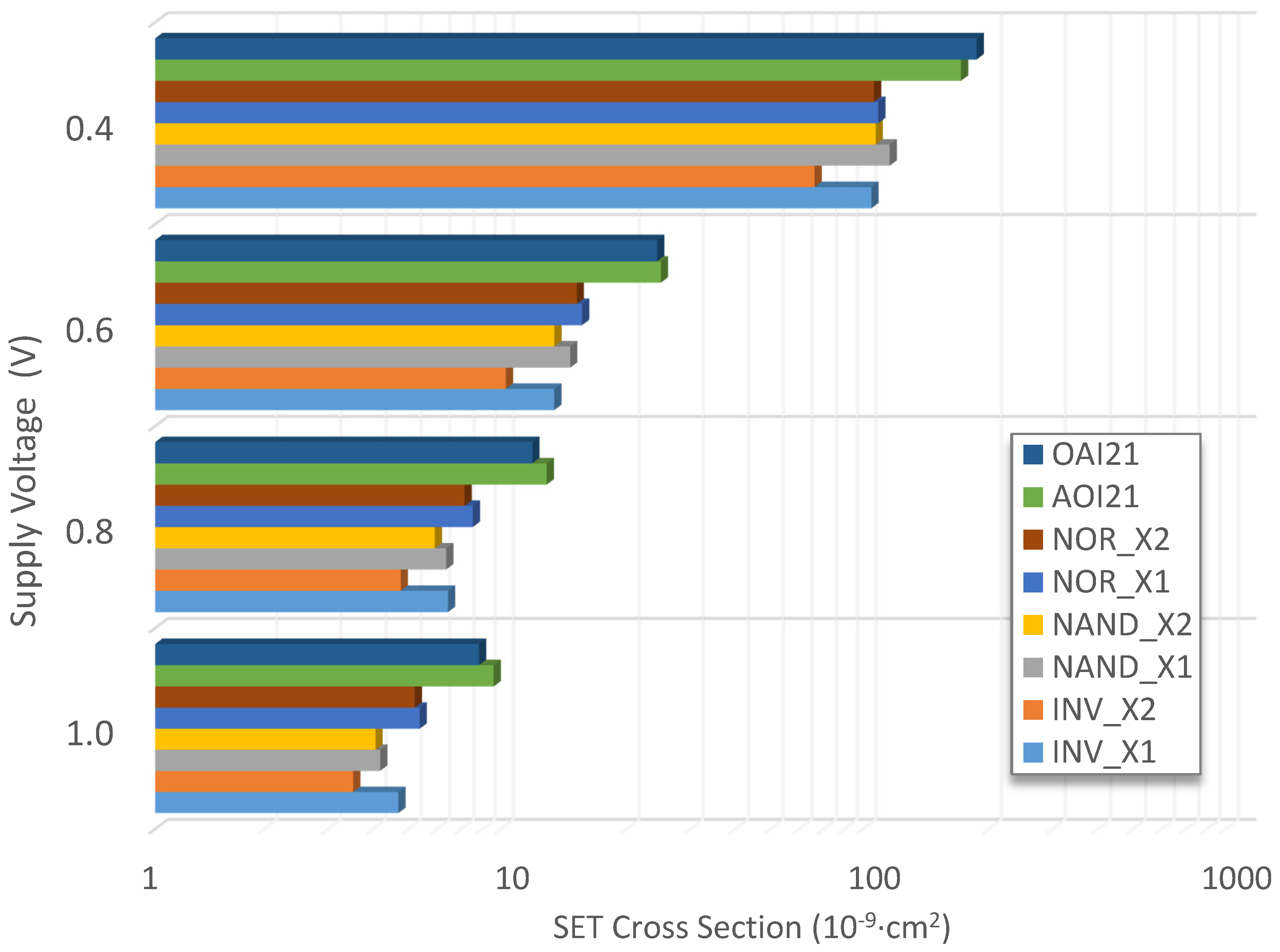

3.1. SET Immunity of Standard-Cell Logic Gates

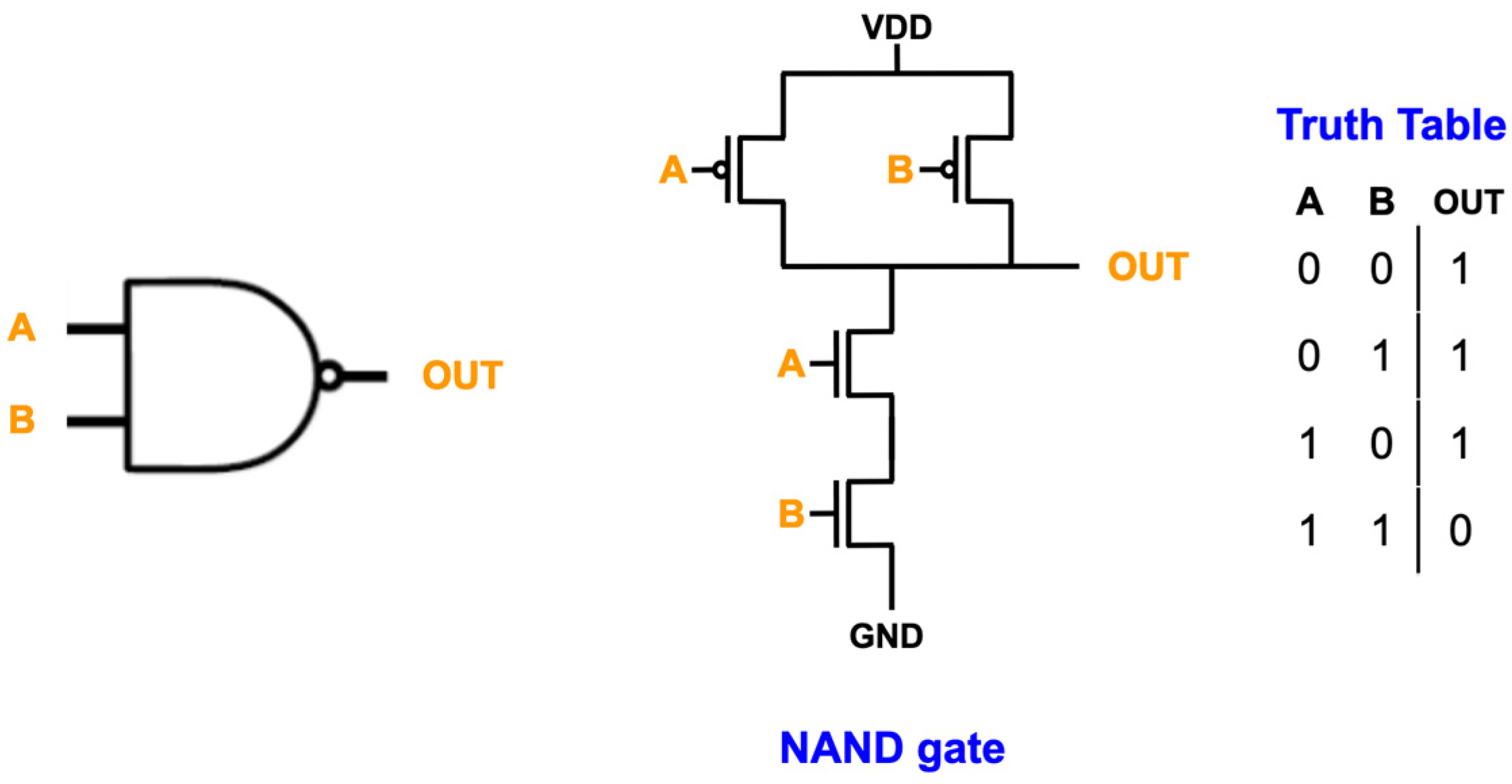

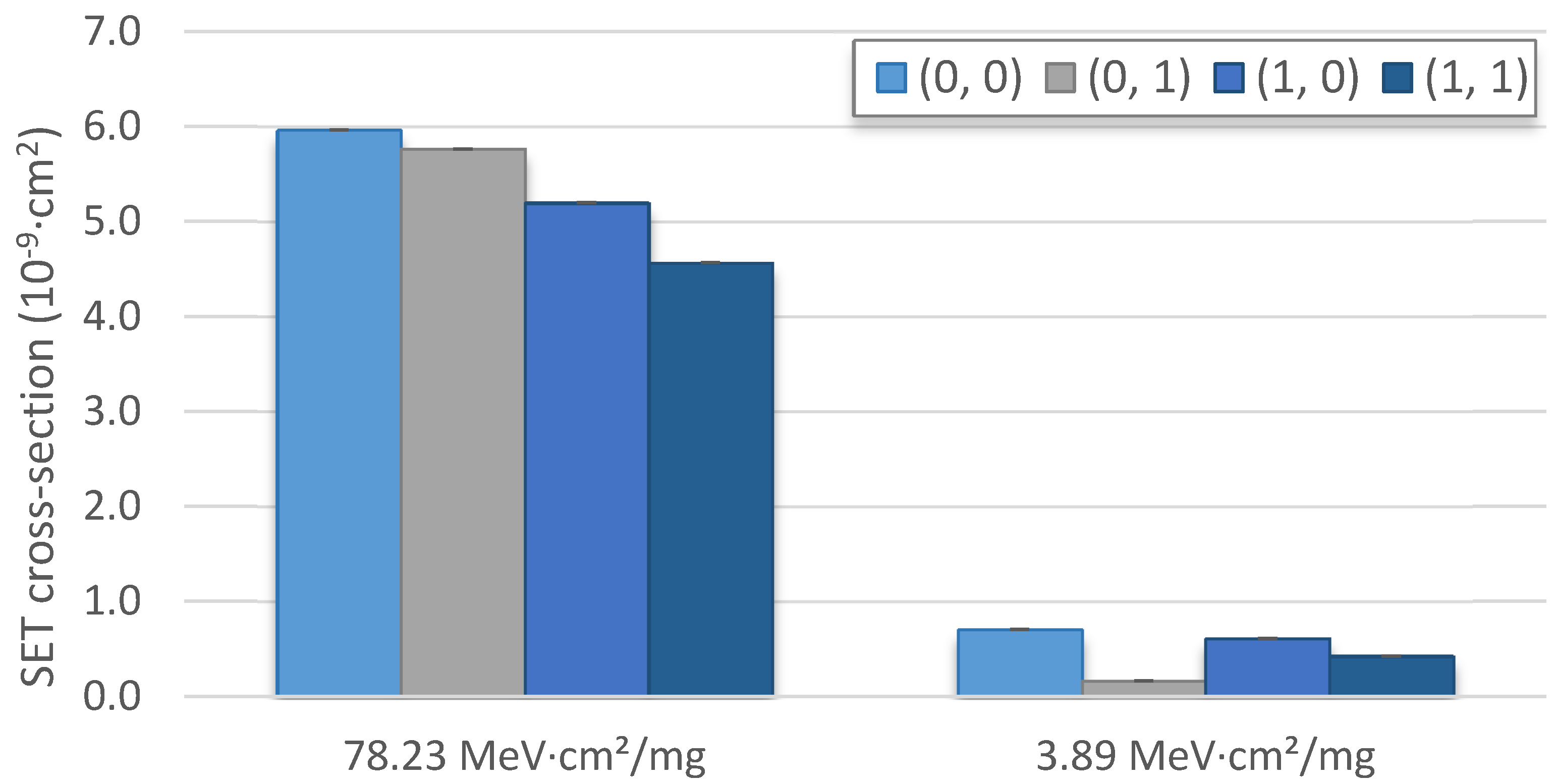

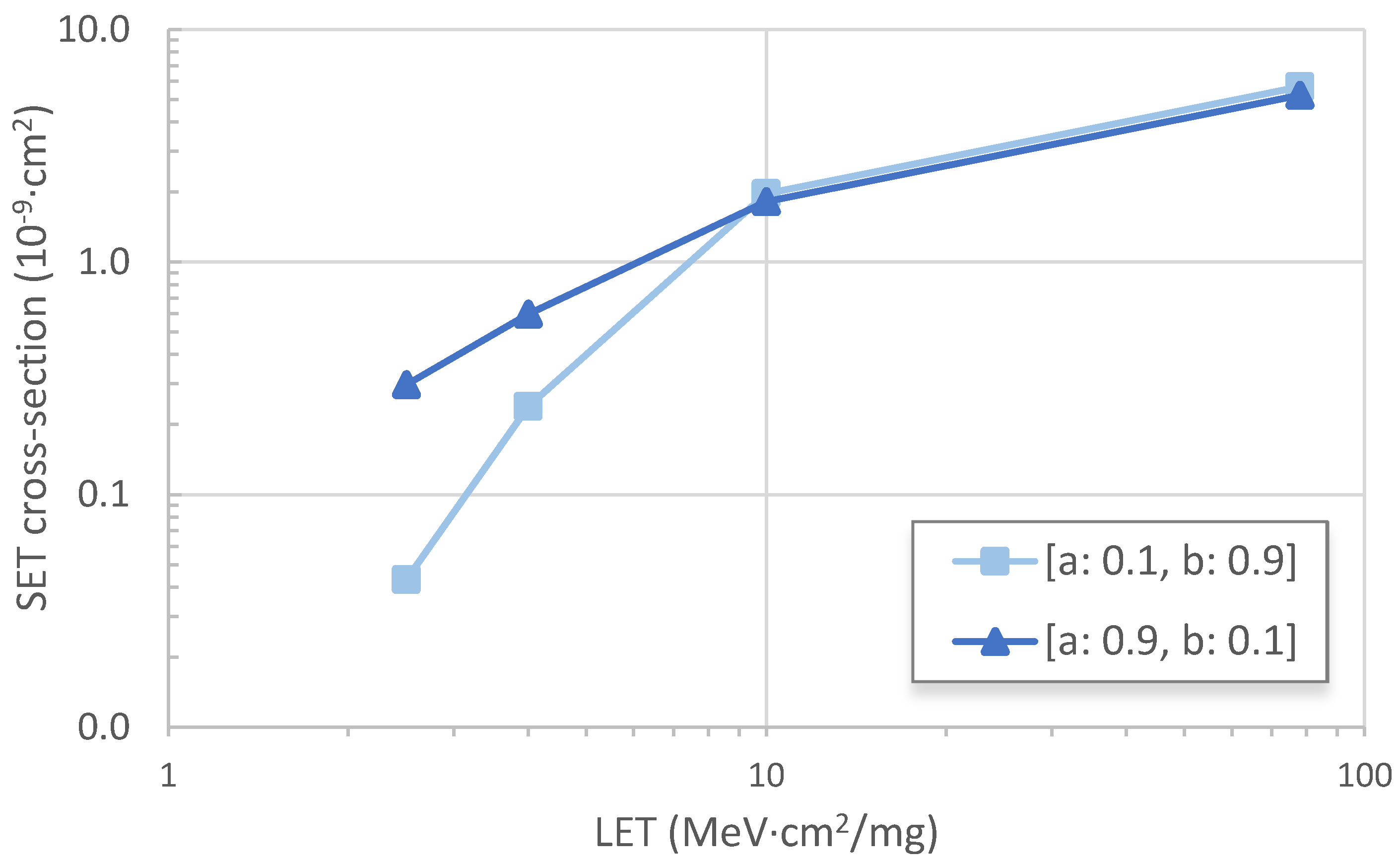

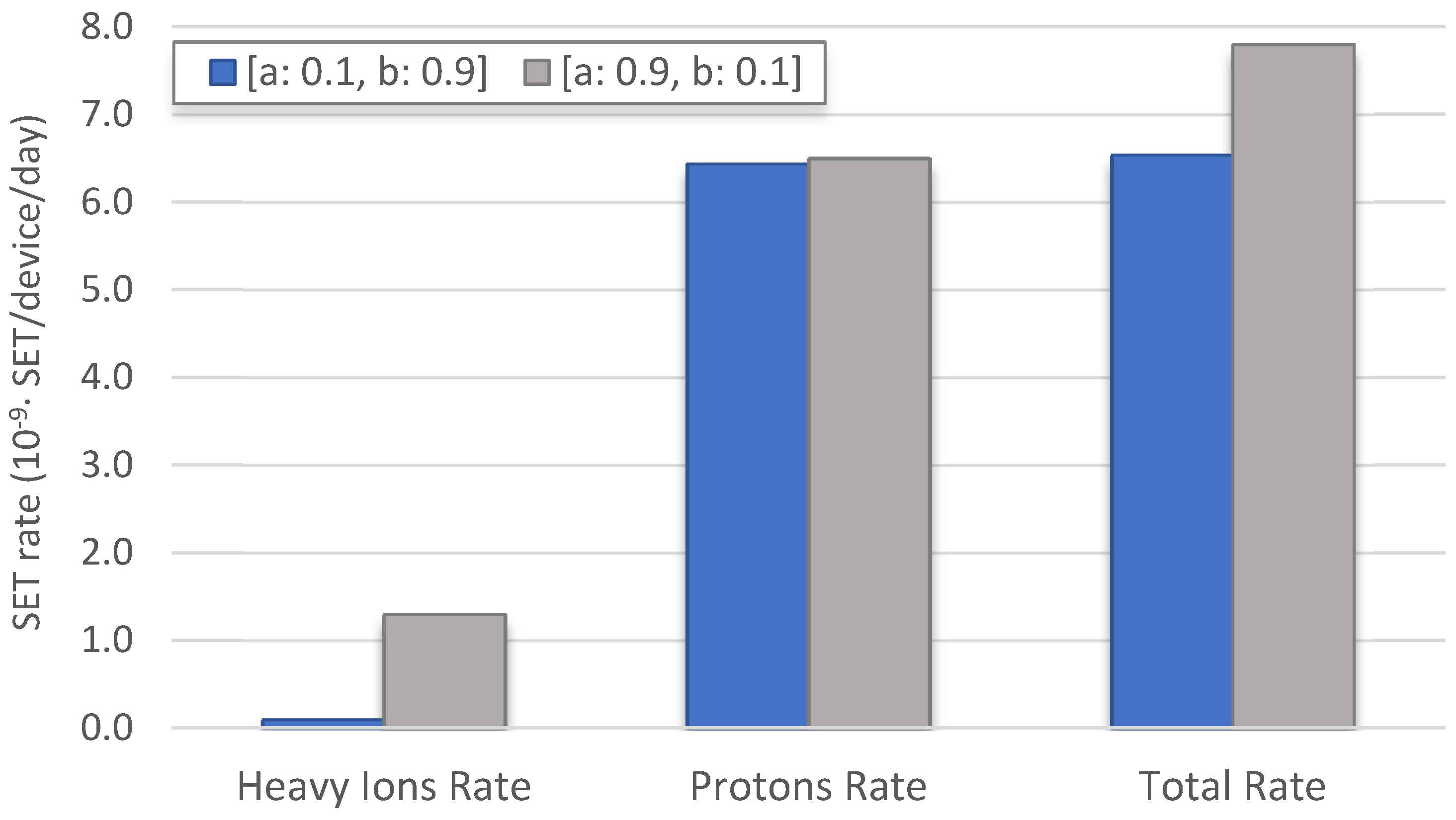

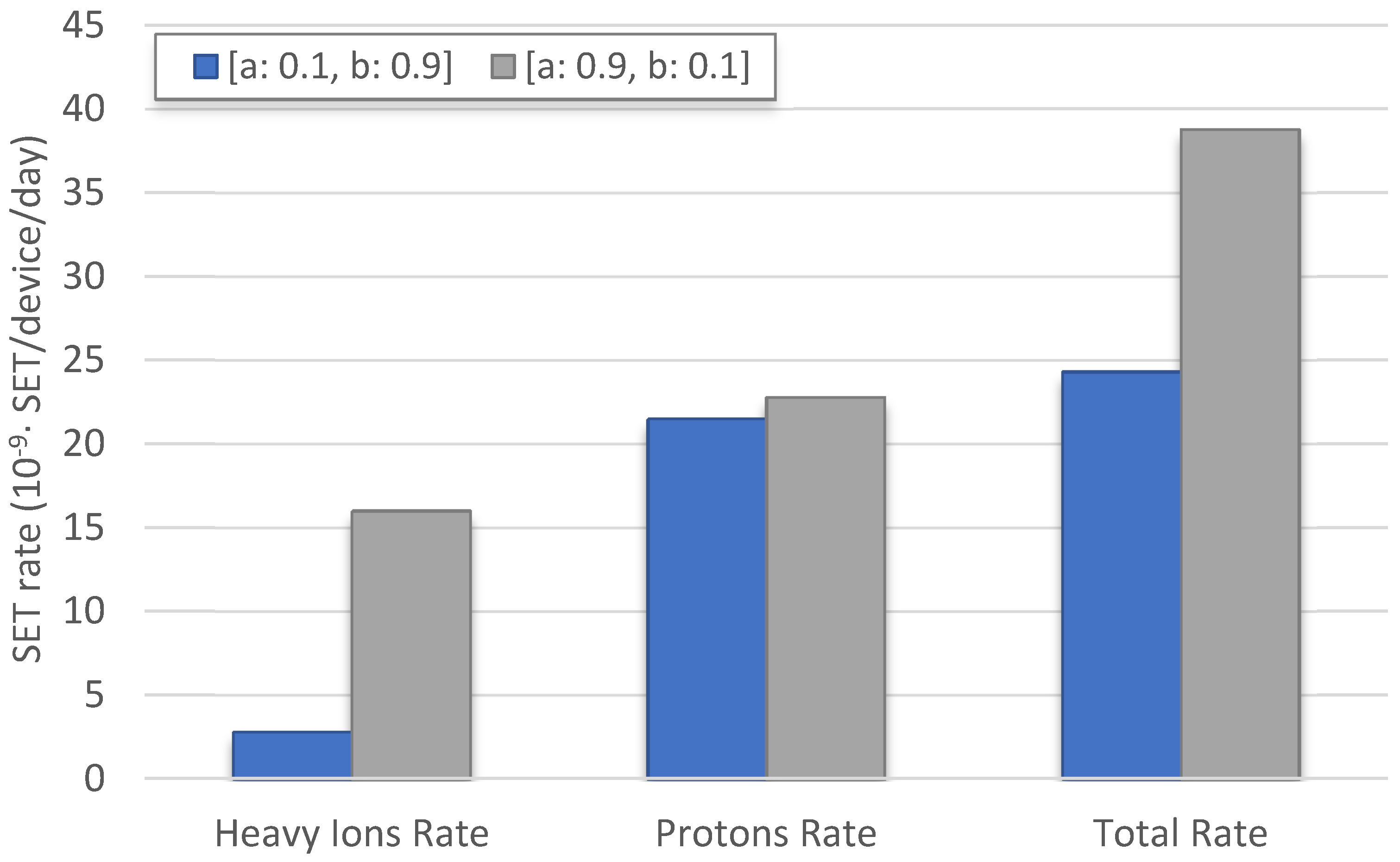

3.2. Impact of Signal Probability and Input Dependence

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Baumann, R.C. The impact of technology scaling on soft error rate performance and limits to the efficacy of error correction. In Proceedings of the International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 8–11 December 2002. [Google Scholar]

- Ferlet-Cavrois, V.; Massengill, L.W.; Gouker, P. Single Event Transients in Digital CMOS—A Review. IEEE Trans. Nucl. Sci. 2013, 60, 1767–1790. [Google Scholar] [CrossRef]

- Buchner, S.; Baze, M. Single-Event Transients in Fast Electronic Circuits. In Proceedings of the IEEE Nuclear Space Radiation Effects Conference (NSREC) Short Course, Section V, Vancouver, BC, Canada, 16 July 2001. [Google Scholar]

- Benedetto, J.M.; Eaton, P.H.; Mavis, D.G.; Gadlage, M.; Turflinger, T. Digital single event transient trends with technology node scaling. IEEE Trans. Nucl. Sci. 2006, 53, 3462–3465. [Google Scholar] [CrossRef]

- Gadlage, M.J.; Ahlbin, J.R.; Narashimham, B.; Bhuva, B.L.; Massengill, L.W.; Reed, R.A.; Schrimpf, R.D.; Vizkelethy, G. Scaling trend in SET pulse widths in sub-100 nm bulk CMOS processes. IEEE Trans. Nucl. Sci. 2010, 57, 3336–3341. [Google Scholar] [CrossRef]

- Mahatme, N.N.; Chatterjee, I.; Bhuva, B.L.; Ahlbin, J.R.; Massengill, L.W.; Shuler, R. Analysis of soft error rates in combinational and sequential logic and implications of hardening for advanced technologies. In Proceedings of the IEEE International Reliability Physics Symposium (IRPS), Anaheim, CA, USA, 17 June 2010. [Google Scholar]

- Sheu, B.J.; Scharfetter, D.L.; Ko, P.-K.; Jeng, M.-C. BSIM: Berkeley short-channel IGFET model for MOS transistors. IEEE J. Solid-State Circuits 1987, 22, 558–566. [Google Scholar] [CrossRef]

- Toh, K.-Y.; Ko, P.-K.; Meyer, R.G. An engineering model for short-channel MOS devices. IEEE J. Solid-State Circuits 1988, 23, 950–958. [Google Scholar] [CrossRef]

- Munteanu, D.; Autran, J.-L. Modeling and Simulation of Single-Event Effects in Digital Devices and ICs. IEEE Trans. Nucl. Sci. 2008, 55, 1854–1878. [Google Scholar] [CrossRef]

- Warren, K.M.; Sternberg, A.L.; Weller, R.A.; Baze, M.P.; Massengill, L.W.; Reed, R.A.; Mendenhall, M.H.; Schrimpf, R.D. Integrating circuit level simulation and Monte-Carlo radiation transport code for single event upset analysis in SEU hardened circuitry. IEEE Trans. Nucl. Sci. 2008, 55, 2886–2894. [Google Scholar] [CrossRef]

- Hubert, G.; Duzellier, S.; Inguimbert, C.; Boatella-Polo, C.; Bezerra, F.; Ecoffet, R. Operational SER Calculations on the SAC-C orbit using the multi scales single event phenomena predictive platform (MUSCA SEP3). IEEE Trans. Nucl. Sci. 2009, 56, 3032–3042. [Google Scholar] [CrossRef]

- Wrobel, F.; Saigné, F. MC-Oracle: A tool for predicting Soft Error Rate. Comp. Phys. Commun. 2011, 182, 317–321. [Google Scholar] [CrossRef]

- Artola, L.; Gaillardin, M.; Hubert, G.; Raine, M.; Paillet, P. Modeling Single Event Transients in Advanced Devices and ICs. IEEE Trans. Nucl. Sci. 2015, 62, 1528–1539. [Google Scholar] [CrossRef]

- Aguiar, Y.Q.; Artola, L.; Hubert, G.; Meinhardt, C.; Kastensmidt, F.L.; Reis, R. Evaluation of Radiation-Induced Soft Error in Majority Voters designed in 7nm FinFET Technology. Microelectron. Reliab. 2017, 76–77, 660–664. [Google Scholar] [CrossRef]

- Koontz, S.; Reddell, B.; Boeder, P. Calculating Spacecraft Single Event Environments with FLUKA: Investigating the Effects of Spacecraft Material Atomic Number on Secondary Particle Showers, Nuclear Reactions, and Linear Energy Transfer (LET) Spectra, Internal to Spacecraft Avionics Materials, at High Shielding Mass. In Proceedings of the IEEE Radiation Effects Data Workshop, Las Vegas, NV, USA, 25–29 July 2011. [Google Scholar]

- Reed, R.A.; Weller, R.A.; Akkerman, A.; Barak, J.; Culpepper, W.; Duzellier, S.; Foster, C.; Gaillardin, M.; Hubert, G.; Jordan, T.; et al. Anthology of the Development of Radiation Transport Tools as Applied to Single Event Effects. IEEE Trans. Nucl. Sci. 2013, 60, 1876–1911. [Google Scholar] [CrossRef]

- Calienes, W.B.; Aguiar, Y.Q.; Meinhardt, C.; Vladmirescu, A.; Reis, R. Evaluation of Heavy-Ion Impact on Bulk and FDSOI devices under ZTC condition. Microelectron. Reliab. 2017, 76–77, 655–659. [Google Scholar] [CrossRef]

- Aguiar, Y.Q.; Wrobel, F.; Autran, J.-L.; Leroux, P.; Saigné, F.; Touboul, A.D.; Pouget, V. Analysis of Charge Sharing Effect in SET sensitivity of bulk 45nm standard cell layouts under heavy ions. Microelectron. Reliab. 2018, 88–90, 920–924. [Google Scholar] [CrossRef]

- Taber, A.; Normand, E. Single Event Upset in Avionics. IEEE Trans. Nucl. Sci. 1993, 40, 120–126. [Google Scholar] [CrossRef]

- Gossett, C.A.; Hughlock, B.W.; Katoozi, M.; LaRue, G.S.; Wender, S.A. Single Event Phenomena in atmospheric neutron environment. IEEE Trans. Nucl. Sci. 1993, 40, 1845–1852. [Google Scholar] [CrossRef]

- Ziegler, J.F.; Biersack, J.P. The stopping and range of ions in matter. In Treatise on Heavy-Ion Science; Springer: Boston, MA, USA, 1985; pp. 93–129. [Google Scholar]

- Ziegler, J.F.; Ziegler, M.D.; Biersack, J.P. SRIM—The stopping and range of ions in matter (2010). In Nuclear Instruments and Methods in Physics Research Section B: Beam Interactions with Materials and Atoms; Elsevier: Amsterdam, The Netherlands, 2010; pp. 1818–1823. [Google Scholar] [CrossRef]

- Wrobel, F. Detailed history of recoiling ions induced by nucleons. Comp. Phys. Commun. 2008, 178, 88–104. [Google Scholar] [CrossRef]

- Mérelle, T.; Chabane, H.; Palau, J.-M.; Castellani-Coulié, K.; Wrobel, F.; Saigné, F.; Sagnes, B.; Boch, J.; Vaille, J.R.; Gasiot, G.; et al. Criterion for SEU Occurrence in SRAM Deduced from Circuit and Device Simulations in Case of Neutron-Induced SER. IEEE Trans. Nucl. Sci. 2005, 52, 1148–1155. [Google Scholar] [CrossRef]

- Zuchowski, P.S.; Reynolds, C.B.; Grupp, R.J.; Davis, S.G.; Cremen, B.; Troxel, B. A hybrid ASIC and FPGA architecture. In Proceedings of the IEEE/ACM International Conference on Computer Aided Design, San Jose, CA, USA, 10–14 November 2002. [Google Scholar]

- Kuon, I.; Rose, J. Measuring the gap between FPGAs and ASICs. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2007, 26, 203–215. [Google Scholar] [CrossRef]

- Entrena, L.; Lindoso, A.; Millan, E.S.; Pagliarini, S.; Almeida, F.; Kastensmidt, F. Constrained placement methodology for reducing SER under single-event-induced charge sharing effects. IEEE Trans. Nucl. Sci. 2012, 59, 811–817. [Google Scholar] [CrossRef]

- Limbrick, D.B.; Mahatme, N.N.; Robinson, W.H.; Bhuva, B.L. Reliability-aware synthesis of combinational logic with minimal performance penalty. IEEE Trans. Nucl. Sci. 2013, 60, 2776–2781. [Google Scholar] [CrossRef]

- Du, Y.; Chen, S.; Liu, B. A constrained layout placement approach to enhance pulse quenching effect in large combinational circuits. IEEE Trans. Device Mater. Reliab. 2014, 14, 268–274. [Google Scholar] [CrossRef]

- Vaz, P.I.; Both, T.H.; Vidor, F.F.; Brum, R.M.; Girth, G.I. Design Flow Methodology for Radiation Hardened by Design CMOS Enclosed-Layout-Transistor-Based Standard-Cell Library. J. Electron. Test. 2018, 34, 735–747. [Google Scholar] [CrossRef]

- Hassoun, S.; Sasao, T. Logic Synthesis and Verification; Kluwer Academic Publishers: Norwell, MA, USA, 2002. [Google Scholar]

- Aguiar, Y.Q.; Wrobel, F.; Autran, J.-L.; Leroux, P.; Saigné, F.; Touboul, A.D.; Pouget, V. Impact of Complex-Logic Cell Layout on the Single-Event Transient Sensitivity. IEEE Trans. Nucl. Sci. 2019, 66, 1465–1472. [Google Scholar] [CrossRef]

- Stine, J.E.; Castellanos, I.; Wood, M.; Henson, J.; Love, F.; Davis, W.R.; Franzon, P.D.; Bucher, M.; Basavarajaiah, S.; Oh, J.; et al. FreePDK: An open-source variation-aware design kit. In Proceedings of the IEEE International Conference on Microelectronics Systems Education, San Diego, CA, USA, 3–4 June 2007. [Google Scholar]

- Zhou, Q.; Mohanram, K. Gate sizing to radiation harden combinational logic. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2006, 25, 155–166. [Google Scholar] [CrossRef]

- Aguiar, Y.Q.; Wrobel, F.; Guagliardo, S.; Autran, J.-L.; Leroux, P.; Saigné, F.; Touboul, A.D.; Pouget, V. Radiation Hardening Efficiency of Gate Sizing and Transistor Stacking based on Standard Cells. Microelectron. Reliab. 2019, 100–101, 113457. [Google Scholar] [CrossRef]

- Sootkaneung, W.; Saluja, K.K. Soft Error Reduction through Gate Input Dependent Weighted Sizing in Combinational Circuits. In Proceedings of the International Symposium on Quality Electronics Design, Santa Clara, CA, USA, 14–16 March 2011. [Google Scholar]

- Raji, M.; Sabet, M.A.; Ghavami, B. Soft Error Reliability Improvement of Digital Circuits by Exploiting a Fast Gate Sizing Scheme. IEEE Access 2019, 7, 66485–66495. [Google Scholar] [CrossRef]

- Kao, J.T.; Chandrakasan, A.P. Dual-threshold voltage techniques for low-power digital circuits. IEEE J. Solid-State Circuits 2000, 7, 1009–1018. [Google Scholar] [CrossRef]

- Flach, G.; Reimann, T.; Posser, G.; Johann, M.; Reis, R. Effective Method for Simultaneous Gate Sizing and Vth Assignment Using Lagrangian Relaxation. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2014, 33, 546–557. [Google Scholar] [CrossRef]

- Aguiar, Y.Q.; Kastensmidt, F.L.; Meinhardt, C.; Artola, L.; Hubert, G.; Reis, R. Implications of Work-Function Fluctuation on Radiation Robustness of FinFET XOR circuits. In Proceedings of the European Conference on Radiation and Its Effects on Components and Systems (RADECS), Geneva, Switzerland, 2–6 October 2017. [Google Scholar]

- Zhang, H.; Jiang, H.; Assis, T.R.; Mahatme, N.N.; Narasimham, B.; Massengill, L.W.; Bhuva, B.L.; Wen, S.-J.; Wong, R. Effects of Threshold Voltage Variations on Single-Event Upset Response of Sequential Circuits at Advanced Technology Nodes. IEEE Trans. Nucl. Sci. 2017, 64, 457–463. [Google Scholar] [CrossRef]

- Harrington, R.C.; Maharrey, J.A.; Kauppila, J.S.; Nsengiyumva, P.; Ball, D.R.; Haeffner, T.D.; Zhang, E.X.; Bhuva, B.L.; Massengill, L.W. Effect of Transistor Variants on Single-Event Transients at the 14-/16-nm Bulk FinFET Technology Generation. IEEE Trans. Nucl. Sci. 2018, 65, 1807–1813. [Google Scholar] [CrossRef]

- Burd, T.D.; Pering, T.A.; Stratakos, A.J.; Brodersen, R.W. A dynamic voltage scaled microprocessor system. IEEE J. Solid-State Circuits 2000, 35, 1571–1580. [Google Scholar] [CrossRef]

- Hejimen, T.; Giot, D.; Roche, P. Factors that impact the critical charge of memory elements. In Proceedings of the IEEE International On-Line Testing Symposium (IOLTS), Lake Como, Italy, 10–12 July 2006. [Google Scholar]

- Kastensmidt, F.L.; Tonfat, J.; Both, T.; Rech, P.; Wirth, G.; Reis, R.; Bruguier, F.; Benoit, P.; Torres, L.; Frost, C. Voltage scaling and aging effects on soft error rate in SRAM-based FPGAs. Microelectron. Reliab. 2014, 54, 2344–2348. [Google Scholar] [CrossRef]

- Najm, F.N. Improved estimation of the switching activity for reliability prediction in VLSI circuits. In Proceedings of the IEEE Custom Integrated Conference, San Diego, CA, USA, 6 August 1994. [Google Scholar]

- Franco, D.T.; Vasconcelos, M.C.; Naviner, L.; Naviner, J.-F. Reliability analysis of logic circuits based on signal probability. In Proceedings of the IEEE International Conference on Electronics, Circuits and Systems (ICECS), St. Julien’s, Malta, 31 August–3 September 2008. [Google Scholar]

- Schvittz, R.; Franco, D.T.; Rosa, L.S.; Butzen, P.F. Probabilistic Method for Reliability Estimation of SP-Networks Considering Single Event Transient Faults. In Proceedings of the IEEE International Conference on Electronics, Circuits and Systems (ICECS), Bordeaux, France, 9–12 December 2018. [Google Scholar]

- The OMERE 5.3 Software by TRAD and CNES. Available online: http://www.trad.fr/en/space/omere-software (accessed on 10 October 2019).

- ECSS Secretariat. Space Engineering: Calculation of Radiation and its Effects and Margin Policy Handbook; ECSS-E-HB-10-12A; ESA Requirements and Standards Division: Noordwijk, The Netherlands, 17 December 2010. [Google Scholar]

- ISO/TC 20/SC 14. Space Environment (Natural and Artificial)—Galactic Cosmic Ray Model; ISO 15390; International Organization for Standardization (ISO): Vernier, Geneva, Switzerland, 2004. [Google Scholar]

- Sawyer, D.M.; Vette, J.I. AP-8 Trapped Proton Environment for Solar Maximum and Solar Minimum; NASA TM-X-72605; National Aeronautics and Space Administration: Washington, DC, USA, 1976.

| Input Combination (a, b) | SET Cross-Section (10−9 cm2) | Signal Probability | ||

|---|---|---|---|---|

| [a:0.5, b:0.5] | [a:0.1, b:0.9] | [a:0.9, b:0.1] | ||

| (0, 0) | 2.92 | 0.25 | 0.09 | 0.09 |

| (0, 1) | 3.29 | 0.25 | 0.81 | 0.01 |

| (1, 0) | 3.75 | 0.25 | 0.01 | 0.81 |

| (1, 1) | 6.75 | 0.25 | 0.09 | 0.09 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Aguiar, Y.Q.; Wrobel, F.; Autran, J.-L.; Leroux, P.; Saigné, F.; Pouget, V.; Touboul, A.D. Mitigation and Predictive Assessment of SET Immunity of Digital Logic Circuits for Space Missions. Aerospace 2020, 7, 12. https://doi.org/10.3390/aerospace7020012

Aguiar YQ, Wrobel F, Autran J-L, Leroux P, Saigné F, Pouget V, Touboul AD. Mitigation and Predictive Assessment of SET Immunity of Digital Logic Circuits for Space Missions. Aerospace. 2020; 7(2):12. https://doi.org/10.3390/aerospace7020012

Chicago/Turabian StyleAguiar, Ygor Q., Frédéric Wrobel, Jean-Luc Autran, Paul Leroux, Frédéric Saigné, Vincent Pouget, and Antoine D. Touboul. 2020. "Mitigation and Predictive Assessment of SET Immunity of Digital Logic Circuits for Space Missions" Aerospace 7, no. 2: 12. https://doi.org/10.3390/aerospace7020012

APA StyleAguiar, Y. Q., Wrobel, F., Autran, J.-L., Leroux, P., Saigné, F., Pouget, V., & Touboul, A. D. (2020). Mitigation and Predictive Assessment of SET Immunity of Digital Logic Circuits for Space Missions. Aerospace, 7(2), 12. https://doi.org/10.3390/aerospace7020012