Design and Implementation of a Compact Single-Photon Counting Module

Abstract

1. Introduction

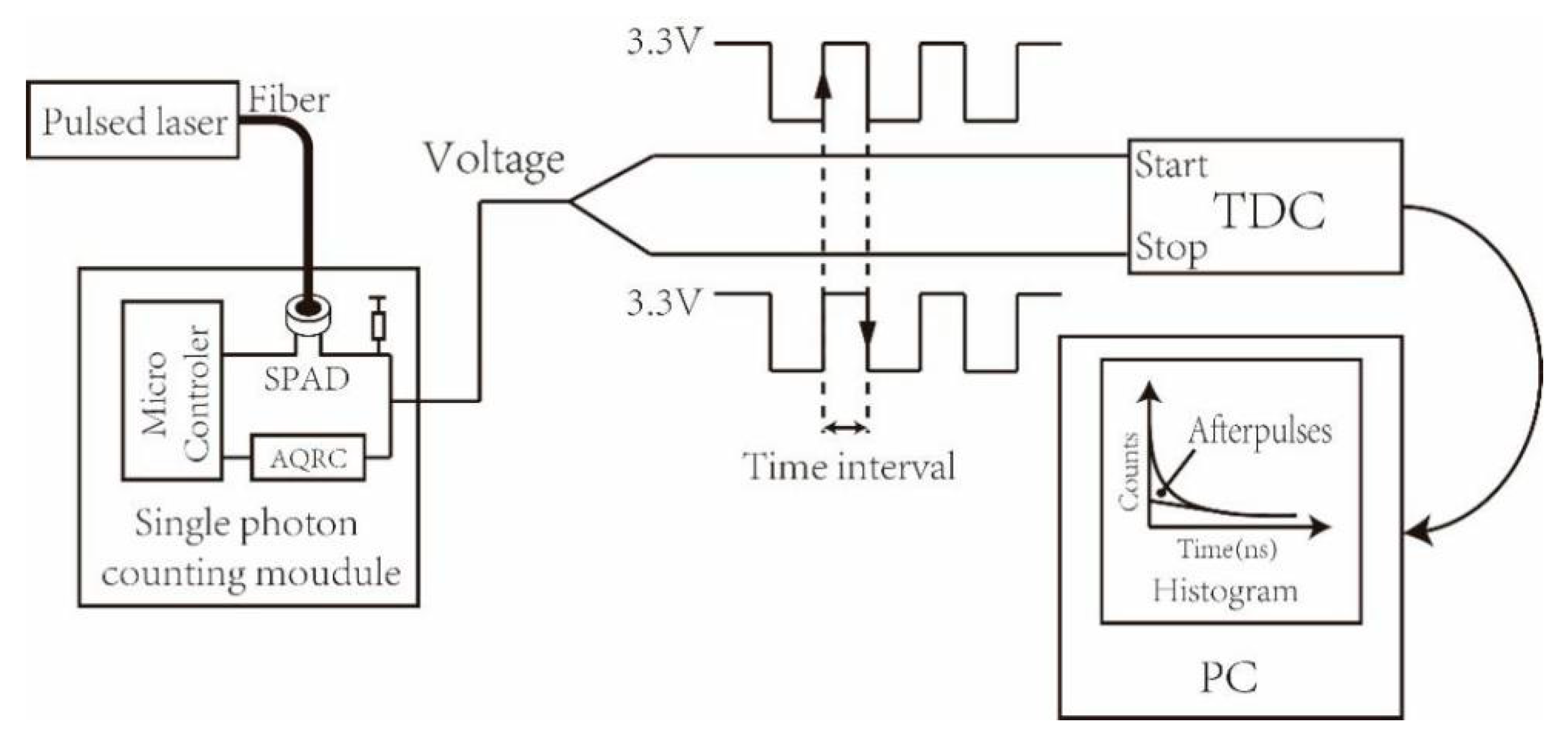

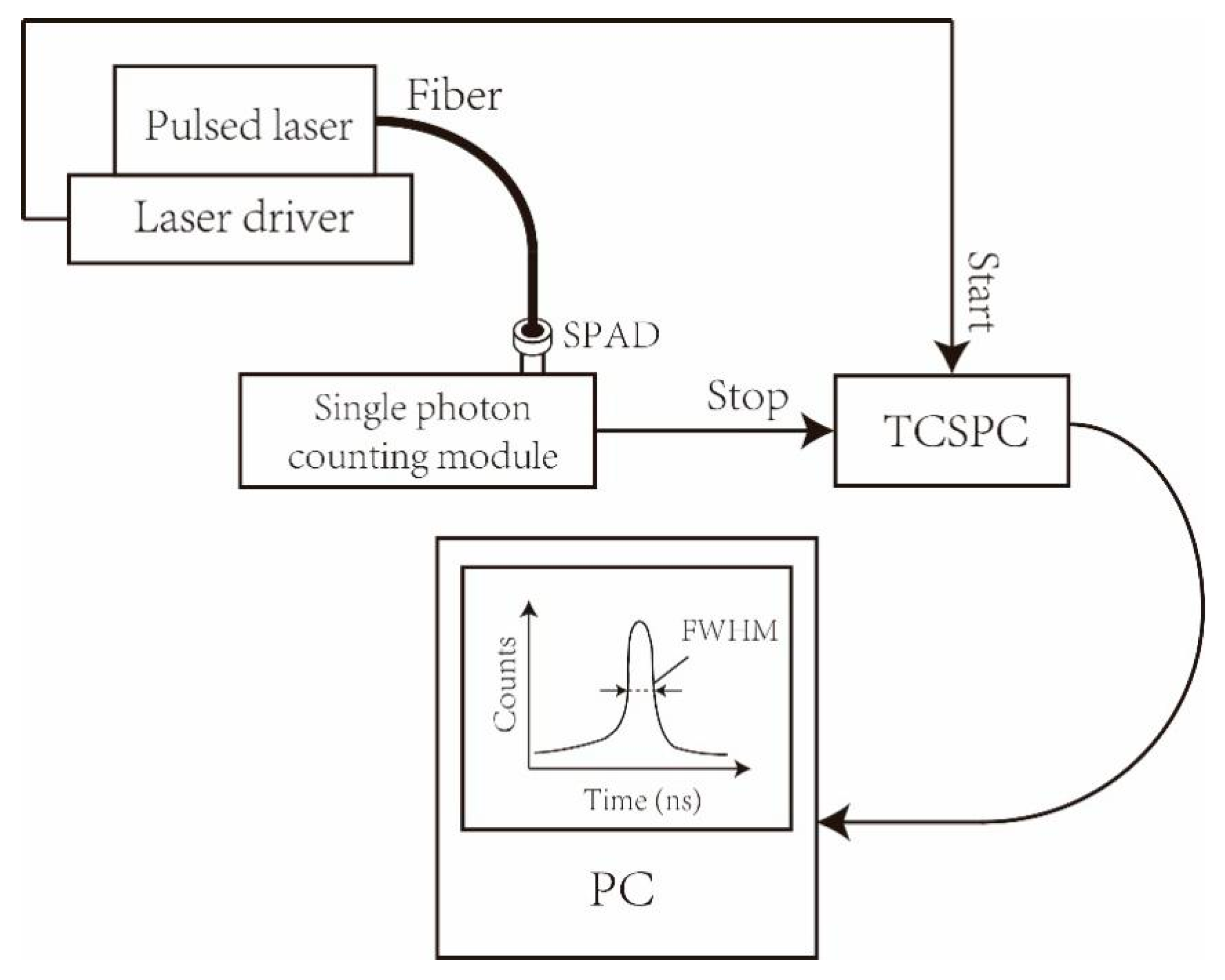

2. System Description

2.1. Microcontroller Circuitry

2.2. Programmable Negative Voltage Generator

2.3. SPAD and AQR-IC

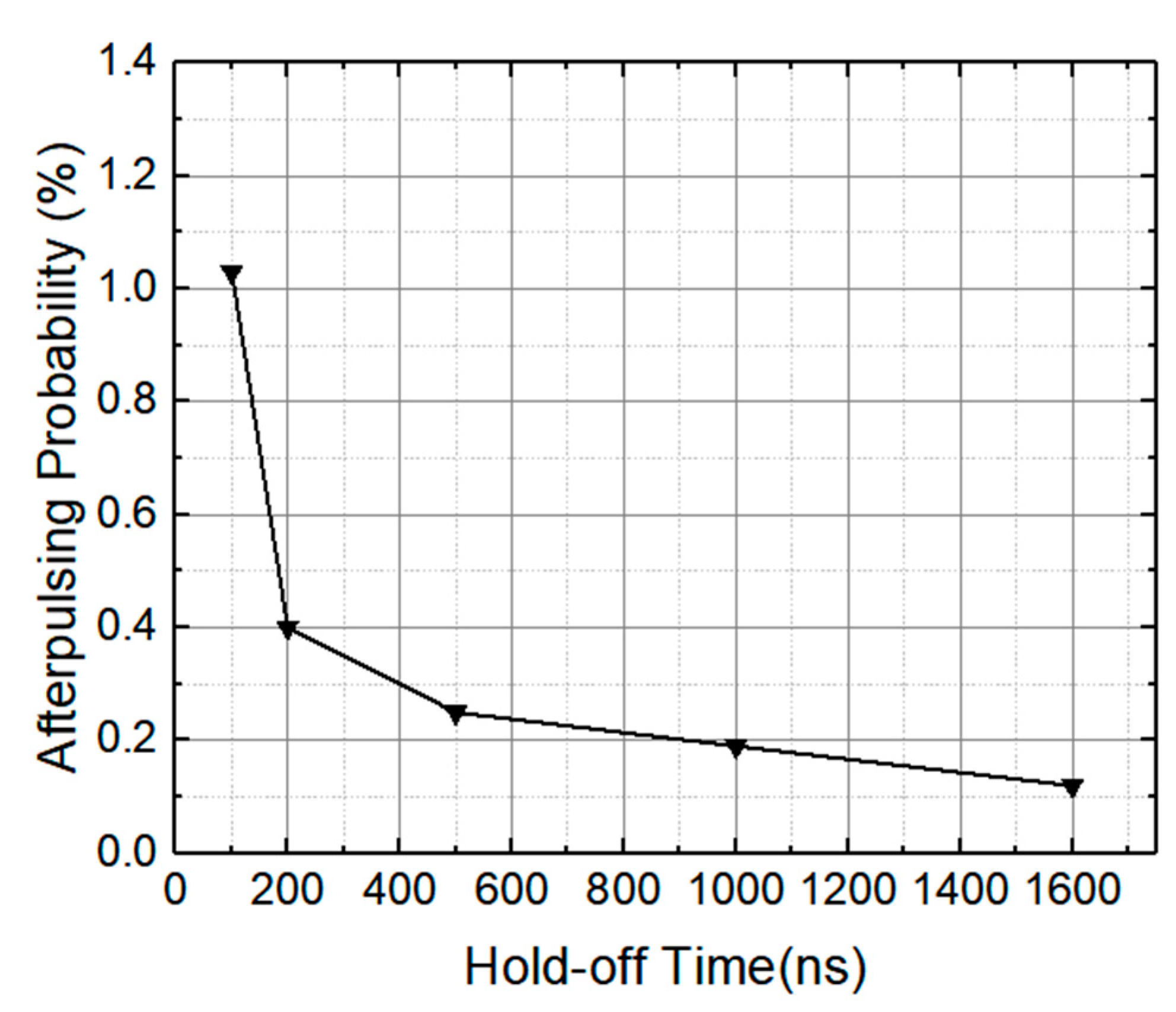

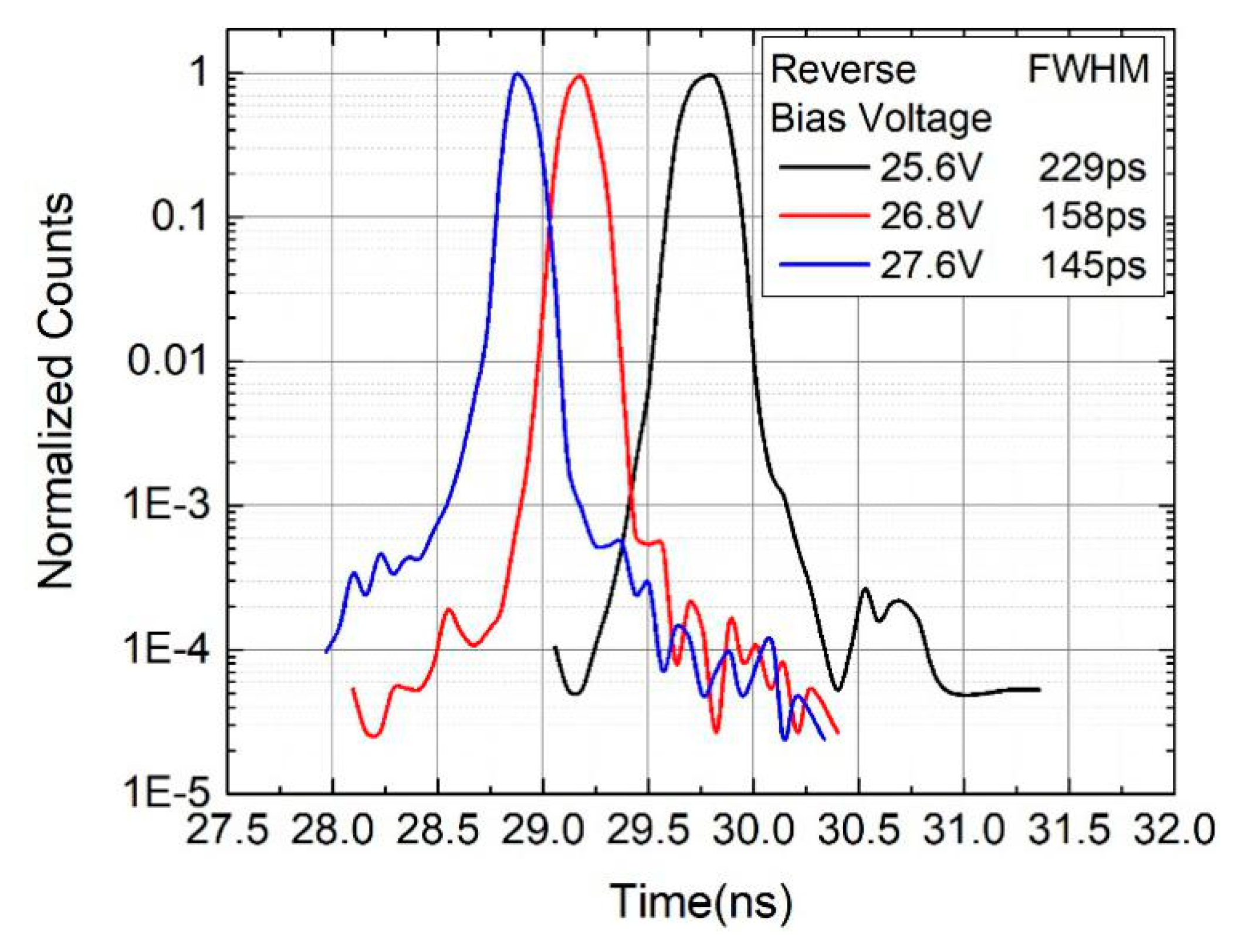

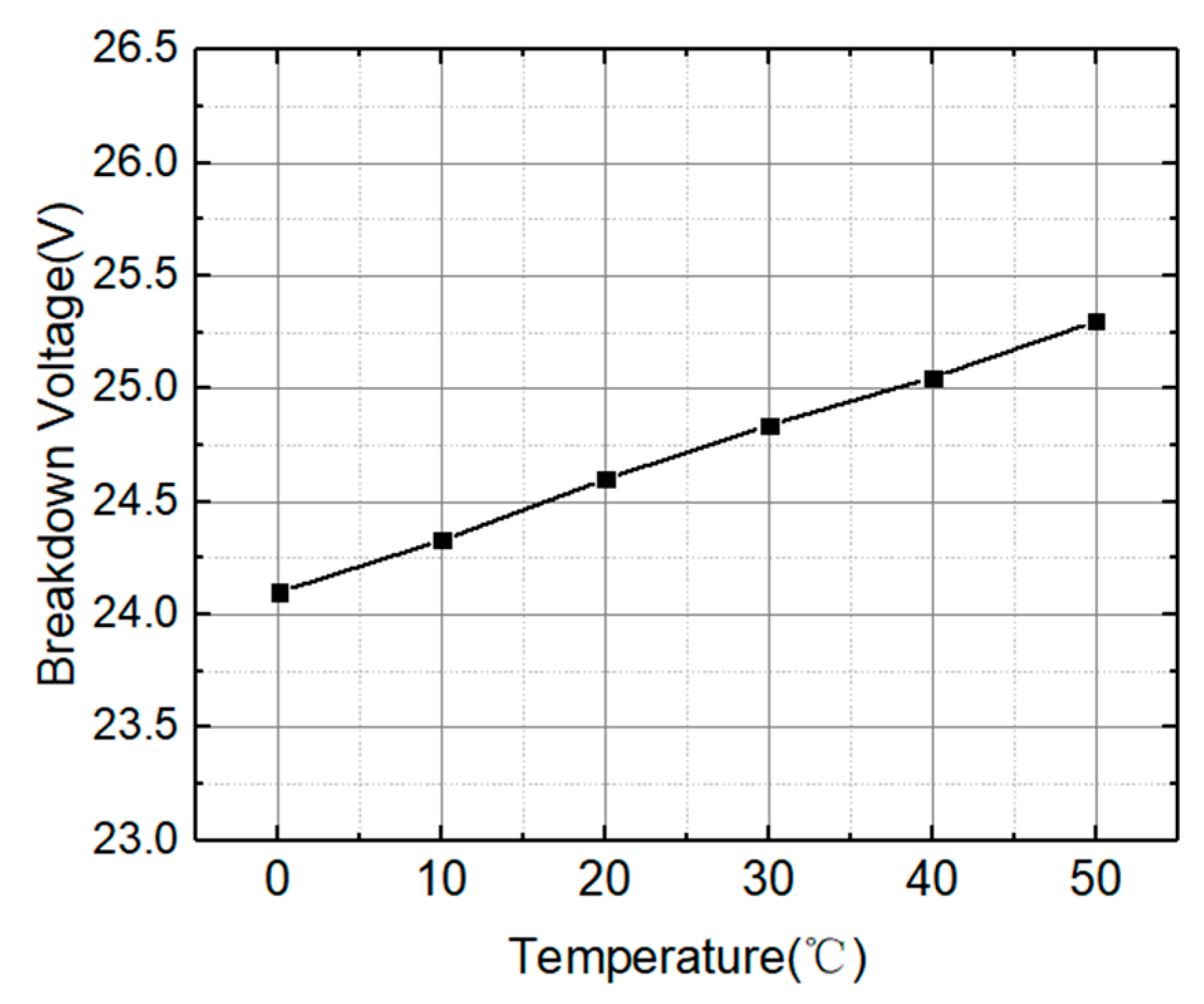

3. Experimental Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Tsai, S.-Y.; Chang, Y.-C.; Sang, T.-H. SPAD LiDARs: Modeling and Algorithms. In Proceedings of the 2018 14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Institute of Electrical and Electronics Engineers (IEEE), Qingdao, China, 31 October–3 November 2018; pp. 1–4. [Google Scholar]

- Zhang, C.; Lindner, S.; Antolović, I.M.; Pavia, J.M.; Wolf, M.; Charbon, E. A 30-frames/s, 252×144 SPAD Flash LiDAR With 1728 Dual-Clock 48.8-ps TDCs, and Pixel-Wise Integrated Histogramming. IEEE J. Solid-State Circuits 2019, 54, 1137–1151. [Google Scholar] [CrossRef]

- Martelli, P.; Brunero, M.; Fasiello, A.; Rossi, F.; Tosi, A.; Martinelli, M. Quantum Key Distribution Exploiting a Faraday Rotator and a Single SPAD. In Proceedings of the 2019 Conference on Lasers and Electro-Optics Europe & European Quantum Electronics Conference (CLEO/Europe-EQEC), Institute of Electrical and Electronics Engineers (IEEE), Munich, Germany, 23–27 June 2019. [Google Scholar]

- Gaudin, E.; Arpin, L.; Bouchard, J.; Paille, M.; Bouziri, H.; Bergeron, M.; Pepin, C.M.; Cadorette, J.; Fontaine, R.; LeComte, R. Performance characterization of a dual-threshold time-over-threshold APD-based detector front-end module for PET imaging. In Proceedings of the 2015 IEEE Nuclear Science Symposium and Medical Imaging Conference (NSS/MIC), San Diego, CA, USA, 31 October–7 November 2015; pp. 1–3. [Google Scholar]

- Arvani, F.; Carusone, T.C.; Rogers, E.S. TDC Sharing in SPAD-Based Direct Time-of-Flight 3D Imaging Applications. In Proceedings of the 2019 IEEE International Symposium on Circuits and Systems (ISCAS), Sapporo, Japan, 26–29 May 2019; pp. 1–5. [Google Scholar] [CrossRef]

- Villa, F.; Lussana, R.; Bronzi, D.; Zappa, F.; Giudice, A. 3D SPAD camera for Advanced Driver Assistance. In Proceedings of the 2017 International Conference of Electrical and Electronic Technologies for Automotive, Torino, Italy, 15–16 June 2017; pp. 1–5. [Google Scholar]

- COUNT®. Available online: https://www.lasercomponents.com/us/product/single-photon-counting-modules/ (accessed on 20 May 2020).

- PDM Series | PicoQuant. Available online: http://www.picoquant.com/products/category/photon-counting-detectors/pdm-series-single-photon-avalanche-diodes (accessed on 20 May 2020).

- Thorlabs. Available online: http://www.thorlabs.de/thorproduct.cfm?partnumber=SPCM50A (accessed on 20 May 2020).

- ID100 Visible Single-Photon Detector. Available online: http://www.idquantique.com/photon-counting/photon-counting-modules/id100/ (accessed on 20 May 2020).

- Single Photon Counting Modules Excelitas. Available online: http://www.excelitas.com/Pages/Product/Single-Photon-Counting-Modules-SPCM.aspx (accessed on 20 May 2020).

- Acconcia, G.; Rech, I.; Labanca, I.; Ghioni, M. 32ps timing jitter with a fully integrated front end circuit and single photon avalanche diodes. Electron. Lett. 2017, 53, 328–329. [Google Scholar] [CrossRef]

- Webster, E.A.G.; Grant, L.A.; Henderson, R.K. A High-Performance Single-Photon Avalanche Diode in 130-nm CMOS Imaging Technology. IEEE Electron Device Lett. 2012, 33, 1589–1591. [Google Scholar] [CrossRef]

- Berdalović, I.; Osrečki, Ž.; Šegmanović, F.; Grubišić, D.; Knežević, T.; Suligoj, T. Design of passive-quenching active-reset circuit with adjustable hold-off time for single-photon avalanche diodes. In Proceedings of the 2016 39th International Convention on Information and Communication Technology, Electronics and Microelectronics (MIPRO), Opatija, Croatia, 30 May–3 June 2016; pp. 34–39. [Google Scholar]

- Ruggeri, A.; Ciccarella, P.; Villa, F.; Zappa, F.; Tosi, A. Integrated Circuit for Subnanosecond Gating of InGaAs/InP SPAD. IEEE J. Quantum Electron. 2015, 51, 1–7. [Google Scholar] [CrossRef]

- Giustolisi, G.; Grasso, A.D.; Palumbo, G. Integrated Quenching-and-Reset Circuit for Single-Photon Avalanche Diodes. IEEE Trans. Instrum. Meas. 2014, 64, 271–277. [Google Scholar] [CrossRef]

- Liu, J.; Li, Y.; Ding, L.; Wang, Y.; Zhang, T.; Wang, Q.; Fang, J. Fast Active-Quenching Circuit for Free-Running InGaAs(P)/InP Single-Photon Avalanche Diodes. IEEE J. Quantum Electron. 2016, 52, 1–6. [Google Scholar] [CrossRef]

- MAX749 Digitally Adjustable LCD Bias Supply. Available online: https://datasheets.maximintegrated.com/en/ds/MAX749.pdf (accessed on 20 May 2020).

- Jackson, J.C.; Phelan, D.; Morrison, A.P.; Redfern, R.M.; Mathewson, A. Toward integrated single-photon-counting microarrays. Opt. Eng. 2003, 42, 112–118. [Google Scholar]

- Jackson, J.C.; Donnelly, J.; O’neill, B.; Kelleher, A.M.; Healy, G.; Morrison, A.P.; Mathewson, A. Integrated bulk/SOI APD sensor: Bulk substrate inspection with Geiger-mode avalanche photodiodes. Electron. Lett. 2003, 39, 735–736. [Google Scholar] [CrossRef]

- Deng, S.; Morrison, A.P. Active quench and reset integrated circuit with novel hold-off time control logic for Geiger-mode avalanche photodiodes. Opt. Lett. 2012, 37, 3876–3878. [Google Scholar] [CrossRef] [PubMed]

- Deng, S.; Gordon, D.; Morrison, A.P. A Geiger-Mode APD Photon Counting System With Adjustable Dead-Time and Interchangeable Detector. IEEE Photon-Technol. Lett. 2015, 28, 99–102. [Google Scholar] [CrossRef]

- Giudice, A.; Ghioni, M.; Cova, S.; Zappa, F. A process and deep level evaluation tool: Afterpulsing in avalanche junctions. In Proceedings of the Electrical Performance of Electrical Packaging (IEEE Cat. No. 03TH8710), Estoril, Portugal, 16–18 September 2003; pp. 347–350. [Google Scholar]

- Humer, G.; Peev, M.; Schaeff, C.; Ramelow, S.; Stipčević, M.; Ursin, R. A simple and robust method for estimating afterpulsing in single photon detectors. J. Light. Technol. 2015, 33, 1. [Google Scholar] [CrossRef]

- Ziarkash, A.W.; Joshi, S.K.; Stipčević, M.; Ursin, R. Comparative study of afterpulsing behavior and models in single photon counting avalanche photo diode detectors. Sci. Rep. 2018, 8, 5076. [Google Scholar] [CrossRef] [PubMed]

- Palubiak, D.P.; Li, Z.; Deen, J. Afterpulsing Characteristics of Free-Running and Time-Gated Single-Photon Avalanche Diodes in 130-nm CMOS. IEEE Trans. Electron. Devices 2015, 62, 3727–3733. [Google Scholar] [CrossRef]

- Villa, F.; Conca, E.; Sesta, V.; Lusardi, N.; Garzetti, F.; Geraci, A.; Zappa, F. SPADs and TDCs for photon-counting, timing and gated-imaging at 30 ps resolution and 60% efficiency. In Proceedings of the 2018 IEEE Nuclear Science Symposium and Medical Imaging Conference Proceedings (NSS/MIC), Sydney, Australia, 10–17 November 2018; pp. 1–5. [Google Scholar]

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, M.; Li, C.; Morrison, A.P.; Deng, S.; Teng, C.; Liu, H.; Deng, H.; Xiong, X.; Yuan, L. Design and Implementation of a Compact Single-Photon Counting Module. Electronics 2020, 9, 1131. https://doi.org/10.3390/electronics9071131

Chen M, Li C, Morrison AP, Deng S, Teng C, Liu H, Deng H, Xiong X, Yuan L. Design and Implementation of a Compact Single-Photon Counting Module. Electronics. 2020; 9(7):1131. https://doi.org/10.3390/electronics9071131

Chicago/Turabian StyleChen, Ming, Chenghao Li, Alan P. Morrison, Shijie Deng, Chuanxin Teng, Houquan Liu, Hongchang Deng, Xianming Xiong, and Libo Yuan. 2020. "Design and Implementation of a Compact Single-Photon Counting Module" Electronics 9, no. 7: 1131. https://doi.org/10.3390/electronics9071131

APA StyleChen, M., Li, C., Morrison, A. P., Deng, S., Teng, C., Liu, H., Deng, H., Xiong, X., & Yuan, L. (2020). Design and Implementation of a Compact Single-Photon Counting Module. Electronics, 9(7), 1131. https://doi.org/10.3390/electronics9071131