Design of Differential Variable-Gain Transimpedance Amplifier in 0.18 µm SiGe BiCMOS

Abstract

1. Introduction

2. Literature Review

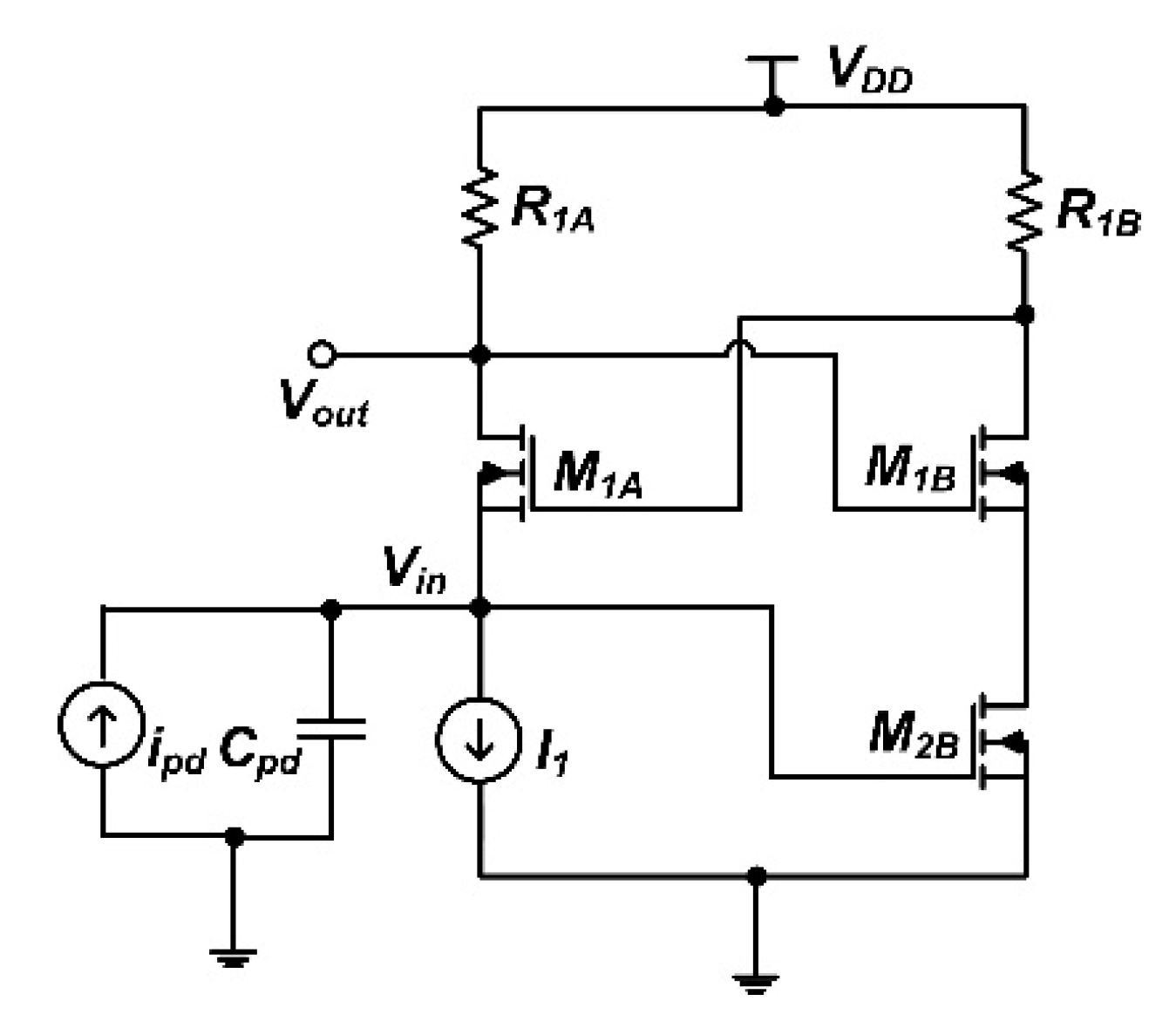

2.1. Regulated Cascode TIA

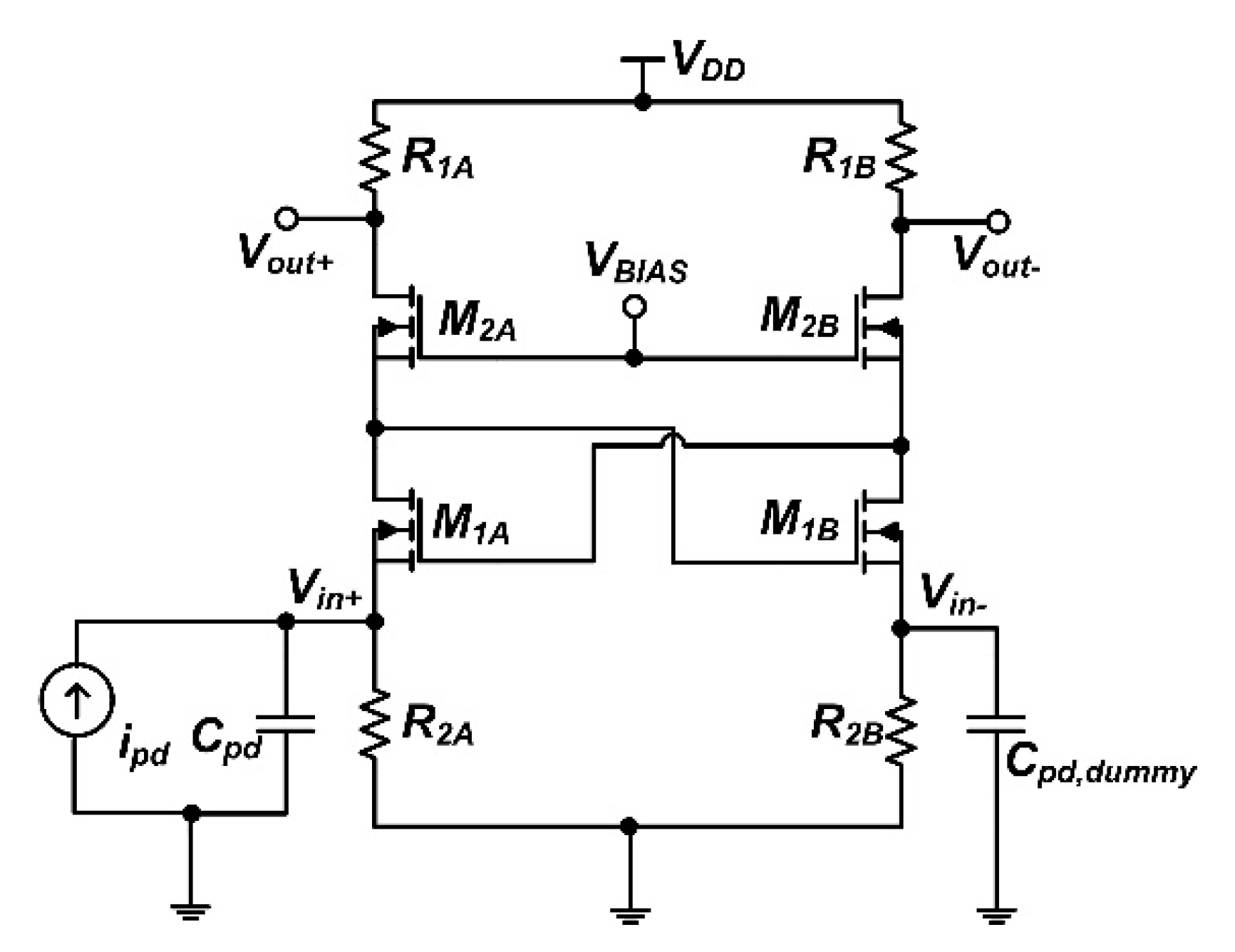

2.2. Cross-Coupling TIA

3. Design Process of Proposed DVGTIA

3.1. Proposed Input Stage of the DVGTIA Design

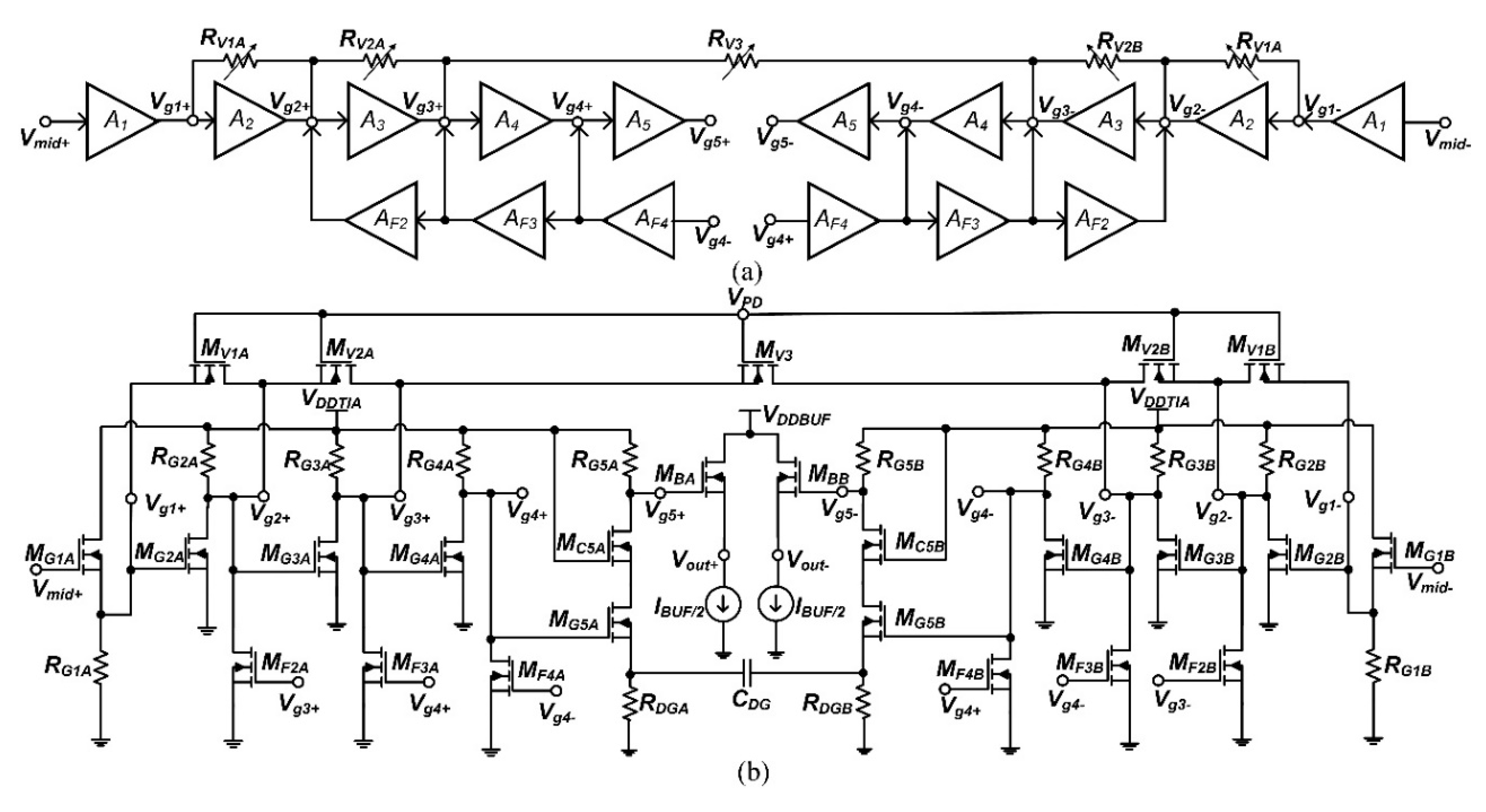

3.2. Proposed DVGTIA Gain Stage

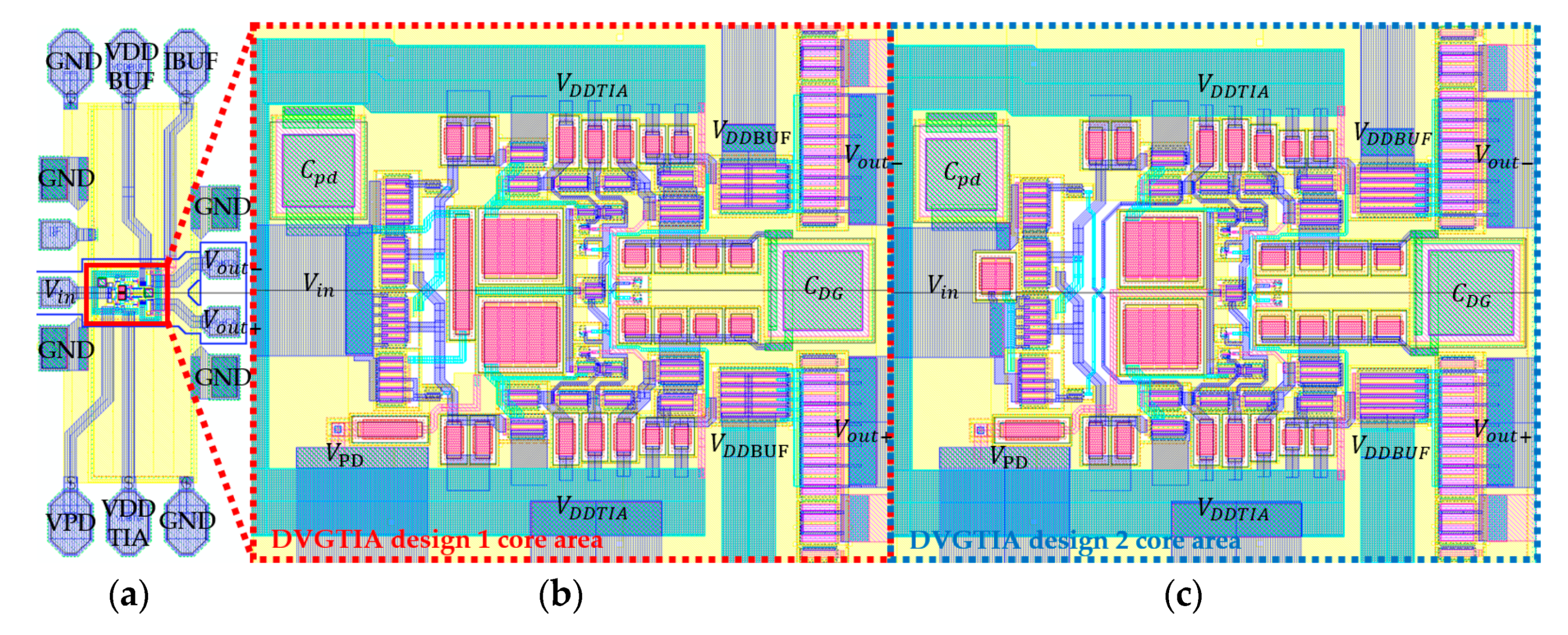

3.3. Layout and Die Microphotograph

3.4. Measurement Setup

4. Results and Discussion

4.1. Frequency Response from S-parameters

4.2. Input Referred 1dB Compression Point

4.3. Noise

4.4. Eye Diagram

4.5. Reliablity

5. Discussion

5.1. Comparison of Theory and Simulation/Measurement Results

5.2. Figure of Merit

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Karunatilaka, D.; Zafar, F.; Kalavally, V.; Parthiban, R. LED based indoor visible light communications: State of the art. IEEE Commun. Surv. Tutor. 2015, 17, 1649–1678. [Google Scholar] [CrossRef]

- Ergul, O.; Dinc, E.; Akan, O. Communicate to illuminate: State-of-the-art and research challenges for visible light communications. Phys. Commun. 2015, 17, 72–85. [Google Scholar] [CrossRef]

- Romanova, A.; Barzdenas, V. A Review of Modern CMOS Transimpedance Amplifiers for OTDR Applications. Electron. J. 2019, 8, 1073. [Google Scholar] [CrossRef]

- Samuel, L.B.S.; Sern, T.Y.; Kumar, T.B.; Yeo, K.S.; Li, Z.; Yu, X. An inductorless transimpedance amplifier design for 10 Gb/s optical communication using 0.18-μm CMOS. In Proceedings of the 15th International Symposium on Integrated Circuits (ISIC), Singapore, 12–14 December 2016. [Google Scholar]

- Samuel, L.B.S.; Sern, T.Y.; Kumar, T.B.; Yeo, K.S. An inductorless variable-gain transimpedance amplifier design for 4GHz optical communication using 0.18-μm CMOS. In Proceedings of the International Conference on Computer Networks and Communication Technology (CNCT 2016), Xiamen, China, 16–18 December 2016; Atlantis Press: Paris, France, 2016; Volume 54. [Google Scholar]

- Samuel, L.B.S.; Kumar, T.B.; Qiong, Z.; Yeo, K.S. An inductorless differential transimpedance amplifier design for 5 GHz optical communication using 0.18-µm CMOS. In Proceedings of the 14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), 2018, Qingdao, China, 31 October–3 November 2018. [Google Scholar]

- Lee, S.B.S.; Liu, H.; Yeo, K.S. An inductorless 6-GHz variable gain differential transimpedance amplifier in 0.18-μm SiGe BiCMOS. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), 2019, Sapporo, Japan, 26–29 May 2019. [Google Scholar]

- Lee, S.B.S.; Liu, H.; Yu, X.; Chen, J.M.; Yeo, K.S. An inductorless 5-GHz differential dual regulated cross-cascode transimpedance amplifier using 40 nm CMOS. In Proceedings of the IEEE 13th International Conference on ASIC (ASICON) 2019, Chongqing, China, 29 October–1 November 2019. [Google Scholar]

- Royo, G.; Sanchez-Azqueta, C.; Aldea, C.; Celma, S.; Gimeno, C. CMOS transimpedance amplifier with controllable gain for RF overlay. In Proceedings of the 12th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME) 2016, Lisbon, Portugal, 27–30 June 2016. [Google Scholar]

- Liu, H.; Zhu, X.; Boon, C.C.; Yi, X.; Kong, L. A 71 dB 150 µW variable-gain amplifier in 0.18 µm CMOS technology. IEEE Microw. Wirel. Compon. Lett. 2015, 25, 334–336. [Google Scholar] [CrossRef]

- Liu, H.; Zhu, X.; Boon, C.C.; He, X. Cell-Based variable-gain amplifiers with accurate dB-linear characteristic in 0.18 µm CMOS technology. IEEE J. Solid-State Circuits (JSSC) 2015, 50, 586–596. [Google Scholar] [CrossRef]

- Liu, H.; Boon, C.C.; He, X.; Zhu, X.; Yi, X.; Kong, L.; Heimlich, M.C. A wideband analog-controlled variable-gain amplifier with dB-linear characteristic for high-frequency applications. IEEE Trans. Microw. Theory Tech. 2016, 64, 533–540. [Google Scholar] [CrossRef]

- Kumar, T.B.; Ma, K.; Yeo, K.S. A 4 GHz 60 dB variable gain amplifier with tunable DC offset cancellation in 65 nm CMOS. IEEE Microw. Wirel. Compon. Lett. 2015, 25, 37–39. [Google Scholar] [CrossRef]

- Taghavi, M.H.; Belostotski, L.; Haslett, J.W. A CMOS low-power cross-coupled immittance-converter transimpedance amplifier. IEEE Microw. Wirel. Compon. Lett. 2015, 25, 403–405. [Google Scholar] [CrossRef]

- Chen, D.D.; Yeo, K.S.; Shi, X.; Manh, A.D.; Chirn, C.B.; Wei, M.L. Cross-coupled current conveyor based CMOS transimpedance amplifier for broadband data transmission. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2013, 21, 1516–1525. [Google Scholar] [CrossRef]

- Eissa, M.H.; Malignaggi, A.; Wang, R.; Elkhouly, M.; Schmalz, K.; Ulusoy, A.C.; Kissinger, D. Wideband 240-GHz transmitter and receiver in BiCMOS technology with 25-Gbit/s data rate. IEEE J. Solid-State Circuits (JSSC) 2018, 53, 2532–2542. [Google Scholar] [CrossRef]

- ElectronicsTutorials.ws, Power Triangle and Power Factor. Available online: https://www.electronics-tutorials.ws/accircuits/power-triangle.html (accessed on 3 June 2020).

- Sackinger, E. Analysis and Design of Transimpedance Amplifiers for Optical Receivers; John Wiley & Sons, Inc.: Hoboken, NJ, USA, 2017. [Google Scholar]

- University of Hawaii Department of Physics and Astronomy, Receiver Sensitivity/Noise. Available online: https://www.phys.hawaii.edu/~anita/new/papers/militaryHandbook/rcvr_sen.pdf (accessed on 3 June 2020).

- McCorkle, J. Microwaves101.com, Noise Figure One and Two Friss and IEEE. Available online: https://www.microwaves101.com/encyclopedias/noise-figure-one-and-two-friis-and-ieee (accessed on 3 June 2020).

- Ngo, T.H.; Kim, C.H.; Kwon, Y.J.; Ko, J.S.; Kim, D.-B.; Park, H.-H. Wideband receiver for a three-dimensional ranging LADAR system. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 448–456. [Google Scholar] [CrossRef]

- Schoeniger, D.; Henker, R.; Ellinger, F. A high-speed energy-efficient inductor-less transimpedance amplifier with adjustable gain for optical chip-to-chip communication. In Proceedings of the SBMO/IEEE MTT-S International Microwave and Optoelectronics Conference (IMOC) 2015, Porto de Galinhas, Brazil, 3–6 November 2015. [Google Scholar]

- Chen, R.Y.; Yang, Z.Y. CMOS transimpedance amplifier for gigabit-per-second optical wireless communications. IEEE Trans. Circuits Syst. Ii Exp. Briefs 2016, 63, 418–422. [Google Scholar] [CrossRef]

- Royo, G.; Martinez-Perez, A.D.; Aldea, C.; Celma, S. A Highly Linear Low-Noise Transimpedance Amplifier for Indoor Fiber-Wireless Remote Antenna Units. Electron. J. 2019, 8, 437. [Google Scholar] [CrossRef]

| Gain * | Transfer Function | Gain * | Transfer Function | ||

|---|---|---|---|---|---|

| ≈1 | |||||

| ≈1 | |||||

| Gain * | Transfer Function | Gain * | Transfer Function | ||

|---|---|---|---|---|---|

| Core Power (mW) | Total Power (mW) | |||

|---|---|---|---|---|

| DVGTIA design 1 | 17.08 | 30.7 | 10.73 | 50.1 |

| DVGTIA design 2 | 15.25 | 27.5 | 11.46 | 48.1 |

| Gain | Equation | Sim Value | Gain | Equation | Sim Value |

|---|---|---|---|---|---|

| −3.51 | −0.23 | ||||

| −2.61 | −0.05 | ||||

| −3.20 | −0.14 | ||||

| −1.77 | Equation (10) gain | 13.1 times | |||

| Reference | Unit | [9] a | [21] b | [22] | [23] | [24] | This Work | |

|---|---|---|---|---|---|---|---|---|

| Technology | nm | 180 CMOS | 130 CMOS | 130 BiCMOS | 180 CMOS | 65 CMOS | 180 BiCMOS Design1 Design2 | |

| V | 1.8 | 3 | 3.3 | 1.8 | 1.2 | 1.8 | ||

| pF | 0.9 | 2 | 0.02 | 0.25 | 0.45 | 0.25 | ||

| Maximum gain | dBΩ | 66 | 78 | 65.1 | 69.3 | 76 | 60.6 c | 62.8 c |

| Ω | 1995 | 7943 | 1793 | 2917 | 6310 | 1072 | 1380 | |

| Minimum gain | dBΩ | 48 | 48 | 56.7 | 55.8 | 60 | 24.5 | 27.8 |

| Ω | 251 | 251 | 684 | 617 | 1000 | 16.8 | 24.5 | |

| Gain range | dBΩ | 18 | 30 | 8.4 | 13.5 | 16 | 36.1 | 35 |

| Bandwidth | GHz | 1.5 | 0.64 | 6.8 | 1 | 0.3 | 6.42 | 5.22 |

| Core power | mW | 27 | 114 | 21.2 | 6 | 6 | 30.7 | 27.5 |

| Core area | mm2 | N.A. | 0.283 | 0.0078 | 0.0075 | 0.015 | 0.0085 | |

| Input-referred noise current | pA/√Hz | 6 d | 5.6 | 4.34 d | 9.33 | 2 d | 10.3 d | 21.7 d |

| Equationn (17) | 100 | 89 | 12 | 122 | 142 | 56 | 65 | |

| Equationn (18) | 1796 | 2676 | 97 | 1641 | 2272 | 2022 | 2293 | |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, S.B.S.; Liu, H.; Yeo, K.S.; Chen, J.-M.; Yu, X. Design of Differential Variable-Gain Transimpedance Amplifier in 0.18 µm SiGe BiCMOS. Electronics 2020, 9, 1058. https://doi.org/10.3390/electronics9071058

Lee SBS, Liu H, Yeo KS, Chen J-M, Yu X. Design of Differential Variable-Gain Transimpedance Amplifier in 0.18 µm SiGe BiCMOS. Electronics. 2020; 9(7):1058. https://doi.org/10.3390/electronics9071058

Chicago/Turabian StyleLee, Samuel B.S., Hang Liu, Kiat Seng Yeo, Jer-Ming Chen, and Xiaopeng Yu. 2020. "Design of Differential Variable-Gain Transimpedance Amplifier in 0.18 µm SiGe BiCMOS" Electronics 9, no. 7: 1058. https://doi.org/10.3390/electronics9071058

APA StyleLee, S. B. S., Liu, H., Yeo, K. S., Chen, J.-M., & Yu, X. (2020). Design of Differential Variable-Gain Transimpedance Amplifier in 0.18 µm SiGe BiCMOS. Electronics, 9(7), 1058. https://doi.org/10.3390/electronics9071058