Design of a Low Power 10-b 8-MS/s Asynchronous SAR ADC with On-Chip Reference Voltage Generator

Abstract

1. Introduction

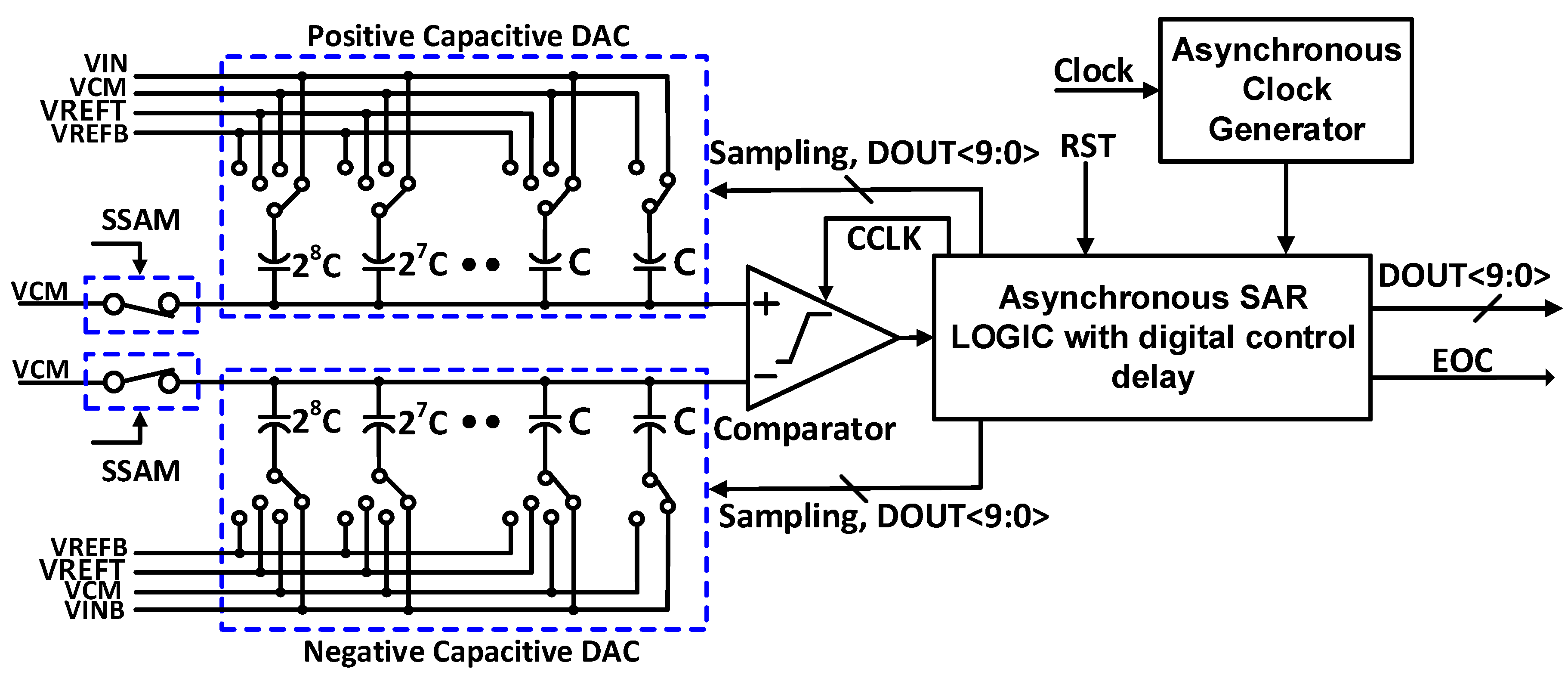

2. The Proposed ADC Architecture

3. Circuit Implementation

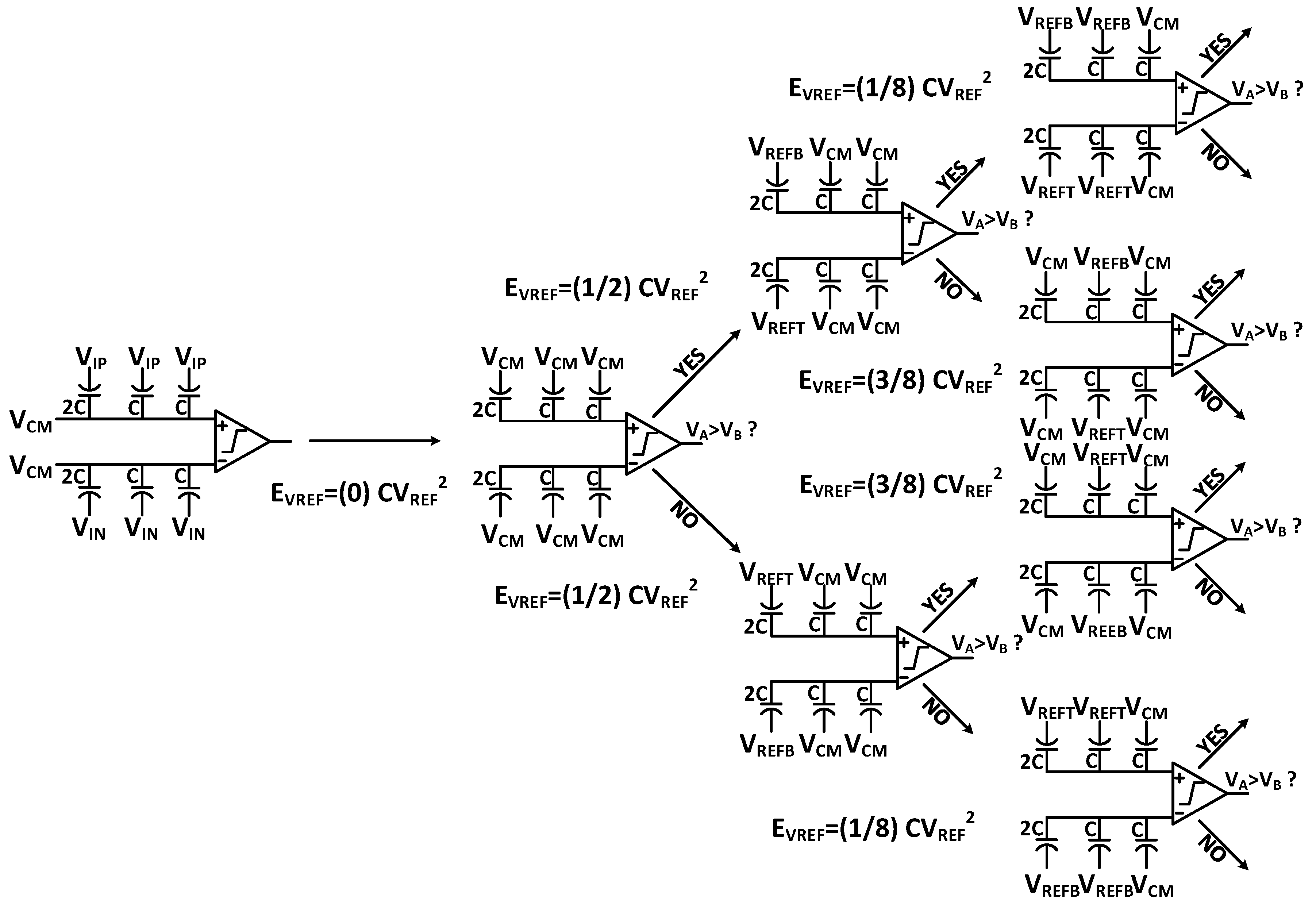

3.1. Capacitive DAC

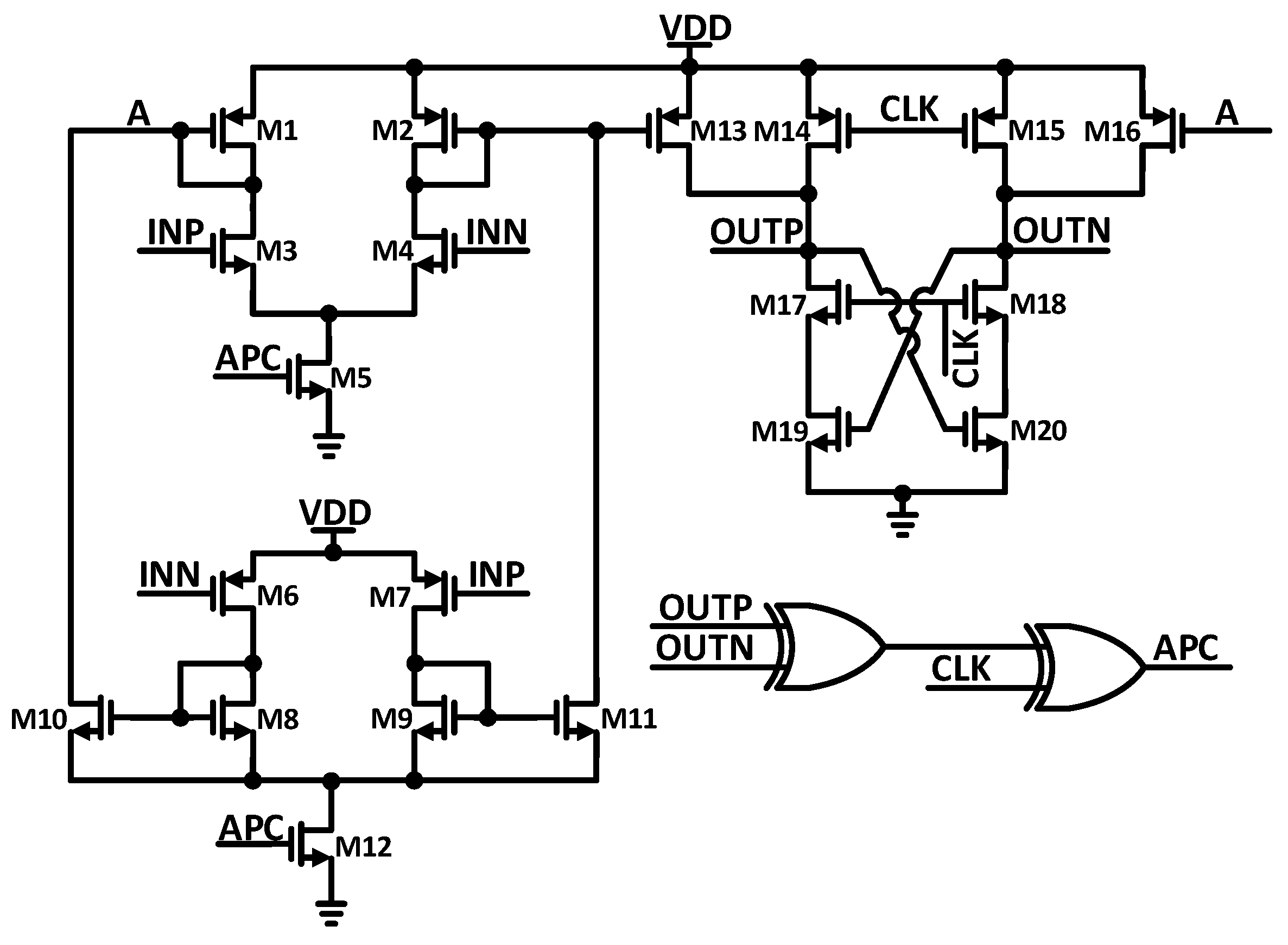

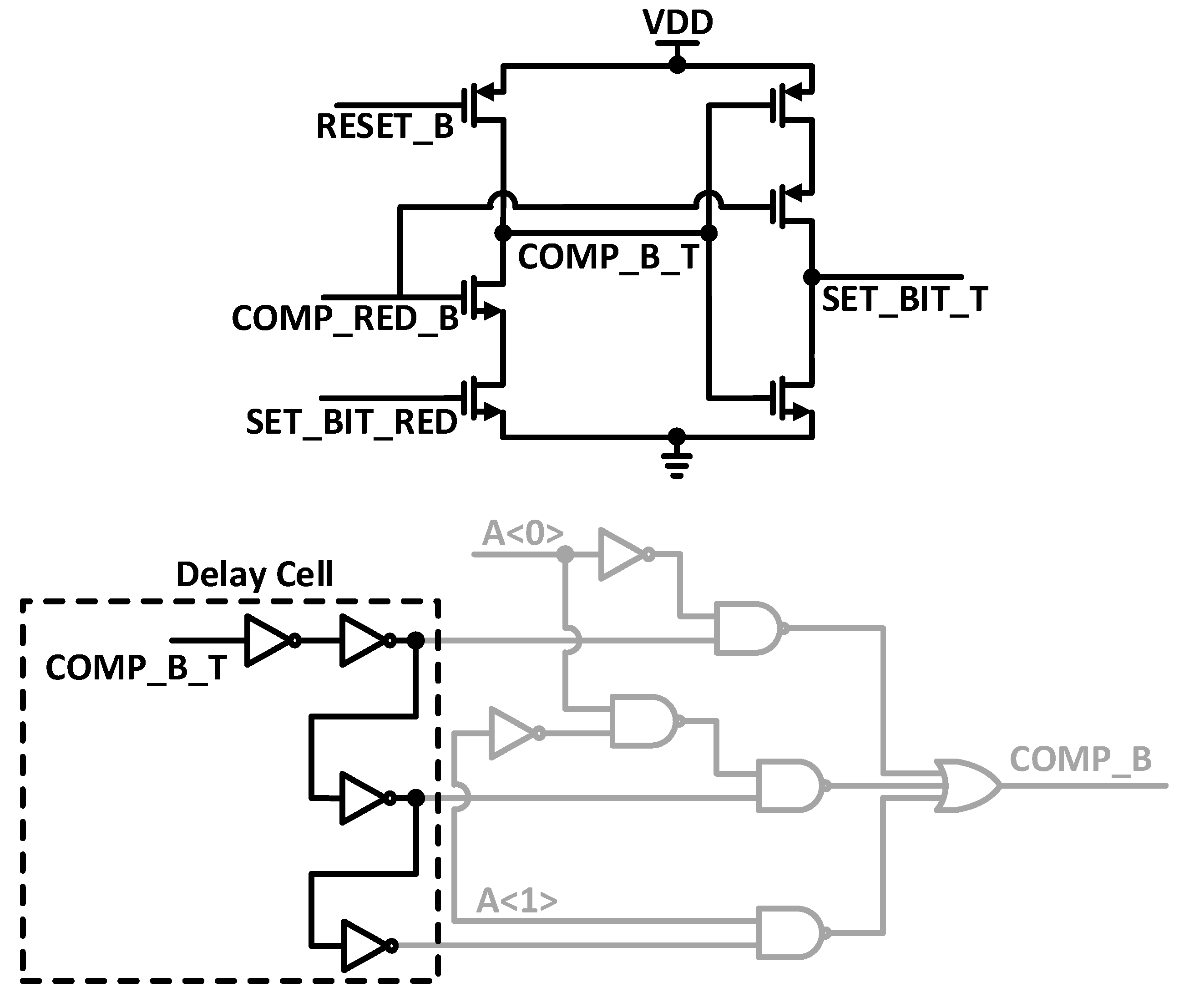

3.2. Rail-to-Rail Dynamic Latch Comparator with APC

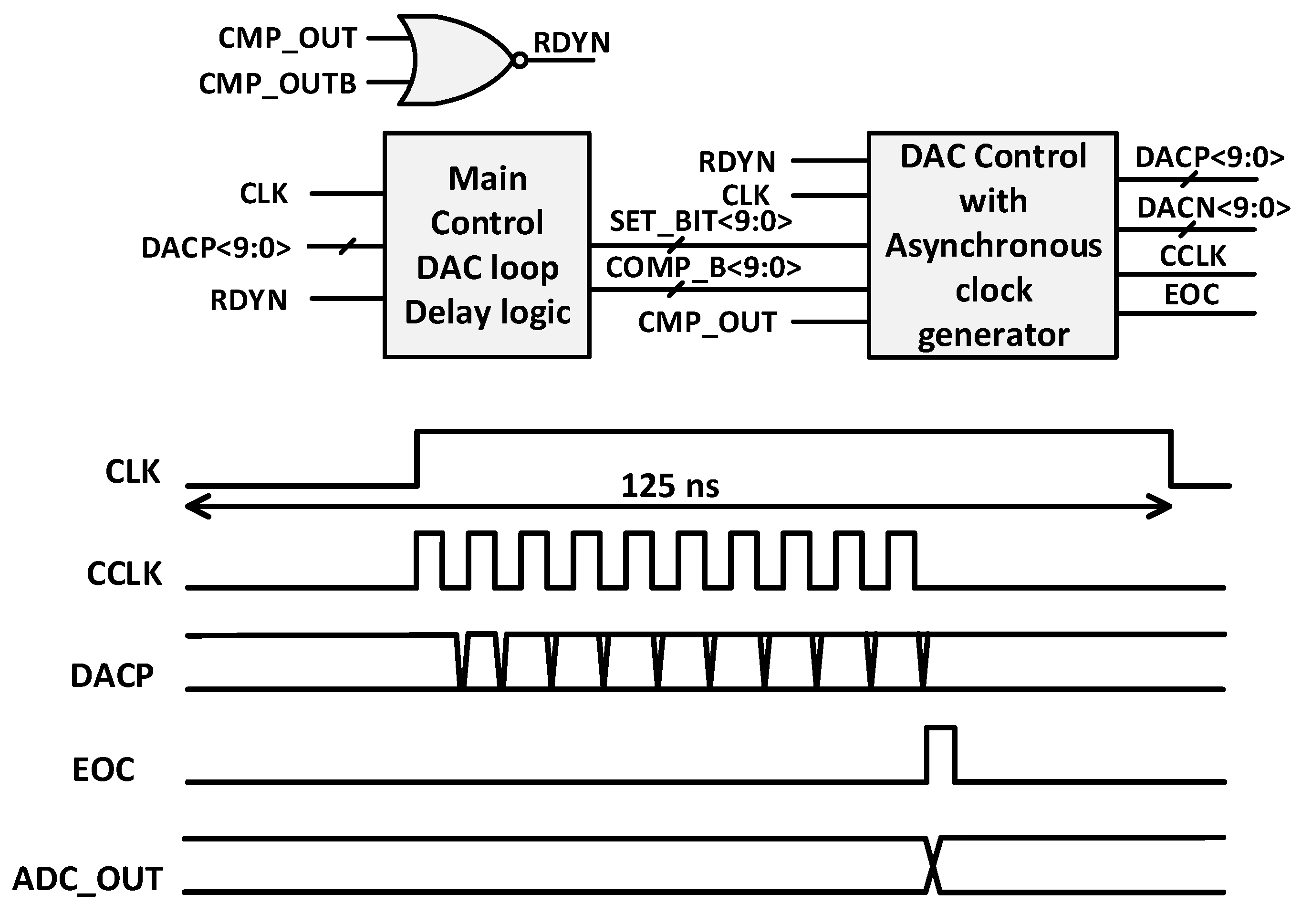

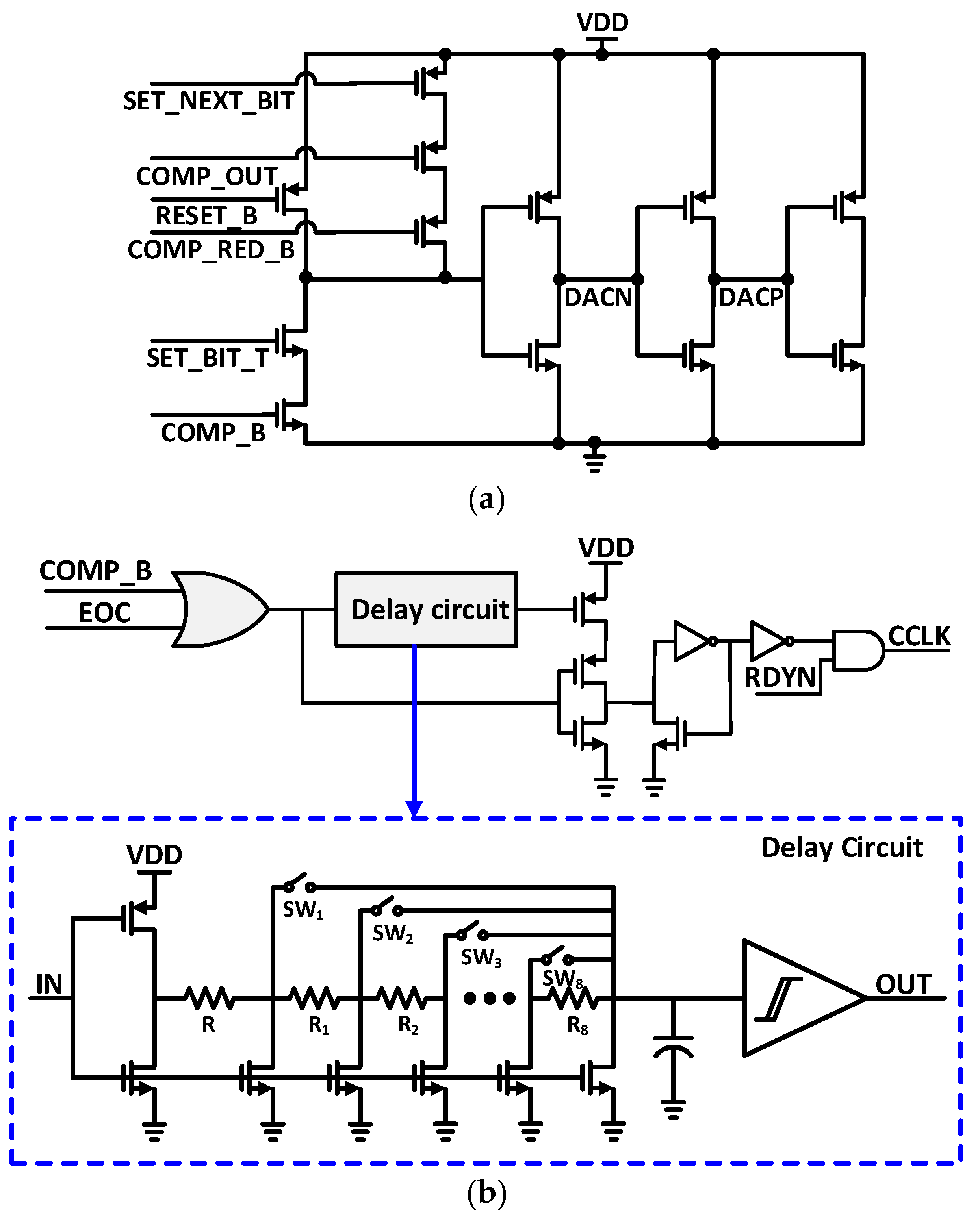

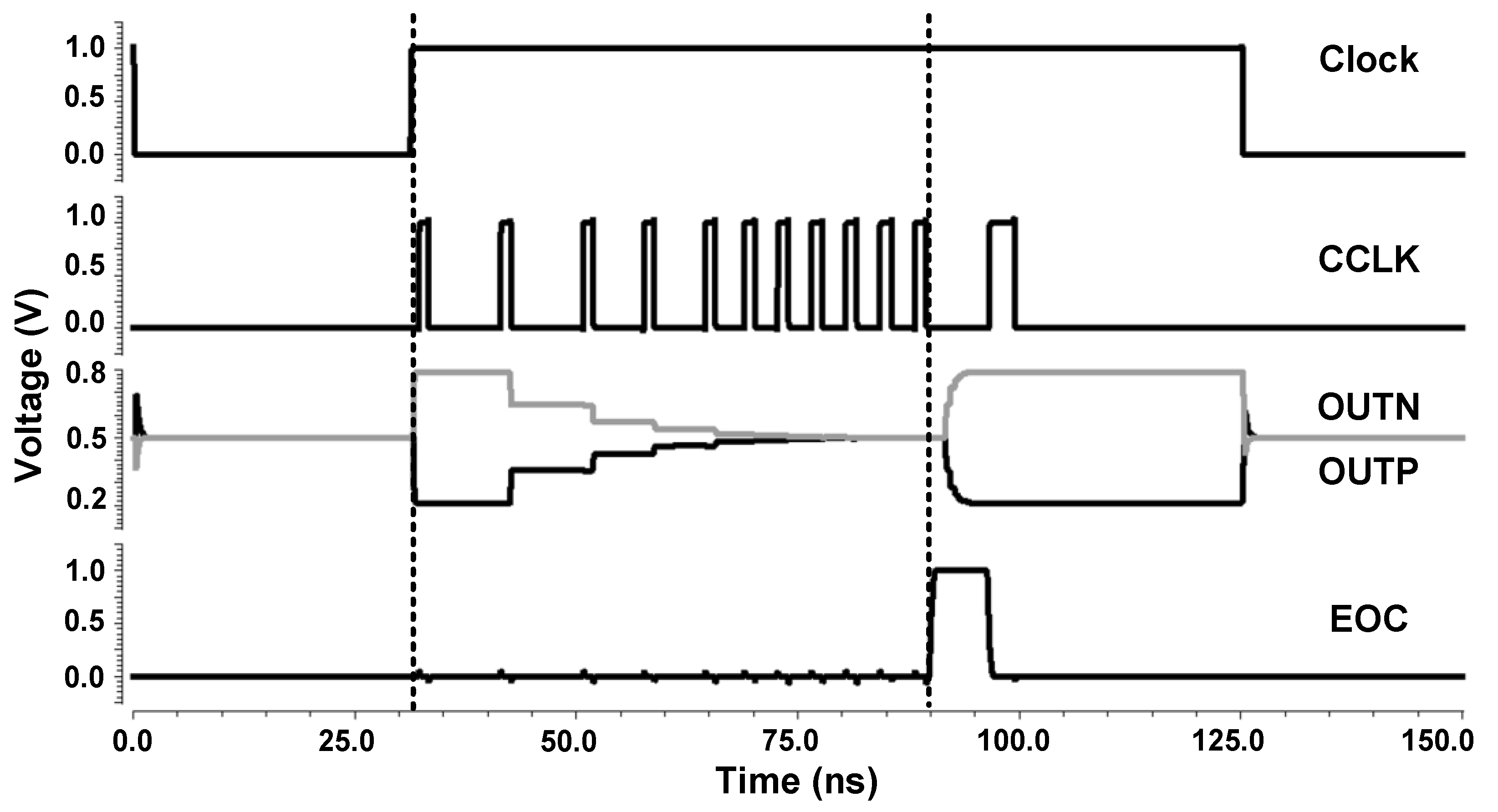

3.3. Asynchronous SAR Logic with Digital Control Delays

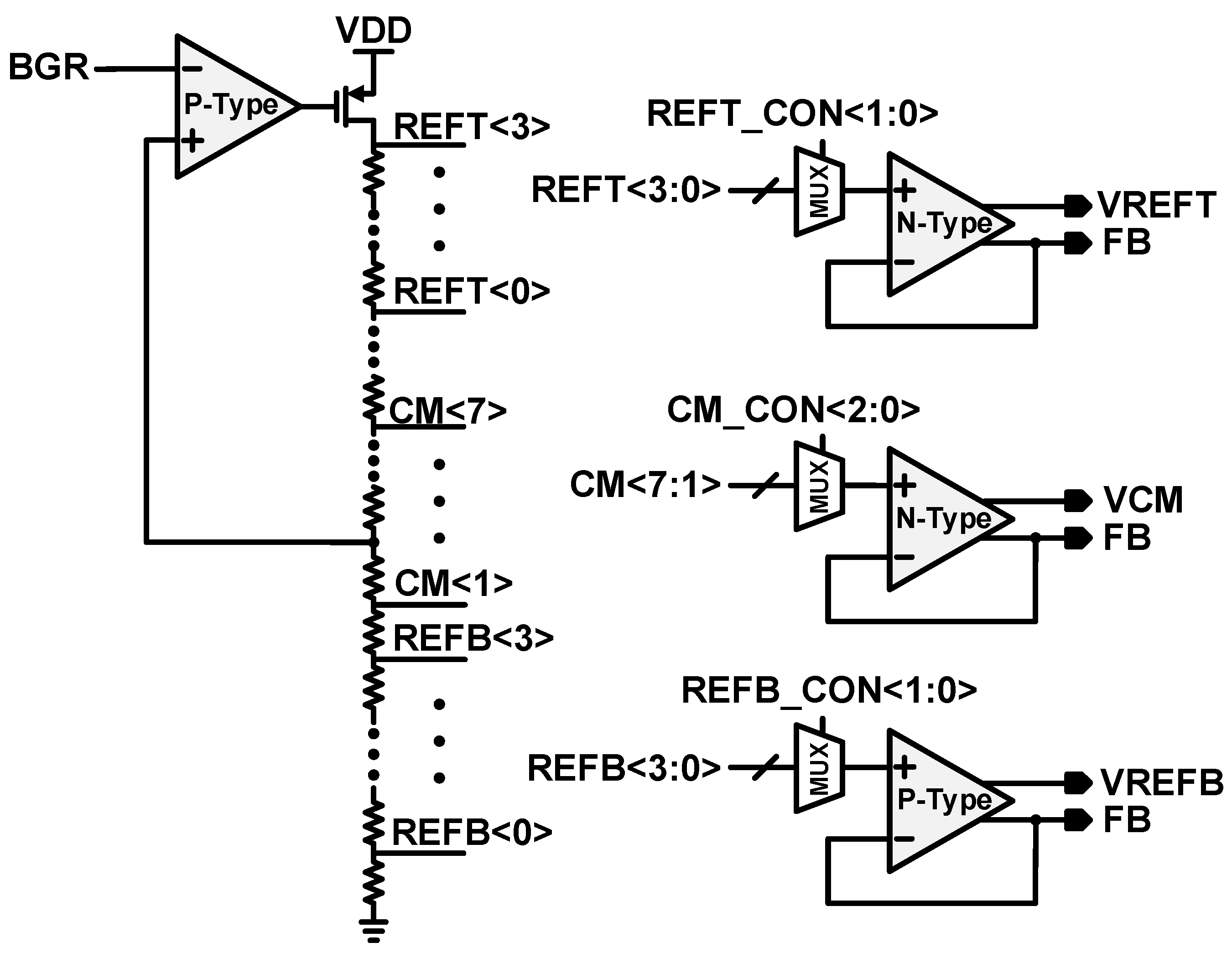

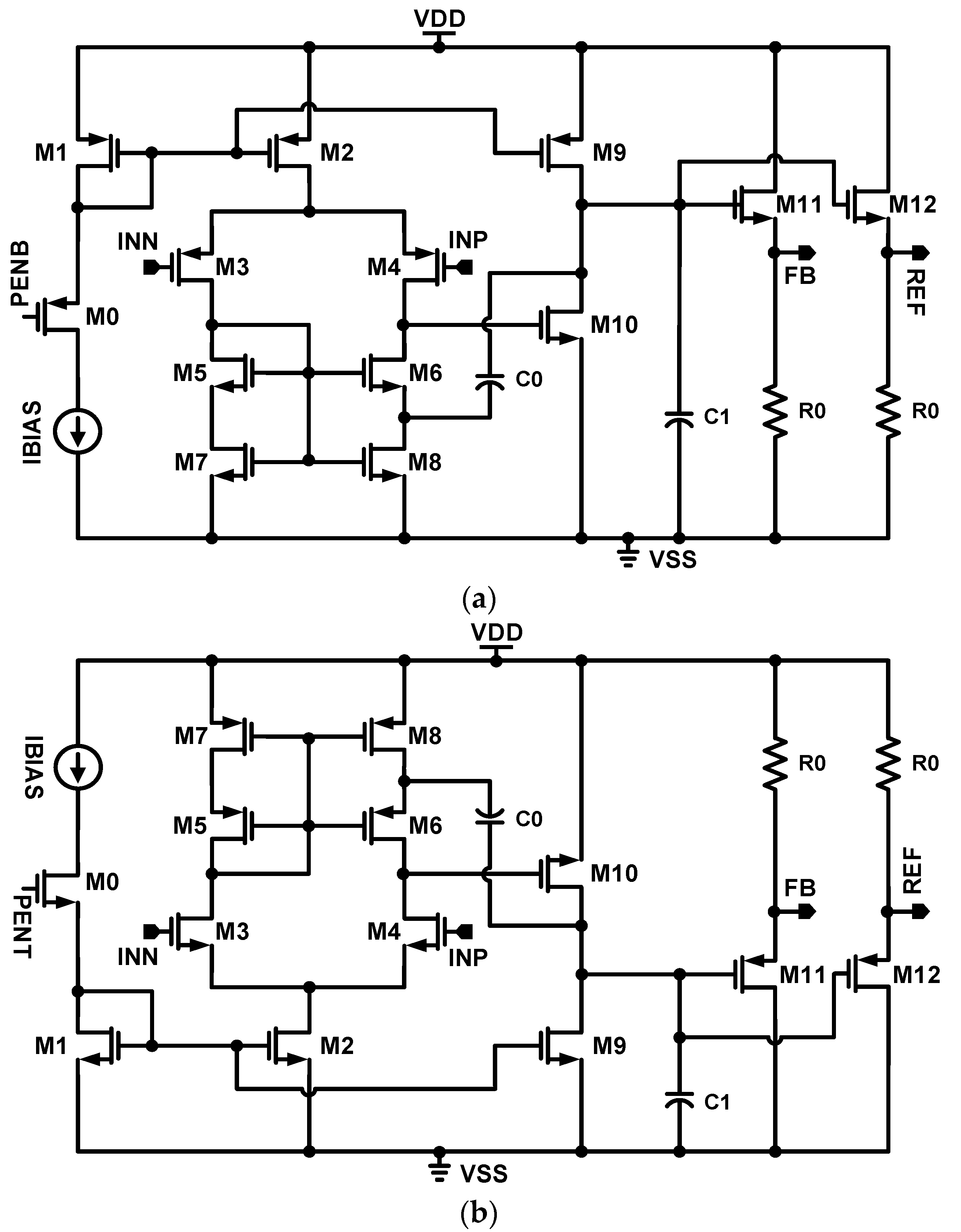

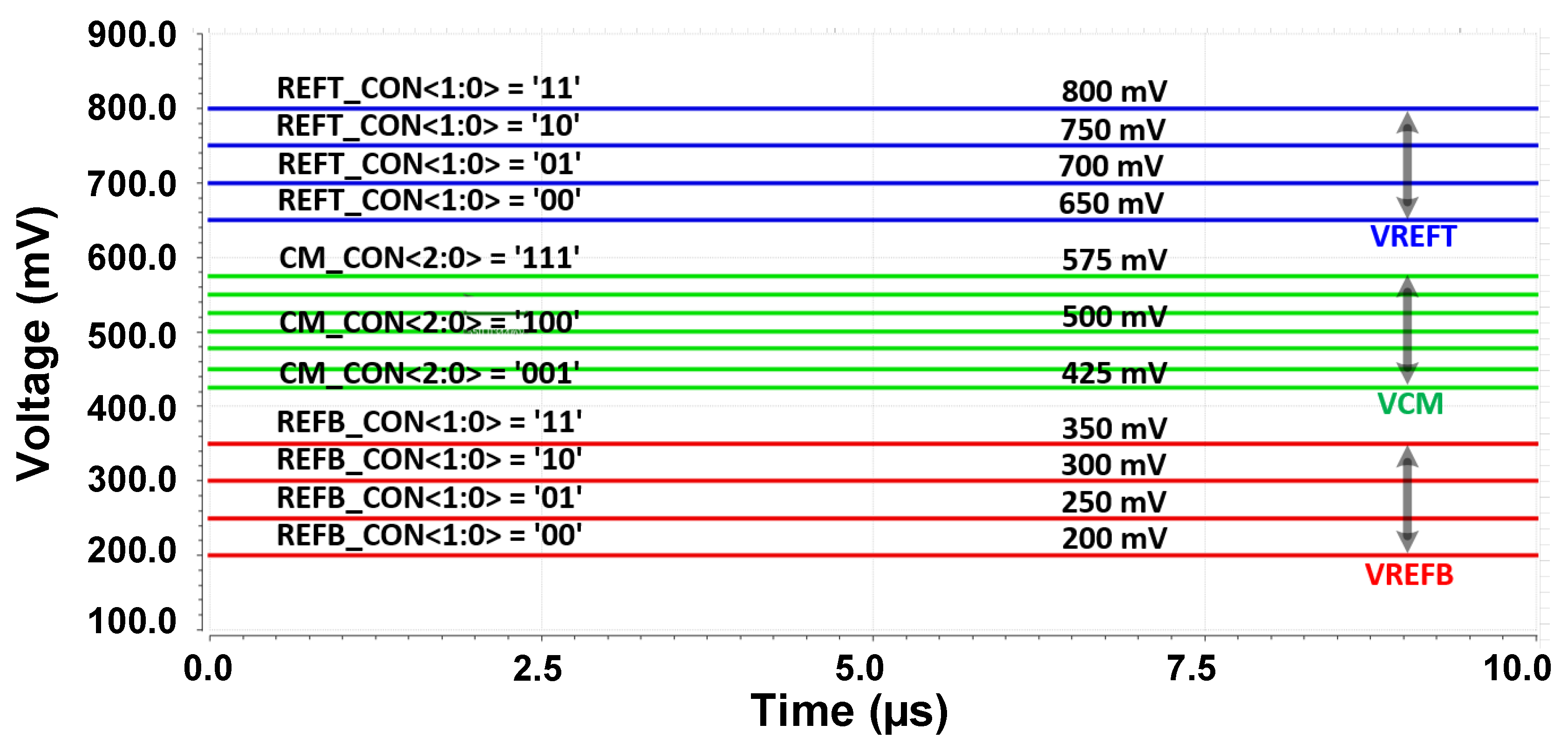

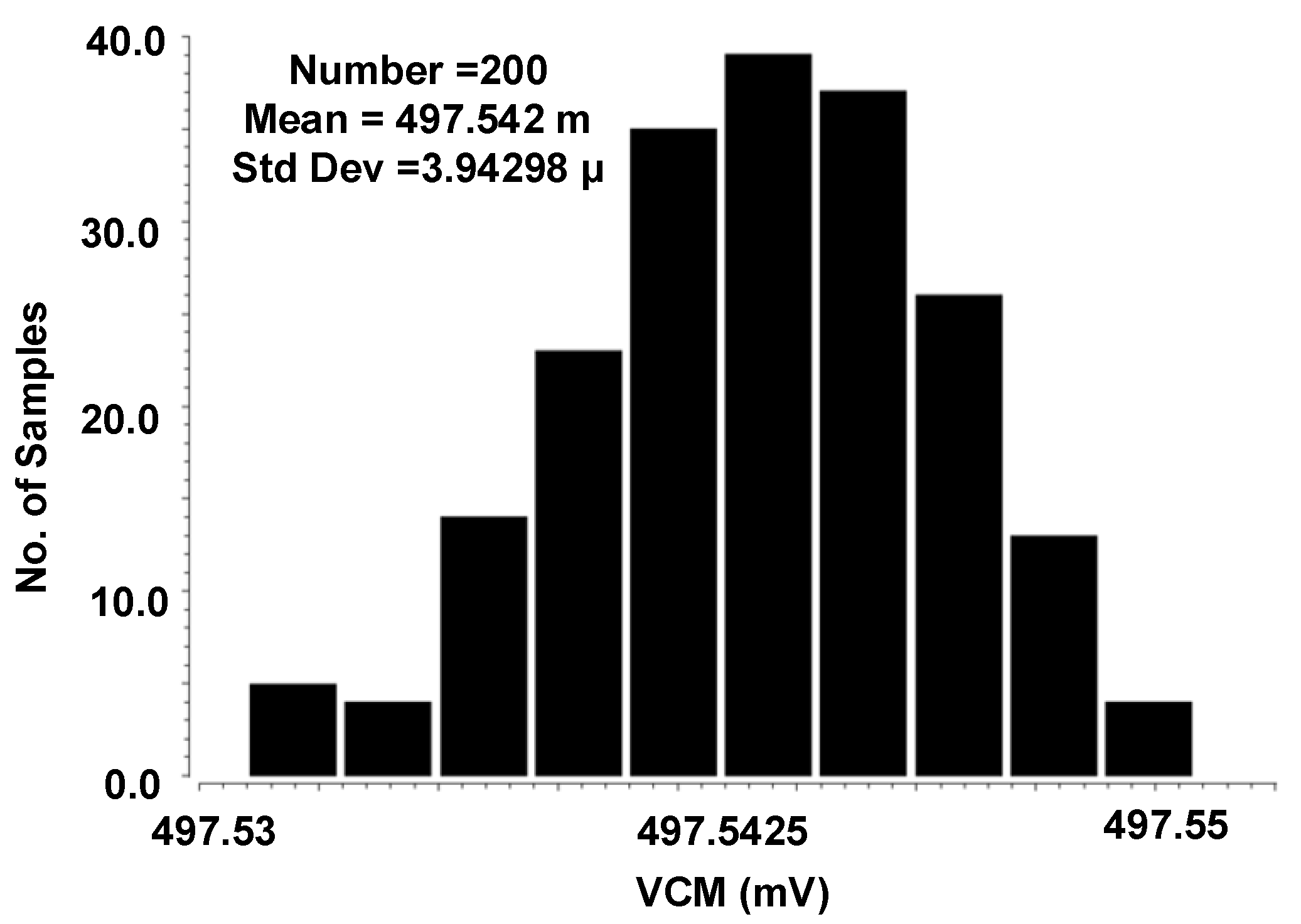

4. Reference Voltage Generator

5. Simulation and Measurement Results

5.1. Simulation Results

5.2. Measurement Results

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Kim, S.J.; Kim, D.G.; Oh, S.J.; Lee, D.S.; Pu, Y.; Hwang, K.C.; Yang, Y.; Lee, K.-Y. A Fully Integrated Bluetooth Low-Energy Transceiver with Integrated Single Pole Double Throw and Power Management Unit for IoT Sensors. Sensors 2019, 19, 2420. [Google Scholar] [CrossRef] [PubMed]

- Shim, J.; Kim, M.-K.; Hong, S.-K.; Kwon, O.-K. A low-power single-ended 11-bit SA-ADC with 1 V supply voltage and 2 V input voltage range for CMOS image sensors. In Proceedings of the 2016 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Jeju, Korea, 25–28 October 2016; pp. 410–413. [Google Scholar]

- Chen, S.-L.; Villaverde, J.F.; Lee, H.-Y.; Chung, D.W.-Y.; Lin, T.-L.; Tseng, C.-H.; Lo, K.-A. A Power-Efficient Mixed-Signal Smart ADC Design With Adaptive Resolution and Variable Sampling Rate for Low-Power Applications. IEEE Sens. J. 2017, 17, 3461–3469. [Google Scholar] [CrossRef]

- Shehzad, K.; Kang, H.-Y.; Verma, D.; Park, Y.J.; Lee, K.-Y. Low-power 10-bit SAR ADC using class-AB type amplifier for IoT applications. In Proceedings of the 2017 International SoC Design Conference (ISOCC), Seoul, Korea, 5–8 November 2017; pp. 224–225. [Google Scholar]

- Giannini, V.; Nuzzo, P.; Chironi, V.; Baschirotto, A.; van der Plas, G.; Craninckx, J. An 820µW 9b 40MS/s Noise-Tolerant Dynamic-SAR ADC in 90nm Digital CMOS. In Proceedings of the 2008 IEEE International Solid-State Circuits Conference—Digest of Technical Papers, San Francisco, CA, USA, 3–7 February 2008; pp. 238–239. [Google Scholar]

- Rikan, B.S.; Kim, S.; Abbasizadeh, H.; Hejazi, A.; Rad, R.E.; Shehzad, K.; Hwang, K.C.; Yang, Y.; Lee, M.; Lee, K.-Y. A 10- and 12-Bit Multi-Channel Hybrid Type Successive Approximation Register Analog-to-Digital Converter for Wireless Power Transfer System. Energies 2018, 11, 2673. [Google Scholar] [CrossRef]

- Scholtens, P.; Vertregt, M. A 6b 1.6 Gsample/s flash ADC in 0.18 /spl mu/m CMOS using averaging termination. In Proceedings of the 2002 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, San Francisco, CA, USA, 7 February 2002; Volume 1, pp. 168–457. [Google Scholar]

- Wang, D.; Zhu, X.; Guo, X.; Luan, J.; Zhou, L.; Wu, D.; Liu, H.; Wu, J.; Liu, X. A 2.6 GS/s 8-Bit Time-Interleaved SAR ADC in 55 nm CMOS Technology. Electronics 2019, 8, 305. [Google Scholar] [CrossRef]

- Verma, D.; Kang, H.Y.; Shehzad, K.; Rehman, M.R.U.; Lee, K.-Y. Design of asynchronous SAR ADC for low power mixed signal applications. In Proceedings of the 2017 International SoC Design Conference (ISOCC), Seoul, Korea, 5–8 November 2017; pp. 222–223. [Google Scholar]

- Xin, X.; Cai, J.; Xie, R.; Wang, P. Ultra-low power comparator with dynamic offset cancellation for SAR ADC. Electron. Lett. 2017, 53, 1572–1574. [Google Scholar] [CrossRef]

- Huang, C.P.; Lin, J.M.; Shyu, Y.T.; Chang, S.J. A Systematic design methodology of asynchronous SAR ADCs. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2016, 24, 1835–8148. [Google Scholar] [CrossRef]

- Liu, C.-C.; Chang, S.-J.; Huang, G.-Y.; Lin, Y.-Z. A 10-bit 50-MS/s SAR ADC with a Monotonic Capacitor Switching Procedure. IEEE J. Solid State Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Zhu, Y.; Chan, C.-H.; Chio, U.-F.; Sin, S.-W.; Seng-Pan, U.; Martins, R.P.; Maloberti, F. A 10-bit 100-MS/s Reference-Free SAR ADC in 90 nm CMOS. IEEE J. Solid State Circuits 2010, 45, 1111–1121. [Google Scholar] [CrossRef]

- Lu, C.-C.; Huang, D.-K. A 10-Bits 50-MS/s SAR ADC Based on Area-Efficient and Low-Energy Switching Scheme. IEEE Access 2020, 8, 28257–28266. [Google Scholar] [CrossRef]

- Verma, D.; Shehzad, K.; Khan, D.; Ain, Q.U.; Kim, S.J.; Lee, D.; Pu, Y.G.; Lee, M.; Hwang, K.C.; Yang, Y.; et al. A Design of 8 fJ/Conversion-Step 10-bit 8MS/s Low Power Asynchronous SAR ADC for IEEE 802.15.1 IoT Sensor Based Applications. IEEE Access 2020, 8, 85869–85879. [Google Scholar] [CrossRef]

- Guerber, J.; Venkatram, H.; Oh, T.; Moon, U.-K. Enhanced SAR ADC energy efficiency from the early reset merged capacitor switching algorithm. In Proceedings of the 2012 IEEE International Symposium on Circuits and Systems (ISCAS), Seoul, Korea, 20–23 May 2012; pp. 2361–2364. [Google Scholar] [CrossRef]

- Verma, D.; Shehzad, K.; Kim, S.J.; Lee, K.-Y. Low Power 10-BIT 8MS/s Asynchronous SAR ADC with Wake-up and Sample Logic for BLE Application. In Proceedings of the 2020 International Conference on Electronics, Information, and Communication (ICEIC), Barcelona, Spain, 19–22 January 2020; pp. 1–3. [Google Scholar]

- Melek, L.A.P.; Da Silva, A.L.; Schneider, M.C.; Galup-Montoro, C. Analysis and Design of the Classical CMOS Schmitt Trigger in Subthreshold Operation. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 869–878. [Google Scholar] [CrossRef]

- Zhang, Y.; Guo, G.; Yan, Y.; Yang, T. Asynchronous 10MS/s 10-Bit SAR ADC for wireless network. Int. J. Comput. Theory Eng. 2014, 6, 443–446. [Google Scholar] [CrossRef][Green Version]

- Borghetti, F.; Nielsen, J.; Ferragina, V.; Malcovati, P.; Andreani, P.; Baschirotto, A. A Programmable 10b up-to-6MS/s SAR-ADC Featuring Constant-FoM with On-Chip Reference Voltage Buffers. In Proceedings of the 2006 Proceedings of the 32nd European Solid-State Circuits Conference, Montreux, Switzerland, 19–21 September 2006; pp. 500–503. [Google Scholar]

- Harikumar, P.; Wikner, J. Design of a reference voltage buffer for a 10-bit 50 MS/s SAR ADC in 65 nm CMOS. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015; pp. 249–252. [Google Scholar]

- Yu, M.; Wu, L.; Li, F.; Wang, Z. An 8 bit 12 MS/s asynchronous successive approximation register ADC with an on-chip reference. J. Semicond. 2013, 34, 25010. [Google Scholar] [CrossRef]

- Liu, M.; Van Roermund, A.; Harpe, P. A 10-b 20-MS/s SAR ADC with DAC-Compensated Discrete-Time Reference Driver. IEEE J. Solid State Circuits 2018, 54, 417–427. [Google Scholar] [CrossRef]

| Parameter | [14] | [20] | [21] | [22] | [23] | This Work |

|---|---|---|---|---|---|---|

| Process (nm) | 90 | 130 | 65 | 180 | 65 | 55 |

| Resolution (bit) | 10 | 10 | 10 | 8 | 10 | 10 |

| Sampling Rate (MS/s) | 50 | 5.5 | 50 | 12 | 20 | 8 |

| Supply Voltage (V) | 1.2 | 1.2 | 1.2 | 1.8 | 1 | 1 |

| SNDR (dB) | 57.5 | 58.9 | 57.4 | 47.8 | 54.4 | 59.3 |

| ENOB (bit) | 9.26 | 9.5 | 9.25 | - | - | 9.56 |

| DNL (LSB) | +0.36/−0.32 | 0.55 | - | +0.43/−0.26 | +0.43/−0.26 | 0.4/−0.2 |

| INL (LSB) | +0.45/−0.38 | 0.6 | - | +0.34/−0.4 | +0.34/−0.4 | 0.5/−0.6 |

| On-chip Ref. | No | Yes | Yes | Yes | No | Yes |

| Power w Ref Gen (mW) | - | 3.2 | 20.697 | 0.92 | - | 0.572 |

| Power w/o Ref Gen (mW) | 0.664 | 0.2 | 0.697 | - | 0.133 | 0.108 |

| FOM w Ref Gen (fJ/step) | - | 1000 | 738 | 384 | - | 94.7 |

| FOM w/o Ref Gen (fJ/step) | 21.68 | 100 | 25 | - | 17.2 | 17.8 |

| Active Area (mm2) | 0.024 | 0.750 | 0.055 | 0.100 | 0.074 | 0.052 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shehzad, K.; Verma, D.; Khan, D.; Ain, Q.U.; Basim, M.; Kim, S.J.; Pu, Y.; Hwang, K.C.; Yang, Y.; Lee, K.-Y. Design of a Low Power 10-b 8-MS/s Asynchronous SAR ADC with On-Chip Reference Voltage Generator. Electronics 2020, 9, 872. https://doi.org/10.3390/electronics9050872

Shehzad K, Verma D, Khan D, Ain QU, Basim M, Kim SJ, Pu Y, Hwang KC, Yang Y, Lee K-Y. Design of a Low Power 10-b 8-MS/s Asynchronous SAR ADC with On-Chip Reference Voltage Generator. Electronics. 2020; 9(5):872. https://doi.org/10.3390/electronics9050872

Chicago/Turabian StyleShehzad, Khuram, Deeksha Verma, Danial Khan, Qurat Ul Ain, Muhammad Basim, Sung Jin Kim, YoungGun Pu, Keum Cheol Hwang, Youngoo Yang, and Kang-Yoon Lee. 2020. "Design of a Low Power 10-b 8-MS/s Asynchronous SAR ADC with On-Chip Reference Voltage Generator" Electronics 9, no. 5: 872. https://doi.org/10.3390/electronics9050872

APA StyleShehzad, K., Verma, D., Khan, D., Ain, Q. U., Basim, M., Kim, S. J., Pu, Y., Hwang, K. C., Yang, Y., & Lee, K.-Y. (2020). Design of a Low Power 10-b 8-MS/s Asynchronous SAR ADC with On-Chip Reference Voltage Generator. Electronics, 9(5), 872. https://doi.org/10.3390/electronics9050872