A 12-Bit 200 MS/s Pipelined-SAR ADC Using Back-Ground Calibration for Inter-Stage Gain

Abstract

1. Introduction

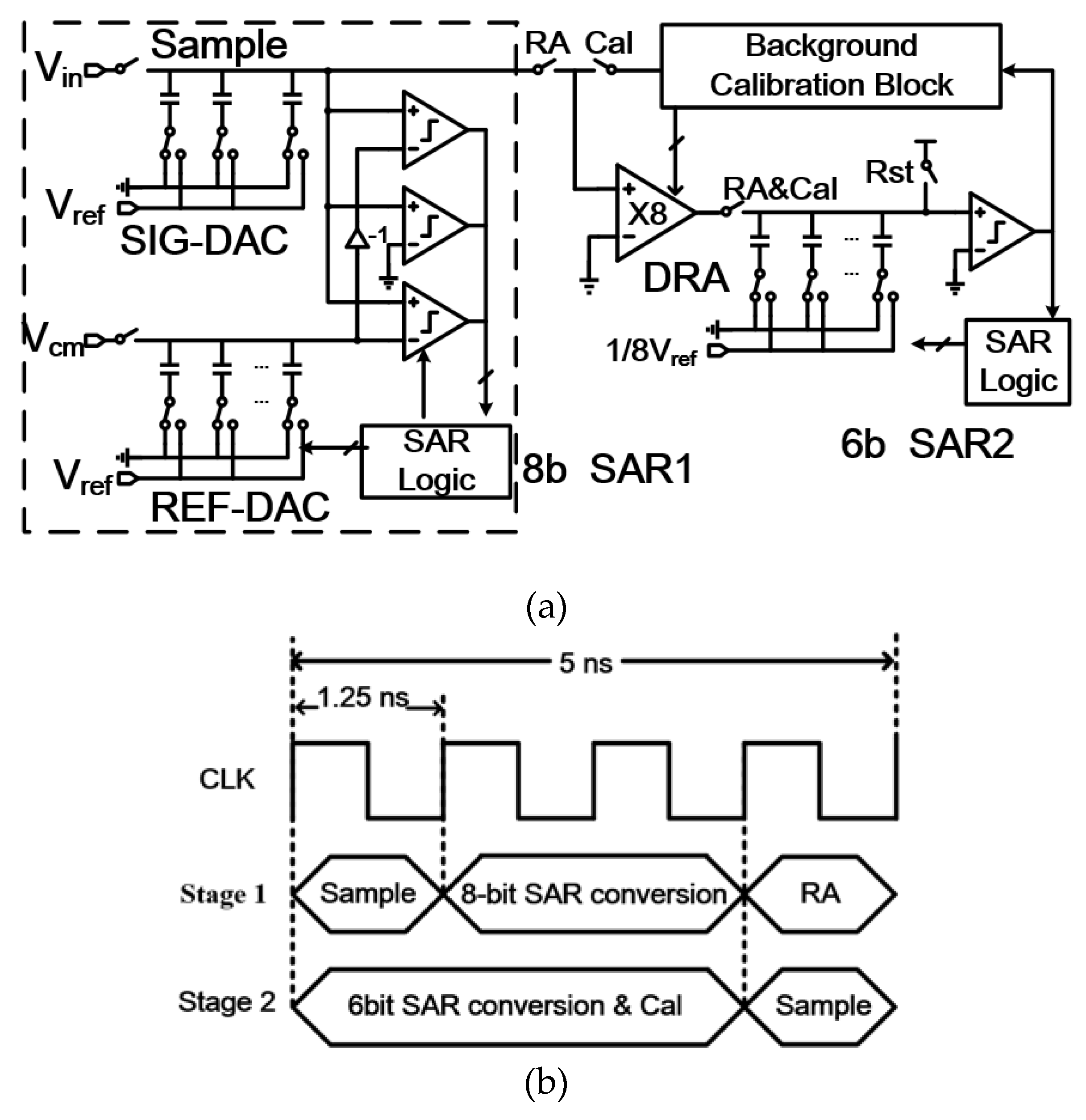

2. Architecture of the Proposed ADC

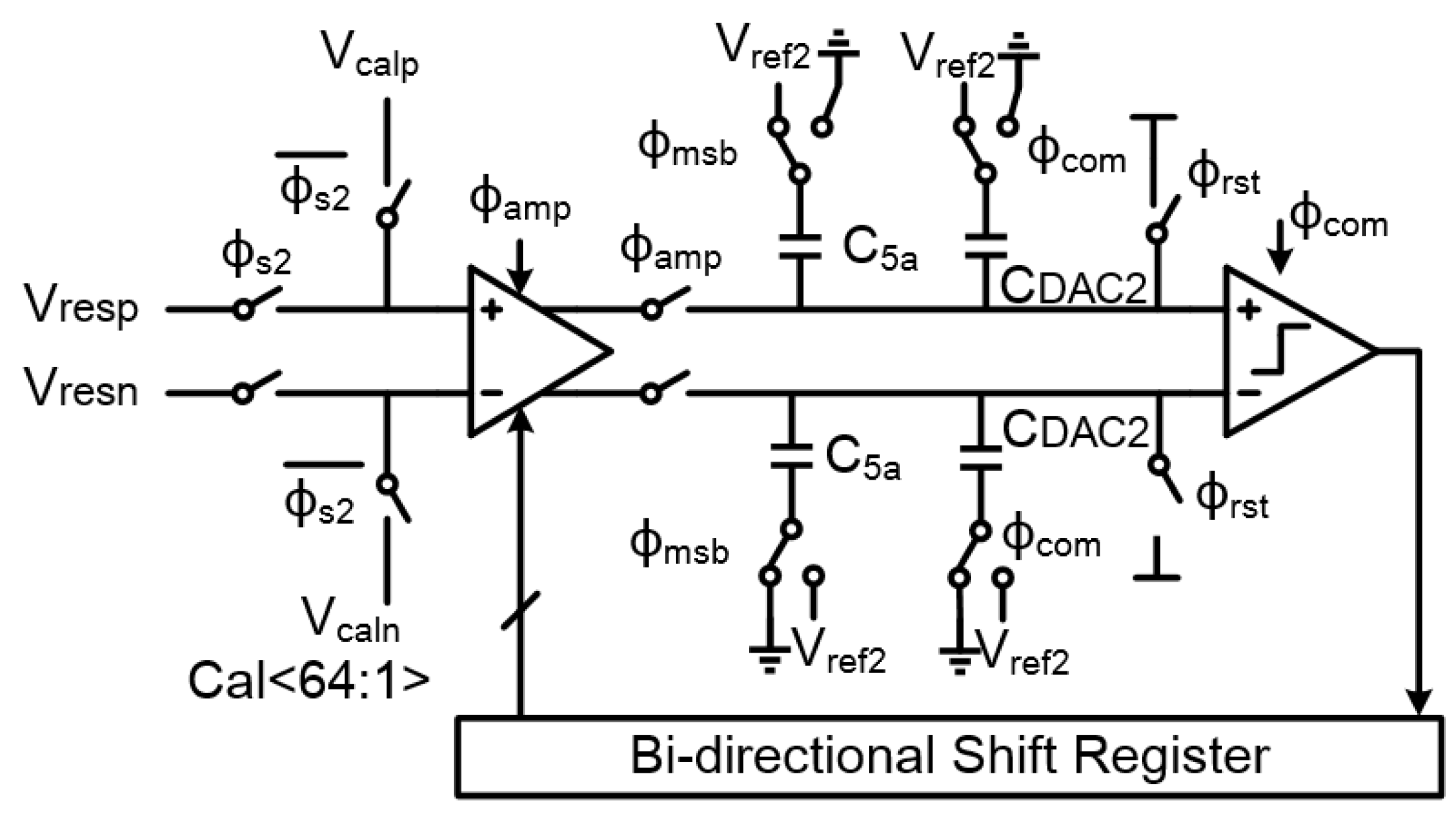

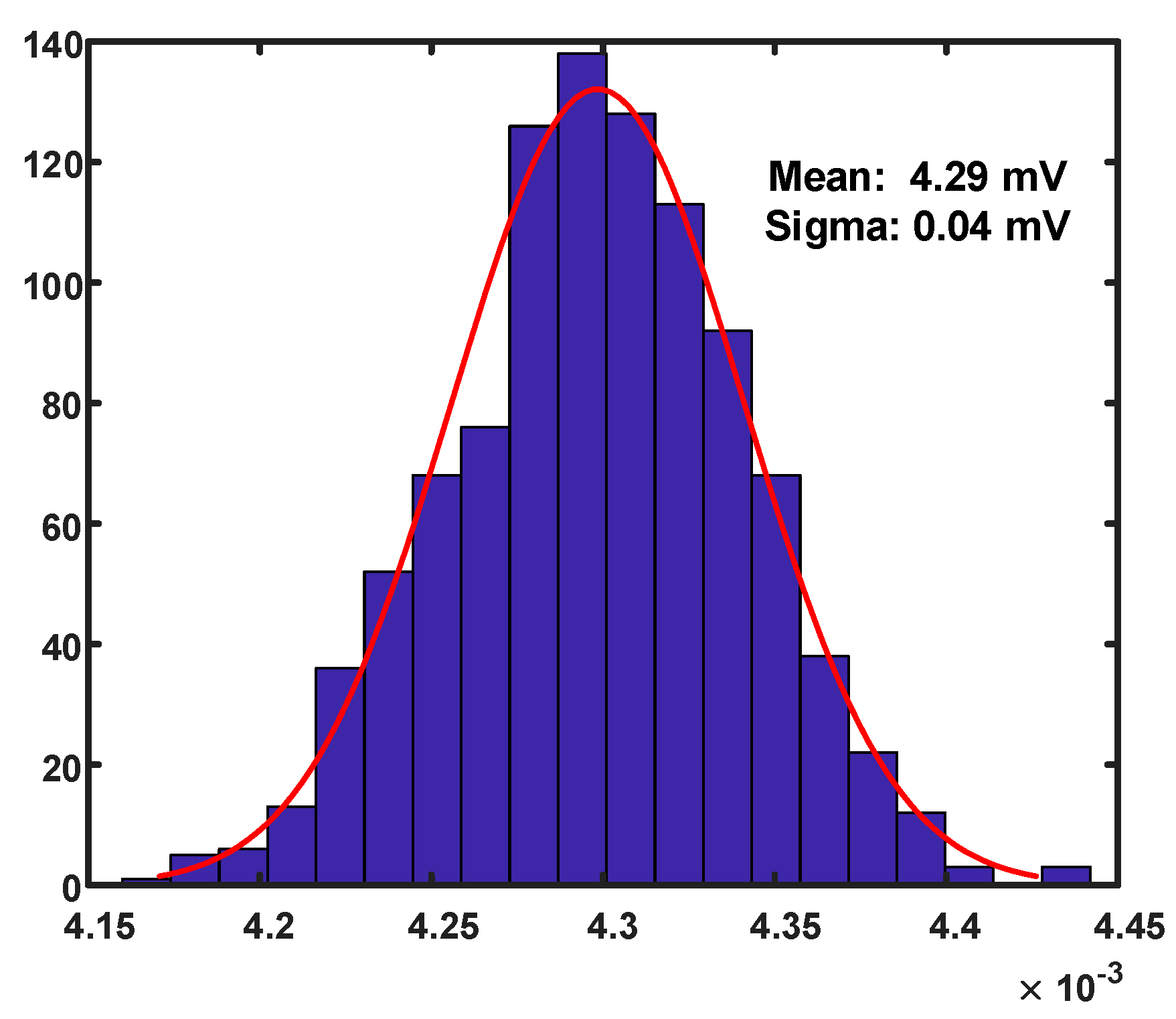

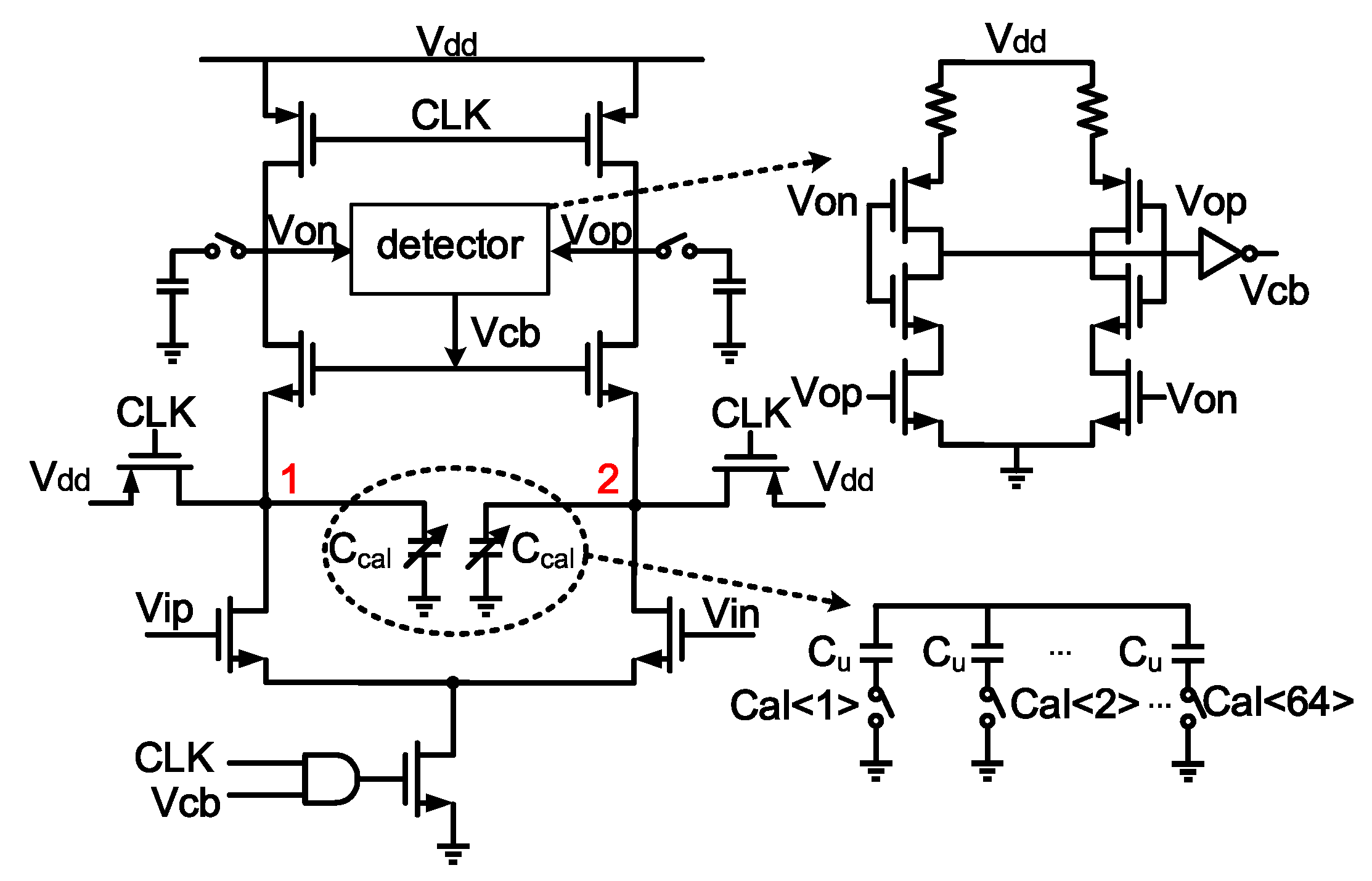

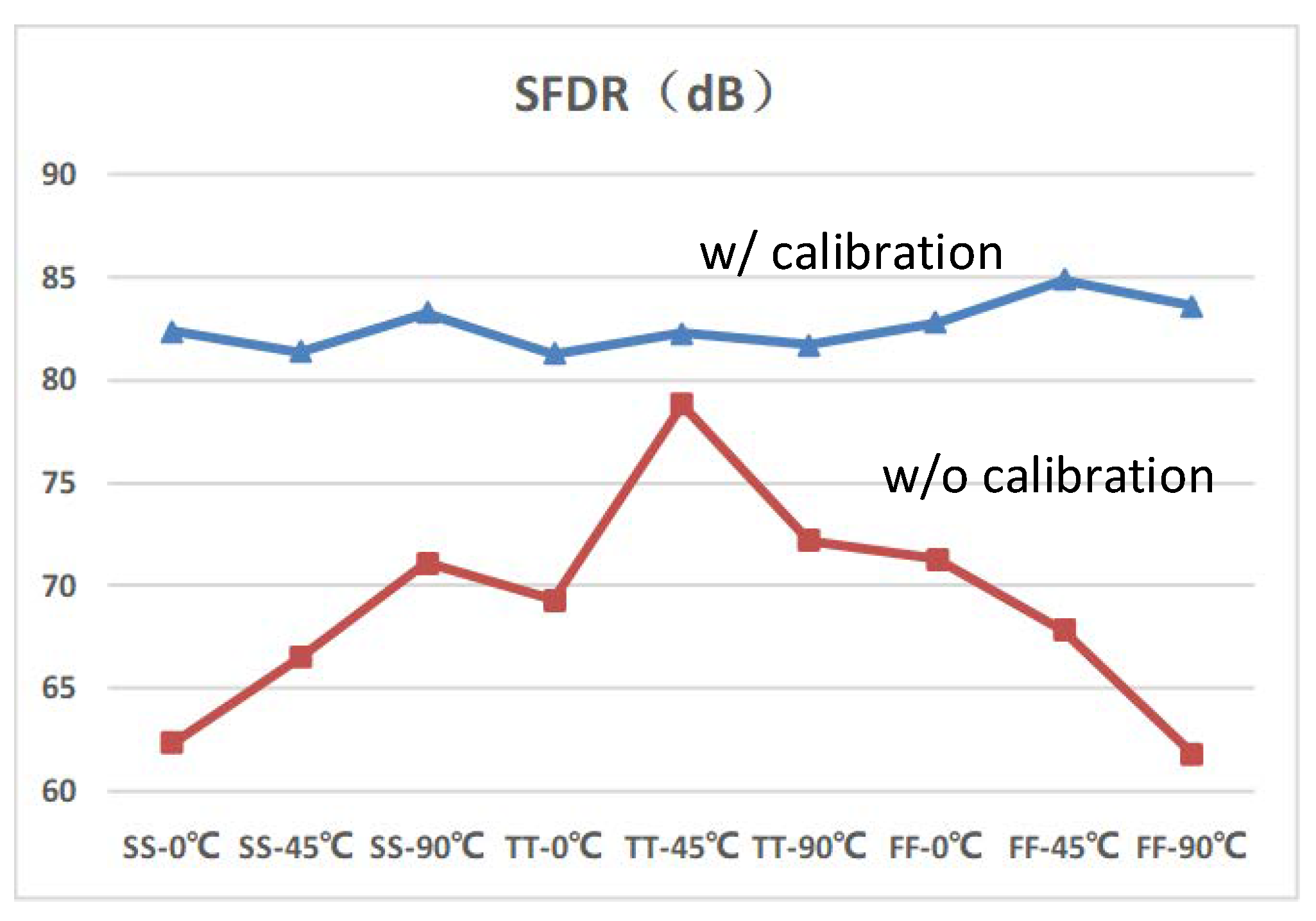

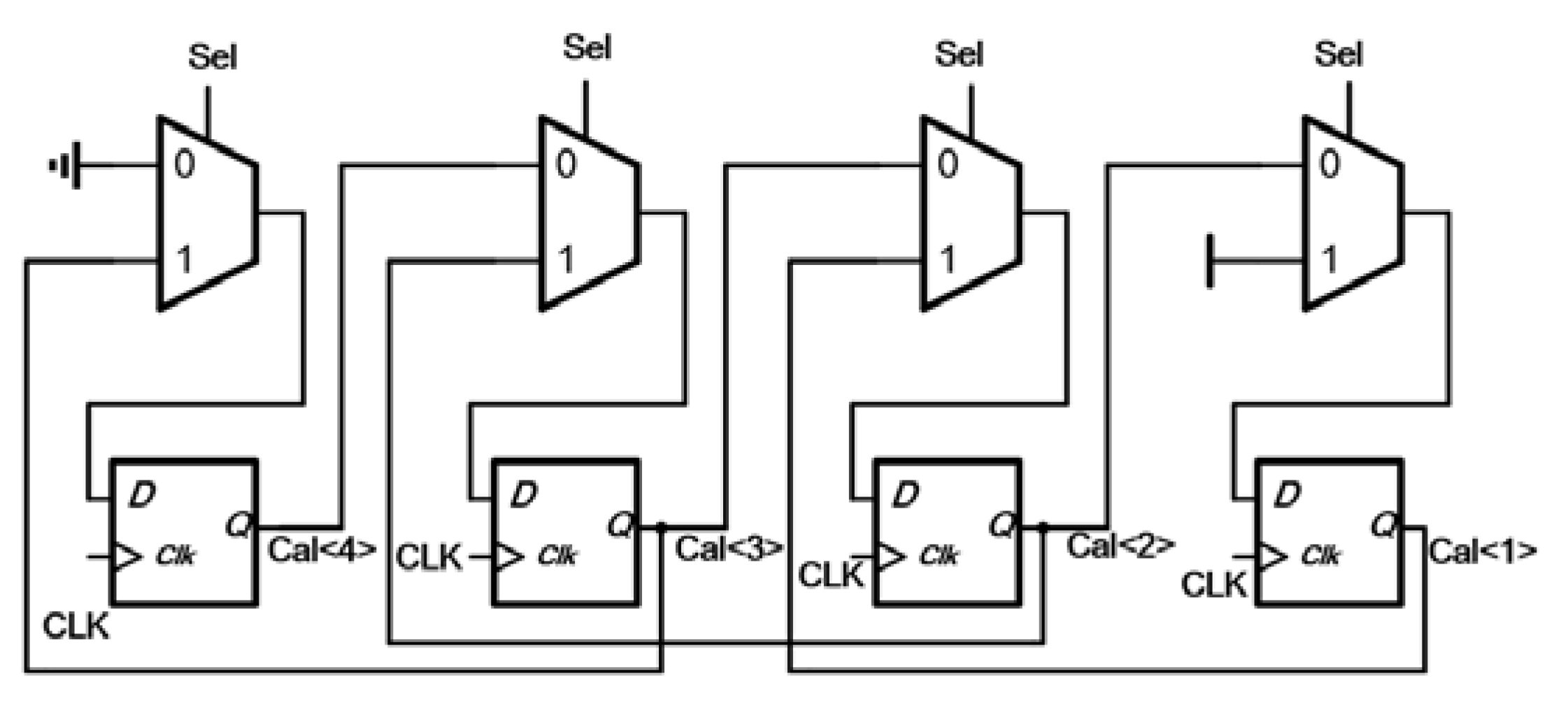

3. Background Calibration of the Inter-Stage Gain

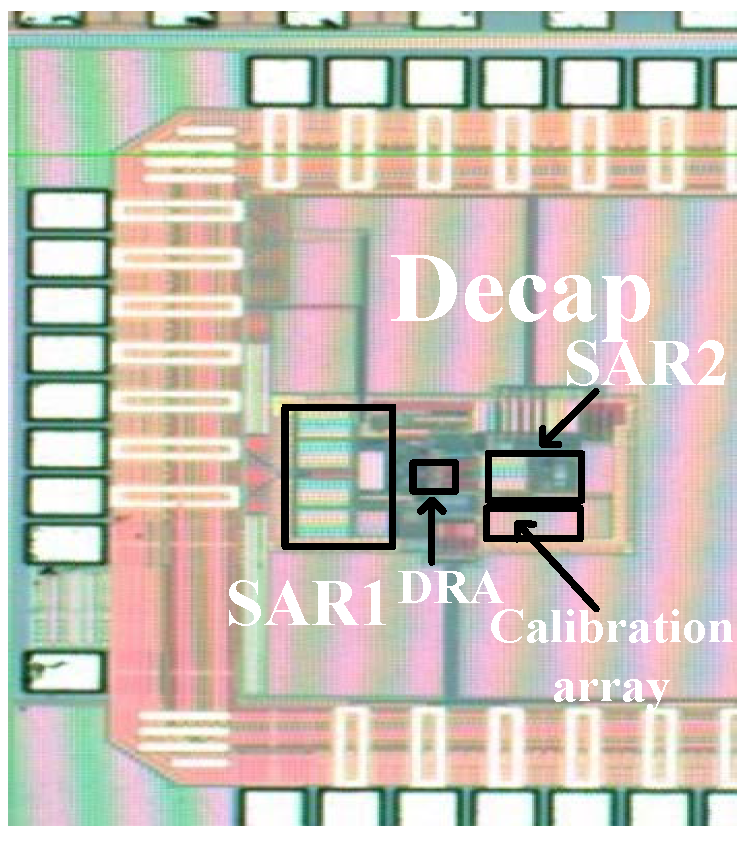

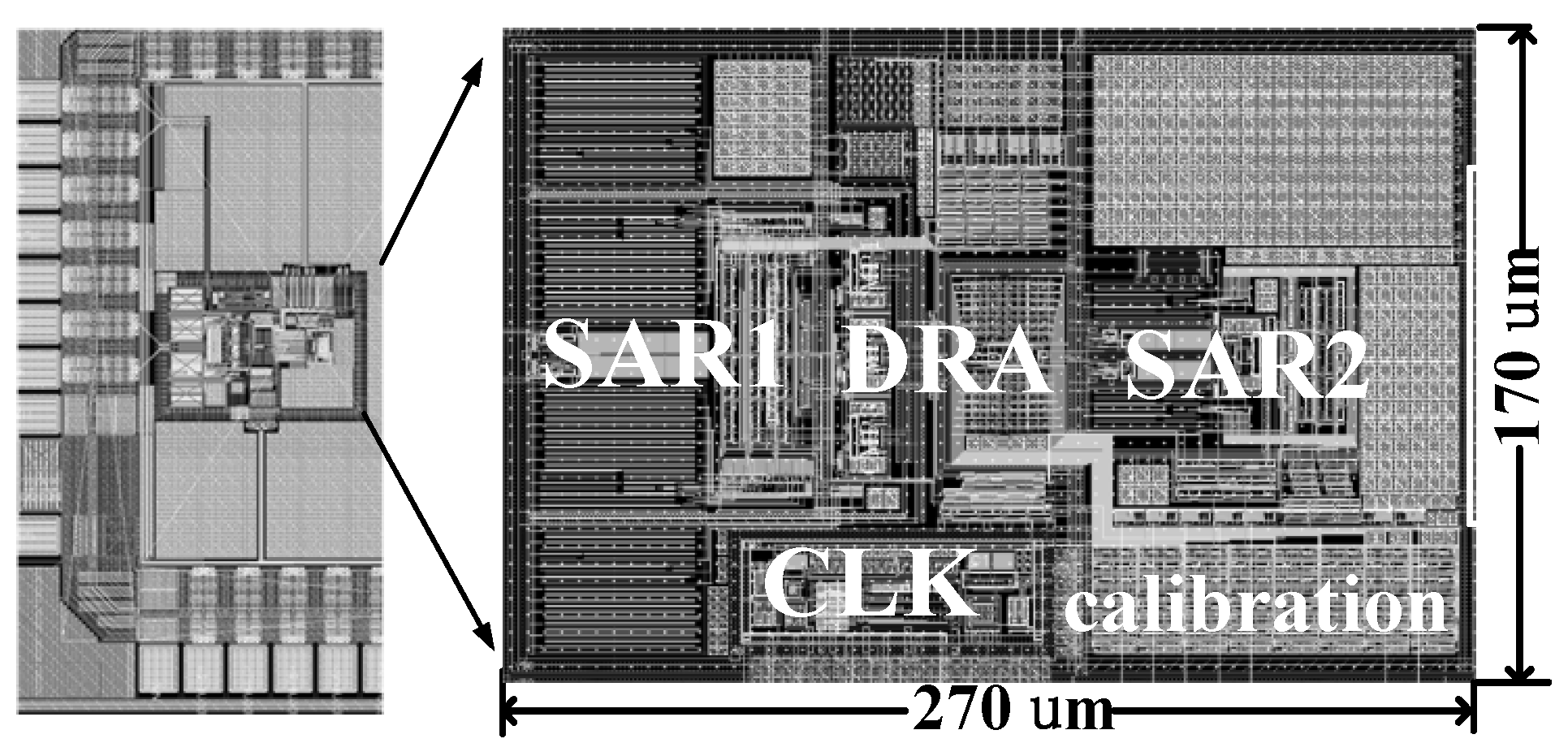

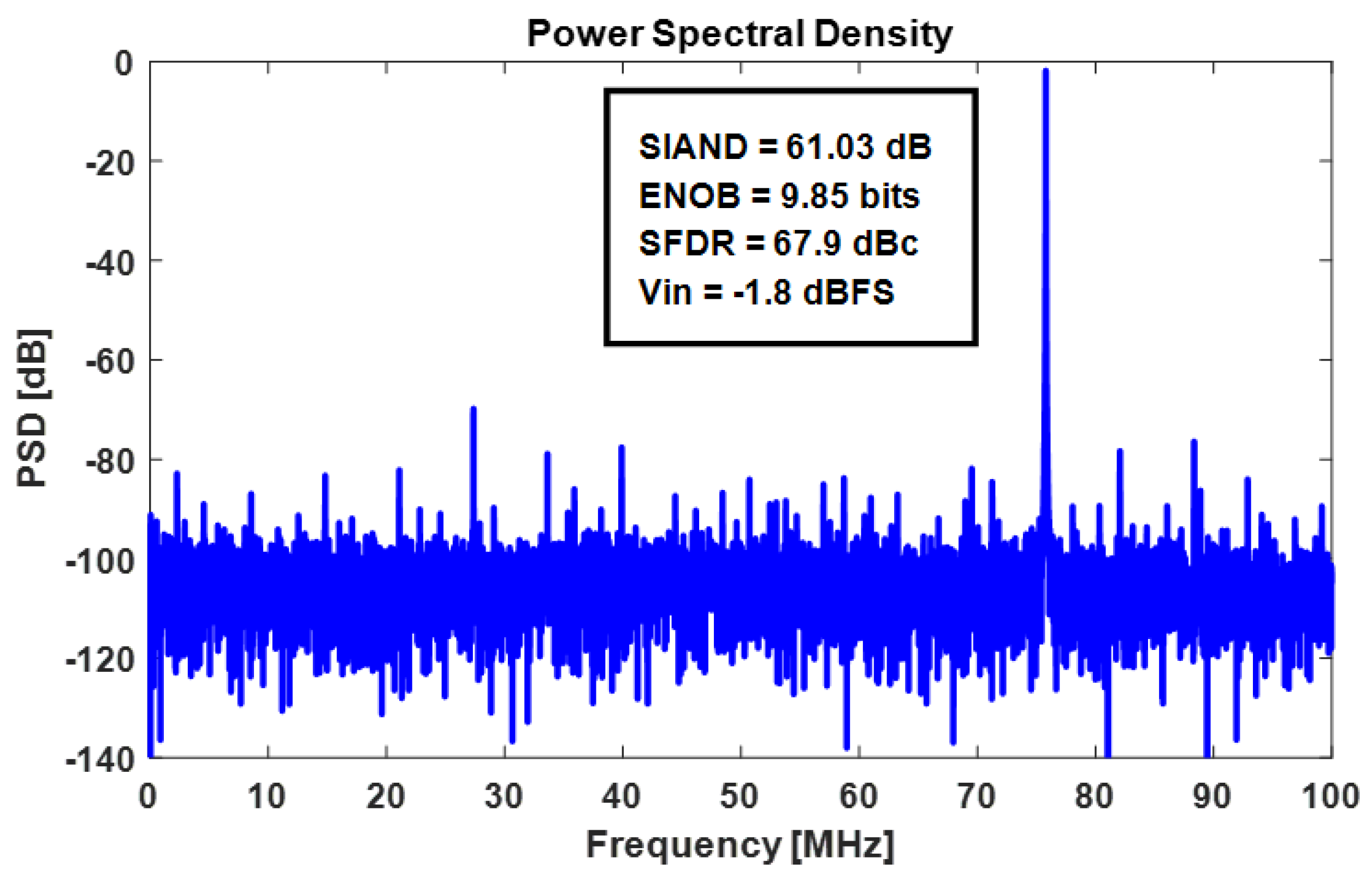

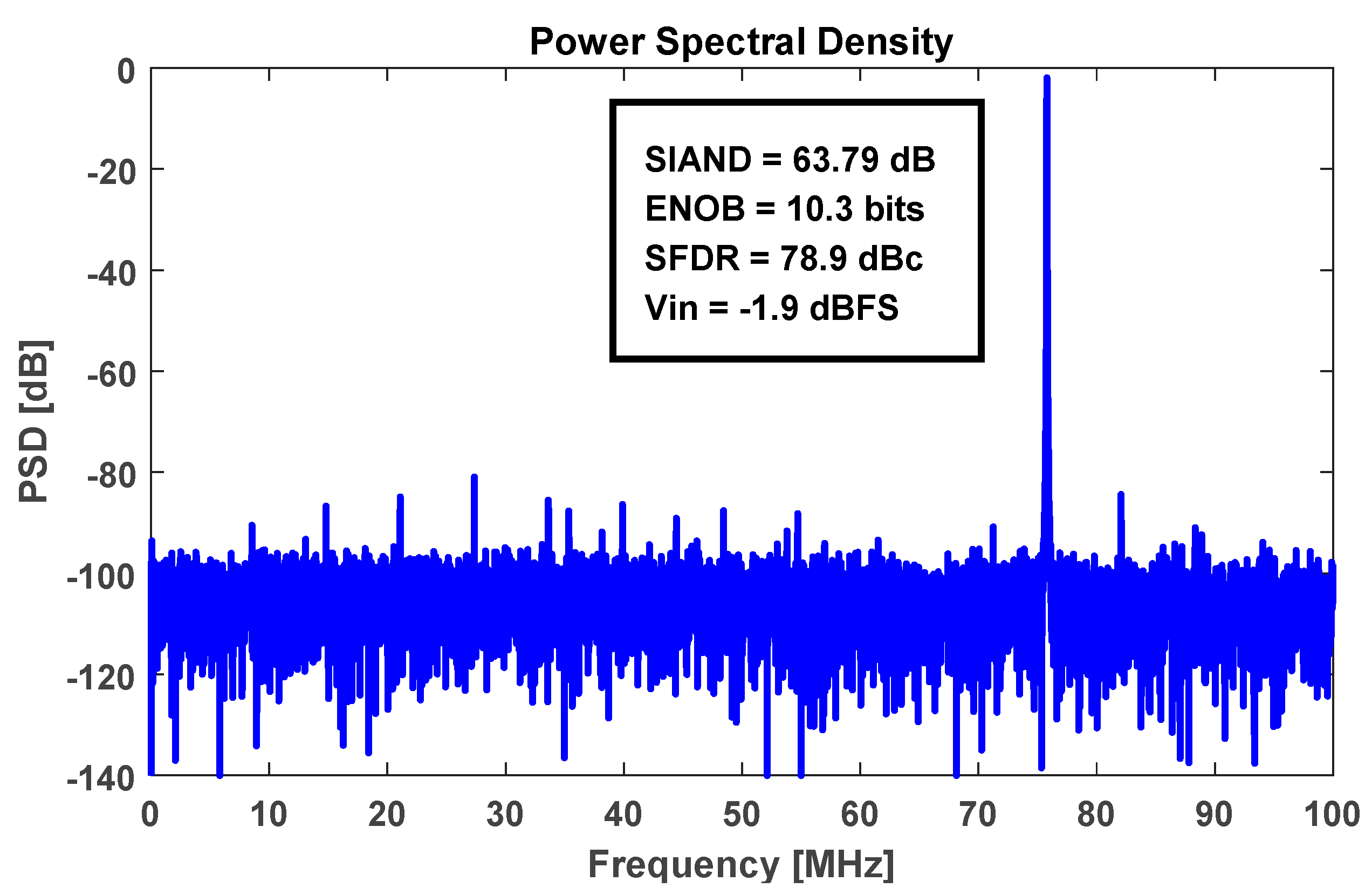

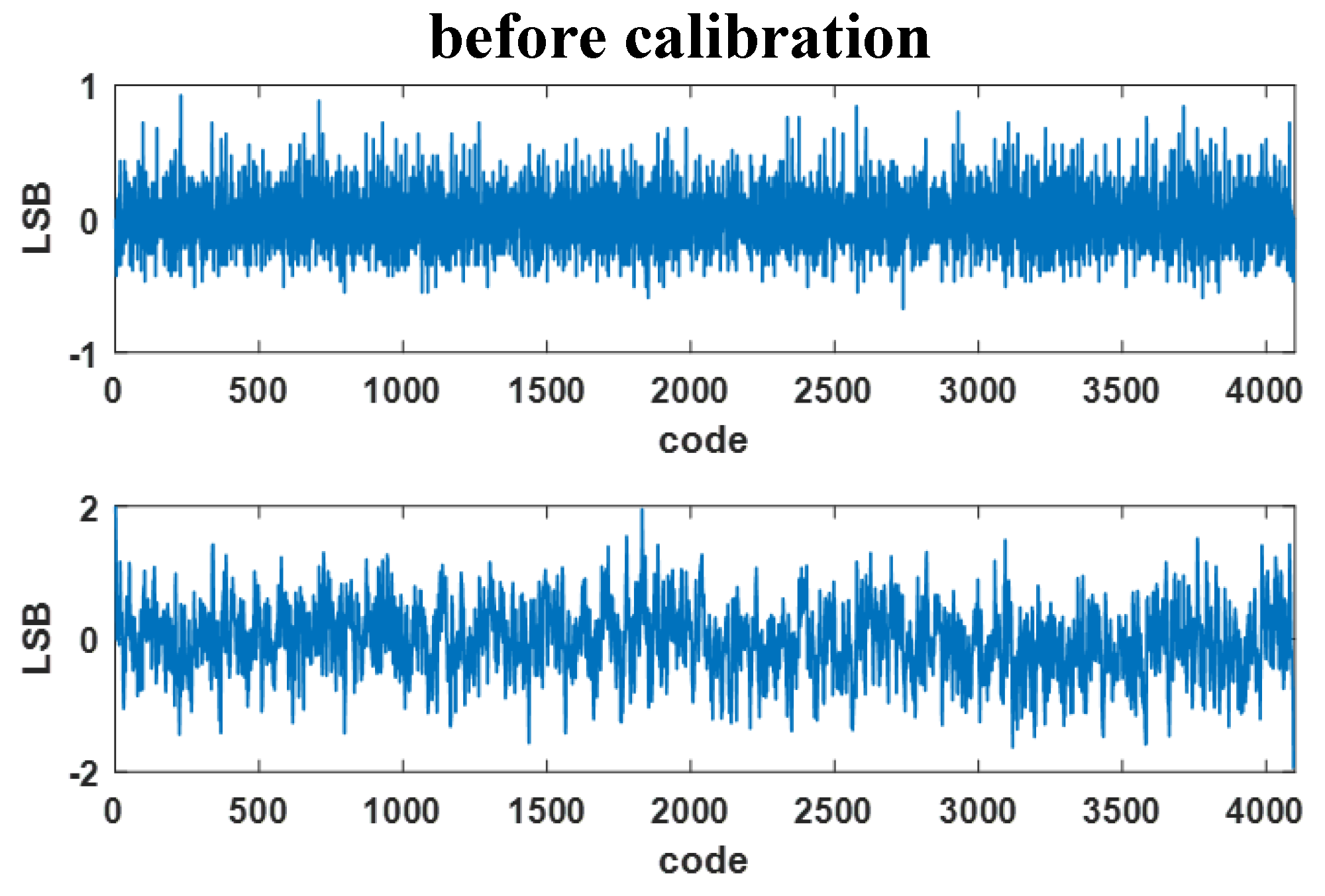

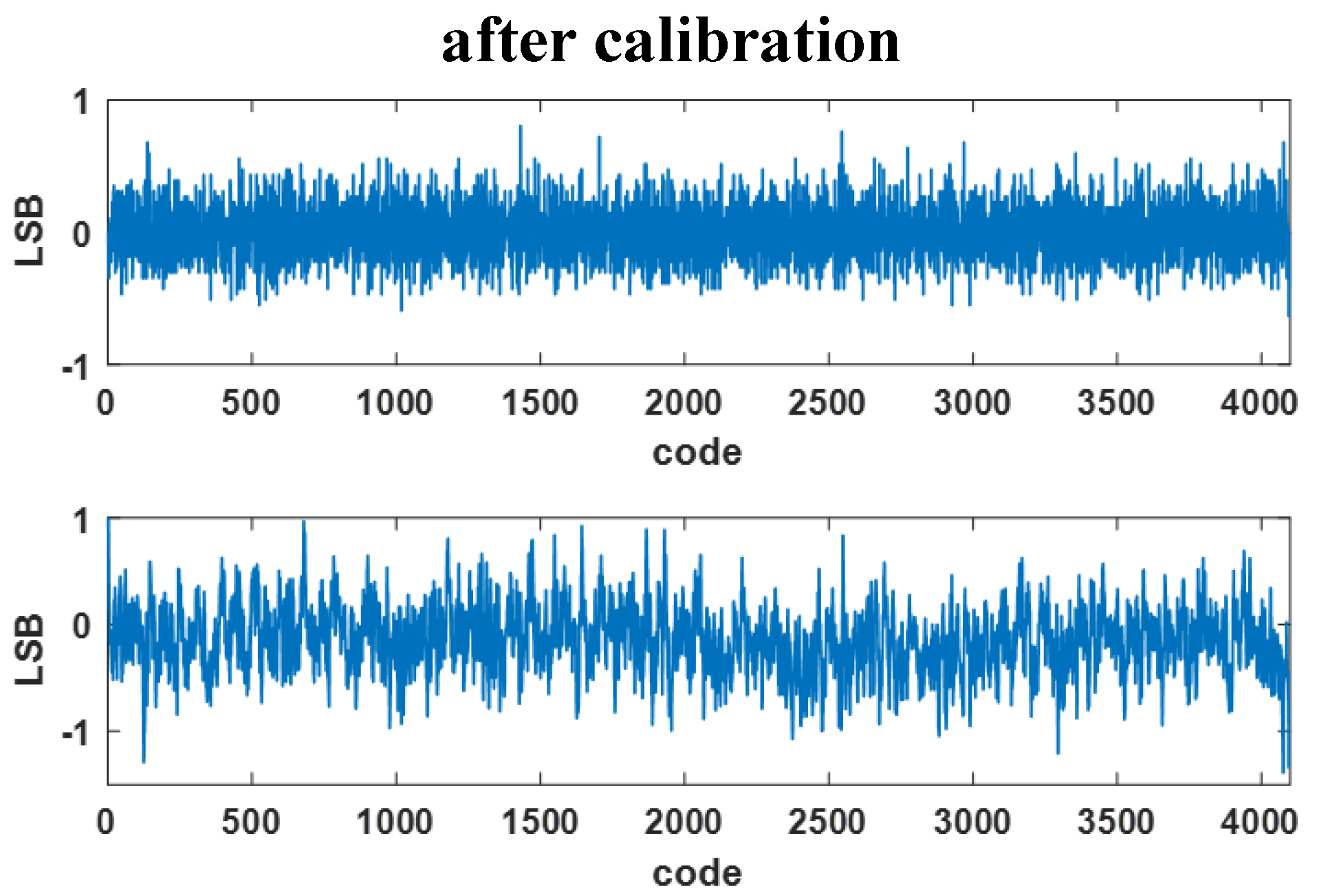

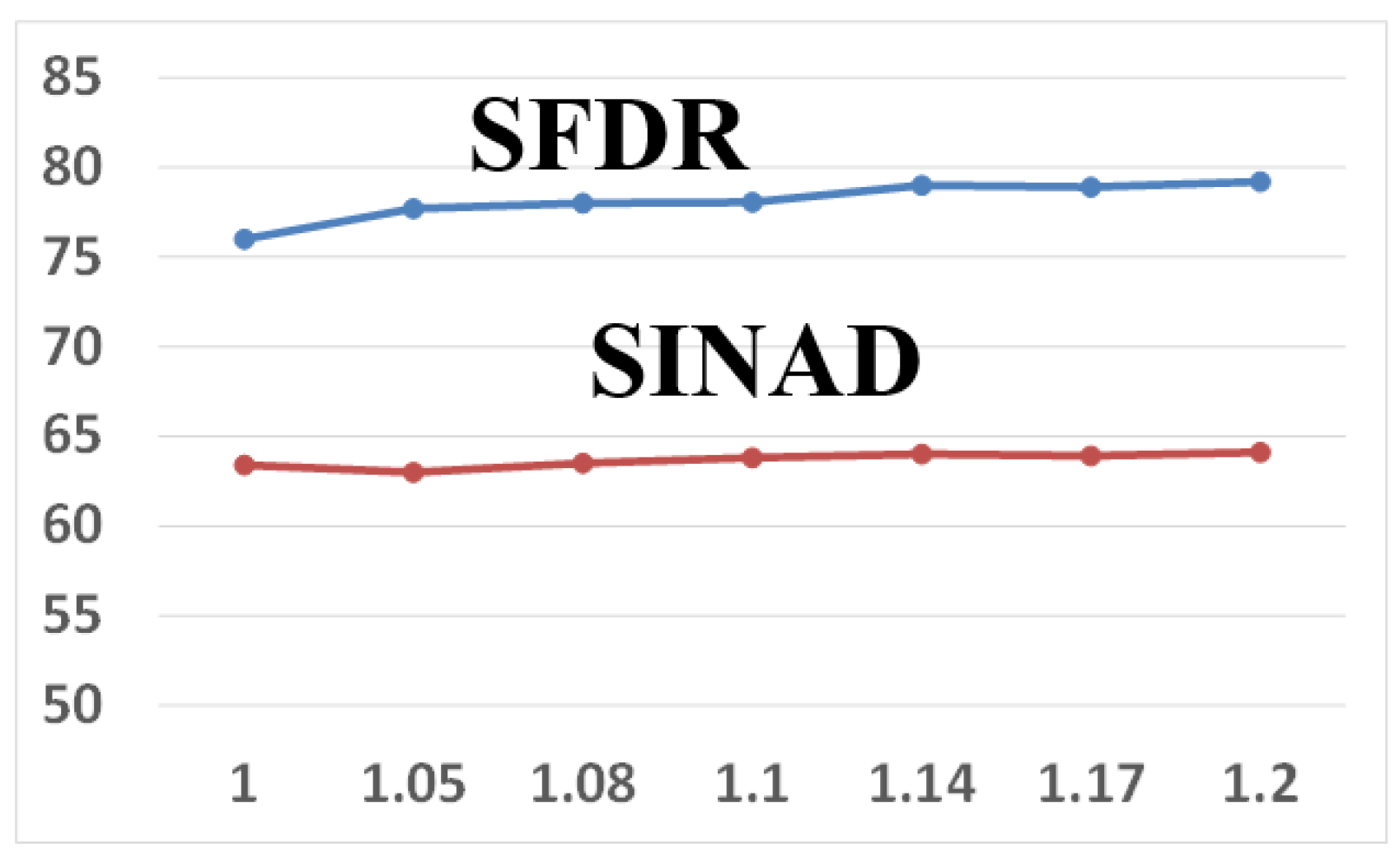

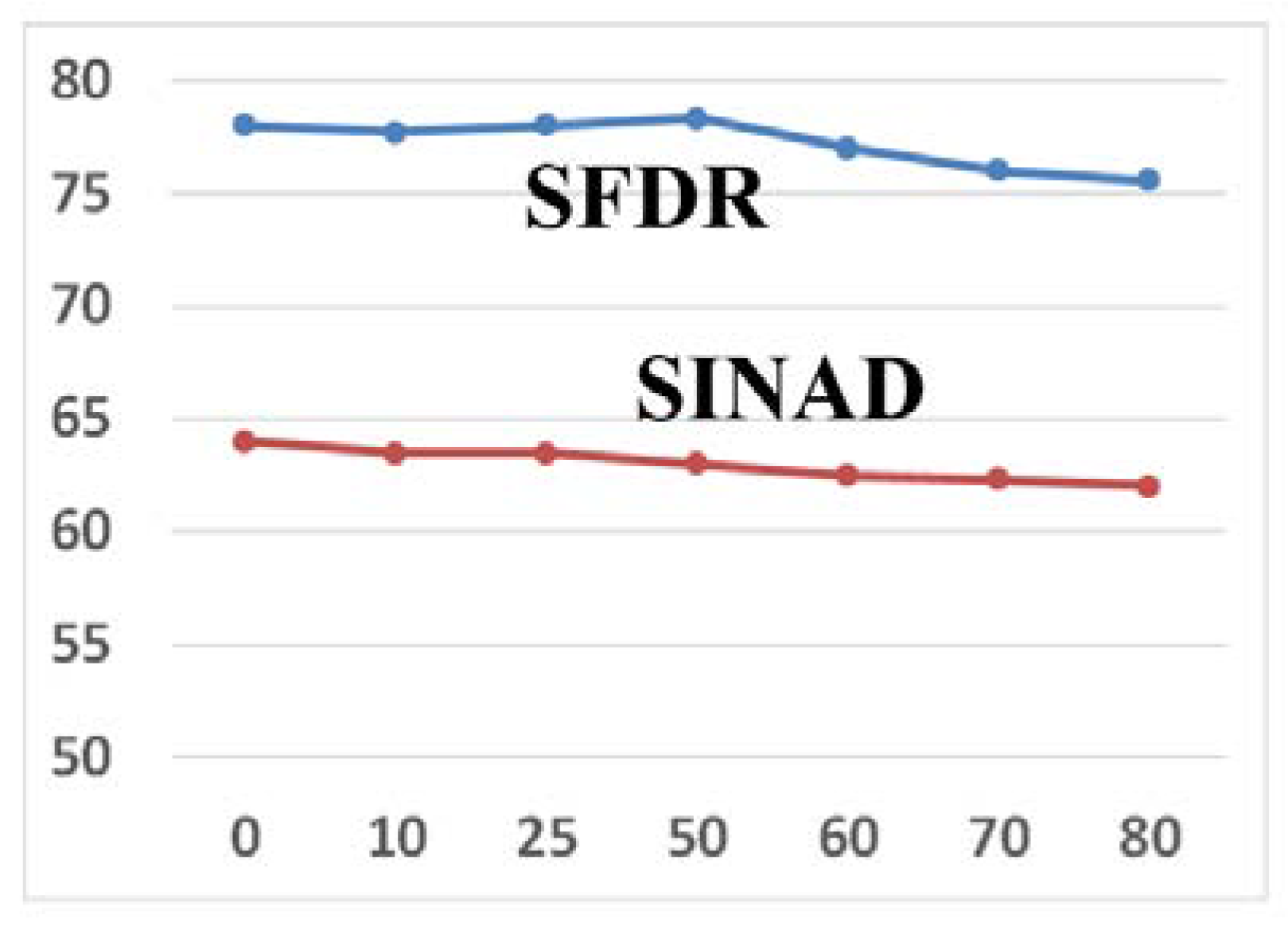

4. Measurement Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kang, H.; Hong, H.; Kim, W.; Ryu, S. A time-interleaved 12-b 270-MS/s SAR ADC with virtual-timing-reference time-skew calibration scheme. IEEE J. Solid-State Circuit 2018, 53, 2584–2594. [Google Scholar] [CrossRef]

- Jun, Y.-H.; Huang, H.-Y.; Lee, S.-Y.; Lai, S.C.; Juang, W.H.; Luo, C.H. A self-testing platform with a foreground digital calibration technique for SAR ADCs. Appl. Sci. 2016, 6, 217. [Google Scholar] [CrossRef]

- Hong, H.; Kim, W.; Kang, H.; Park, S.J.; Choi, M.; Park, H.J.; Ryu, S.T. A decision-error-tolerant 45 nm CMOS 7b 1 GS/s nonbinary 2b/Cycle SAR ADC. IEEE J. Solid-State Circuit 2015, 50, 543–555. [Google Scholar] [CrossRef]

- Chan, C.; Zhu, Y.; Seng, U.; Martins, R.P. A two-way interleaved 7-b 2.4-GS/s 1-then-2 b/Cycle SAR ADC with background offset calibration. IEEE J. Solid-State Circuit 2017, 53, 850–860. [Google Scholar] [CrossRef]

- Furuta, M.; Nozawa, M.; Itakura, T. A 10-bit, 40-MS/s, 1.21 mW pipelined SAR ADC using single-ended 1.5-bit/cycle conversion technique. IEEE J. Solid-State Circuit 2011, 46, 1360–1370. [Google Scholar] [CrossRef]

- Lim, Y.; Flynn, M. A 1 mW 71.5 dB SNDR 50 MS/s 13 bit fully differential ring amplifier based SAR-assisted pipelined ADC. IEEE J. Solid-State Circuit 2015, 50, 2901–2911. [Google Scholar] [CrossRef]

- Martens, E.; Hershberg, B.; Craninckx, J. A 69-dB SNDR 300-MS/s two-time interleaved pipelined SAR ADC in 16-nm CMOS FinFET with capacitive reference stabilization. IEEE J. Solid-State Circuit 2018, 53, 1161–1171. [Google Scholar] [CrossRef]

- Brandolini, M.; Shin, Y.; Raviprakash, K.; Wang, T.; Wu, R.; Geddada, H.M.; Ko, Y.J.; Ding, Y.; Huang, C.S.; Shih, W.T.; et al. A 5 GS/s 150 mW 10b SHA-Less pipelined/SAR hybrid ADC for direct-sampling systems in 28 nm CMOS. IEEE J. Solid-State Circuit 2015, 50, 2922–2934. [Google Scholar] [CrossRef]

- Zhu, Y.; Chan, C.; Seng, U.; Martins, R.P. A 10-bit 500-MS/s partial-interleaving pipelined SAR ADC with offset and reference mismatch calibrations. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2017, 25, 354–363. [Google Scholar] [CrossRef]

- Zhu, Y.; Chan, C.; Seng, U.; Martins, R.P. An 11b 450 MS/s three-way time-interleaved subranging pipelined-SAR ADC in 65 nm CMOS. IEEE J. Solid-State Circuit 2016, 51, 1223–1234. [Google Scholar] [CrossRef]

- Lin, C.; Lee, T. A 12-bit 210-MS/s 2-times interleaved pipelined-SAR ADC with a passive residue transfer technique. IEEE Trans. Circuits Syst. I Reg. Pap. 2016, 63, 929–938. [Google Scholar] [CrossRef]

- Yoshioka, K.; Sugimoto, T.; Waki, N.; Kim, S.; Kurose, D.; Ishii, H.; Furuta, M.; Sai, A.; Itakura, T. A 0.7V 12b 160 MS/s 12.8 fJ/conv-step pipelined-SAR ADC in 28 nm CMOS with digital amplifier technique. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017. [Google Scholar]

- Kull, L.; Luu, D.; Menolfi, C.; Braendli, M.; Francese, P.A.; Morf, T.; Kossel, M.; Yueksel, H.; Cevrero, A.; Ozkaya, I.; et al. A 10b 1.5GS/s pipelined-SAR ADC with background second-stage common-mode regulation and offset calibration in 14 nm CMOS FinFET. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017. [Google Scholar]

- Xu, H.; Cai, Y.; Du, L. A 78.5dB-SNDR radiation-and metastability-tolerant two-step split SAR ADC operating up to 75 MS/s with 24.9 mW power consumption in 65 nm CMOS. In Proceedings of the 2017 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017. [Google Scholar]

- Verbruggen, B.; Iriguchi, M.; Craninckx, J. A 1.7 mW 11b 250 MS/s 2-times interleaved fully dynamic pipelined SAR ADC in 40 nm digital CMOS. IEEE J. Solid-State Circuit 2011, 47, 2880–2887. [Google Scholar] [CrossRef]

- Goes, F.; Ward, C.; Astgimath, S.; Yan, H.; Riley, J.; Zeng, Z.; Jan, M.; Wang, S.; Bult, K. A 1.5 mW 68 dB SNDR 80 MS/s 2×Interleaved pipelined SAR ADC in 28 nm CMOS. IEEE J. Solid-State Circuit 2014, 49, 2835–2845. [Google Scholar] [CrossRef]

- Huang, H.; Xu, H.; Chiu, Y. A non-interleaved 12-b 330-MS/s pipelined-SAR ADC with PVT-Stabilized dynamic amplifier achieving sub-1-dB SNDR variation. IEEE J. Solid-State Circuit 2017, 52, 3235–3247. [Google Scholar] [CrossRef]

- Zhang, M.; Liu, Q.; Fan, X. Gain-boosted dynamic amplifier for pipelined-SAR ADCs. Electron. Lett. 2017, 53, 708–709. [Google Scholar] [CrossRef]

- Zhou, Y.; Xu, B.; Chiu, Y. A 12 bit 160 MS/s two-step SAR ADC with background bit-weight calibration using a time-domain proximity detector. IEEE J. Solid-State Circuit 2015, 50, 920–931. [Google Scholar] [CrossRef]

- Zhong, J.; Zhu, Y.; Chan, C. A 12b 180 MS/s 0.068mm2 with full-calibration-integrated pipelined-SAR ADC. IEEE Trans. Circuits Syst. I Reg. Pap. 2017, 64, 1684–1695. [Google Scholar] [CrossRef]

- Ginsburg, B.; Chandrakasan, A. An energy-efficient charge recycling approach for a SAR converter with capacitive DAC. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS2005), Kobe, Japan, 23–26 May 2005. [Google Scholar]

| [7] | [9] | [20] | This Work | |

|---|---|---|---|---|

| Process (nm) | 65 | 40 | 65 | 40 |

| Supply (V) | 1.2 | 1.8 | 1.2 | 1.1 |

| Resolution (bits) | 12 | 12 | 12 | 12 |

| Power (mW) | 6.23 | 4.96 | 6 | 8 |

| Sampling rate (MHz) | 330 | 160 | 180 | 200 |

| SFDR (dB) | 83.4 | 86.9 | 76 | 78.9 |

| SINAD (dB) | 63.5 | 65.3 | 63 | 63.7 |

| Process-voltage-temperature stable | Yes | Yes | No | Yes |

| Area (mm2) | 0.08 | 0.042 | 0.068 | 0.0459 |

| Figure of merit (fj/conv-step) | 15.4 | 20.6 | 36.7 | 31.7 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, J.; Wu, J. A 12-Bit 200 MS/s Pipelined-SAR ADC Using Back-Ground Calibration for Inter-Stage Gain. Electronics 2020, 9, 507. https://doi.org/10.3390/electronics9030507

Wu J, Wu J. A 12-Bit 200 MS/s Pipelined-SAR ADC Using Back-Ground Calibration for Inter-Stage Gain. Electronics. 2020; 9(3):507. https://doi.org/10.3390/electronics9030507

Chicago/Turabian StyleWu, Junjie, and Jianhui Wu. 2020. "A 12-Bit 200 MS/s Pipelined-SAR ADC Using Back-Ground Calibration for Inter-Stage Gain" Electronics 9, no. 3: 507. https://doi.org/10.3390/electronics9030507

APA StyleWu, J., & Wu, J. (2020). A 12-Bit 200 MS/s Pipelined-SAR ADC Using Back-Ground Calibration for Inter-Stage Gain. Electronics, 9(3), 507. https://doi.org/10.3390/electronics9030507