Enhance Reliability of Semiconductor Devices in Power Converters

Abstract

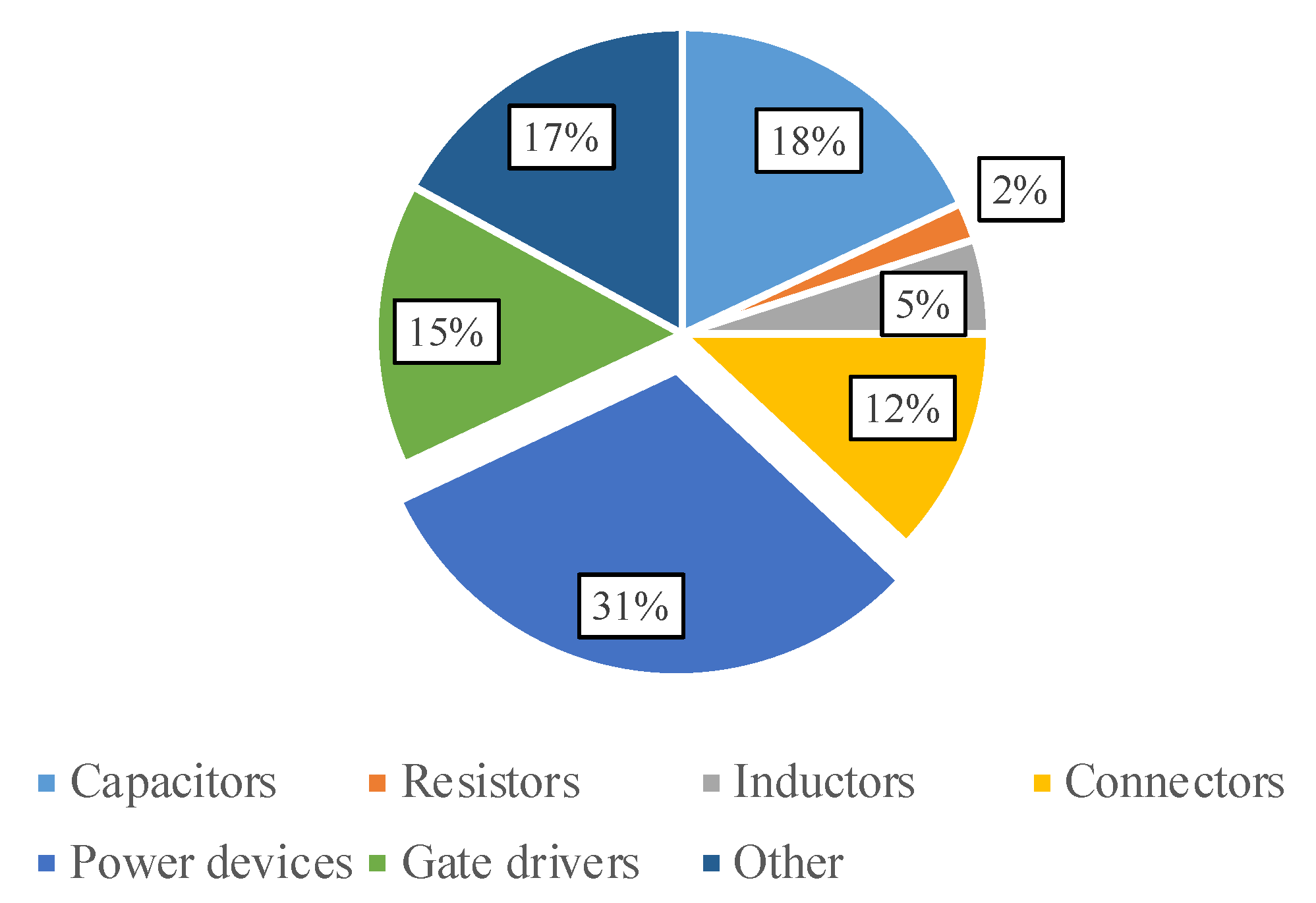

1. Introduction

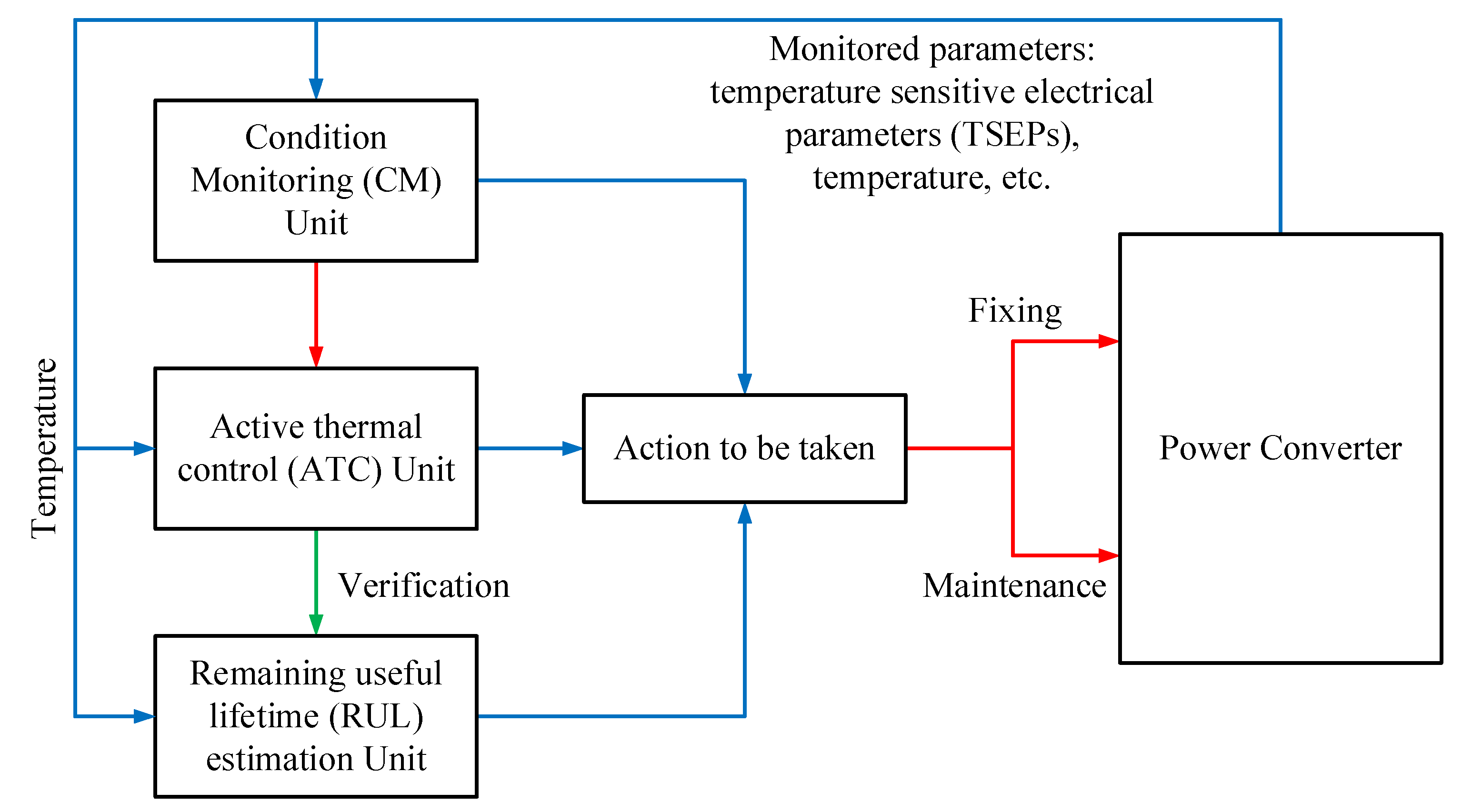

2. Condition Monitoring Techniques

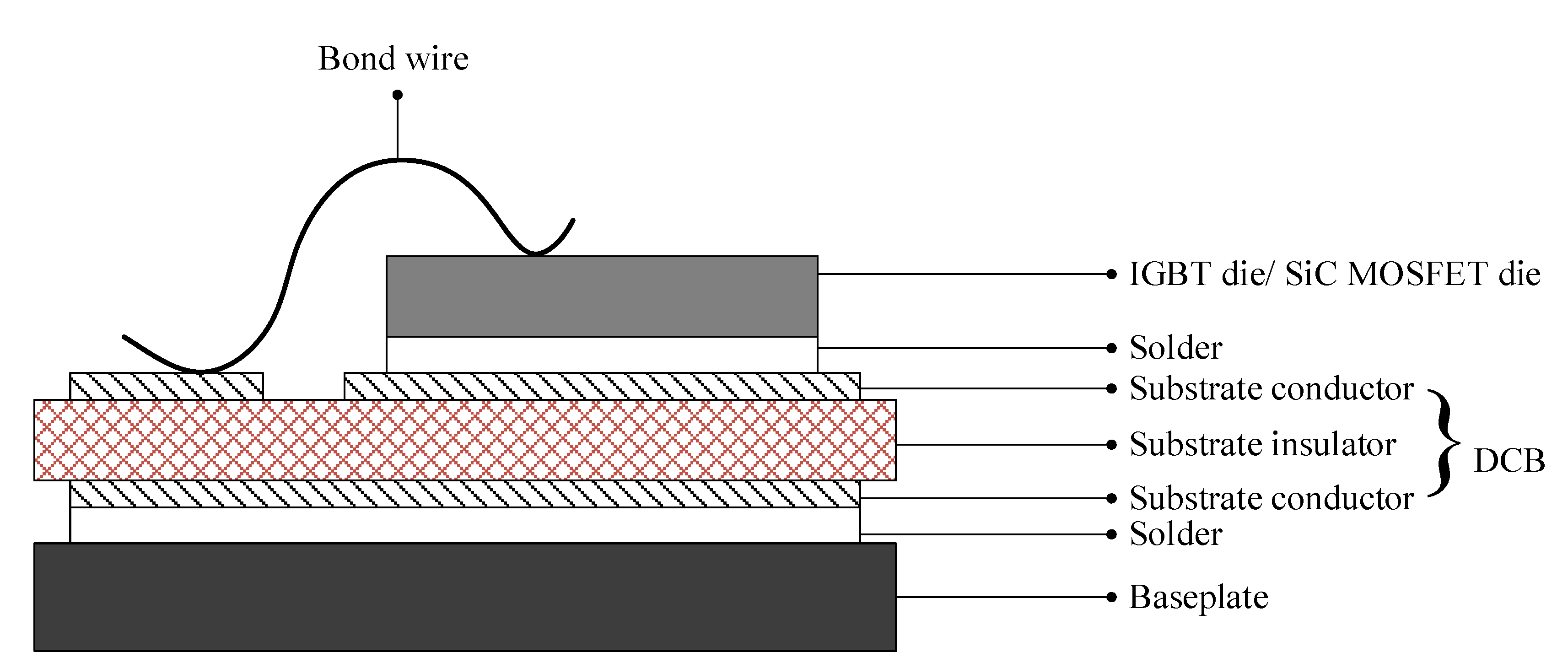

2.1. Failure Mechanism and Indicators

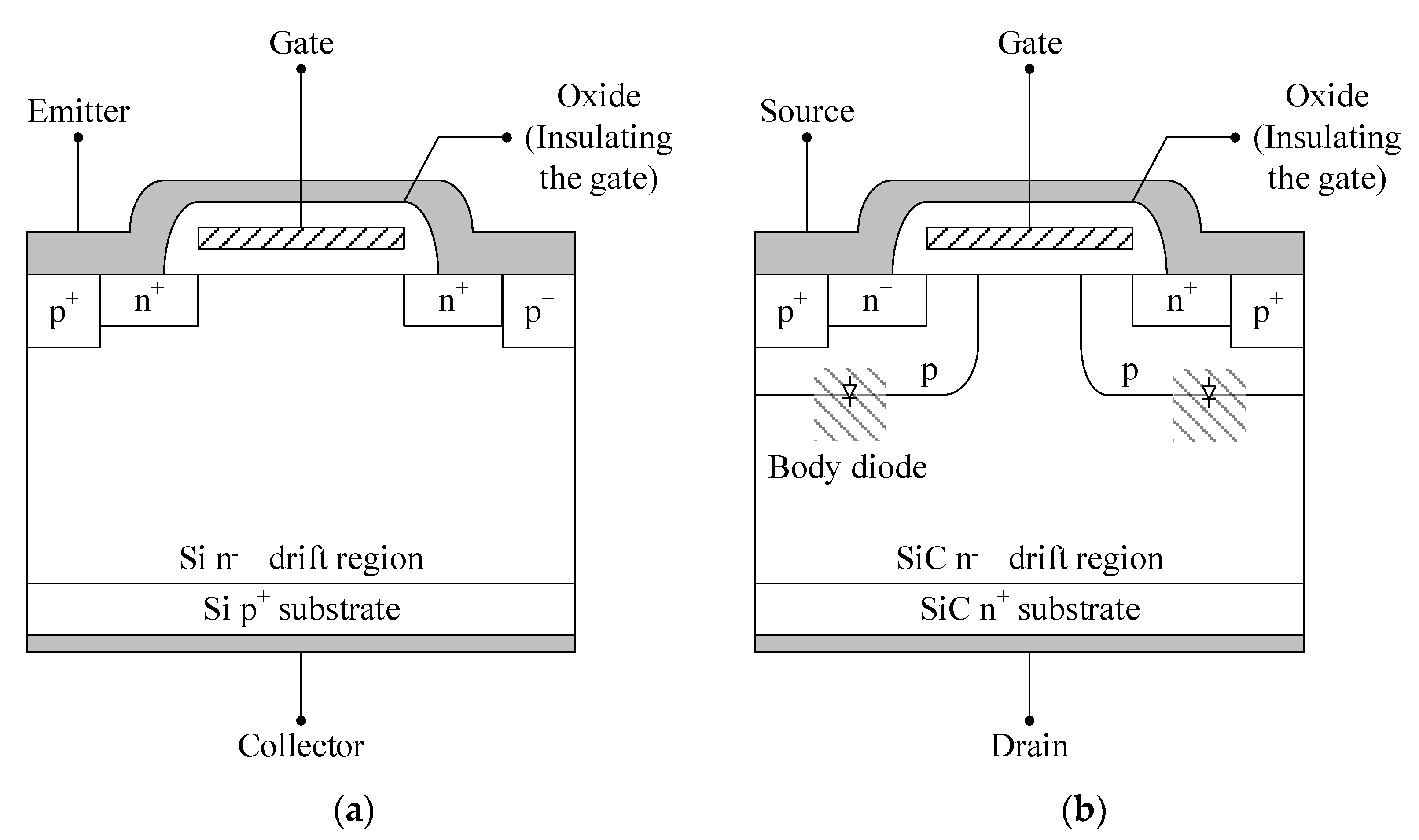

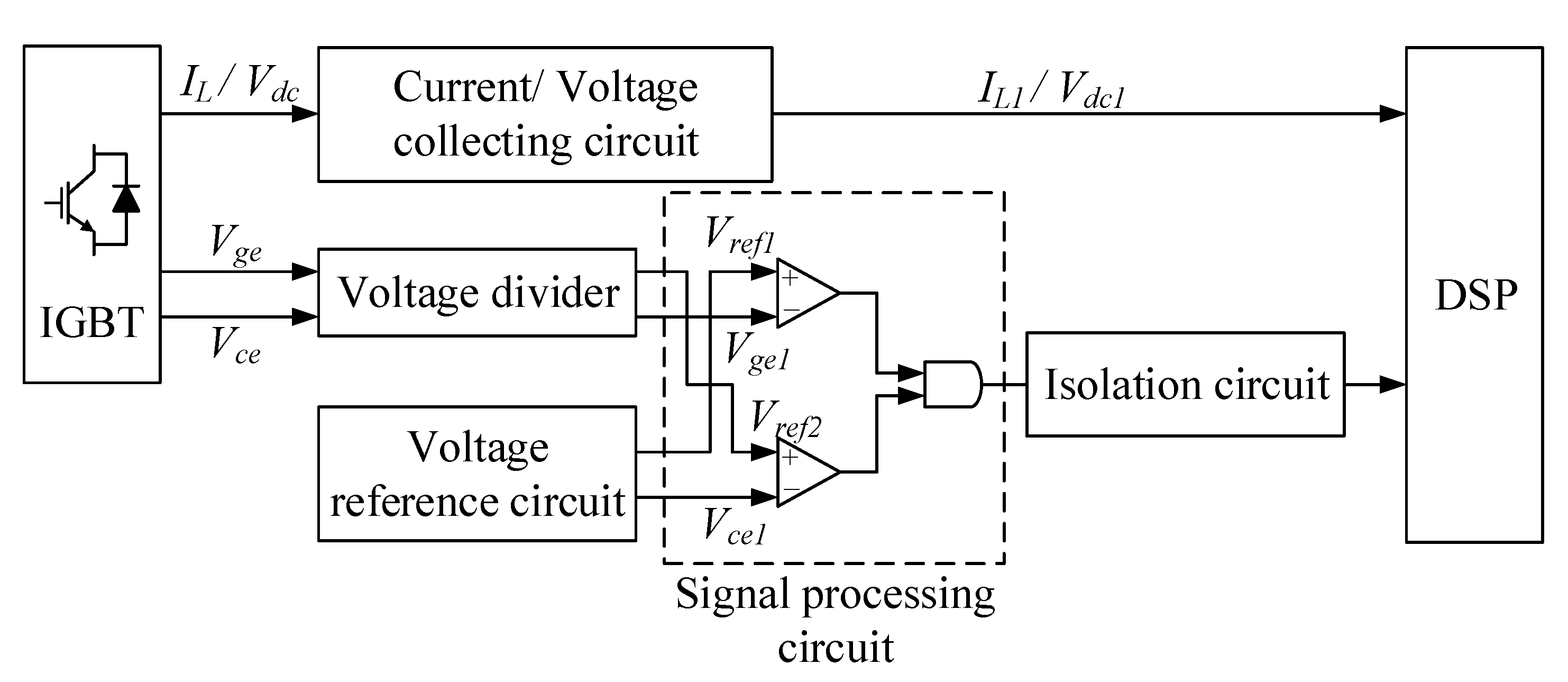

2.2. CM for IGBT

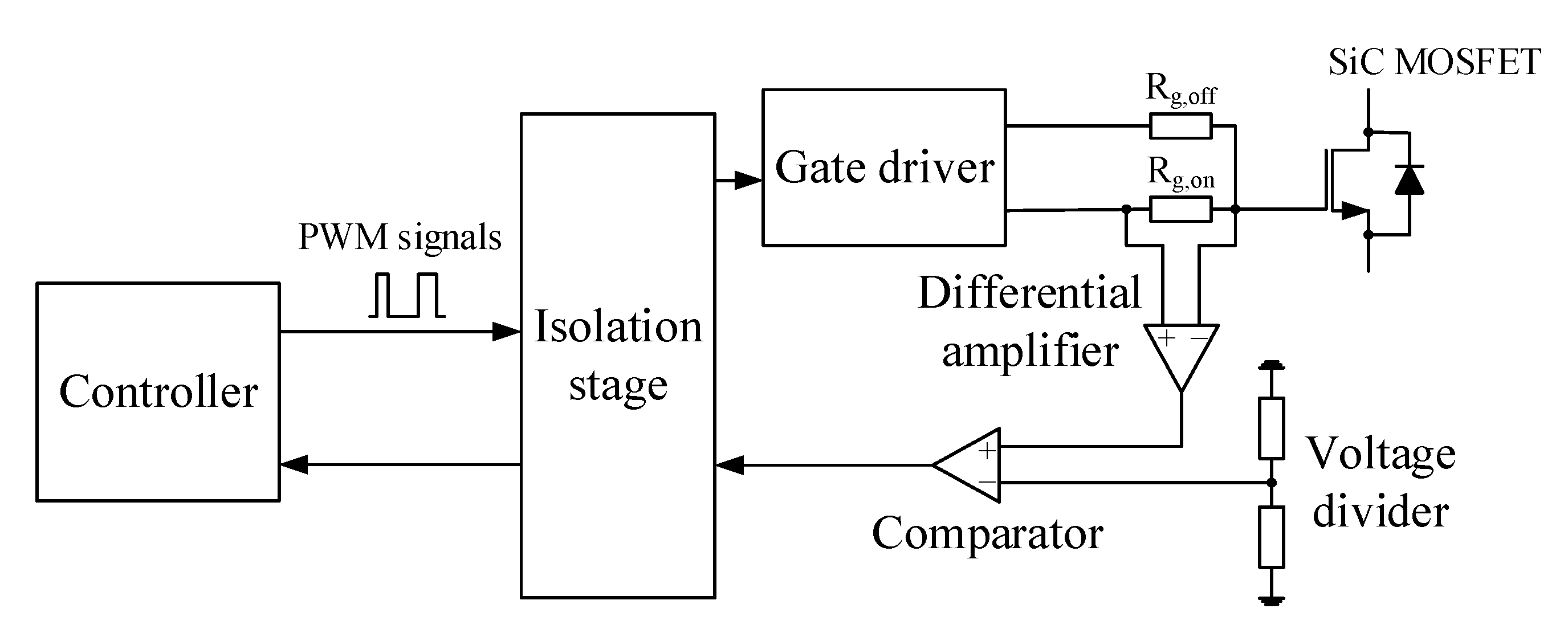

2.2.1. Monitoring Collector-Emitter on-State Voltage

2.2.2. Monitoring Miller Plateau Time Duration

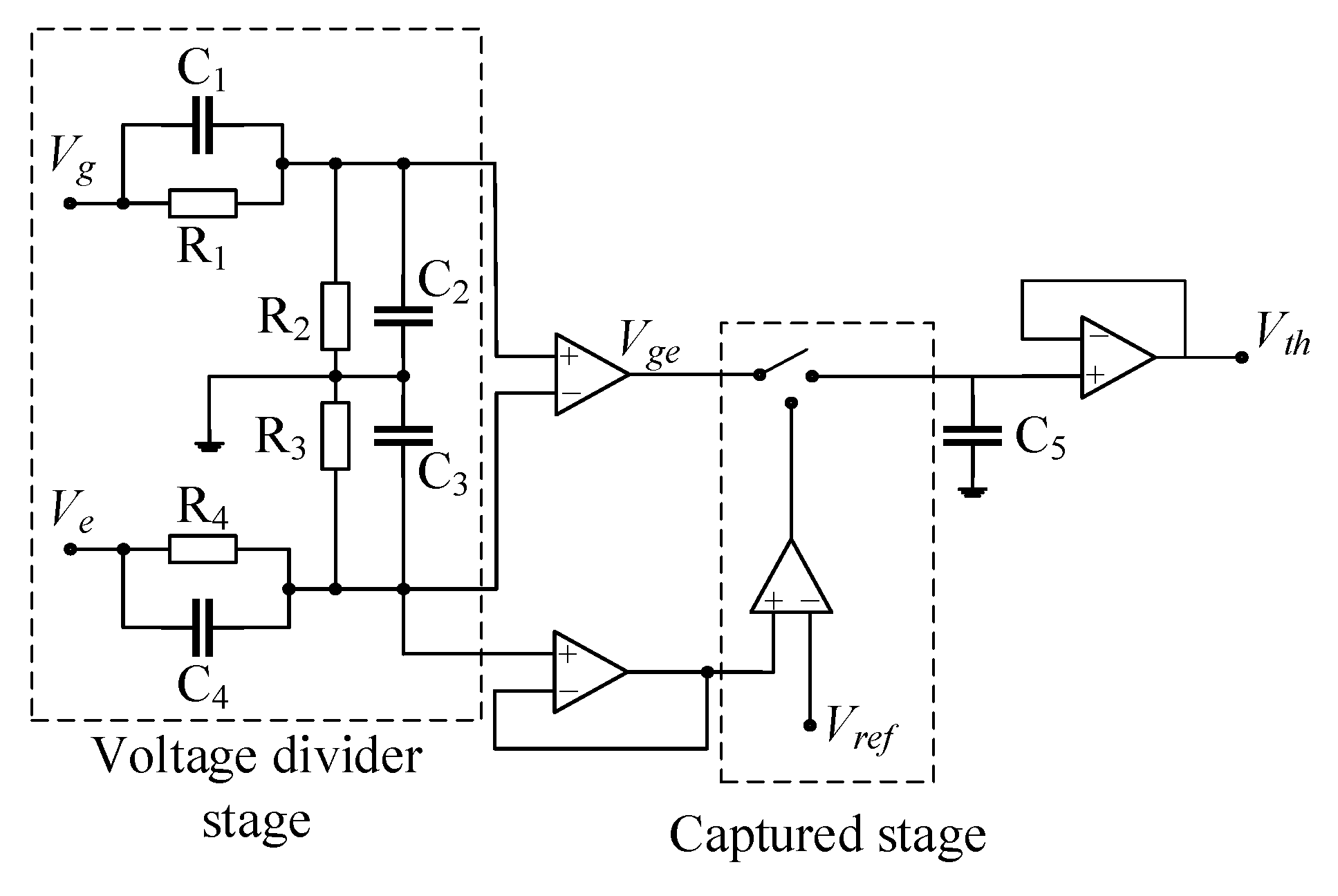

2.2.3. Monitoring Threshold Voltage

2.2.4. Monitoring Junction Temperature and Thermal Resistance

- Calculate the junction temperature using the on-state collector-emitter voltage at a high current.

- Calculate the junction temperature using the on-state collector-emitter voltage at a low current.

- Calculate the junction temperature using the gate internal resistance.

- Calculate the junction temperature using short-circuit current.

- Calculate the junction temperature using the threshold voltage.

- Calculate the junction temperature using Miller plateau voltage.

- Calculate the junction temperature using turn on/off delay time.

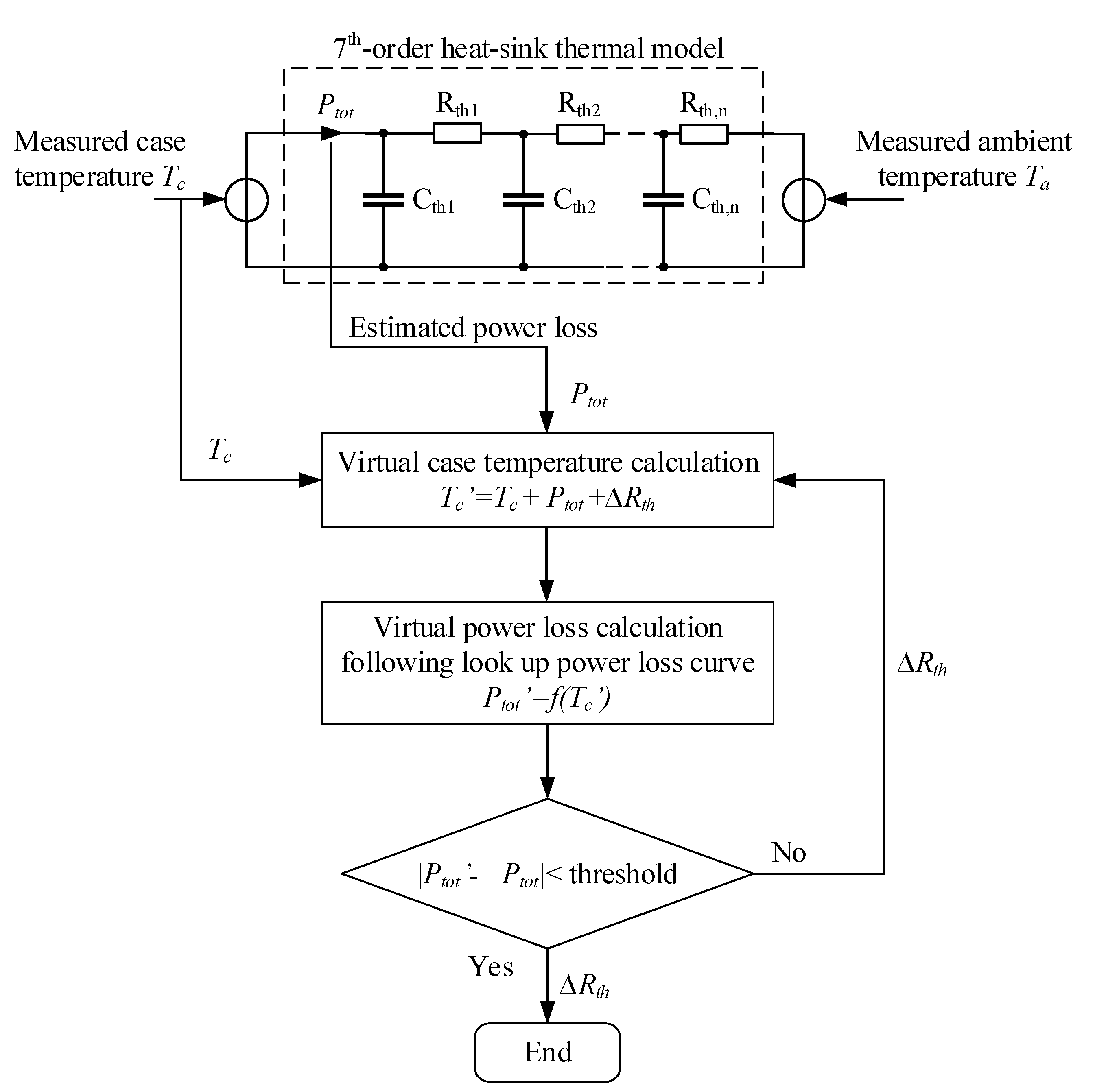

- Monitoring thermal resistance.

2.2.5. Other Monitoring Techniques

- Embedded sensor-based CM techniques.

- Converter output-based techniques.

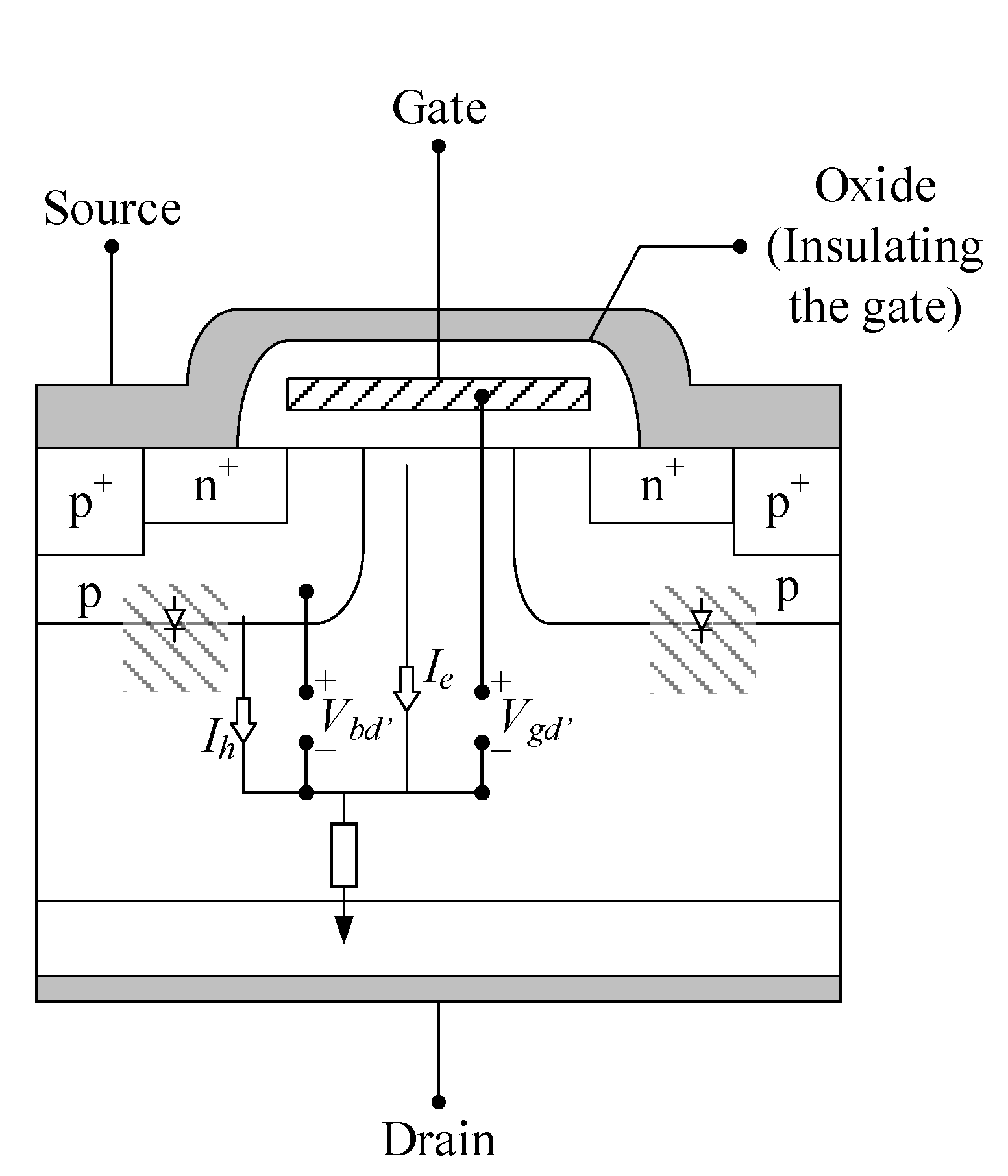

2.3. CM for SiC MOSFET Module

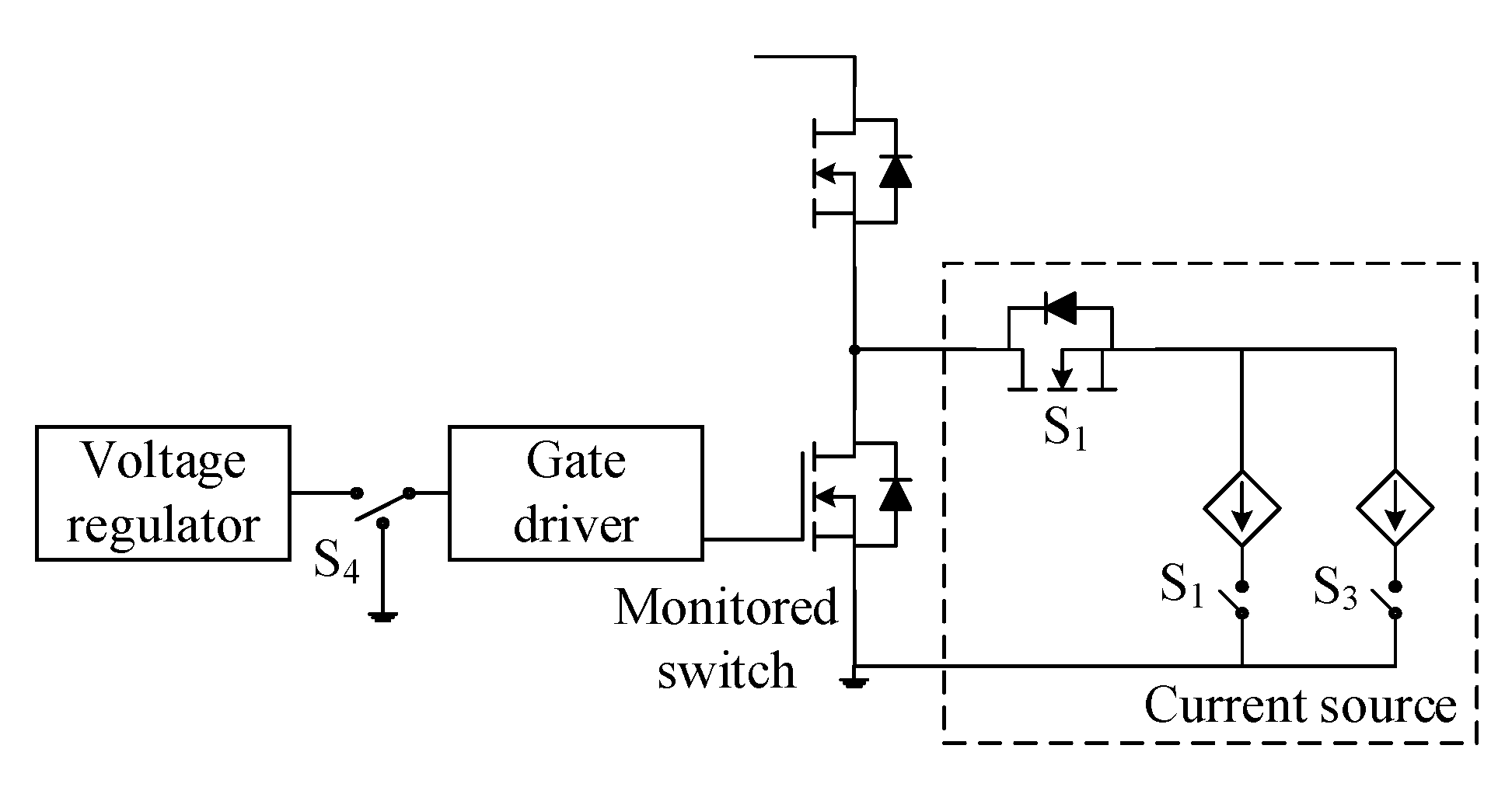

2.3.1. Monitoring Gate Leakage Current

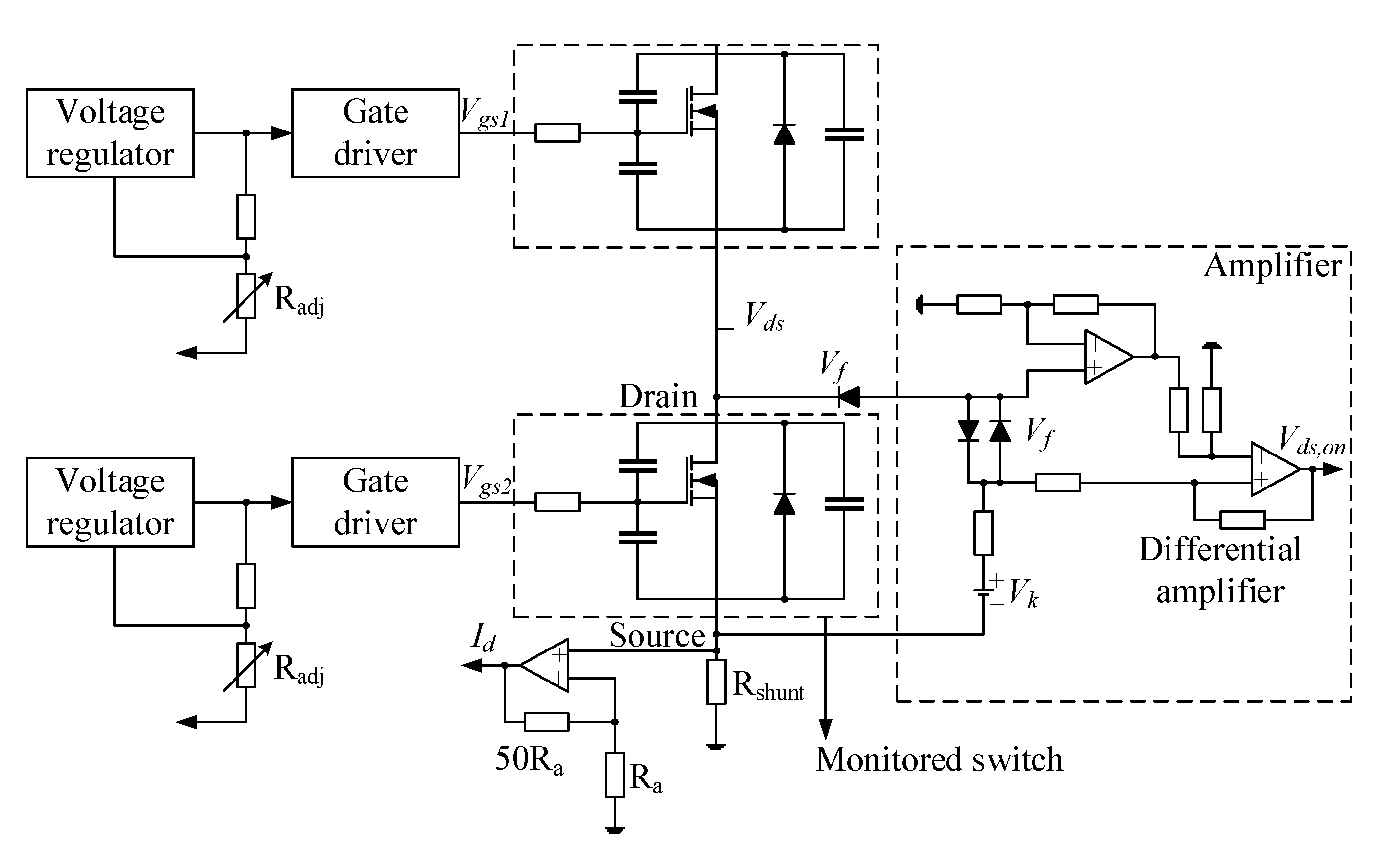

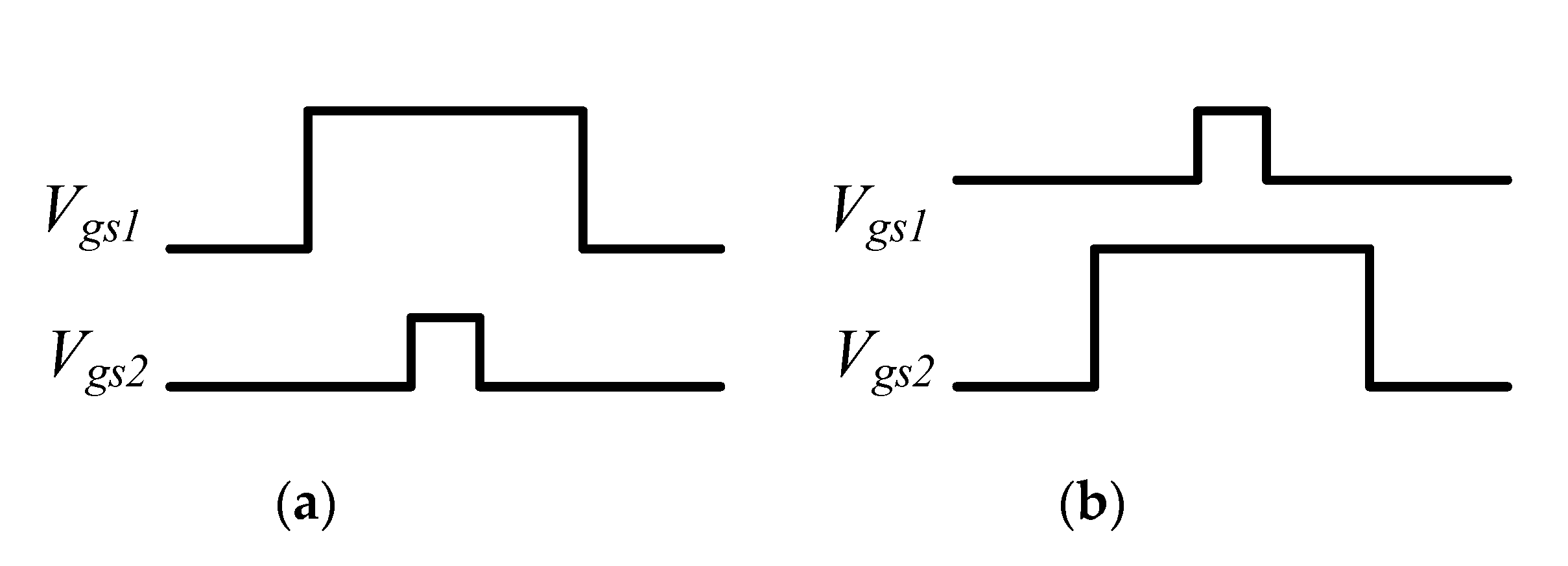

2.3.2. Monitoring on-State Resistance

2.3.3. Monitoring Reverse Body Diode

3. Active Thermal Control

- (1)

- The single converter systems include the two-level, three-level converters in ship power, machine drive applications, and buck/boost converters in the photovoltaic application.

- (2)

- The cascaded converter systems include the cascaded H-bridge (CHB) converters and MMC.

- (3)

- The parallel converter systems include the systems that utilize parallel structure based on two-, three-level converters, buck/boost converters in wind power, and machine drive applications.

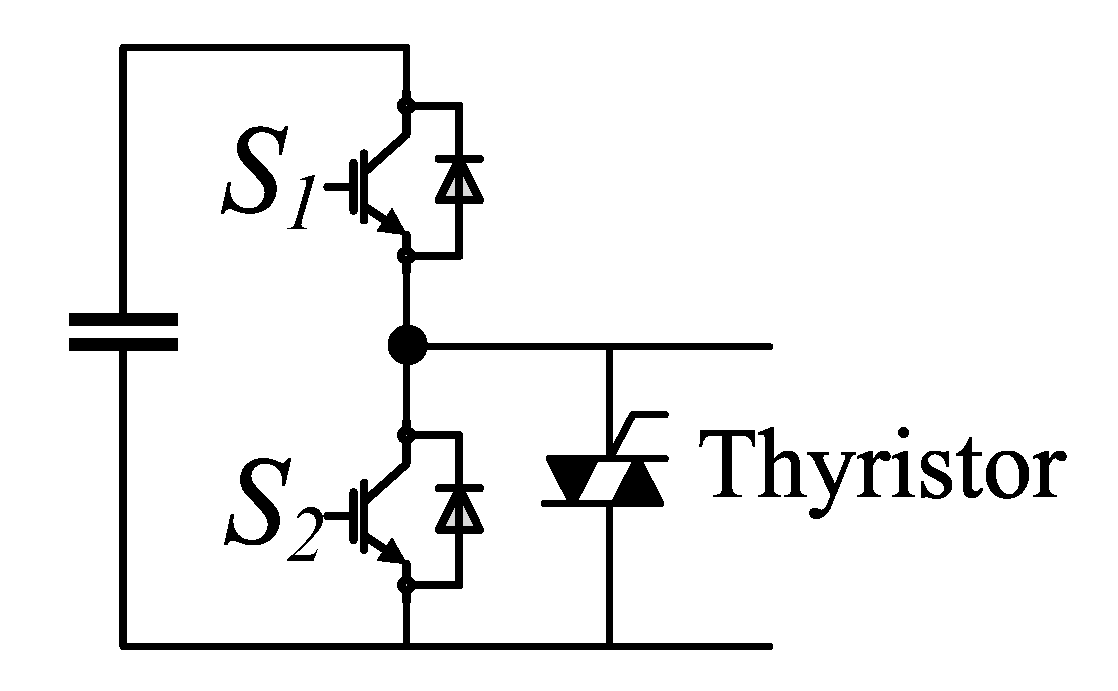

3.1. Single Converter System

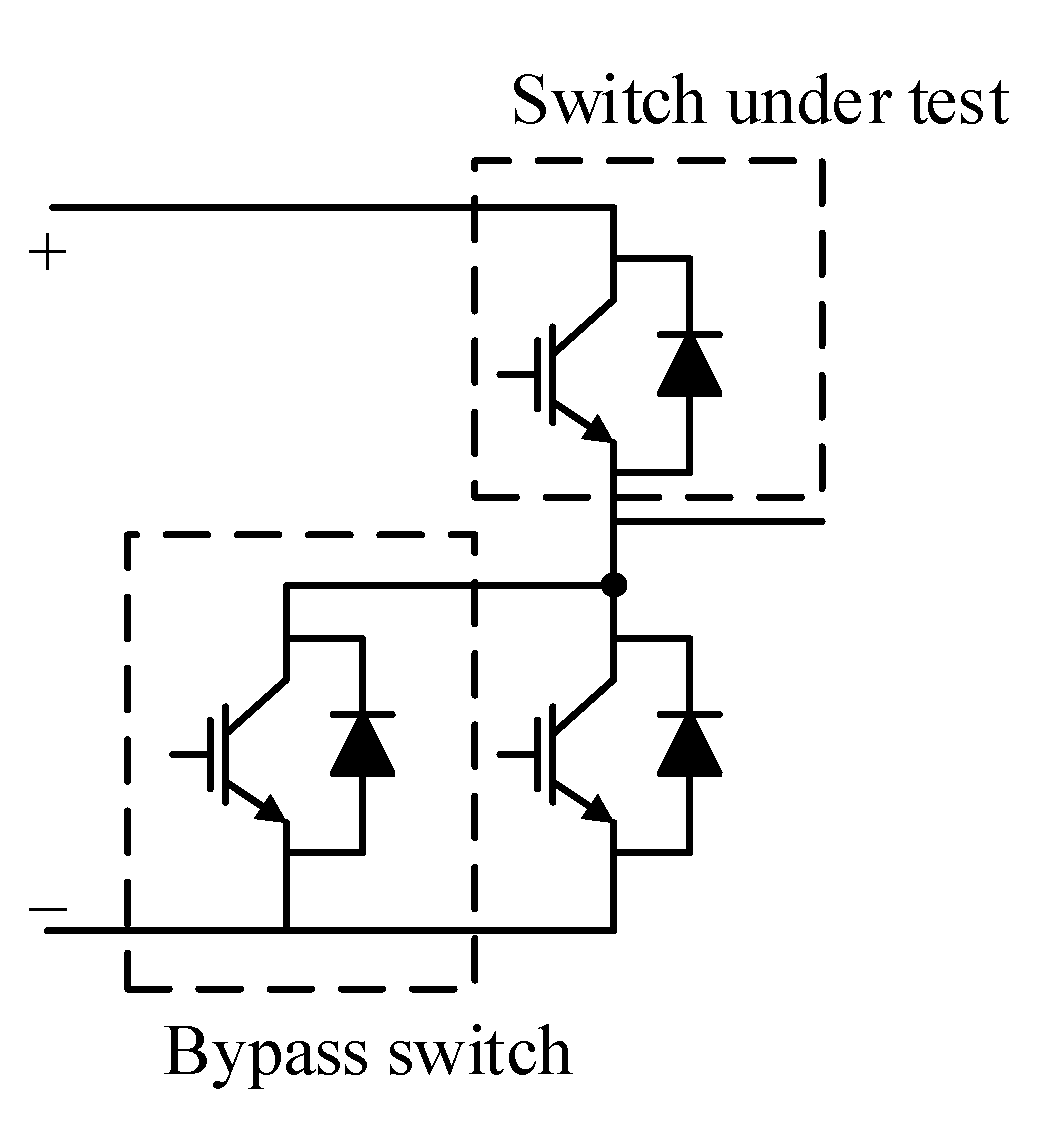

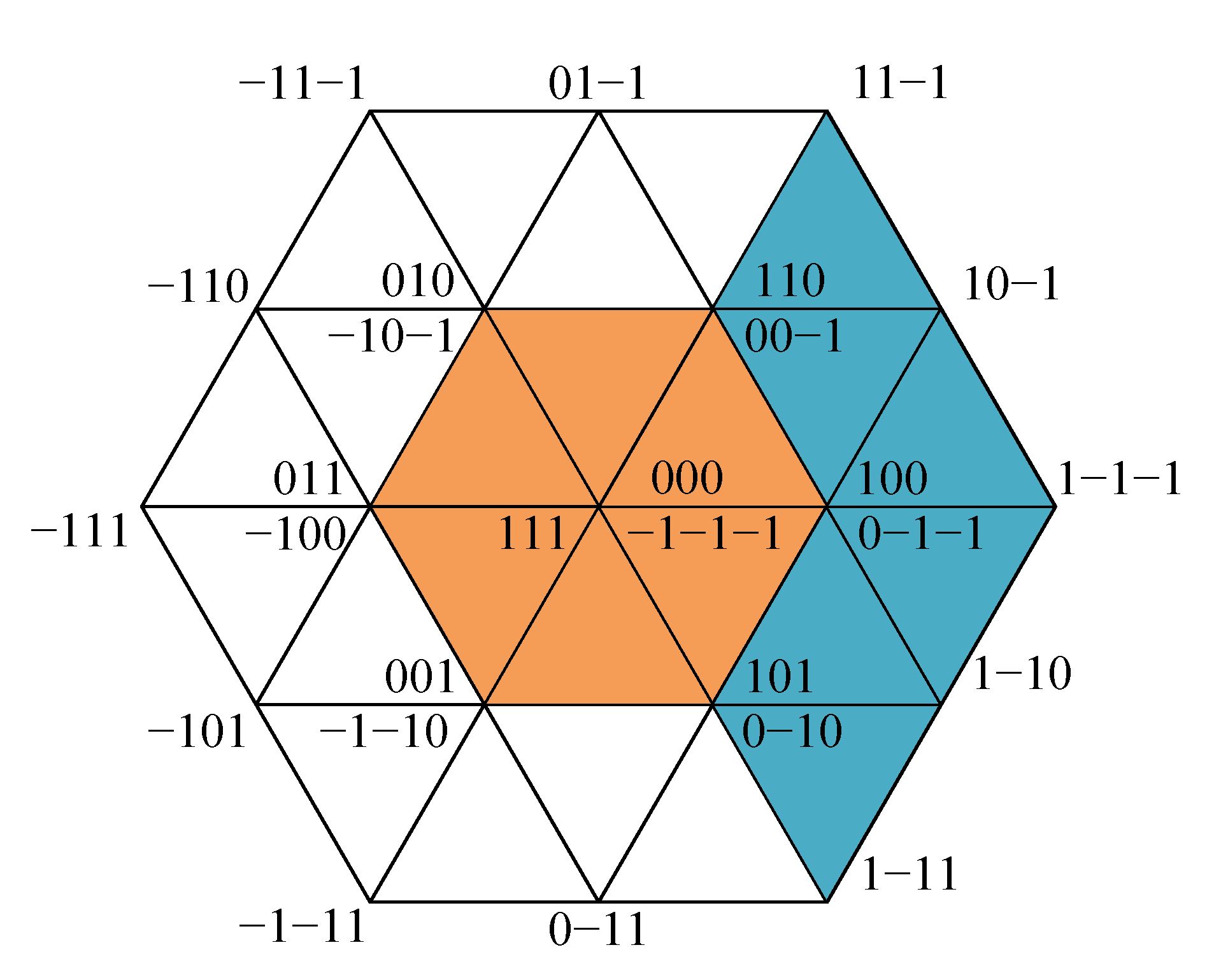

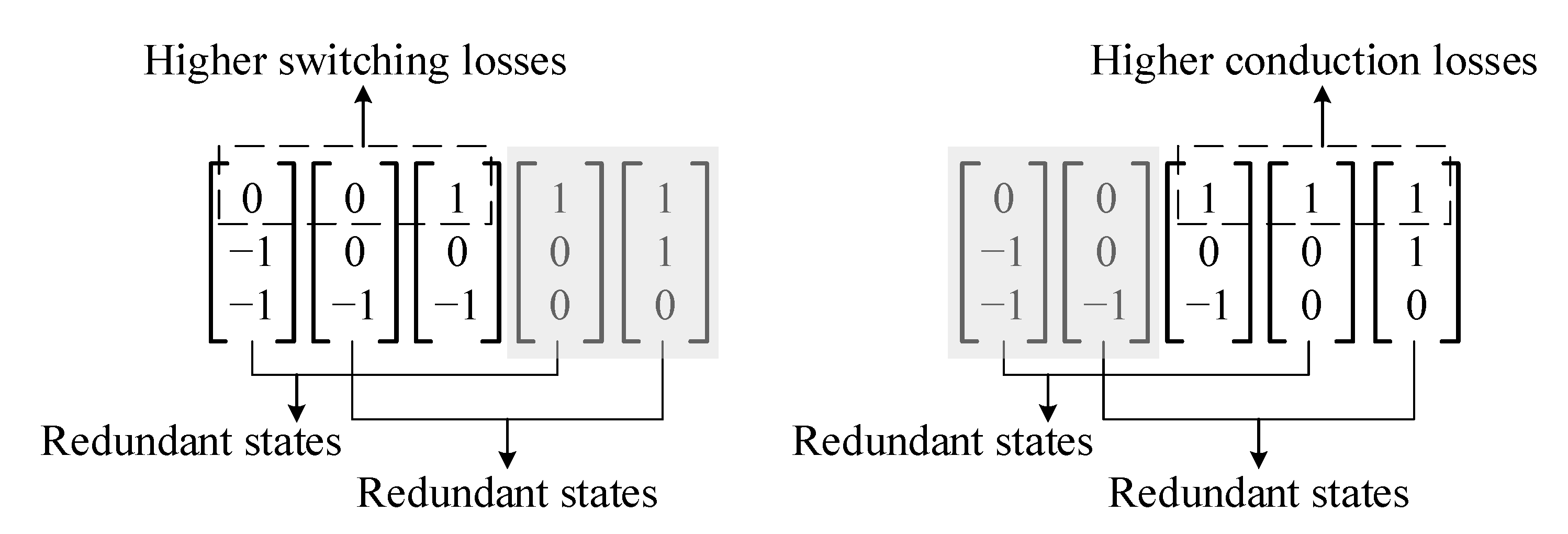

3.2. Cascaded Converter System

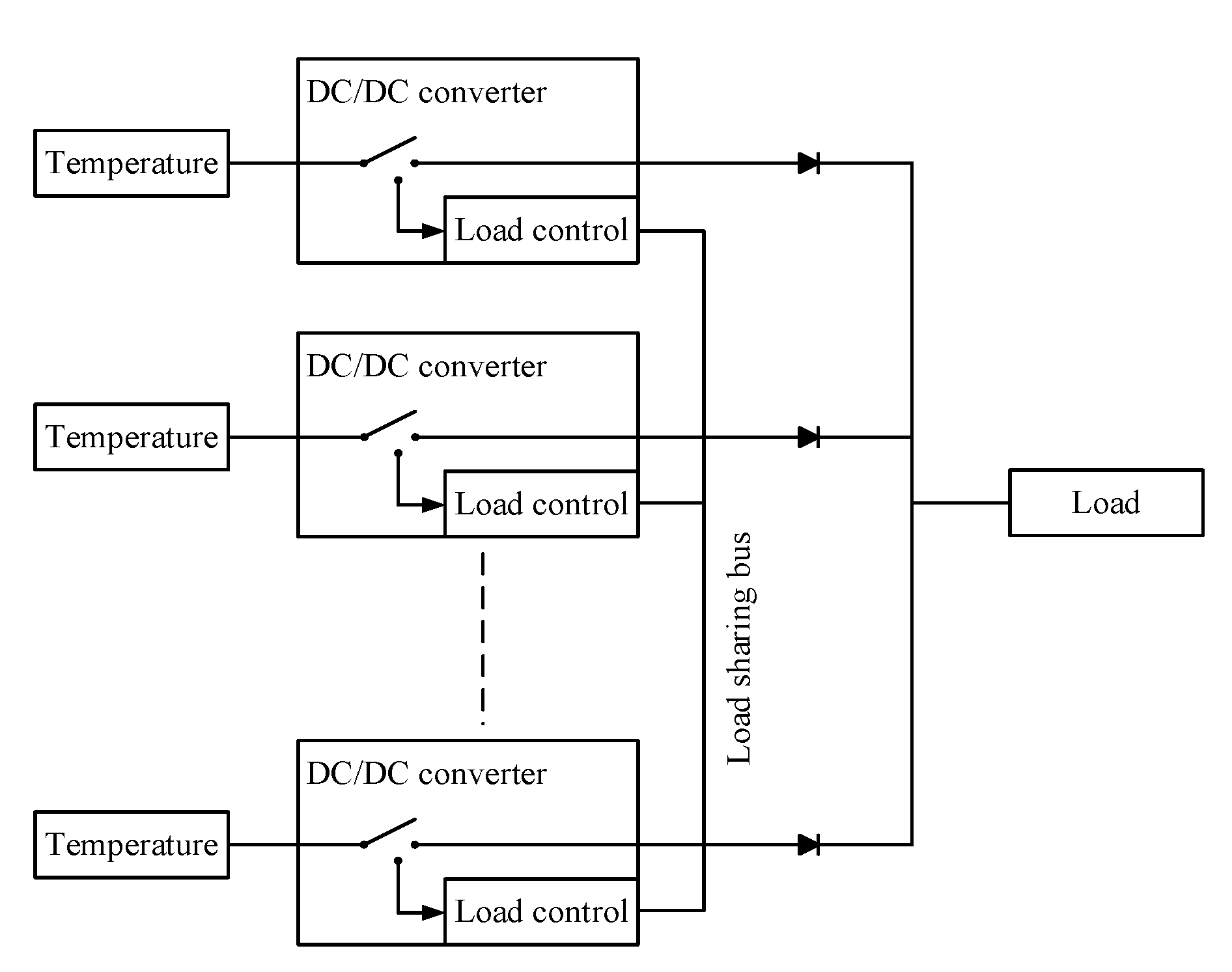

3.3. Parallel Converter System

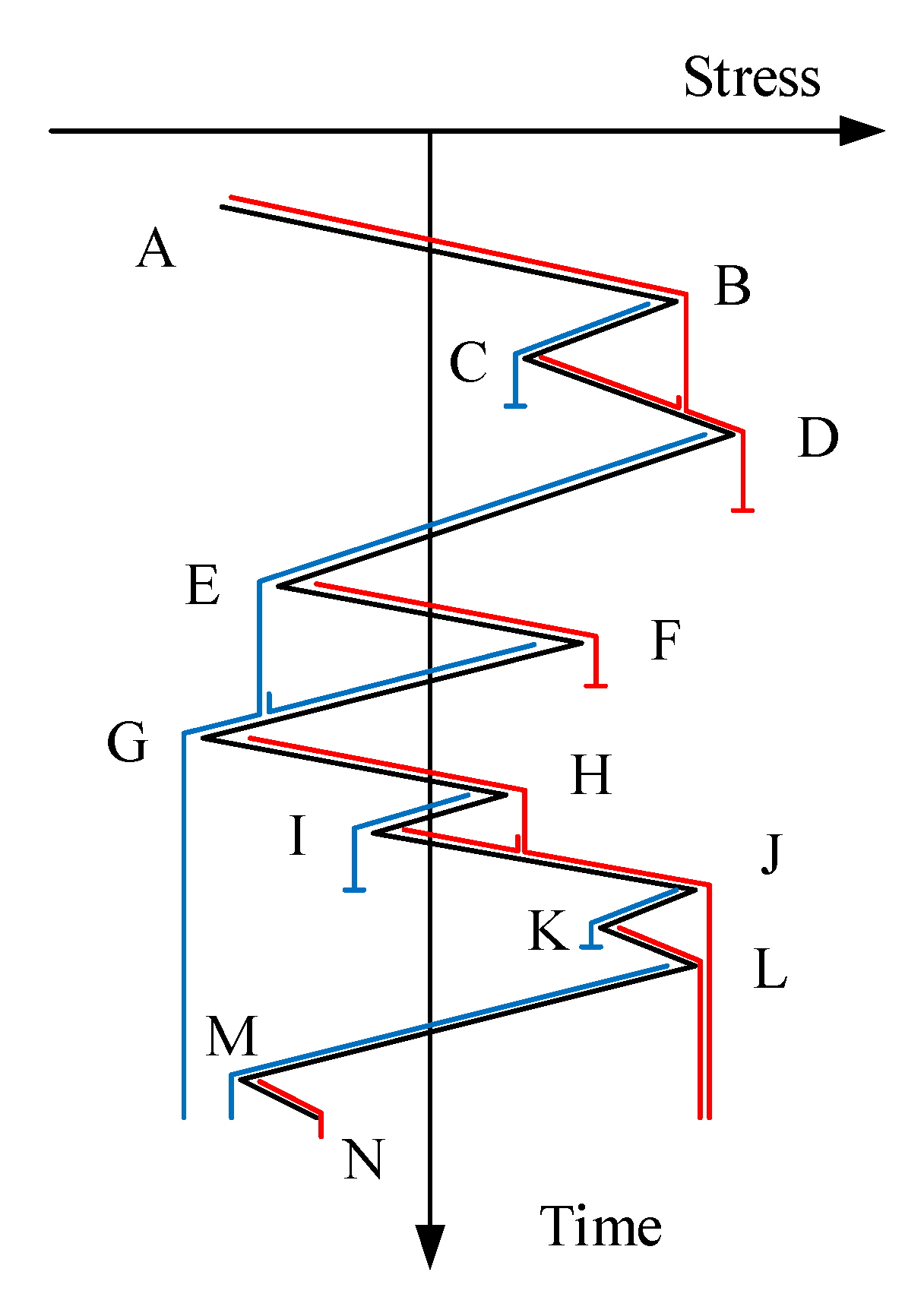

4. Remaining Useful Lifetime Estimation

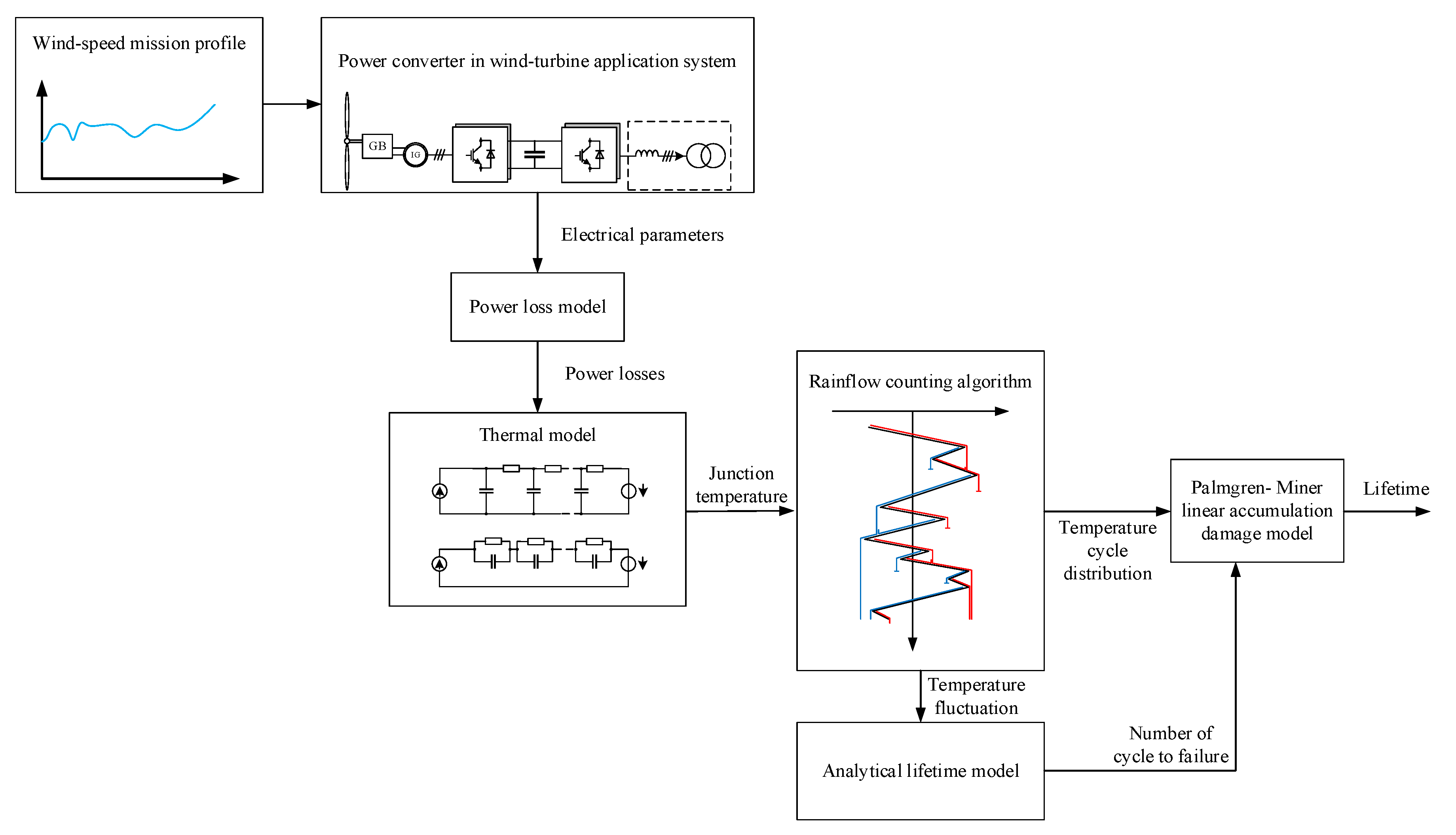

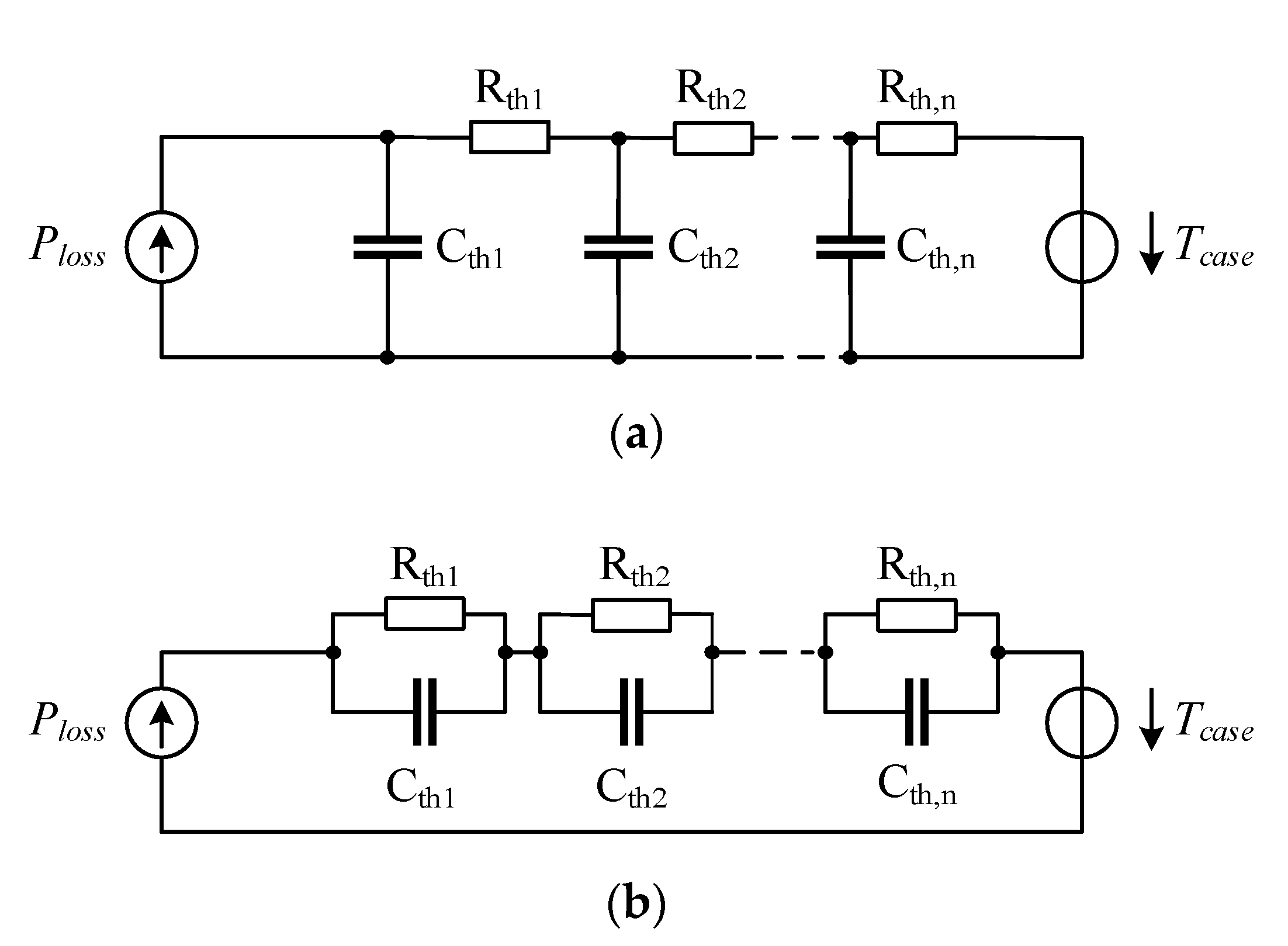

4.1. Model-Based Methods

4.2. Data-Driven Based Methods

5. Discussion of Enhancing Reliability Techniques

6. Conclusions

- (1)

- Based on the basics of existing CM techniques, it is still required to find out more failure indicators that can more accurately indicate the health condition, especially for the SiC devices—understanding the effect of failure and other impacts such as temperature on changes of failure indicators.

- (2)

- It is significantly required to find a method to monitor many failures at the same time by using one or more failure indicators. Therefore, an accurate and reliable decoupling of the failure indicators and TSEPs should be investigated.

- (3)

- In addition to the CM at the device level, the converter-based or system-level CM techniques need to be further developed to find out more failure indicators based on the power system output performance. Furthermore, an approach utilized to locate the failure devices should be investigated to assist the system-level CM approaches.

- (4)

- The need for a CM method when the power converter is working is significant. Apparently, the variation of electrical and thermal parameters during system operation, especially in photovoltaic and wind turbine applications, complicates the CM techniques.

- (5)

- In terms of the ATC, the trade-off among ATC efficiency, output performance, and cost should be considered. The utilization of ATC without deteriorating the power system performance is a critical aspect. Furthermore, the verification of ATC with practical applications should be more investigated.

- (6)

- The linear damage accumulation method, such as the Palmgre–Miner model, is widely utilized. Besides, the non-linear damage accumulation methods need to be developed to increase the accuracy of the lifetime modes.

- (1)

- The advances in semiconductor materials and packaging technologies provide more aspects for exploring them as far as reliability issues are concerned.

- (2)

- New technologies with measurement circuitry for high-frequency applications are further developed, which provide an open window to apply them in terms of CM techniques without interrupting the operation of the power converter system.

- (3)

- Further development of a real-time monitoring system helps obtain better mission profile data for various types of power converter systems to improve RUL estimation accuracy.

Author Contributions

Funding

Conflicts of Interest

References

- Teke, A.; Latran, M.B. Review of Multifunctional Inverter Topologies and Control Schemes Used in Distributed Generation Systems. J. Power Electron. 2014, 14, 324–340. [Google Scholar] [CrossRef]

- Miveh, M.R.; Rahmat, M.F.; Ghadimi, A.A.; Mustafa, M.W. Power Quality Improvement in Autonomous Microgrids Using Multi-functional Voltage Source Inverters: A Comprehensive Review. J. Power Electron. 2015, 15, 1054–1065. [Google Scholar] [CrossRef]

- Wang, X.; Guerrero, J.M.; Blaabjerg, F.; Chen, Z. A Review of Power Electronics Based Microgrids. J. Power Electron. 2012, 12, 181–192. [Google Scholar] [CrossRef]

- Ballal, M.S.; Bhadane, K.V.; Moharil, R.M.; Suryawanshi, H.M. A Control and Protection Model for the Distributed Generation and Energy Storage Systems in Microgrids. J. Power Electron. 2016, 16, 748–759. [Google Scholar] [CrossRef]

- O’Connor, P.D.T.; Kleyner, A. Practical Reliability Engineering: O’Connor/Practical Reliability Engineering; John Wiley & Sons, Ltd.: Chichester, UK, 2011. [Google Scholar]

- Saleh, J.H.; Marais, K. Highlights from the early (and pre-) history of reliability engineering. Reliab. Eng. Syst. Saf. 2006, 91, 249–256. [Google Scholar] [CrossRef]

- Yang, S.; Bryant, A.; Mawby, P.; Xiang, D.; Ran, L.; Tavner, P. An Industry-Based Survey of Reliability in Power Electronic Converters. IEEE Trans. Ind. Appl. 2011, 47, 1441–1451. [Google Scholar] [CrossRef]

- Reddy, L.G.; Tolbert, L.; Ozpineci, B. Power Cycle Testing of Power Switches: A Literature Survey. IEEE Trans. Power Electron. 2014, 30, 2465–2473. [Google Scholar]

- Kostandyan, E.E.; Sørensen, J.D. Physics of failure as a basis for solder elements reliability assessment in wind turbines. Reliab. Eng. Syst. Saf. 2012, 108, 100–107. [Google Scholar] [CrossRef]

- Sze, S.M.; Ng, K.K. Physics of Semiconductor Devices, 3rd ed.; Wiley-Interscience: Hoboken, NJ, USA, 2007. [Google Scholar]

- Janicki, M.; Napieralski, A. Modelling electronic circuit radiation cooling using analytical thermal model. Microelectron. J. 2000, 31, 781–785. [Google Scholar] [CrossRef]

- Yang, S.; Xiang, D.; Bryant, A.; Mawby, P.; Ran, L.; Tavner, P. Condition Monitoring for Device Reliability in Power Electronic Converters: A Review. IEEE Trans. Power Electron. 2010, 25, 2734–2752. [Google Scholar] [CrossRef]

- Oh, H.; Han, B.; McCluskey, P.; Han, C.; Youn, B.D. Physics-of-Failure, Condition Monitoring, and Prognostics of Insulated Gate Bipolar Transistor Modules: A Review. IEEE Trans. Power Electron. 2015, 30, 2413–2426. [Google Scholar] [CrossRef]

- Avenas, Y.; Dupont, L.; Baker, N.; Zara, H.; Barruel, F. Condition Monitoring: A Decade of Proposed Techniques. IEEE Ind. Electron. Mag. 2015, 9, 22–36. [Google Scholar] [CrossRef]

- Moeini, R.; Tricoli, P.; Hemida, H.; Baniotopoulos, C. Increasing the reliability of wind turbines using condition monitoring of semiconductor devices: A review. IET Renew. Power Gener. 2018, 12, 182–189. [Google Scholar] [CrossRef]

- Andresen, M.; Ma, K.; Buticchi, G.; Falck, J.; Blaabjerg, F.; Liserre, M. Junction Temperature Control for More Reliable Power Electronics. IEEE Trans. Power Electron. 2018, 33, 765–776. [Google Scholar] [CrossRef]

- Hanif, A.; Yu, Y.; DeVoto, D.; Khan, F. A Comprehensive Review toward the State-of-the-Art in Failure and Lifetime Predictions of Power Electronic Devices. IEEE Trans. Power Electron. 2019, 34, 4729–4746. [Google Scholar] [CrossRef]

- Wang, B.; Cai, J.; Du, X.; Zhou, L. Review of power semiconductor device reliability for power converters. CPSS Trans. Power Electron. Appl. 2017, 2, 101–117. [Google Scholar] [CrossRef]

- Falck, J.; Felgemacher, C.; Rojko, A.; Liserre, M.; Zacharias, P. Reliability of Power Electronic Systems: An Industry Perspective. IEEE Ind. Electron. Mag. 2018, 12, 24–35. [Google Scholar] [CrossRef]

- Manohar, S.S.; Sahoo, A.; Subramaniam, A.; Panda, S.K. Condition monitoring of power electronic converters in power plants—A review. In Proceedings of the 2017 20th International Conference on Electrical Machines and Systems (ICEMS), Sydney, Australia, 11–14 August 2017; pp. 1–5. [Google Scholar]

- Rabkowski, J.; Peftitsis, D.; Nee, H. Silicon Carbide Power Transistors: A New Era in Power Electronics Is Initiated. IEEE Ind. Electron. Mag. 2012, 6, 17–26. [Google Scholar] [CrossRef]

- Neudeck, P.G.; Okojie, R.S.; Chen, L. High-temperature electronics—A role for wide bandgap semiconductors? Proc. IEEE 2002, 90, 1065–1076. [Google Scholar] [CrossRef]

- Millan, J.; Godignon, P.; Perpina, X.; Perez-Tomas, A.; Rebollo, J. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar] [CrossRef]

- Castellazzi, A.; Fayyaz, A.; Romano, G.; Yang, L.; Riccio, M.; Irace, A. SiC power MOSFETs performance, robustness and technology maturity. Microelectron. Reliab. 2016, 58, 164–176. [Google Scholar] [CrossRef]

- Kimoto, T.; Cooper, J.A. Device Processing of Silicon Carbide. In Fundamentals of Silicon Carbide Technology; John Wiley & Sons Singapore Pte. Ltd.: Singapore, 2014; pp. 189–276. [Google Scholar]

- Patil, N.; Celaya, J.; Das, D.; Goebel, K.; Pecht, M. Precursor Parameter Identification for Insulated Gate Bipolar Transistor (IGBT) Prognostics. IEEE Trans. Reliab. 2009, 58, 271–276. [Google Scholar] [CrossRef]

- Lelis, A.J.; Green, R.; Habersat, D.B.; El, M. Basic Mechanisms of Threshold-Voltage Instability and Implications for Reliability Testing of SiC MOSFETs. IEEE Trans. Electron Devices 2015, 62, 316–323. [Google Scholar] [CrossRef]

- Tounsi, M.; Oukaour, A.; Tala-Ighil, B.; Gualous, H.; Boudart, B.; Aissani, D. Characterization of high-voltage IGBT module degradations under PWM power cycling test at high ambient temperature. Microelectron. Reliab. 2010, 50, 1810–1814. [Google Scholar] [CrossRef]

- Mohamed Sathik, M.H.; Prasanth, S.; Sasongko, F.; Pou, J.; Gupta, A.K. Online Condition Monitoring of IGBT Modules Using Gate-Charge Identification. In Proceedings of the 2019 IEEE Applied Power Electronics Conference and Exposition (APEC), Anaheim, CA, USA, 17–21 March 2019; pp. 2702–2707. [Google Scholar]

- Wang, P.; Zatarski, J.; Banerjee, A.; Donnal, J. Condition Monitoring of SiC MOSFETs Utilizing Gate Leakage Current. In Proceedings of the 2020 IEEE Applied Power Electronics Conference and Exposition (APEC), New Orleans, LA, USA, 15–19 March 2020; IEEE: New Orleans, LA, USA, 2020; pp. 1837–1843. [Google Scholar]

- Ni, Z.; Li, Y.; Lyu, X.; Yadav, O.P.; Cao, D. Miller plateau as an indicator of SiC MOSFET gate oxide degradation. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 1280–1287. [Google Scholar]

- Karki, U.; Peng, F.Z. Effect of Gate-Oxide Degradation on Electrical Parameters of Power MOSFETs. IEEE Trans. Power Electron. 2018, 33, 10764–10773. [Google Scholar] [CrossRef]

- Ugur, E.; Yang, F.; Pu, S.; Zhao, S.; Akin, B. Degradation Assessment and Precursor Identification for SiC MOSFETs Under High Temp Cycling. IEEE Trans. Ind. Applicat. 2019, 55, 2858–2867. [Google Scholar] [CrossRef]

- Chen, C.; Ye, X.; Wang, Y.; Xu, J.; Zhai, G. PHM application of power converters using health precursor of power MOSFETs. In Proceedings of the 2015 Prognostics and System Health Management Conference (PHM), Beijing, China, 21–23 October 2015; pp. 1–5. [Google Scholar]

- “SiC power devices and modules,” ROHM Semicond. Application Note, 2014. Available online: http://rohmfs.rohm.com/en/products/databook/applinote/discrete/sic/common/sic_appli-e.pdf (accessed on 18 November 2020).

- Agarwal, A.; Fatima, H.; Haney, S.; Ryu, S.-H. A New Degradation Mechanism in High-Voltage SiC Power MOSFETs. IEEE Electron Device Lett. 2007, 28, 587–589. [Google Scholar] [CrossRef]

- Kusumoto, O.; Ohoka, A.; Horikawa, N.; Tanaka, K.; Niwayama, M.; Uchida, M.; Kanzawa, Y.; Sawada, K.; Ueda, T. Reliability of Diode-Integrated SiC Power MOSFET(DioMOS). Microelectron. Reliab. 2016, 58, 158–163. [Google Scholar] [CrossRef]

- Green, R.; Lelis, A.; Nouketcha, F. Comparison of SiC MOSFET Characteristics Following Body-Diode Forward-Current Stress. MSF 2019, 963, 583–587. [Google Scholar] [CrossRef]

- Bonyadi, R.; Alatise, O.; Jahdi, S.; Hu, J.; Evans, L.; Mawby, P.A. Investigating the reliability of SiC MOSFET body diodes using Fourier series modelling. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 443–448. [Google Scholar]

- Hasari, S.A.; Salemnia, A.; Hamzeh, M. Applicable Method for Average Switching Loss Calculation in Power Electronic Converters. J. Power Electron. 2017, 17, 1097–1108. [Google Scholar]

- Lee, K.; Suh, Y.; Kang, Y. Loss Analysis and Comparison of High Power Semiconductor Devices in 5MW PMSG MV Wind Turbine Systems. J. Power Electron. 2015, 15, 1380–1391. [Google Scholar] [CrossRef]

- Wang, H.; Tang, G.; He, Z.; Cao, J. Power Loss and Junction Temperature Analysis in the Modular Multilevel Converters for HVDC Transmission Systems. J. Power Electron. 2015, 15, 685–694. [Google Scholar] [CrossRef]

- Bouarroudj, M.; Khatir, Z.; Ousten, J.P.; Badel, F.; Dupont, L.; Lefebvre, S. Degradation behavior of 600V–200A IGBT modules under power cycling and high temperature environment conditions. Microelectron. Reliab. 2007, 47, 1719–1724. [Google Scholar] [CrossRef][Green Version]

- Morozumi, A.; Yamada, K.; Miyasaka, T.; Sumi, S.; Seki, Y. Reliability of power cycling for igbt power semiconductor modules. IEEE Trans. Ind. Applicat. 2003, 39, 665–671. [Google Scholar] [CrossRef]

- Ji, B.; Pickert, V.; Cao, W.; Zahawi, B. In Situ Diagnostics and Prognostics of Wire Bonding Faults in IGBT Modules for Electric Vehicle Drives. IEEE Trans. Power Electron. 2013, 28, 5568–5577. [Google Scholar] [CrossRef]

- Hamidi, A.; Beck, N.; Thomas, K.; Herr, E. Reliability and lifetime evaluation of different wire bonding technologies for high power IGBT modules. Microelectron. Reliab. 1999, 39, 1153–1158. [Google Scholar] [CrossRef]

- Nayak, P.; Pramanick, S.K.; Rajashekara, K. A High-Temperature Gate Driver for Silicon Carbide mosfet. IEEE Trans. Ind. Electron. 2018, 65, 1955–1964. [Google Scholar] [CrossRef]

- Sarkany, Z.; Vass-Varnai, A.; Rencz, M. Investigation of die-attach degradation using power cycling tests. In Proceedings of the 2013 IEEE 15th Electronics Packaging Technology Conference (EPTC 2013), Singapore, 11–13 December 2013; pp. 780–784. [Google Scholar]

- Kim, T.; Funaki, T. Thermal measurement and analysis of packaged SiC MOSFETs. Thermochim. Acta 2016, 633, 31–36. [Google Scholar] [CrossRef]

- Luo, H.; Iannuzzo, F.; Blaabjerg, F. Solder layer degradation measurement for SiC-MOSFET Modules under accelerated power cycling conditions. In Proceedings of the CIPS 2018; 10th International Conference on Integrated Power Electronics Systems, Stuttgart, Germany, 20–22 March 2018; pp. 1–5. [Google Scholar]

- Uwe, S.; Schmidt, R. Impact of solder fatigue on module lifetime in power cycling tests. In Proceedings of the 2011 14th European Conference on Power Electronics and Applications, Birmingham, UK, 30 August–1 September 2011; pp. 1–10. [Google Scholar]

- Eleffendi, M.A.; Johnson, C.M. Thermal path integrity monitoring for IGBT power electronics modules. In Proceedings of the CIPS 2014, 8th International Conference on Integrated Power Electronics Systems, Nuremberg, Germany, 25–27 February 2014; pp. 1–7. [Google Scholar]

- Ciappa, M. Selected failure mechanisms of modern power modules. Microelectron. Reliab. 2002, 42, 653–667. [Google Scholar] [CrossRef]

- Smet, V.; Forest, F.; Huselstein, J.-J.; Rashed, A.; Richardeau, F. Evaluation of Vce Monitoring as a Real-Time Method to Estimate Aging of Bond Wire-IGBT Modules Stressed by Power Cycling. IEEE Trans. Ind. Electron. 2013, 60, 2760–2770. [Google Scholar] [CrossRef]

- Xiong, Y.; Cheng, X.; Shen, Z.J.; Mi, C.; Wu, H.; Garg, V.K. Prognostic and Warning System for Power-Electronic Modules in Electric, Hybrid Electric, and Fuel-Cell Vehicles. IEEE Trans. Ind. Electron. 2008, 55, 2268–2276. [Google Scholar] [CrossRef]

- Smet, V.; Forest, F.; Huselstein, J.-J.; Richardeau, F.; Khatir, Z.; Lefebvre, S.; Berkani, M. Ageing and Failure Modes of IGBT Modules in High-Temperature Power Cycling. IEEE Trans. Ind. Electron. 2011, 58, 4931–4941. [Google Scholar] [CrossRef]

- Beczkowski, S.; Ghimre, P.; de Vega, A.R.; Munk-Nielsen, S.; Rannestad, B.; Thogersen, P. Online Vce measurement method for wear-out monitoring of high power IGBT modules. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 3–5 September 2013; IEEE: Lille, France, 2013; pp. 1–7. [Google Scholar]

- Choi, U.-M.; Blaabjerg, F.; Jorgensen, S.; Munk-Nielsen, S.; Rannestad, B. Reliability Improvement of Power Converters by Means of Condition Monitoring of IGBT Modules. IEEE Trans. Power Electron. 2017, 32, 7990–7997. [Google Scholar] [CrossRef]

- Chen, S.; Ji, S.; Pan, L.; Liu, C.; Zhu, L. An ON-State Voltage Calculation Scheme of MMC Submodule IGBT. IEEE Trans. Power Electron. 2019, 34, 7996–8007. [Google Scholar] [CrossRef]

- Liu, J.; Zhang, G.; Chen, Q.; Qi, L.; Geng, Y.; Wang, J. In situ Condition Monitoring of IGBTs Based on the Miller Plateau Duration. IEEE Trans. Power Electron. 2019, 34, 769–782. [Google Scholar] [CrossRef]

- Eleffendi, M.A.; Johnson, C.M. Evaluation of on-state voltage Vce(on) and threshold voltage Vth for real-time health monitoring of IGBT power modules. In Proceedings of the 2015 17th European Conference on Power Electronics and Applications (EPE’15 ECCE-Europe), Geneva, Switzerland, 8–10 September 2015; pp. 1–10. [Google Scholar]

- Choi, U.M.; Blaabjerg, F.; Iannuzzo, F.; Jørgensen, S. Junction temperature estimation method for a 600 V, 30A IGBT module during converter operation. Microelectron. Reliab. 2015, 55, 2022–2026. [Google Scholar] [CrossRef]

- Avenas, Y.; Dupont, L.; Khatir, Z. Temperature Measurement of Power Semiconductor Devices by Thermo-Sensitive Electrical Parameters—A Review. IEEE Trans. Power Electron. 2012, 27, 3081–3092. [Google Scholar] [CrossRef]

- Mautry, P.G.; Trager, J. Investigation of self-heating in VLSI and ULSI MOSFETs. In Proceedings of the International Conference on Microelectronic Test Structures, San Diego, CA, USA, 5–7 March 1990; pp. 221–226. [Google Scholar]

- Brekel, W.; Duetemeyer, T.; Puk, G.; Schilling, O. Time resolved in situ TVJ measurements of 6.5kV IGBTs during inverter operation. In Proceedings of the PCIM Europe, Nuremberg, Germany, 12–14 May 2009; pp. 806–813. [Google Scholar]

- Baker, N.; Munk-Nielsen, S.; Iannuzzo, F.; Liserre, M. IGBT Junction Temperature Measurement via Peak Gate Current. IEEE Trans. Power Electron. 2016, 31, 3784–3793. [Google Scholar] [CrossRef]

- Xu, Z.; Xu, F.; Wang, F. Junction Temperature Measurement of IGBTs Using Short Circuit Current as a Temperature Sensitive Electrical Parameter for Converter Prototype Evaluation. IEEE Trans. Ind. Electron. 2014, 62, 3419–3429. [Google Scholar] [CrossRef]

- Busatto, G.; Abbate, C.; Cascone, B.; Manzo, R.; Fratelli, L.; Giannini, G.; Iannuzzo, F.; Velardi, F. Characterisation of high-voltage IGBT modules at high temperature and high currents. In Proceedings of the Fifth International Conference on Power Electronics and Drive Systems, 2003. PEDS, Singapore, 17–20 November 2003; Volume 2, pp. 1391–1396. [Google Scholar]

- Azzopardi, S.; Boubkari, K.E.; Belmehdi, Y.; Deletage, J.Y.; Woirgard, E. Investigation of mechanical stress effect on electrical behavior of Trench Punch through IGBT under short-circuit condition at low and high temperature. In Proceedings of the 2011 14th European Conference on Power Electronics and Applications, Birmingham, UK, 30 August–1 September 2011; pp. 1–10. [Google Scholar]

- Laska, T.; Miller, G.; Pfaffenlehner, M.; Turkes, P.; Berger, D.; Gutsmann, B.; Kanschat, P.; Munzer, M. Short circuit properties of Trench-/Field-Stop-IGBTs-design aspects for a superior robustness. In Proceedings of the ISPSD ’03, 2003 IEEE 15th International Symposium on Power Semiconductor Devices and ICs, Cambridge, UK, 14–17 April 2003; pp. 152–155. [Google Scholar]

- Du, M.; Tang, Y.; Gao, M.; Ouyang, Z.; Wei, K.; Hurley, W.G. Online Estimation of the Junction Temperature Based on the Gate Pre-Threshold Voltage in High-Power IGBT Modules. IEEE Trans. Device Mater. Relib. 2019, 19, 501–508. [Google Scholar] [CrossRef]

- Bahun, I.; Sunde, V.; Jakopovic, Z. Estimation of Insulated-gate Bipolar Transistor Operating Temperature: Simulation and Experiment. J. Power Electron. 2013, 13, 729–736. [Google Scholar] [CrossRef]

- van der Broeck, C.H.; Gospodinov, A.; De Doncker, R.W. IGBT Junction Temperature Estimation via Gate Voltage Plateau Sensing. IEEE Trans. Ind. Applicat. 2018, 54, 4752–4763. [Google Scholar] [CrossRef]

- Kuhn, H.; Mertens, A. Online junction temperature measurement of IGBTs based on temperature sensitive electrical parameters. In Proceedings of the 2009 13th European Conference on Power Electronics and Applications, Barcelona, Spain, 8–10 September 2009; pp. 1–10. [Google Scholar]

- Luo, H.; Iannuzzo, F.; Blaabjerg, F.; Wang, X.; Li, W.; He, X. Elimination of bus voltage impact on temperature sensitive electrical parameter during turn-on transition for junction temperature estimation of high-power IGBT modules. In Proceedings of the 2017 IEEE Energy Conversion Congress and Exposition (ECCE), Cincinnati, OH, USA, 1–5 October 2017; pp. 5892–5898. [Google Scholar]

- Li, L.; Ning, P.; Wen, X.; Li, Y.; Ge, Q.; Zhang, D.; Tai, X. A turn-off delay time measurement and junction temperature estimation method for IGBT. In Proceedings of the 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), Tampa, FL, USA, 26–30 March 2017; pp. 2290–2296. [Google Scholar]

- Coquery, G.; Lallemand, R. Failure criteria for long term Accelerated Power Cycling Test linked to electrical turn off SOA on IGBT module. A 4000 hours test on 1200A–3300V module with AlSiC base plate. Microelectron. Reliab. 2000, 40, 1665–1670. [Google Scholar] [CrossRef]

- Xiang, D.; Ran, L.; Tavner, P.; Bryant, A.; Yang, S.; Mawby, P. Monitoring Solder Fatigue in a Power Module Using Case-Above-Ambient Temperature Rise. IEEE Trans. Ind. Applicat. 2011, 47, 2578–2591. [Google Scholar] [CrossRef]

- Lehmann, J.; Netzel, M.; Herzer, R.; Pawel, S. Method for electrical detection of bond wire lift-off for power semiconductors. In Proceedings of the ISPSD ’03, 2003 IEEE 15th International Symposium on Power Semiconductor Devices and ICs, Cambridge, UK, 14–17 April 2003; pp. 333–336. [Google Scholar]

- Sheng, M.; Alvi, M.H.; Lorenz, R.D. Real-time Bond Wire Lift-off Monitoring via Module Integrated Current Sensors. In Proceedings of the 2019 IEEE Energy Conversion Congress and Exposition (ECCE), Baltimore, MD, USA, 29 September–3 October 2019; pp. 3163–3169. [Google Scholar]

- Sheng, M.; Nogawa, H.; Alvi, M.H.; Lorenz, R.D. Current Sensing Integration with Lead Frames in 6-in-1 IGBT Modules. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018; pp. 367–374. [Google Scholar]

- Brauhn, T.J.; Sheng, M.; Dow, B.A.; Nogawa, H.; Lorenz, R.D. Module-Integrated GMR-Based Current Sensing for Closed-Loop Control of a Motor Drive. IEEE Trans. Ind. Applicat. 2017, 53, 222–231. [Google Scholar] [CrossRef]

- Chen, C.; Pickert, V.; Al-Greer, M.; Jia, C.; Ng, C. Localization and Detection of Bond Wire Faults in Multichip IGBT Power Modules. IEEE Trans. Power Electron. 2020, 35, 7804–7815. [Google Scholar] [CrossRef]

- Xiang, D.; Ran, L.; Tavner, P.; Yang, S.; Bryant, A.; Mawby, P. Condition Monitoring Power Module Solder Fatigue Using Inverter Harmonic Identification. IEEE Trans. Power Electron. 2012, 27, 235–247. [Google Scholar] [CrossRef]

- Ouaida, R.; Berthou, M.; Leon, J.; Perpina, X.; Oge, S.; Brosselard, P.; Joubert, C. Gate Oxide Degradation of SiC MOSFET in Switching Conditions. IEEE Electron Device Lett. 2014, 35, 1284–1286. [Google Scholar] [CrossRef]

- Erturk, F.; Ugur, E.; Olson, J.; Akin, B. Real-Time Aging Detection of SiC MOSFETs. IEEE Trans. Ind. Applicat. 2019, 55, 600–609. [Google Scholar] [CrossRef]

- Baker, N.; Munk-Nielsen, S.; Beczkowski, S. Test setup for long term reliability investigation of Silicon Carbide MOSFETs. In Proceedings of the 2013 15th European Conference on Power Electronics and Applications (EPE), Lille, France, 2–6 September 2013; pp. 1–9. [Google Scholar]

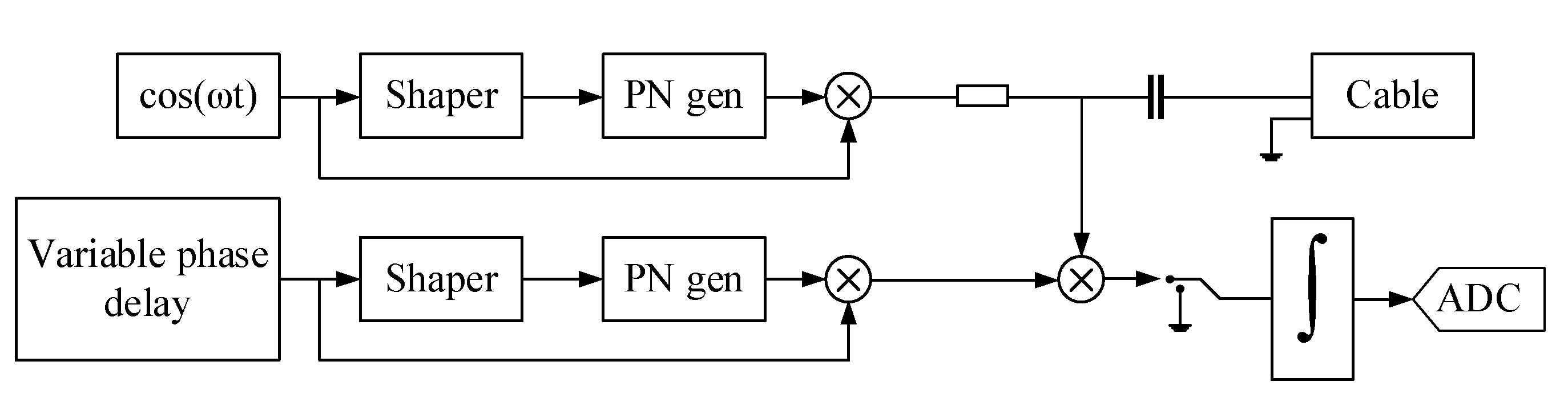

- Hanif, A.; Roy, S.; Khan, F. Detection of gate oxide and channel degradation in SiC power MOSFETs using reflectometry. In Proceedings of the 2017 IEEE 5th Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Santa Ana Pueblo, NM, USA, 30 October–1 November 2017; IEEE: Albuquerque, NM, USA, 2017; pp. 383–387. [Google Scholar]

- Smith, P.; Furse, C.; Gunther, J. Analysis of spread spectrum time domain reflectometry for wire fault location. IEEE Sens. J. 2005, 5, 1469–1478. [Google Scholar] [CrossRef]

- Pu, S.; Yang, F.; Vankayalapati, B.T.; Ugur, E.; Xu, C.; Akin, B. A Practical On-Board SiC MOSFET Condition Monitoring Technique for Aging Detection. IEEE Trans. Ind. Applicat. 2020, 56, 2828–2839. [Google Scholar] [CrossRef]

- Gonzalez-Hernando, F.; San-Sebastian, J.; Arias, M.; Rujas, A.; Iannuzzo, F. Discontinuous PWM for Online Condition Monitoring of SiC Power Modules. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 323–330. [Google Scholar] [CrossRef]

- Ugur, E.; Xu, C.; Yang, F.; Pu, S.; Akin, B. A New Complete Condition Monitoring Method for SiC Power MOSFETs. IEEE Trans. Ind. Electron. 2020, 68, 1654–1664. [Google Scholar] [CrossRef]

- Murdock, D.A.; Torres, J.E.R.; Connors, J.J.; Lorenz, R.D. Active thermal control of power electronic modules. IEEE Trans. Ind. Applicat. 2006, 42, 552–558. [Google Scholar] [CrossRef]

- Andresen, M.; Buticchi, G.; Falck, J.; Liserre, M.; Muehlfeld, O. Active thermal management for a single-phase H-Bridge inverter employing switching frequency control. In Proceedings of the PCIM Europe 2015, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 19–20 May 2015; pp. 1–8. [Google Scholar]

- Wei, L.; McGuire, J.; Lukaszewski, R.A. Analysis of PWM Frequency Control to Improve the Lifetime of PWM Inverter. IEEE Trans. Ind. Applicat. 2011, 47, 922–929. [Google Scholar]

- Phan, T.-M.; Oikonomou, N.; Riedel, G.J.; Pacas, M. PWM for active thermal protection in three level neutral point clamped inverters. In Proceedings of the 2014 IEEE Energy Conversion Congress and Exposition (ECCE), Pittsburgh, PA, USA, 14–18 September 2014; pp. 3710–3716. [Google Scholar]

- Ma, K.; Blaabjerg, F. Modulation Methods for Neutral-Point-Clamped Wind Power Converter Achieving Loss and Thermal Redistribution Under Low-Voltage Ride-Through. IEEE Trans. Ind. Electron. 2014, 61, 835–845. [Google Scholar] [CrossRef]

- Blaabjerg, F.; Ma, K. Thermal optimised modulation methods of three-level neutral-point-clamped inverter for 10 MW wind turbines under low-voltage ride through. IET Power Electron. 2012, 5, 920–927. [Google Scholar]

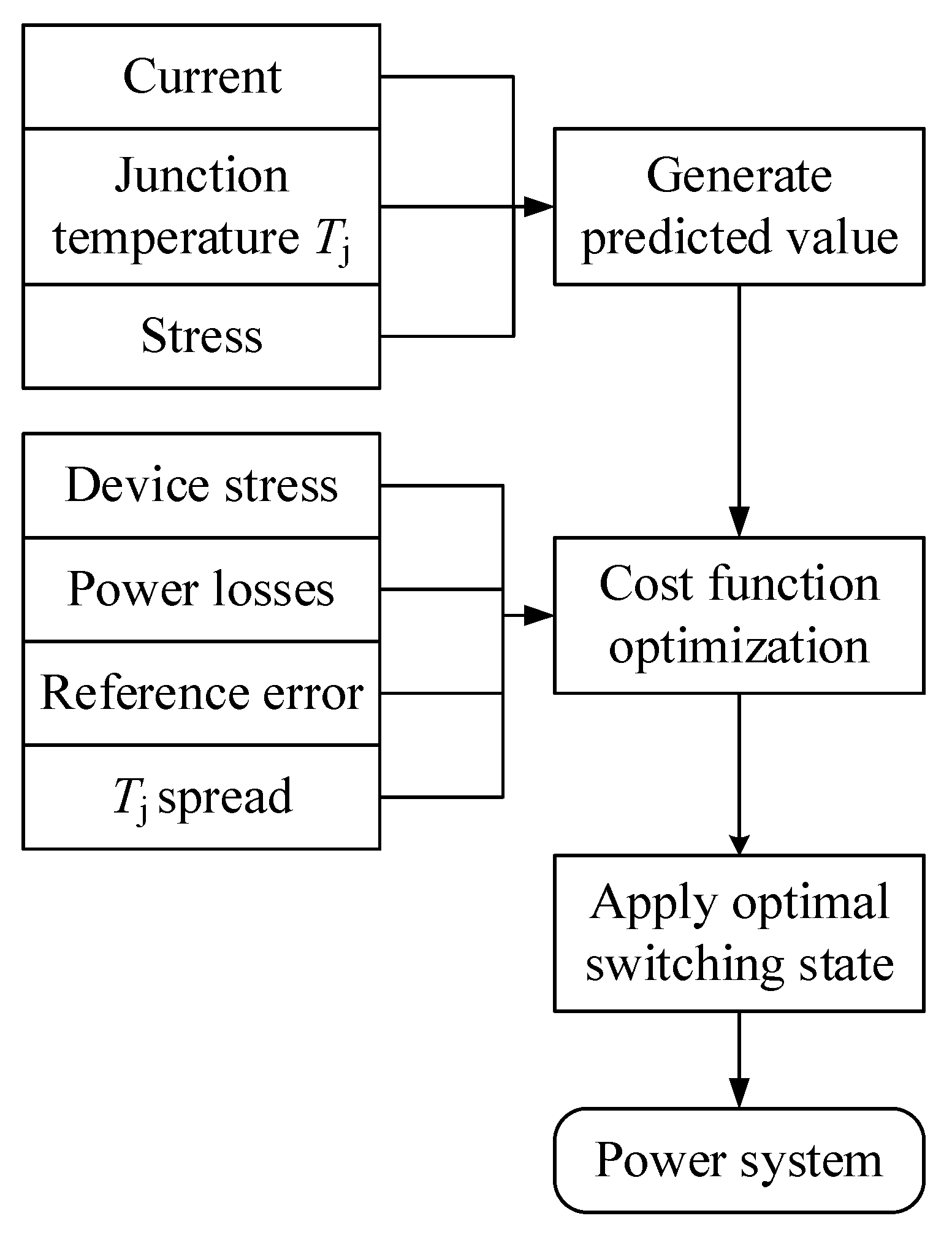

- Falck, J.; Buticchi, G.; Liserre, M. Thermal Stress Based Model Predictive Control of Electric Drives. IEEE Trans. Ind. Applicat. 2018, 54, 1513–1522. [Google Scholar] [CrossRef]

- Ozkan, G.; Papari, B.; Hoang, P.H.; Deb, N.; Edrington, C.S. An Active Thermal Control Method for AC-DC Power Converter with Sequence-based Control Approach. In Proceedings of the 2019 IEEE Electric Ship Technologies Symposium (ESTS), Washington, DC, USA, 14–16 August 2019; pp. 263–267. [Google Scholar]

- Liserre, M.; Andresen, M.; Costa, L.; Buticchi, G. Power Routing in Modular Smart Transformers: Active Thermal Control through Uneven Loading of Cells. IEEE Ind. Electron. Mag. 2016, 10, 43–53. [Google Scholar] [CrossRef]

- Ko, Y.; Andresen, M.; Buticchi, G.; Liserre, M. Power Routing for Cascaded H-Bridge Converters. IEEE Trans. Power Electron. 2017, 32, 9435–9446. [Google Scholar] [CrossRef]

- Andresen, M.; Raveendran, V.; Buticchi, G.; Liserre, M. Lifetime-Based Power Routing in Parallel Converters for Smart Transformer Application. IEEE Trans. Ind. Electron. 2018, 65, 1675–1684. [Google Scholar] [CrossRef]

- Raveendran, V.; Andresen, M.; Buticchi, G.; Liserre, M. Thermal Stress Based Power Routing of Smart Transformer With CHB and DAB Converters. IEEE Trans. Power Electron. 2020, 35, 4205–4215. [Google Scholar] [CrossRef]

- Li, J. Design and Control Optimisation of a Novel Bypass-embedded Multilevel Multicell Inverter for Hybrid Electric Vehicle Drives. In Proceedings of the 2020 IEEE 11th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Dubrovnik, Croatia, 28 September–1 October 2020; pp. 382–385. [Google Scholar]

- Wang, J.; Liu, X.; Xiao, Q.; Zhou, D.; Qiu, H.; Tang, Y. Modulated Model Predictive Control for Modular Multilevel Converters with Easy Implementation and Enhanced Steady-State Performance. IEEE Trans. Power Electron. 2020, 35, 9107–9118. [Google Scholar] [CrossRef]

- Nguyen, M.H.; Kwak, S.; Kim, T. Phase-Shifted Carrier Pulse-Width Modulation Algorithm with Improved Dynamic Performance for Modular Multilevel Converters. IEEE Access 2019, 7, 170949–170960. [Google Scholar] [CrossRef]

- Nguyen, M.H.; Kwak, S. Nearest-Level Control Method with Improved Output Quality for Modular Multilevel Converters. IEEE Access 2020, 8, 110237–110250. [Google Scholar] [CrossRef]

- Gutierrez, B.; Kwak, S.-S. Modular Multilevel Converters (MMCs) Controlled by Model Predictive Control with Reduced Calculation Burden. IEEE Trans. Power Electron. 2018, 33, 9176–9187. [Google Scholar] [CrossRef]

- Ronanki, D.; Williamson, S.S. A Novel 2N + 1 Carrier-Based Pulse Width Modulation Scheme for Modular Multilevel Converters with Reduced Control Complexity. IEEE Trans. Ind. Applicat. 2020, 56, 5593–5602. [Google Scholar] [CrossRef]

- Nguyen, M.H.; Kwak, S. Simplified Indirect Model Predictive Control Method for a Modular Multilevel Converter. IEEE Access 2018, 6, 62405–62418. [Google Scholar] [CrossRef]

- Wang, Z.; Wang, H.; Zhang, Y.; Blaabjerg, F. Submodule Level Power Loss Balancing Control for Modular Multilevel Converters. In Proceedings of the 2018 IEEE Energy Conversion Congress and Exposition (ECCE), Portland, OR, USA, 23–27 September 2018; pp. 5731–5736. [Google Scholar]

- Nguyen; Kwak Switching Loss Balancing Technique for Modular Multilevel Converters Operated by Model Predictive Control Method. Electronics 2019, 8, 1175. [CrossRef]

- Sangwongwanich, A.; Mathe, L.; Teodorescu, R.; Lascu, C.; Harnefors, L. Two-dimension sorting and selection algorithm featuring thermal balancing control for modular multilevel converters. In Proceedings of the 2016 18th European Conference on Power Electronics and Applications (EPE’16 ECCE Europe), Karlsruhe, Germany, 5–9 September 2016; pp. 1–10. [Google Scholar]

- Hahn, F.; Andresen, M.; Buticchi, G.; Liserre, M. Thermal Analysis and Balancing for Modular Multilevel Converters in HVDC Applications. IEEE Trans. Power Electron. 2018, 33, 1985–1996. [Google Scholar] [CrossRef]

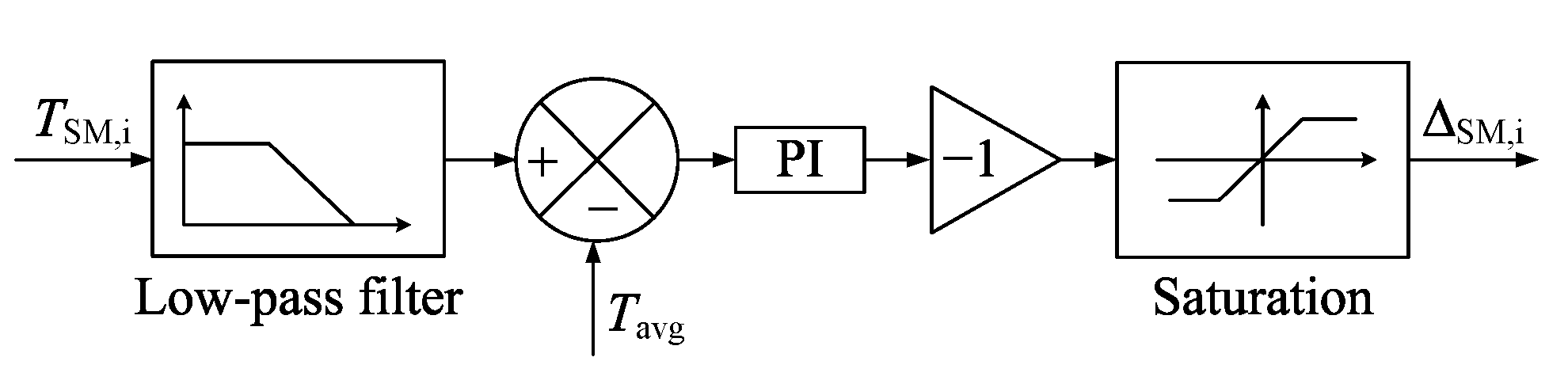

- Goncalves, J.; Rogers, D.J.; Liang, J. Submodule Temperature Regulation and Balancing in Modular Multilevel Converters. IEEE Trans. Ind. Electron. 2018, 65, 7085–7094. [Google Scholar] [CrossRef]

- Hagiwara, M.; Akagi, H. Control and Experiment of Pulsewidth-Modulated Modular Multilevel Converters. IEEE Trans. Power Electron. 2009, 24, 1737–1746. [Google Scholar] [CrossRef]

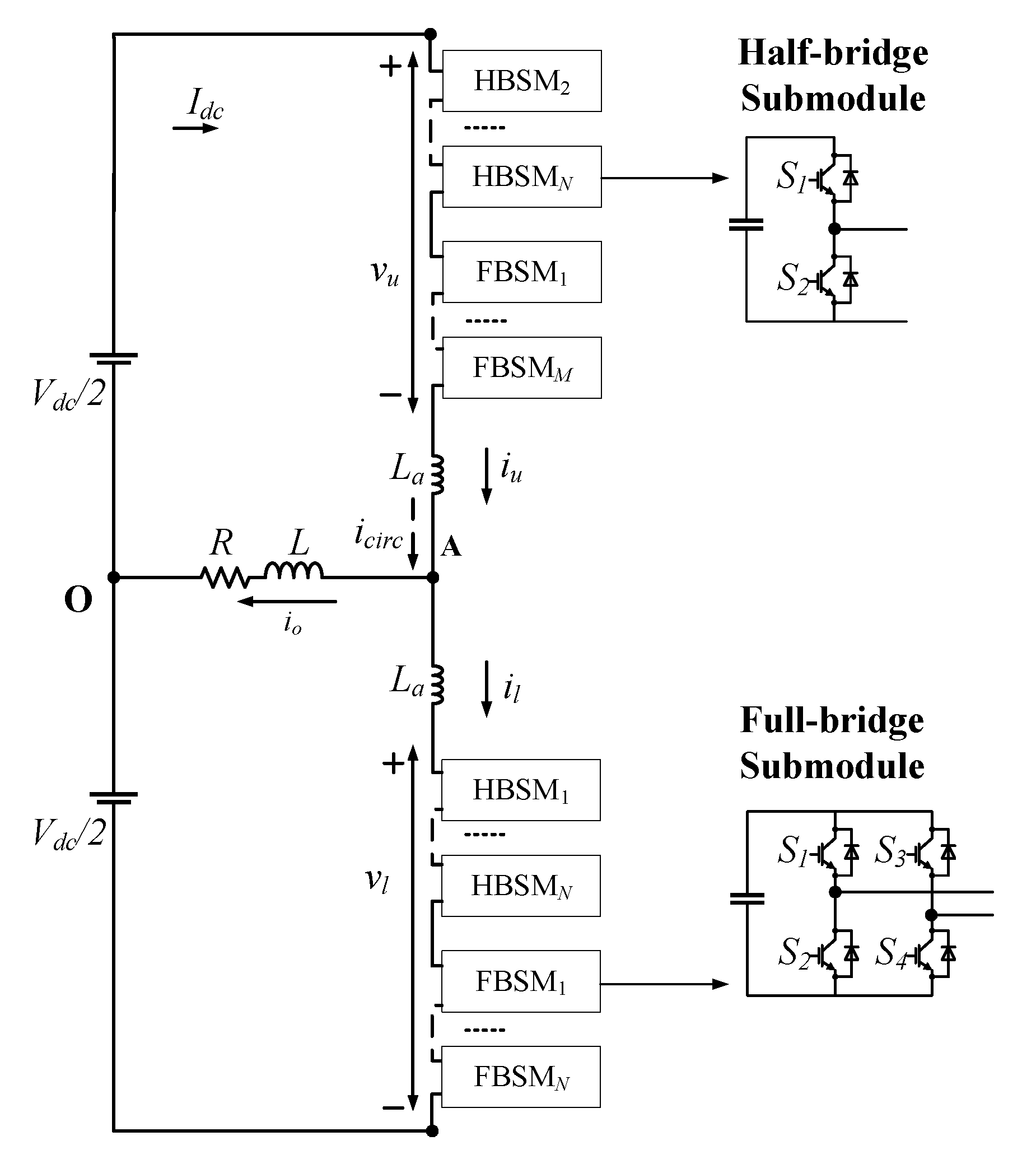

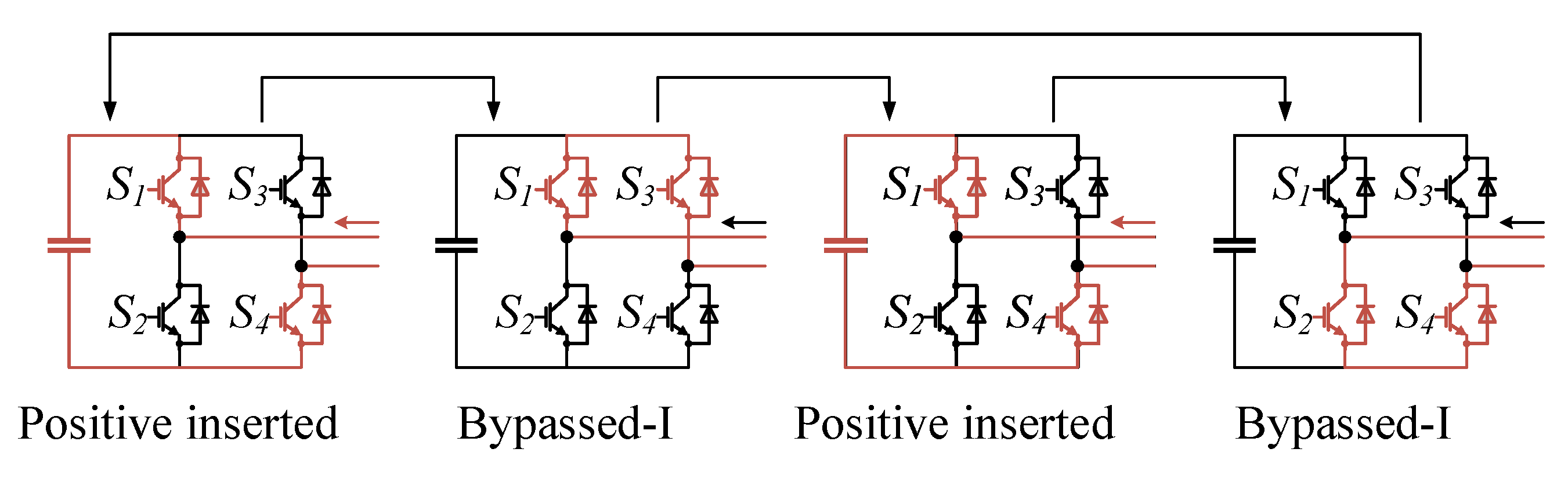

- Sheng, J.; Yang, H.; Li, C.; Chen, M.; Li, W.; He, X.; Gu, X. Active Thermal Control for Hybrid Modular Multilevel Converter Under Overmodulation Operation. IEEE Trans. Power Electron. 2020, 35, 4242–4255. [Google Scholar] [CrossRef]

- Nesgaard, C.; Andersen, M.A.E. Optimized load sharing control by means of thermal reliability management. In Proceedings of the 2004 IEEE 35th Annual Power Electronics Specialists Conference (IEEE Cat. No.04CH37551), Aachen, Germany, 20–25 June 2004; pp. 4901–4906. [Google Scholar]

- Joseph, C.J.J.; Zolghadri, M.R.; Homaifar, A.; Lee, F.; Lorenz, R.D. Novel thermal based current sharing control of parallel converters. In Proceedings of the 2004 10th International Workshop on Computational Electronics (IEEE Cat. No.04EX915), Chicago, IL, USA, 19–23 September 2004; pp. 647–653. [Google Scholar]

- Barnette, J.L.; Zolghadri, M.R.; Walters, M.; Homaifar, A. Temperature Integrated Load Sharing of Paralleled Modules. In Proceedings of the 2006 1st IEEE Conference on Industrial Electronics and Applications, Singapore, 24–26 May 2006; pp. 1–6. [Google Scholar]

- Guerrero, J.M.; Vasquez, J.C.; Matas, J.; de Vicuna, L.G.; Castilla, M. Hierarchical Control of Droop-Controlled AC and DC Microgrids—A General Approach Toward Standardization. IEEE Trans. Ind. Electron. 2011, 58, 158–172. [Google Scholar] [CrossRef]

- Peyghami, S.; Mokhtari, H.; Blaabjerg, F. Decentralized Load Sharing in a Low-Voltage Direct Current Microgrid with an Adaptive Droop Approach Based on a Superimposed Frequency. IEEE J. Emerg. Sel. Top. Power Electron. 2017, 5, 1205–1215. [Google Scholar] [CrossRef]

- Peyghami, S.; Davari, P.; Blaabjerg, F. System-level lifetime-oriented power sharing control of paralleled DC/DC converters. In Proceedings of the 2018 IEEE Applied Power Electronics Conference and Exposition (APEC), San Antonio, TX, USA, 4–8 March 2018; pp. 1890–1895. [Google Scholar]

- Marquez, A.; Leon, J.I.; Vazquez, S.; Franquelo, L.G. Closed-loop active thermal control via power routing of parallel DC-DC converters. In Proceedings of the 2018 IEEE 12th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG 2018), Doha, Qatar, 10–12 April 2018; pp. 1–6. [Google Scholar]

- Yan, H.; Buticchi, G.; Yang, J.; Zhao, W.; Zhang, H.; Gerada, C. Active Thermal Control for Power Converters in Modular Winding Permanent Magnet Synchronous Motor. In Proceedings of the 2019 IEEE 13th International Conference on Compatibility, Power Electronics and Power Engineering (CPE-POWERENG), Sonderborg, Denmark, 23–25 April 2019; pp. 1–6. [Google Scholar]

- Zhang, J.; Chen, G.; Cai, X. Thermal smooth control for Multi-MW parallel wind power converter. In Proceedings of the 2013 IEEE International Conference of IEEE Region 10 (TENCON 2013), Xi’an, China, 22–25 October 2013; pp. 1–4. [Google Scholar]

- Zhang, J.; Li, Y.; Wang, H.; Cai, X.; Igarashi, S.; Wang, Z. Thermal smooth control based on orthogonal circulating current for multi-MW parallel wind power converter. In Proceedings of the 2014 International Power Electronics and Application Conference and Exposition, Shanghai, China, 5–8 November 2014; pp. 146–151. [Google Scholar]

- Zhang, J.; Wang, J.; Cai, X. Active Thermal Control-Based Anticondensation Strategy in Paralleled Wind Power Converters by Adjusting Reactive Circulating Current. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 277–291. [Google Scholar] [CrossRef]

- Ma, K.; Liserre, M.; Blaabjerg, F. Reactive Power Influence on the Thermal Cycling of Multi-MW Wind Power Inverter. IEEE Trans. Ind. Applicat. 2013, 49, 922–930. [Google Scholar] [CrossRef]

- Ahmadzadeh, F.; Lundberg, J. Remaining useful life estimation: Review. Int. J. Syst. Assur. Eng. Manag. 2014, 5, 461–474. [Google Scholar] [CrossRef]

- Manson, S.S.; Dolan, T.J. Thermal Stress and Low Cycle Fatigue. J. Appl. Mech. 1966, 33, 957. [Google Scholar] [CrossRef]

- Bayerer, R.; Herrmann, T.; Licht, T.; Lutz, J.; Feller, M. Model for Power Cycling lifetime of IGBT Modules-various factors influencing lifetime. In Proceedings of the 5th International Conference on Integrated Power Electronics Systems, Nuremberg, Germany, 11–13 March 2008; pp. 1–6. [Google Scholar]

- Rychlik, I. A new definition of the rainflow cycle counting method. Int. J. Fatigue 1987, 9, 119–121. [Google Scholar] [CrossRef]

- Miner, M.A. Cumulative damage in fatigue. J. Appl. Mech. 1945, 12, A159–A164. [Google Scholar]

- Ma, K.; Liserre, M.; Blaabjerg, F.; Kerekes, T. Thermal Loading and Lifetime Estimation for Power Device Considering Mission Profiles in Wind Power Converter. IEEE Trans. Power Electron. 2015, 30, 590–602. [Google Scholar] [CrossRef]

- Ji, H.; Li, H.; Li, Y.; Yang, L.; Lei, G.; Xiao, H.; Zhao, J.; Shi, L. A Reliability Evaluation Model for the Power Devices Used in Power Converter Systems Considering the Effect of the Different Time Scales of the Wind Speed Profile. J. Power Electron. 2016, 16, 685–694. [Google Scholar] [CrossRef]

- Shipurkar, U.; Lyrakis, E.; Ma, K.; Polinder, H.; Ferreira, J.A. Lifetime Comparison of Power Semiconductors in Three-Level Converters for 10-MW Wind Turbine Systems. IEEE J. Emerg. Sel. Top. Power Electron. 2018, 6, 1366–1377. [Google Scholar] [CrossRef]

- Ma, K. Electro-Thermal Model of Power Semiconductors Dedicated for Both Case and Junction Temperature Estimation. In Power Electronics for the Next Generation Wind Turbine System; Research Topics in Wind Energy; Springer International Publishing: Cham, Switzerland, 2015; Volume 5, pp. 139–143. [Google Scholar]

- Liu, H.; Ma, K.; Qin, Z.; Loh, P.C.; Blaabjerg, F. Lifetime Estimation of MMC for Offshore Wind Power HVDC Application. IEEE J. Emerg. Sel. Top. Power Electron. 2016, 4, 504–511. [Google Scholar] [CrossRef]

- Kovacevic, I.F.; Drofenik, U.; Kolar, J.W. New physical model for lifetime estimation of power modules. In Proceedings of the the 2010 International Power Electronics Conference—ECCE ASIA, Sapporo, Japan, 21–24 June 2010; pp. 2106–2114. [Google Scholar]

- Dusmez, S.; Duran, H.; Akin, B. Remaining Useful Lifetime Estimation for Thermally Stressed Power MOSFETs Based on on-State Resistance Variation. IEEE Trans. Ind. Applicat. 2016, 52, 2554–2563. [Google Scholar] [CrossRef]

- Dusmez, S.; Heydarzadeh, M.; Nourani, M.; Akin, B. Remaining Useful Lifetime Estimation for Power MOSFETs under Thermal Stress with RANSAC Outlier Removal. IEEE Trans. Ind. Inf. 2017, 13, 1271–1279. [Google Scholar] [CrossRef]

- Ali, S.H.; Heydarzadeh, M.; Dusmez, S.; Li, X.; Kamath, A.S.; Akin, B. Lifetime Estimation of Discrete IGBT Devices Based on Gaussian Process. IEEE Trans. Ind. Applicat. 2018, 54, 395–403. [Google Scholar] [CrossRef]

| Failure Types | Mechanism | Indicators | ||

|---|---|---|---|---|

| IGBT | SiC MOSFET | IGBT | SiC MOSFET | |

| Gate oxide | High temperature, high electric field |

| ||

| ||||

| Body diode | Forward voltage bias stress |

| ||

| Bond wire fatigue | Combination of CTE mismatch and temperature fluctuation |

| ||

|

| |||

| Solder layer fatigue | Combination of CTE mismatch and temperature fluctuation |

| ||

|

| |||

| Static parameters | Collector-emitter voltage under high currents |

| Collector-emitter voltage under high currents | |

| Gate internal resistance | |

| Short circuit current | |

| Gate-emitter voltage | |

| Dynamic parameters | Threshold voltage |

| Miller Plateau voltage | |

| Turn-on/turn off delay time |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nguyen, M.H.; Kwak, S. Enhance Reliability of Semiconductor Devices in Power Converters. Electronics 2020, 9, 2068. https://doi.org/10.3390/electronics9122068

Nguyen MH, Kwak S. Enhance Reliability of Semiconductor Devices in Power Converters. Electronics. 2020; 9(12):2068. https://doi.org/10.3390/electronics9122068

Chicago/Turabian StyleNguyen, Minh Hoang, and Sangshin Kwak. 2020. "Enhance Reliability of Semiconductor Devices in Power Converters" Electronics 9, no. 12: 2068. https://doi.org/10.3390/electronics9122068

APA StyleNguyen, M. H., & Kwak, S. (2020). Enhance Reliability of Semiconductor Devices in Power Converters. Electronics, 9(12), 2068. https://doi.org/10.3390/electronics9122068