A Negative Charge Pump Using Enhanced Pumping Clock for Low-Voltage DRAM

Abstract

1. Introduction

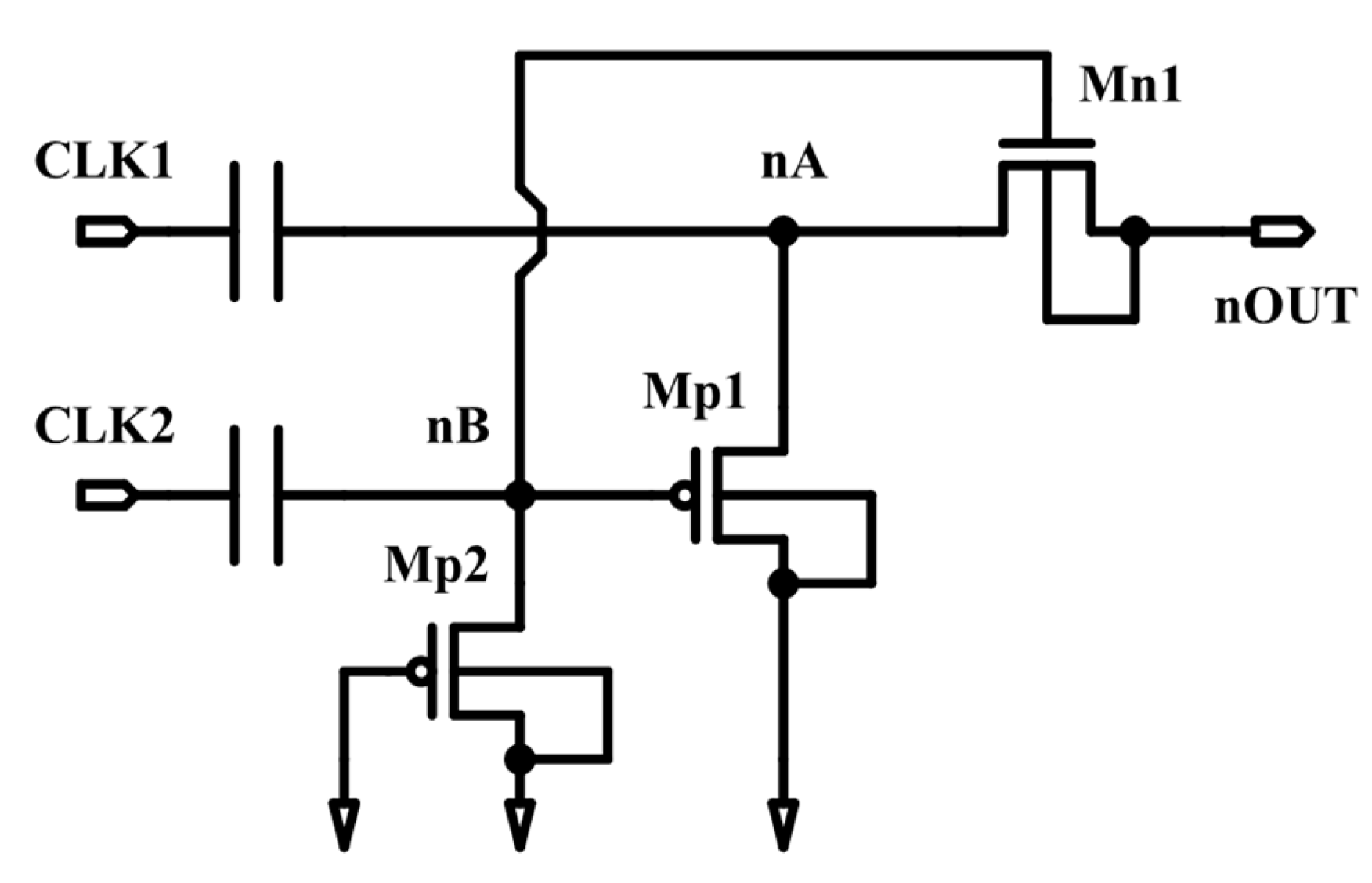

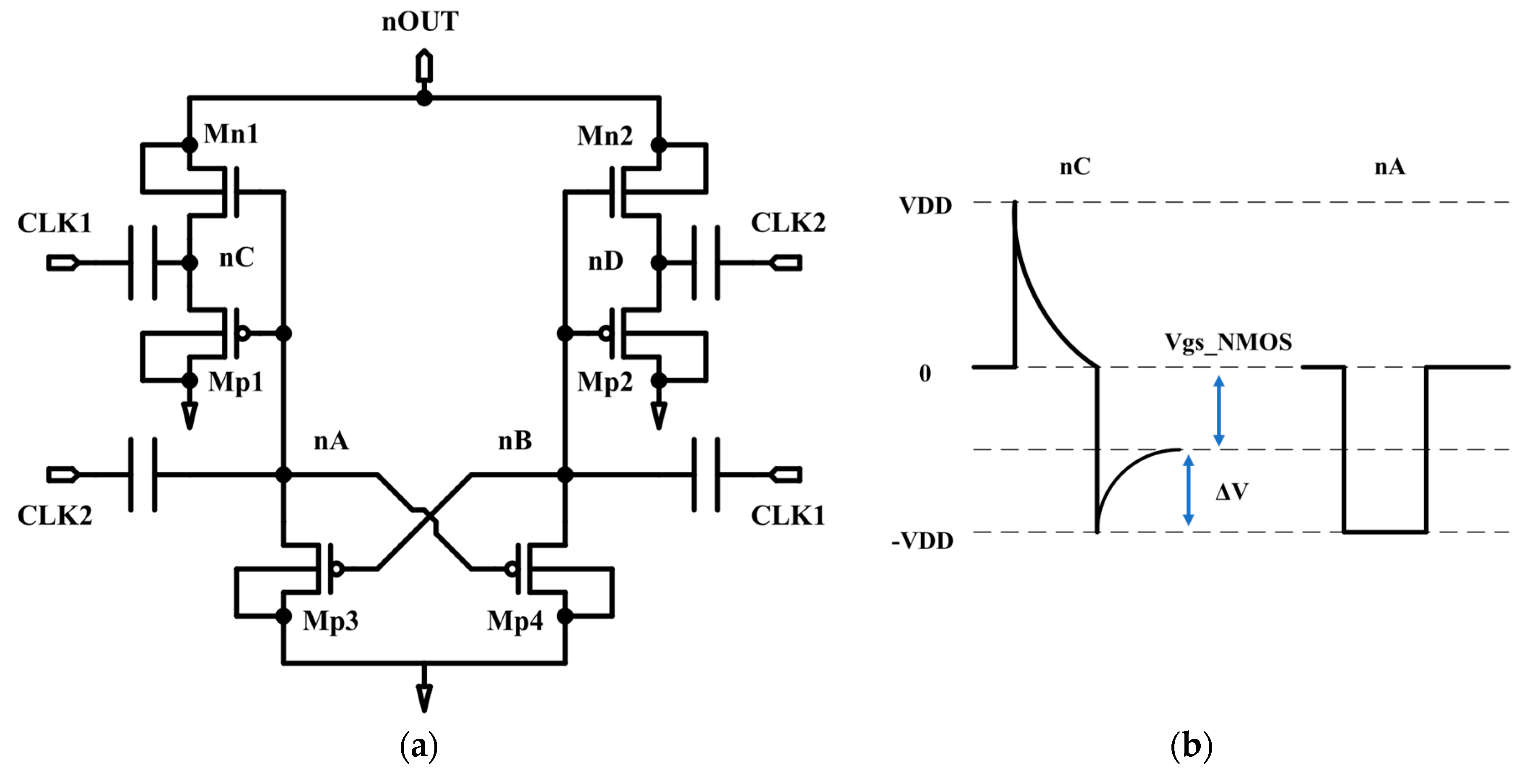

2. Conventional Negative Charge Pump Circuits

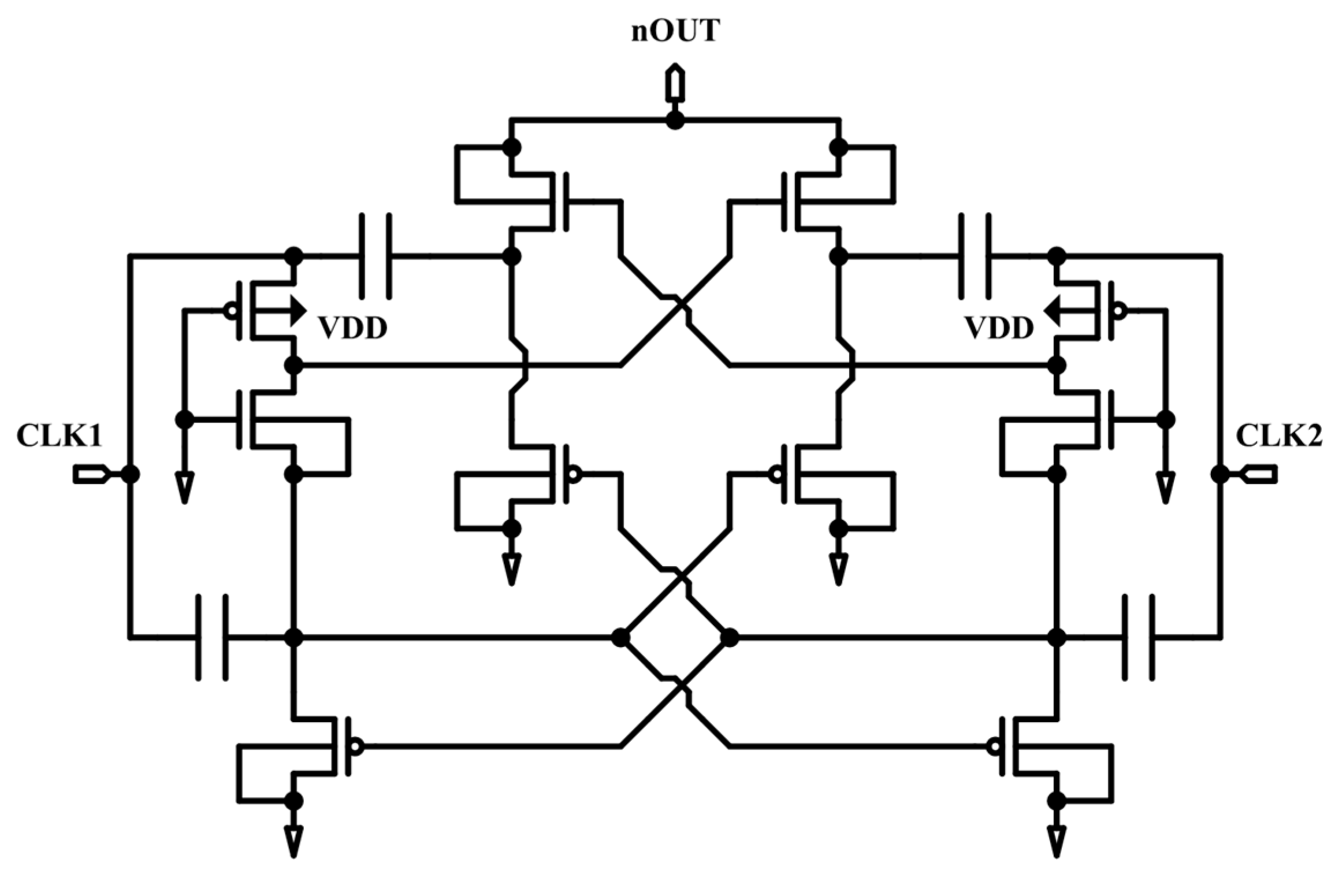

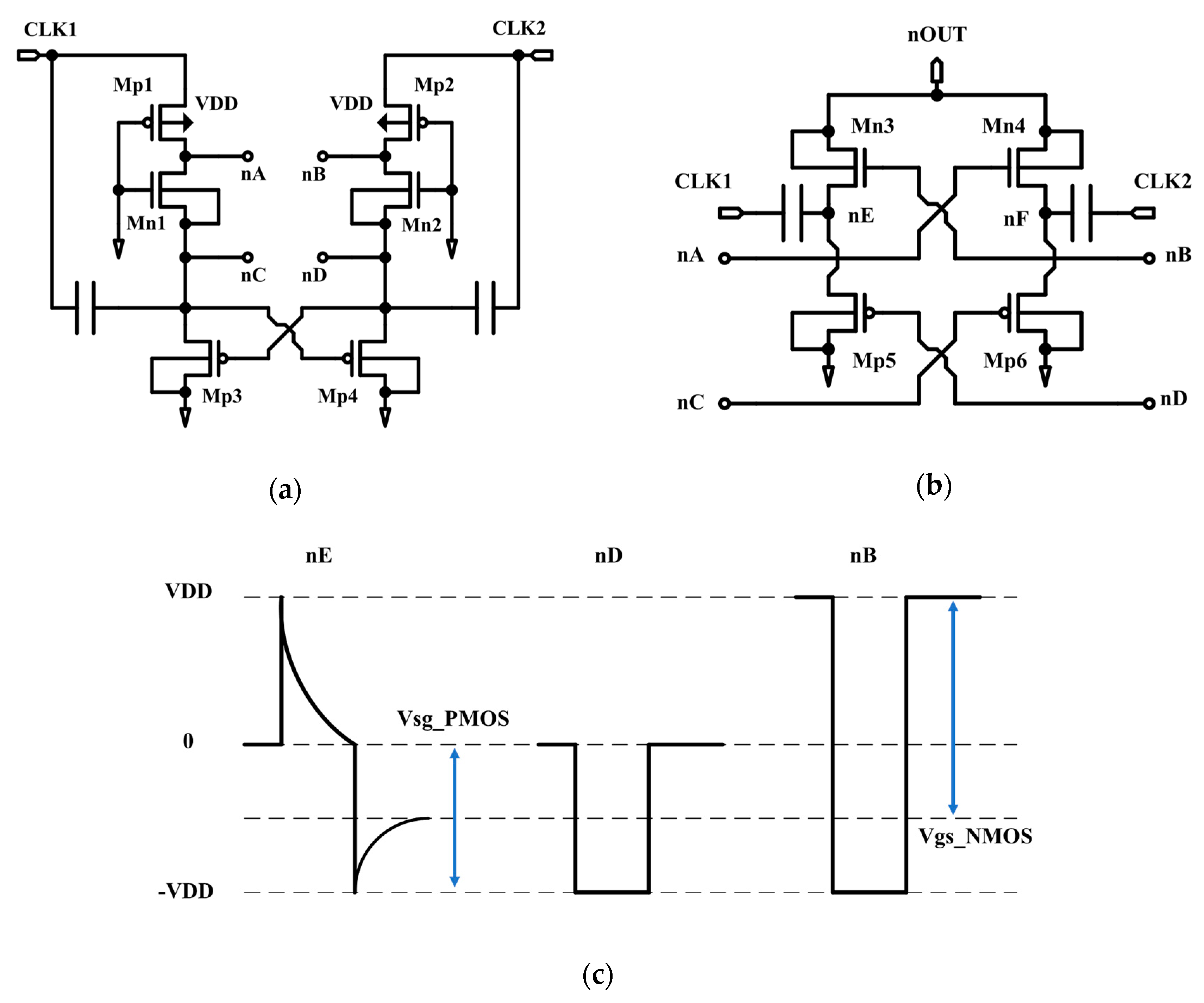

3. Enhanced Clock Pump Circuit (ECPC)

4. Simulation Results

4.1. Pump down Speed

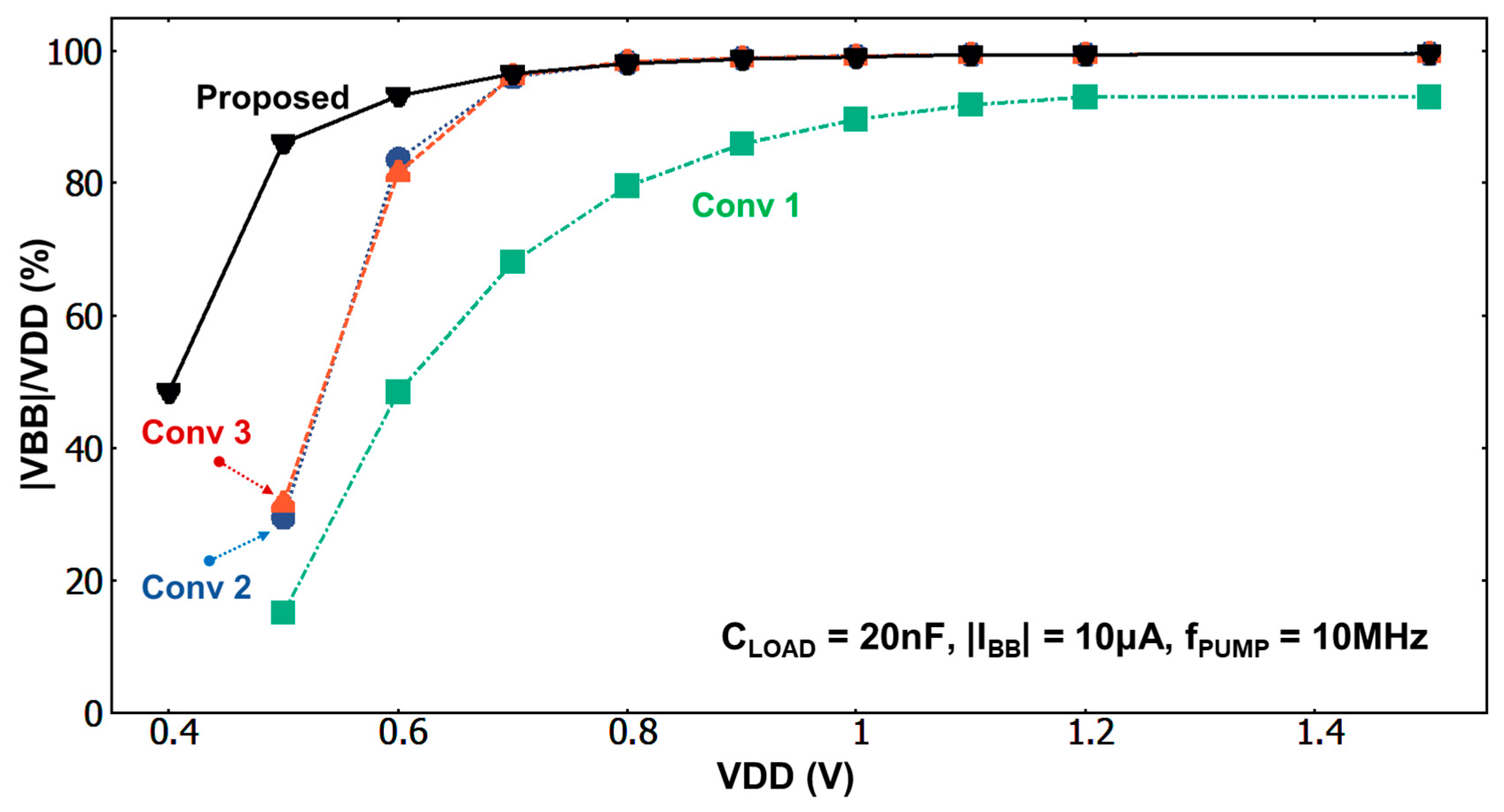

4.2. |VBB|/VDD Ratio

4.3. Pumping Current Comparison with Various VBB

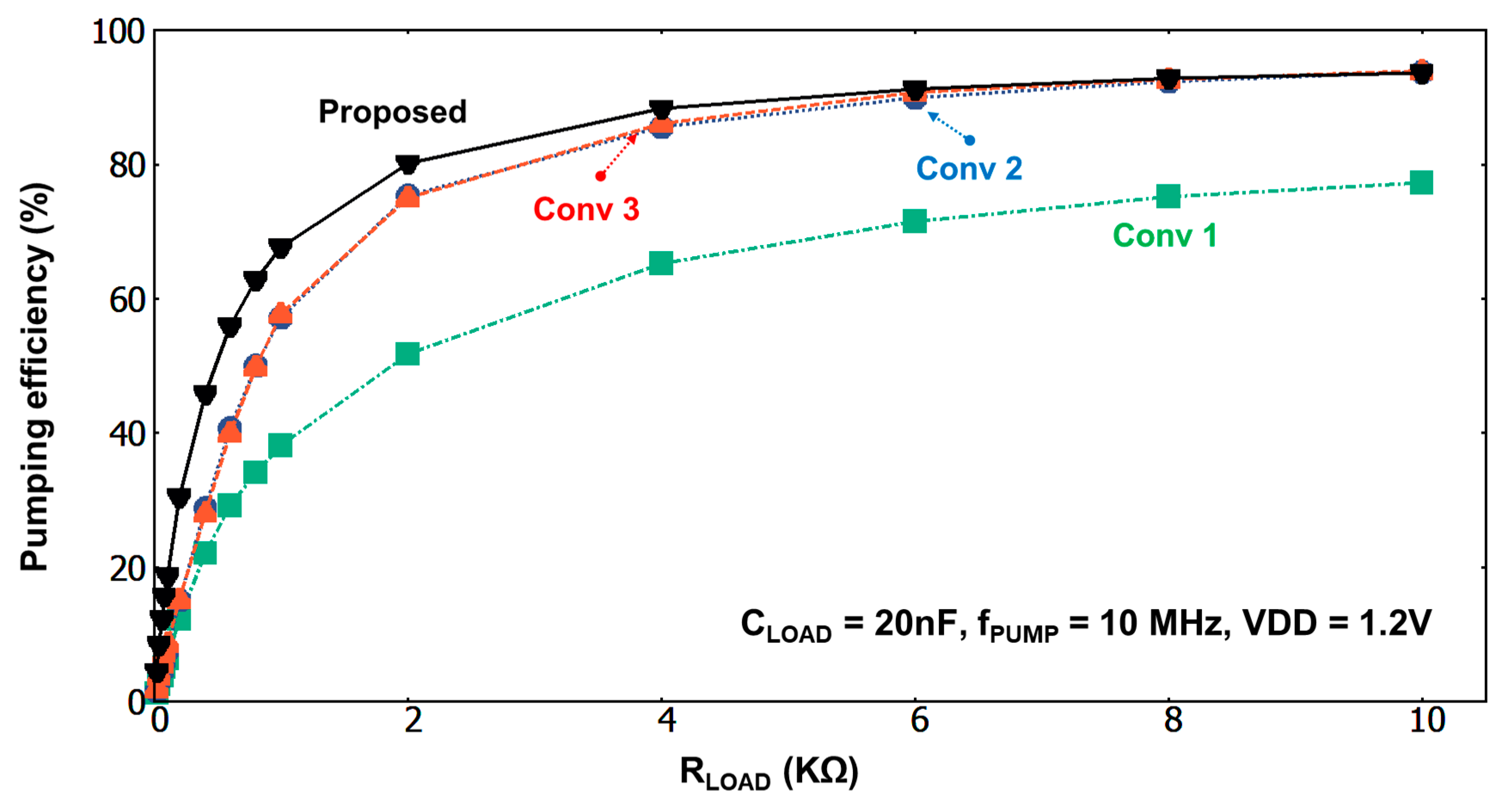

4.4. Pumping Efficiency with Various RLOAD

4.5. Power Loss Estimation

5. Discussion

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Takashima, D.; Watanabe, S.; Nakano, H.; Oowaki, Y.; Ohuchi, K.; Tango, H. Standby/active mode logic for sub-1-V operating ULSI memory. IEEE J. Solid-State Circuits 1994, 29, 441–447. [Google Scholar] [CrossRef]

- Kuroda, T.; Fujita, T.; Mita, S.; Nagamatsu, T.; Yoshioka, S.; Suzuki, K.; Sano, F.; Norishima, M.; Murota, M.; Kako, M.; et al. A 0.9-V, 150-MHz, 10-mW, 4 mm2, 2-D discrete cosine transform core processor with variable threshold-voltage (VT) scheme. IEEE J. Solid-State Circuits 1996, 31, 1770–1779. [Google Scholar] [CrossRef]

- Srivastava, A.; Zhang, C. An adaptive body-bias generator for low voltage CMOS VLSI circuits. Int. J. Distrib. Sens. Netw. 2008, 4, 213–222. [Google Scholar] [CrossRef]

- Martino, W.L.; Moench, J.D.; Bormann, A.R.; Tesch, R.C. An on-chip back-bias generator for MOS dynamic memory. IEEE J. Solid-State Circuits 1980, 15, 820–826. [Google Scholar] [CrossRef]

- Seung-Wuk, K.; Seung-Hoon, L.; Jong-Du, J.; Bong-Gyun, K.; Byung-Geun, S.; Jae-Geun, P.; Kae-Dal, K. A novel substrate-bias generator for low-power and high-speed DRAMs. In Proceedings of the IEEE Region 10 Conference. TENCON 99. ‘Multimedia Technology for Asia-Pacific Information Infrastructure’ (Cat. No.99CH37030), Cheju Island, Korea, 15–17 September 1999; Volume 862, pp. 864–867. [Google Scholar]

- Kim, Y.H.; Park, H.J.; Sohn, J.D.; Choi, J.S.; Park, C.S.; Ahn, S.H.; Jeong, J.Y. Two-phase back-bias generator for low-voltage gigabit DRAMs. Electron. Lett. 1998, 34, 1831–1833. [Google Scholar] [CrossRef]

- Kyeong-Sik, M.; Jin-Yong, C. A fast pump-down VBB generator for sub-1.5-V DRAMs. IEEE J. Solid-State Circuits 2001, 36, 1154–1157. [Google Scholar] [CrossRef]

- Shiratake, S. Scaling and performance challenges of future DRAM. In Proceedings of the 2020 IEEE International Memory Workshop (IMW), Dresden, Germany, 17–20 May 2020. [Google Scholar]

- Sato, K.; Kawamoto, H.; Yanagisawa, K.; Matsumoto, T.; Shimizu, S.; Hori, R. A 20ns static column 1Mb DRAM in CMOS technology. In Proceedings of the 1985 IEEE International Solid-State Circuits Conference, Digest of Technical Papers, New York, NY, USA, 13–15 February 1985. [Google Scholar]

- Tsukikawa, Y.; Kajimoto, T.; Okasaka, Y.; Morooka, Y.; Furutani, K.; Miyamoto, H.; Ozaki, H. An efficient back-bias generator with hybrid pumping circuit for 1.5-V DRAMs. IEEE J. Solid-State Circuits 1994, 29, 534–538. [Google Scholar] [CrossRef]

- Cho, C.; Cha, J.; Ahn, M.; Kim, J.J.; Lee, C. Negative charge-pump based antenna switch controller using 0.18 μm SOI CMOS technology. Electron. Lett. 2011, 47, 371–372. [Google Scholar] [CrossRef]

- Tan, Y.; Zhan, C.; Wang, G. A fully-on-chip analog low-dropout regulator with negative charge pump for low-voltage applications. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1361–1365. [Google Scholar] [CrossRef]

- Justo, D.; Cavalheiro, D.; Moll, F. Body bias generators for ultra low voltage circuits in FDSOI technology. In Proceedings of the 2017 32nd Conference on Design of Circuits and Integrated Systems (DCIS), Barcelona, Spain, 22–24 November 2017; pp. 1–6. [Google Scholar]

- Tan, Y.; Zhan, C.; Wang, G. A fully-on-chip low-voltage low-dropout regulator with negative charge pump. In Proceedings of the 2018 IEEE International Conference on Electron Devices and Solid State Circuits (EDSSC), Shenzhen, China, 6–8 June 2018; pp. 1–2. [Google Scholar]

- Kyeong-Sik, M.; Kyo-Won, J.; Ji-Beom, K. A high-efficiency back-bias generator with cross-coupled hybrid pumping circuit for sub-1.5 V DRAM applications. In Proceedings of the 26th European Solid-State Circuits Conference, Stockholm, Sweden, 19–21 September 2000; pp. 188–191. [Google Scholar]

- Matoušek, D.; Beran, L. Comparison of positive and negative Dickson charge pump and Fibonacci charge pump. In Proceedings of the 2017 International Conference on Applied Electronics (AE), Pilsen, Czech Republic, 5–6 September 2017; pp. 1–4. [Google Scholar]

- Ballo, A.; Grasso, A.D.; Palumbo, G. A review of charge pump topologies for the power management of IoT nodes. Electronics 2019, 8, 480. [Google Scholar] [CrossRef]

- Chi-Chang, W.; Jiin-Chuan, W. Efficiency improvement in charge pump circuits. IEEE J. Solid-State Circuits 1997, 32, 852–860. [Google Scholar] [CrossRef]

| Conv 1 (HPC) | Conv 2 (CHPC1) | Conv 3 (CHPC2) | Proposed | |

|---|---|---|---|---|

| Topology | Bootstrap | Cross-coupled | Cross-coupled with gate biasing | Cross-coupled with clock boosting |

| |VBB|/VDD ratio | 48.5% | 83.6% | 81.6% | 93.2% |

| Pump-down speed | 177.8 μs | 176.4 μs | 178.7 μs | 120.0 μs |

| Pumping current at VBB = 0 V | 57.7 μA | 79.9 μA | 89.8 μA | 471.6 μA |

| Pumping efficiency at RL = 10 kΩ | 34.7% | 48.1% | 46.0% | 81.1% |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, C.; Yim, T.; Yoon, H. A Negative Charge Pump Using Enhanced Pumping Clock for Low-Voltage DRAM. Electronics 2020, 9, 1769. https://doi.org/10.3390/electronics9111769

Lee C, Yim T, Yoon H. A Negative Charge Pump Using Enhanced Pumping Clock for Low-Voltage DRAM. Electronics. 2020; 9(11):1769. https://doi.org/10.3390/electronics9111769

Chicago/Turabian StyleLee, Choongkeun, Taegun Yim, and Hongil Yoon. 2020. "A Negative Charge Pump Using Enhanced Pumping Clock for Low-Voltage DRAM" Electronics 9, no. 11: 1769. https://doi.org/10.3390/electronics9111769

APA StyleLee, C., Yim, T., & Yoon, H. (2020). A Negative Charge Pump Using Enhanced Pumping Clock for Low-Voltage DRAM. Electronics, 9(11), 1769. https://doi.org/10.3390/electronics9111769