Fault Modeling of Graphene Nanoribbon FET Logic Circuits

Abstract

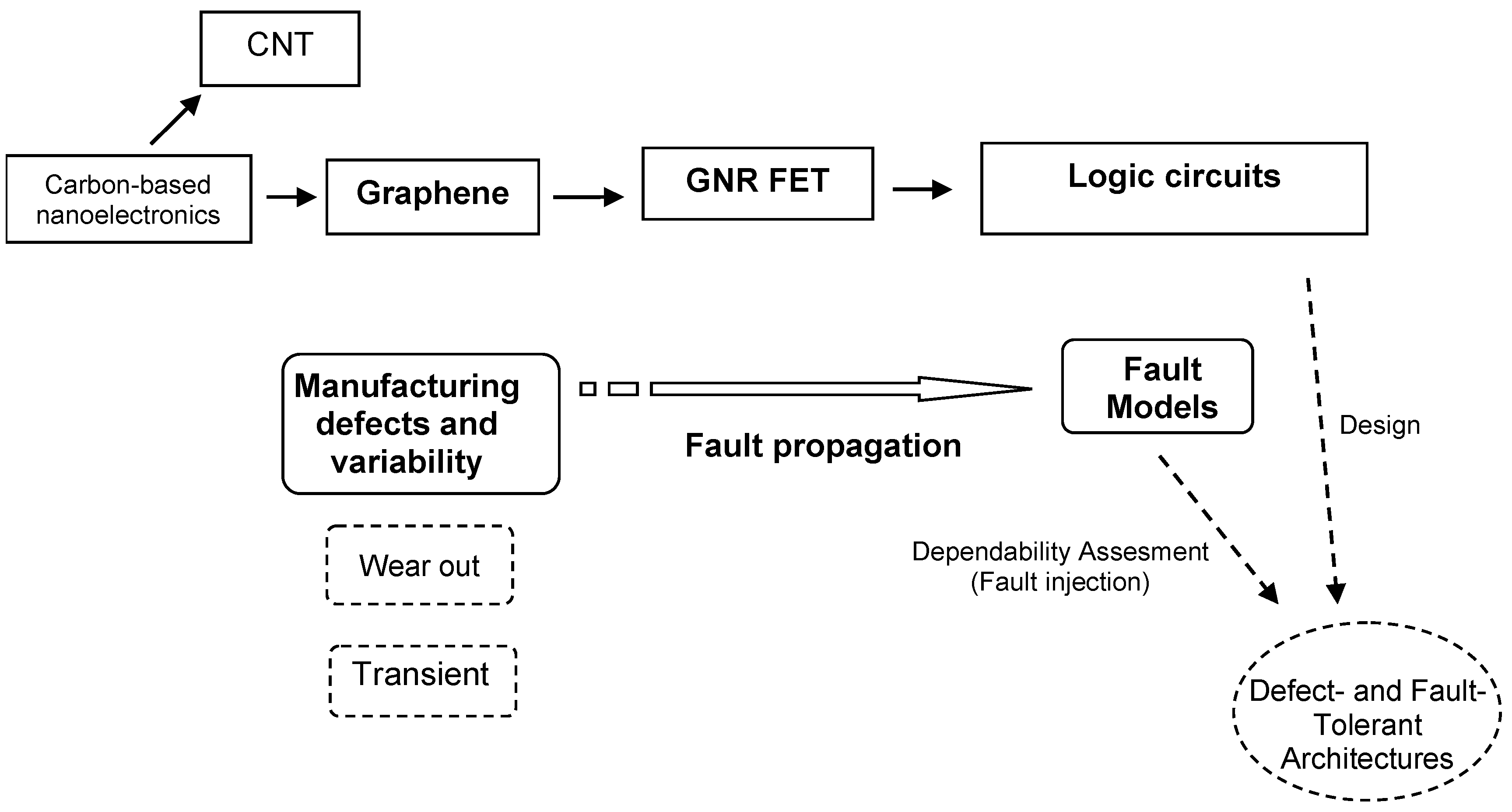

1. Introduction

- Device fabrication. It may be difficult to extend optical lithography into the realm of low tens of nanometers. Furthermore, random process variations can lead to device characteristics that are unpredictable.

- Device operation. As dimensions are reduced, voltage levels also need to be reduced accordingly. This fact increases the subthreshold static power of the metal–oxide–semiconductor field-effect transistors (MOSFETs). In addition, conventional MOSFETs will behave differently, appearing quantum effects, such as tunneling and ballistic transport.

- Heat dissipation. As device density increases, heat dissipation becomes a major problem, reducing circuit reliability and leading to shorter device lifetimes, or even to device failure.

- Identifying a wide set of fault causes and mechanisms in GNR FET devices. This constitutes a deep review task, necessary to develop points 2 and 3.

- Analyzing the fault propagation and modeling faults at the logic level. This phase is done based on the previous point, and the structure and equations of digital circuits. Fault modeling opens the possibility of evaluating the reliability of defect-tolerant nanoarchitectures by means of fault injection at a manageable cost.

- Comparing the fault models with other emerging devices, namely, CNT FETs and NW FETs. They are also promising devices for future digital applications.

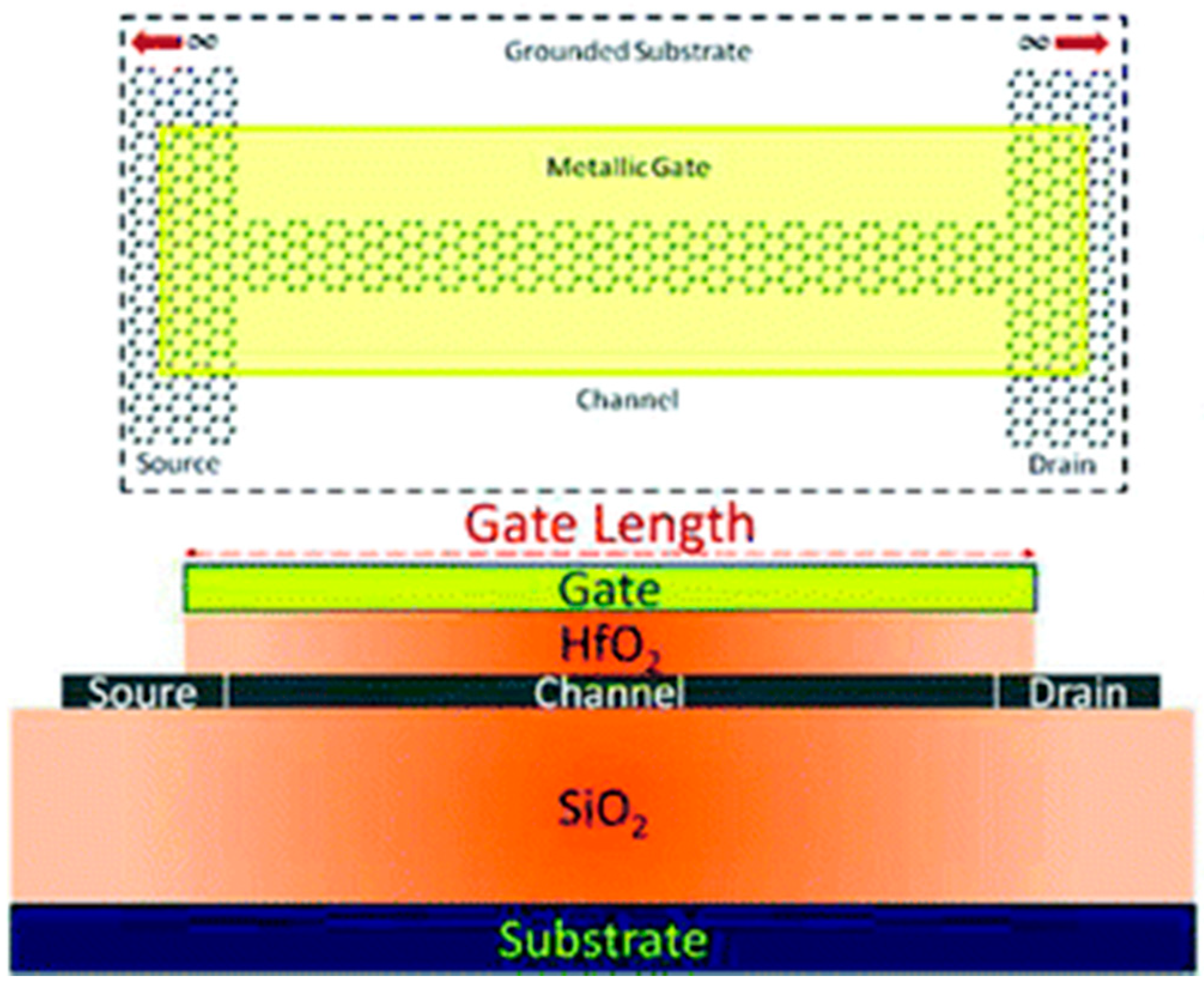

2. Graphene Nanoribbon Devices

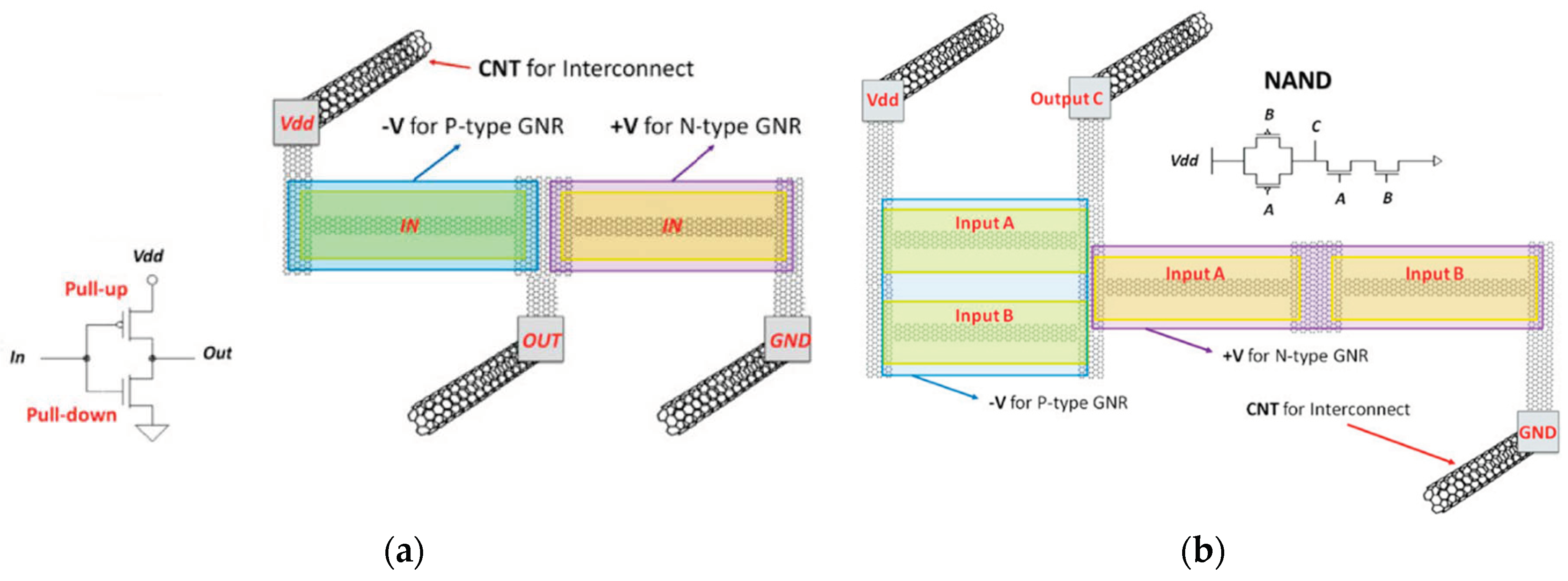

3. Graphene Nanoribbon Logic Circuits

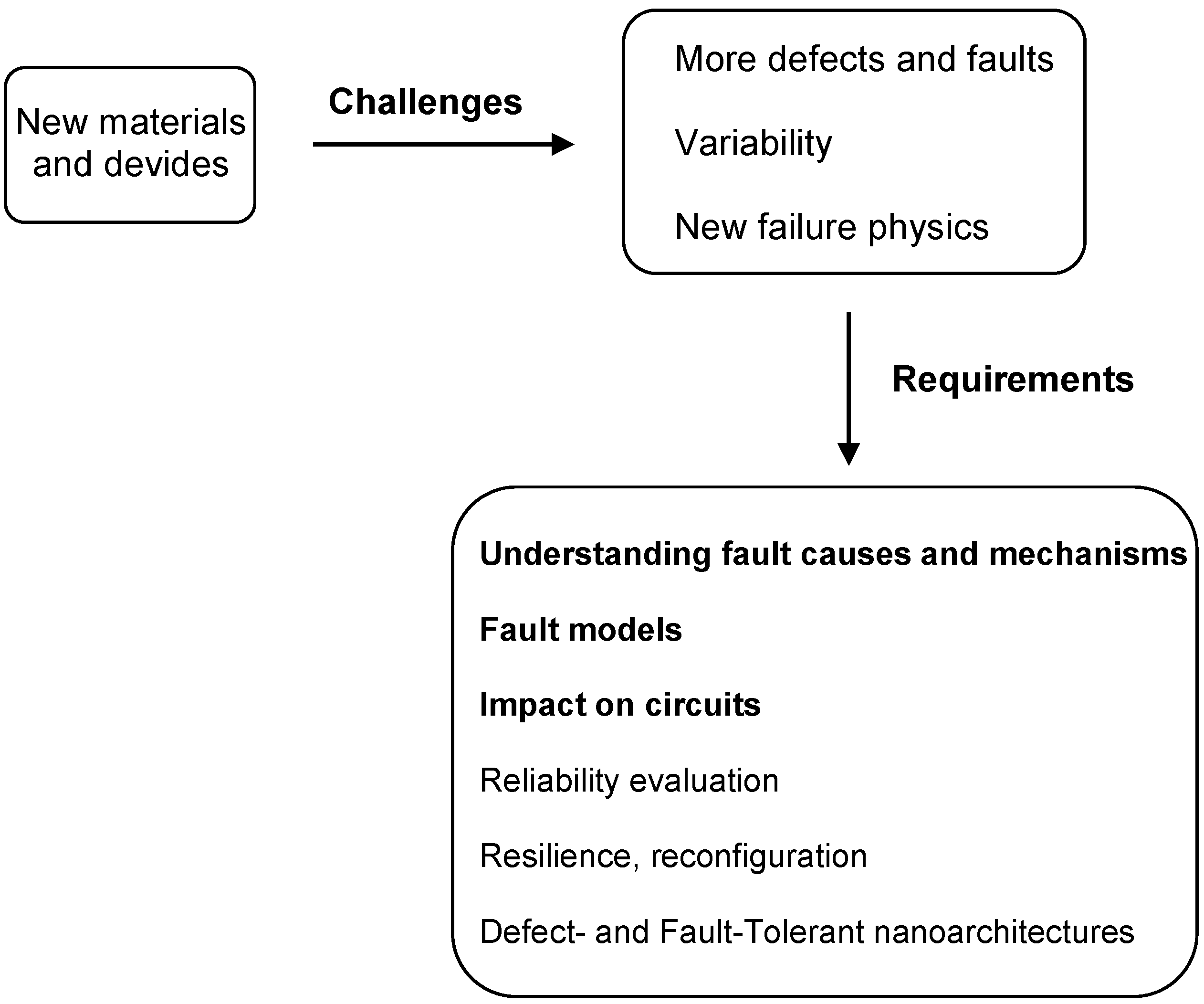

4. Reliability Challenges and Requirements

5. Fault Causes, Mechanisms, and Models

- Study of the impact of defects and faults on GNR FETs. Generation of fault models at the device (transistor) level. In this step, we analyzed the equations of the devices and their parameters.

- Study of fault propagation from the device level to the (logic) circuit level. Generation of fault models at the logic circuit level. This step is based on the structure of logic circuits made of transistors.

5.1. Manufacturing Variations

5.1.1. Ribbon Width

- Power degradation. GNR FET ON current scales proportionally with width W, whereas the OFF current has an exponential dependency [10]:where: Eg = GNR bandgap, K = Boltzmann constant, T = temperature.

- Noise margin degradation. The second effect is a significantly diminishing noise margin. Band-to-band tunneling in narrow bandgap GNR FETs prevents either PUN or PDN of logic circuits from completely cutting off when its complement network is active [10]. This may lead to voltage variations in the output of logic circuits. We propose complementary value and indetermination fault models for combinational circuits. The complementary value model means a change in the logic value (“0” changes to “1” or vice versa). The indetermination model represents a value that is in the forbidden gap between “0” and “1” logic values. In the case that the perturbed signal arrives at a sequential circuit, it can propagate and manifest as a bit-flip, which means a change in the memory state.

- Speed degradation. W variations can provoke the mobility degradation of the carriers, and thus the reduction of the GNR FET switching speed. Let us analyze this relationship. First, the ribbon width affects the energy bandgap according to Equation (3). Then, the mobility µ depends on Eg using the following expression [10]:where:

- λsc = scattering length,

- m* = effective mass,

- m*v = ℏkF = carrier momentum,

- ℏ = h/2π = reduced Planck constant,

- kF = Fermi wavenumber.

5.1.2. Oxide Thickness

5.1.3. Channel Length

5.1.4. Misalignment of Electrodes

5.2. Manufacturing Defects

5.2.1. Edge Roughness

5.2.2. Charge Impurities

5.2.3. Lattice Vacancies and Adsorbates

5.2.4. Electrical Contacts

5.3. Environmental Faults

5.3.1. Ion Radiation

5.3.2. Thermal Effects

5.4. Aging Faults

Graphene Interconnection Defects

5.5. Summary

- Fault causes have been classified in four groups (see Table 1): manufacturing variations, manufacturing defects, environmental faults and aging faults. The most harmful causes according to the literature are ribbon width variations, edge roughness, and charge impurities in gate oxide.

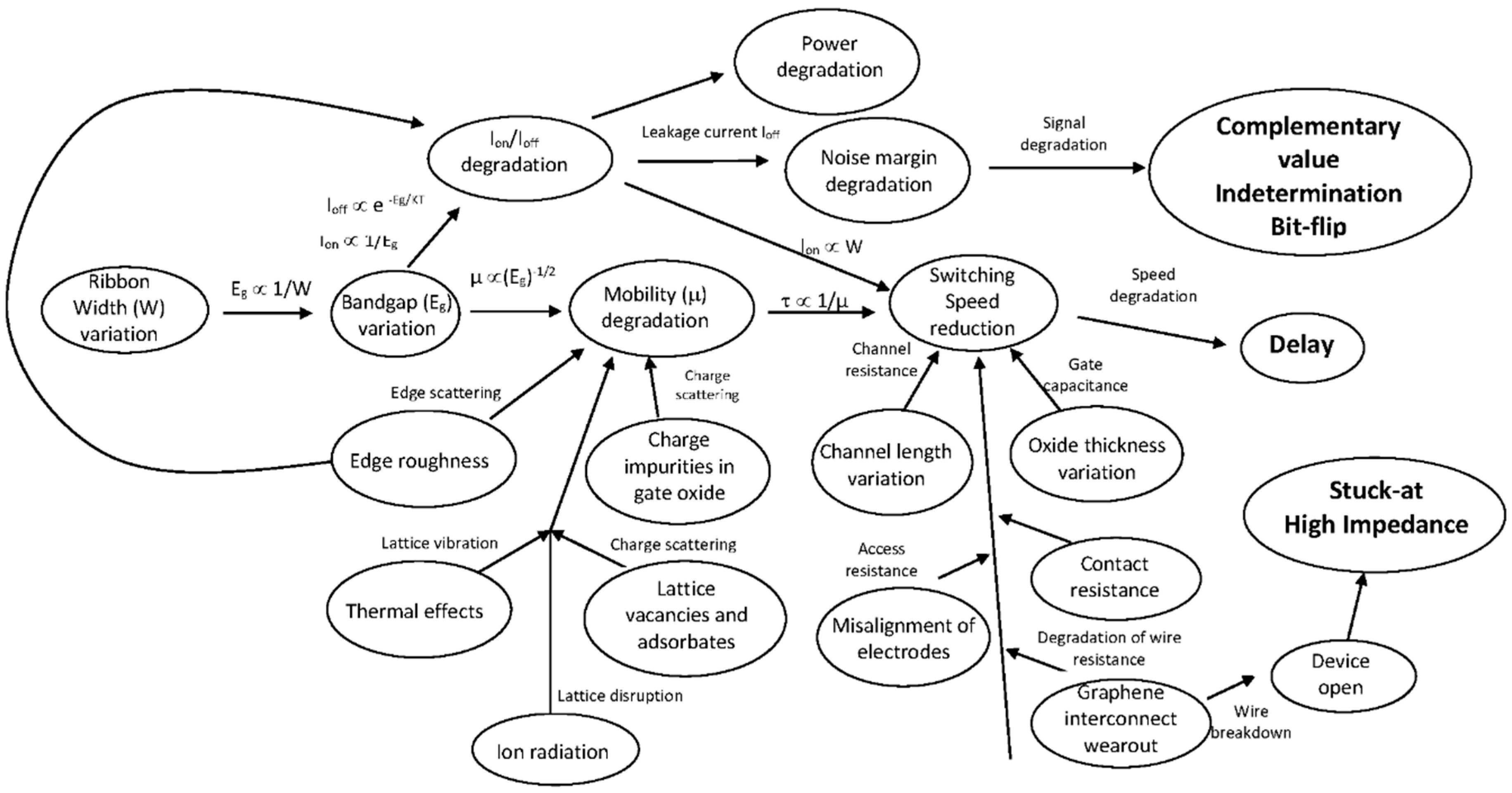

- Two main types of fault mechanisms have been identified (see Figure 5): those that perturb the logic signal value and those that impact the logic signal timing. The former are related to Ion/Ioff degradation and some aging processes, whereas the latter are linked with mobility degradation.

- With respect to fault models at the device level, we note that the most frequent is the delay fault model (see Table 1). This is because there is no standard fault model (stuck-on, stuck-off, delay) related to Ion/Ioff degradation at the device level. In this case, a dash appears in the table. Nevertheless, stuck-off related to wire breakdown has been identified.

- Directly related to the fault mechanisms, two groups of fault models are proposed at the logic level. Timing degradation can be modelled with the delay fault model. Value degradation can be modelled with several fault models: complementary value and indetermination in combinational circuits, and bit-flip in sequential circuits and memory. Complementary value, indetermination and delay are permanent faults, whereas bit-flip is transient. Other fault models that affect the output value are stuck-at and high impedance, related to the breakdown of graphene wires. Table 1 and Figure 5 show that timing degradation and the delay fault model are quite relevant, because they are related to more fault causes.

- Note that manufacturing defects and variations are permanent faults in essence. Nevertheless, environmental and wear-out faults can provoke aging processes, where the device characteristics change over time. Even transient faults may be generated by environment, although this is a subject of future research. The term “degradation” related to permanent faults implies an alteration in the spatial domain.

6. Comparison with CNT and NW Circuits

6.1. Comparison with CNTs

- Manufacturing defects of the metallic and misalignment/misposition types [20]. The manufacturing process makes it nearly impossible to guarantee the perfect alignment and accurate positioning of all CNTs at the Very Large Scale Integration (VLSI scale, or the growing of semiconducting CNTs exclusively. GNR FET circuits avoid these defects, because graphene’s planar profile makes it amenable to well-established top-down planar fabrication techniques for silicon CMOS devices [40,41,42]. Some fault models, different from those of GNR FET circuits, have been identified in relation with metallic and misalignment/misposition defects. For instance, we note stuck-on/stuck-off at the device level, which may manifest as stuck-at or even a change in the logic function at the logic level [20,29].

- Producing a good electrical contact between CNTs and metal electrodes can be problematic, because they tend to create Schottky barriers. Although electrical contacts also remain an important issue in graphene circuits, GNR metal–semiconducting junctions can be patterned together into all-graphene circuits (see Figure 2), avoiding metallic contacts to some extent. Moreover, GNR–CNT junctions are possible, as shown in Figure 3. Poor contacts in CNT circuits provoke an increase of the device resistance. They can be modelled with the delay fault model [20]. Defective metallic contacts in GNR circuits are also modelled with the delay fault model (see Figure 5 and Table 1).

- 3.

- Manufacturing variations, which affect some parameters of the CNT FET. Variations in the dimensions of the devices (CNT diameter, length, and oxide thickness) can modify the channel resistance and the threshold voltage of the transistor. This degrades the circuit speed. Thus, the delay fault model is proposed. As we have seen in Section 5, manufacturing variations are a critical issue in GNR FETs, especially ribbon width variation.

- 4.

- The break probability in CNT is very low, due to its high flexibility and fracture strain. Nevertheless, some research papers have studied the fracture mechanism in small diameter (less than 5 angströms) CNTs due to deformation and bending [43]. Related fault models have been identified in [20]. The fracture of CNT provokes the opening of the CNT FET channel and can be modelled with the stuck-off fault model at the device level. This may manifest as stuck-at or high impedance (open) at the logic level. About GNR, extremely high Young’s modulus and excellent flexibility has been demonstrated [44]. Although the fracture process is similar to that occurred in carbon nanotube, the width of the GNR was found to have a slight effect on the fracture point. On the other hand, graphene wire degradation with time has been observed [39]. Under constant current, wire conductivity degrades linearly with time, similar to CNTs. This can be modelled with delay, stuck-at, or high impedance at the logic level, as shown in Section 5.4.

6.2. Comparison with NWs

7. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Hanson, G.W. Fundamentals of Nanoelectronics; Pearson Prentice Hall: Upper Saddle River, NJ, USA, 2008. [Google Scholar]

- International Technology Roadmap for Semiconductors (ITRS) 2013. Available online: http://www.itrs2.net/2013-itrs.html (accessed on 3 July 2019).

- Schuegraf, K. Semiconductor Logic Technology Innovation to Achieve Sub-10 nm Manufacturing. IEEE J. Electron Devices Soc. 2013, 1, 66–75. [Google Scholar] [CrossRef]

- International Technology Roadmap for Semiconductors (ITRS) 2015. Available online: https://bit.ly/2xiiT8P (accessed on 3 July 2019).

- Das, S. Overview of Emerging Research Logic Devices. In Proceedings of the ITRS Architecture Workshop; Stanford University: Stanford, CA, USA, 2015. Available online: https://bit.ly/2KWCvrB (accessed on 3 July 2019).

- Novoselov, K.S.; Geim, A.K.; Morozov, S.V.; Jiang, D.; Zhang, Y.; Dubonos, S.V.; Grigorieva, I.V.; Firsov, A.A. Electric Field Effect in Atomically Thin Carbon Films. Science 2004, 306, 666–669. [Google Scholar] [CrossRef] [PubMed]

- Geim, A.K.; Novoselov, K.S. The Rise of Graphene. Nat. Mater. 2007, 6, 183–191. Available online: https://www.nature.com/articles/nmat1849 (accessed on 3 July 2019). [CrossRef] [PubMed]

- Wu, Y.; Farmer, D.B.; Xia, F.; Avouris, P. Graphene Electronics: Materials, Devices, and Circuits. Proc. IEEE 2013, 101, 1620–1637. [Google Scholar] [CrossRef]

- Choudhury, M.R.; Yoon, Y.; Guo, J.; Mohanram, K. Graphene Nanoribbon FETs: Technology Exploration for Performance and Reliability. IEEE Trans. Nanotechnol. 2010, 10, 7217–7736. [Google Scholar] [CrossRef]

- Raza, H. Graphene Nanoelectronics: Metrology, Synthesis, Properties and Applications; Springer: Berlin/Heidelberg, Germany, 2012. [Google Scholar]

- De Heer, W.A.; Berger, C.; Conrad, E.H.; First, P. Pionics: The Emerging Science and technology of Graphene-Based Nanoelectronics. In Proceedings of the 2007 IEEE International Electron Devices Meeting, Washington, DC, USA, 10–12 December 2007; pp. 199–202. [Google Scholar]

- Avouris, P. Graphene: Electronic and Photonic Properties and Devices. Nano Lett. 2010, 10, 4285–4294. [Google Scholar] [CrossRef]

- Banakadi, Y.M.; Srivaska, A. Scaling Effects on Static Metrics and Switching Attributes of Graphene Nanoribbon FET for Emerging Technology. IEEE Trans. Emerg. Top. Comput. 2015, 3, 458–469. [Google Scholar]

- Rodríguez, S.; Rusu, A.; de la Rosa, J.M. Overview of Carbon-Based Circuits and Systems. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015; pp. 2912–2915. [Google Scholar]

- Avouris, P.; Cheng, Z.; Perebeinos, V. Carbon-based Electronics. Nat. Nanotechnol. 2007, 2, 605–615. [Google Scholar] [CrossRef]

- Banerjee, S.K.; Register, L.F.; Tutuc, E.; Basu, D.; Kim, S.; Reddy, D.; MacDonald, A.H. Graphene for CMOS and Beyond CMOS applications. Proc. IEEE 2010, 98, 2032–2046. [Google Scholar] [CrossRef]

- Schwierz, F. Graphene Transistors: Status, Prospects, and Problems. Proc. IEEE 2013, 101, 1567–1584. [Google Scholar] [CrossRef]

- Gil, D.; de Andrés, D.; Ruiz, J.; Gil, P. Identifying Fault Mechanisms and Models of Emerging Nanoelectronic Devices. In Proceedings of the 1st Workshop on Dependable and Secure Nanocomputing, IEEE International Conference on Dependable Systems and Networks, Washington, DC, USA, 25–28 June 2007; p. 288. Available online: https://bit.ly/2FOsnwH (accessed on 3 July 2019).

- Gil, D.; de Andrés, D.; Ruiz, J.C.; Gil-Vicente, P.; de Vera, C.N. Developing Fault Models for Nanowire Logic Circuits. In Proceedings of the 2nd Workshop on Dependable and Secure Nanocomputing, IEEE International Conference on Dependable Systems and Networks, Anchorage, AK, USA, 27 June 2008; pp. C6–C11. Available online: https://bit.ly/2LBBepk (accessed on 3 July 2019).

- Gil, D.; de Andrés, D.; Ruiz, J.C.; Gil-Vicente, P. Impact of Manufacturing Defects on Carbon Nanotube Logic Circuits. In Proceedings of the 3rd Workshop on Dependable and Secure Nanocomputing, IEEE International Conference on Dependable Systems and Networks, Lisbon, Portugal, 29 June 2009; Available online: https://bit.ly/2NrMMxR (accessed on 3 July 2019).

- Choudhury, M.; Yoon, Y.; Guo, J.; Mohanram, K. Technology Exploration for Graphene Nanoribbon FETs. In Proceedings of the 2008 45th ACM/IEEE Design Automation Conference, Anaheim, CA, USA, 8–13 June 2008; pp. 272–277. [Google Scholar]

- Frégonèse, S.; Magallo, M.; Maneux, C.; Happy, H.; Zimmer, T. Scalable Electrical Compact Modeling for Graphene FET Transistors. IEEE Trans. Nanotechnol. 2013, 12, 539–546. [Google Scholar] [CrossRef]

- Chen, Y.; Sangai, A.; Rogachev, A.; Gholipour, M.; Iannaccone, G.; Fiori, G.; Chen, D. A SPICE-Compatible Model of MOS-Type Graphene Nano-Ribbon Field-Effect Transistor Enabling Gate and Circuit-Level Delay and Power Analysis Under Process Variation. IEEE Trans. Nanotechnol. 2015, 14, 1068–1082. [Google Scholar] [CrossRef]

- Ferrari, A.; Bonaccorso, F.; Fal’ko, V.; Novoselov, K.S.; Roche, S.; Bøggild, P.; Borini, S.; Koppens, F.H.L.; Palermo, V.; Pugno, N.; et al. Science and technology roadmap for graphene, related two-dimensional crystals, and hybrid systems. Nanoscale 2015, 7, 4587–5062. [Google Scholar] [CrossRef] [PubMed]

- Hong, A.J.; Song, E.B.; Yu, H.S.; Allen, M.J.; Kim, J.; Fowler, J.D.; Wasse, J.K.; Park, Y.; Wang, Y.; Zou, J.; et al. Graphene Flash Memory. ACS Nano 2011, 5, 7812–7817. [Google Scholar] [CrossRef] [PubMed]

- Gune, A.; Gupta, A. Graphene Nanoribbon Based Static Random Access Memory for Better Noise Margin and Power Reduction. In Proceedings of the International Conference on Advanced Nanomaterials & Emerging Engineering Technologies, Chennai, India, 24–26 July 2013; pp. 450–452. [Google Scholar]

- Yoshi, S.; Mohanty, S.P.; Kougianos, E.; Yanambaka, V.P. Graphene Nanoribbon Field Effect Transistor based Ultra-Low Energy SRAM Design. In Proceedings of the 2016 IEEE International Symposium on Nanoelectronic and Information Systems (iNIS), Gwalior, India, 19–21 December 2016; pp. 76–79. [Google Scholar]

- Jeng, S.; Lu, J.; Wang, K. A Review of Reliability Research on Nanotechnology. IEEE Trans. Reliab. 2007, 56, 401–410. [Google Scholar] [CrossRef]

- Srinivasu, B.; Sridharan, K. A Transistor-Level Probabilistic Approach for Reliability Analysis of Arithmetic Circuits with Applications to Emerging Technologies. IEEE Trans. Reliab. 2017, 66, 440–457. [Google Scholar] [CrossRef]

- Franco, D.T.; Naviner, J.F.; Naviner, L. Yield and reliability issues in nanoelectronic technologies. Ann. Télécommunications 2006, 61, 1422–1457. [Google Scholar] [CrossRef]

- Mohanram, K.; Guo, J. Graphene Nanoribbon FETs: Technology Exploration and CAD. In Proceedings of the 2008 IEEE/ACM International Conference on Computer-Aided Design, San Jose, CA, USA, 2–5 November 2009; pp. 412–415. [Google Scholar]

- Lin, Y.M.; Jenkins, K.A.; Valdes-Garcia, A.; Small, J.P.; Farmer, D.B.; Avouris, P. Operation of Graphene Transistors at Gigahertz Frequencies. Nano Lett. 2008, 9, 422–426. [Google Scholar] [CrossRef]

- Liao, L.; Lin, Y.; Bao, M.; Cheng, R.; Bai, J.; Liu, Y.; Qu, Y.; Wang, K.L.; Huang, Y.; Duan, X. High-speed graphene transistors with a self-aligned nanowire gate. Nature 2010, 467, 305–308. [Google Scholar] [CrossRef]

- Wang, X.; Tabakman, S.M.; Dai, H. Atomic Layer Deposition of Metal Oxides on Pristine and Functionalized Graphene. J. Am. Chem. Soc. 2008, 130, 8152–8153. [Google Scholar] [CrossRef]

- Geim, A.K. Graphene: Status and Prospects. Science 2009, 19, 1530–1534. [Google Scholar] [CrossRef] [PubMed]

- Lemme, M. Graphene Process and Device Options for Microelectronics Applications. In Proceedings of the NanoTec-Workshop, Lausanne, Switzerland, 31 May 2012; Available online: http://bit.ly/32a5AFu (accessed on 3 July 2019).

- Mistewicz, K.; Nowak, M.; Wrzalik, R.; Śleziona, J.; Wieczorek, J.; Guiseppi-Elie, A. Ultrasonic processing of SbSI nanowires for their application to gas sensors. Ultrasonics 2016, 69, 67–73. [Google Scholar] [CrossRef] [PubMed]

- Jesionek, M.; Nowak, M.; Mistewicz, K.; Kępińska, M.; Stróż, D.; Bednarczyk, I.; Paszkiewicz, R. Sonochemical growth of nanomaterials in carbon nanotube. Ultrasonics 2018, 83, 179–187. [Google Scholar] [CrossRef] [PubMed]

- Chen, X.; Seo, D.H.; Seo, S.; Chung, H.; Wong, H.-S.P. Graphene Interconnect Lifetime: A Reliability Analysis. IEEE Electron Device Lett. 2010, 33, 1604–1606. [Google Scholar] [CrossRef]

- Stan, M.R.; Ghosh, A. Monolithically-Integrated Graphene-Nanoribbon (GNR) Devices, Interconnects and Circuits. U.S. Patent 2009,0174,435, 9 June 2009. Available online: https://patents.justia.com/patent/20090174435 (accessed on 3 July 2019).

- Chen, D.; Chilstedt, S.; Dong, C.; Pop, E.; Chen, D.; Chilstedt, S.; Dong, C.; Pop, E. What Everyone Needs to Know about Carbon-Based Nanocircuits. In Proceedings of the IEEE/ACM Design Automation Conference, Anaheim, CA, USA, 13–18 June 2010. [Google Scholar]

- Wang, Z.F.; Shi, Q.W.; Chen, J. Emerging nanodevice paradigm: Graphene-based electronics for nanoscale computing. ACM J. Emerg. Technol. Comput. Syst. 2009, 5, 3. [Google Scholar] [CrossRef]

- Dong, J.; Gao, X.; Kong, X.-Y.; Li, J.-M. Atomistic Failure Mechanism of Single Wall Carbon Nanotubes with Small Diameters. Chin. Phys. Lett. 2007, 24, 165–168. [Google Scholar] [CrossRef]

- Bu, H.; Chen, Y.; Zou, M.; Yi, H.; Bi, K.; Ni, Z. Atomistic Simulations of Mechanical Properties of Graphene Nanoribbons. Phys. Lett. A 2009, 373, 3359–3362. [Google Scholar] [CrossRef]

| Defects and Faults | Causes and Mechanisms | Effect on GNR FET | Fault Model at Device Level | Effect on the Logic Circuits | Fault Model at Logic Level | |

|---|---|---|---|---|---|---|

| Manufacturing variations | Width [9,21,23,27,31] | Energy band-gap variation | Leakage current, Ion/Ioff degradation | - | Power degradation, noise margin degradation | Combinational → Complementary value, Indetermination FF, memory → Bit-flip |

| Mobility degradation | Reduction of the switching speed | Delay | Speed degradation | Delay | ||

| Oxide thickness [10] | Gate capacitance variation | Delay degradation | Delay | Speed degradation | Delay | |

| Channel length [1,32] | Channel resistance variation | Reduction of the switching speed, degradation of ballistic transport | Delay | Speed degradation | Delay | |

| Misalignment of electrodes [33] | Access resistance in the channel | Reduction of the switching speed | Delay | Speed degradation | Delay | |

| Manufacturing defects and residues | Edge roughness [7,9,12,23,31] | Irregular edges | Leakage current, reduction of Ion/Ioff | - | Noise margin degradation, power degradation | Combinational → Complementary value, Indetermination FF, memory → Bit- flip |

| Edge scattering, mobility degradation | Reduction of the switching speed | Delay | Speed degradation | Delay | ||

| Charge impurities in the gate oxide [9,21,23,31,32,34] | Modification of the electrostatic potential in the channel | Ion/Ioff degradation | - | Noise margin degradation, power degradation | Combinational → Complementary value, Indetermination FF, memory → Bit-flip | |

| Charge scattering, mobility degradation, conductance decay | Reduction of the switching speed | Delay | Speed degradation | Delay | ||

| Lattice vacancies and adsorbates [10,35] | Charge scattering, mobility degradation, conductance decay | Reduction of the switching speed | Delay | Speed degradation | Delay | |

| Electrical contacts [12,36,37,38] | Contact resistance between electrodes and graphene channel | Reduction of the switching speed | Delay | Speed degradation | Delay | |

| Environment | Ion radiation [10] | Lattice disruption, mobility degradation | Reduction of the switching speed | Delay | Speed degradation | Delay |

| Thermal effects [1] | Lattice vibration, mobility degradation | Reduction of the switching speed | Delay | Speed degradation | Delay | |

| Thermal decoherence of the electron wave function (quantum) | - | - | ||||

| Wearout | Interconnect defects [39] | Graphene oxidation | Increase of wire resistance, breakdown | Delay, Open | Speed degradation, Fixed or floating output | Delay, Stuck-at, High impedance |

| GNR | CNT | NW | |

|---|---|---|---|

| Most harmful causes and mechanisms | Width variation, edge roughness, gate oxide impurities | Metallic, misalignment/ mispositioning, poor contacts | Broken, poor contacts, doping variation, cross-point defects |

| Models at device level | Delay, stuck-off | Stuck-on, stuck-off, delay | Stuck-on, stuck-off, delay |

| Models at logic level | Delay, complementary value, indetermination, bit-flip | Delay, stuck-at, indetermination, high impedance, change of logic function | Delay, stuck-at, indetermination, high impedance, complementary value |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Gil-Tomàs, D.; Gracia-Morán, J.; Saiz-Adalid, L.J.; Gil-Vicente, P.J. Fault Modeling of Graphene Nanoribbon FET Logic Circuits. Electronics 2019, 8, 851. https://doi.org/10.3390/electronics8080851

Gil-Tomàs D, Gracia-Morán J, Saiz-Adalid LJ, Gil-Vicente PJ. Fault Modeling of Graphene Nanoribbon FET Logic Circuits. Electronics. 2019; 8(8):851. https://doi.org/10.3390/electronics8080851

Chicago/Turabian StyleGil-Tomàs, D., J. Gracia-Morán, L.J. Saiz-Adalid, and P.J. Gil-Vicente. 2019. "Fault Modeling of Graphene Nanoribbon FET Logic Circuits" Electronics 8, no. 8: 851. https://doi.org/10.3390/electronics8080851

APA StyleGil-Tomàs, D., Gracia-Morán, J., Saiz-Adalid, L. J., & Gil-Vicente, P. J. (2019). Fault Modeling of Graphene Nanoribbon FET Logic Circuits. Electronics, 8(8), 851. https://doi.org/10.3390/electronics8080851