A High-Accuracy Ultra-Low-Power Offset-Cancelation On-Off Bandgap Reference for Implantable Medical Electronics

Abstract

:1. Introduction

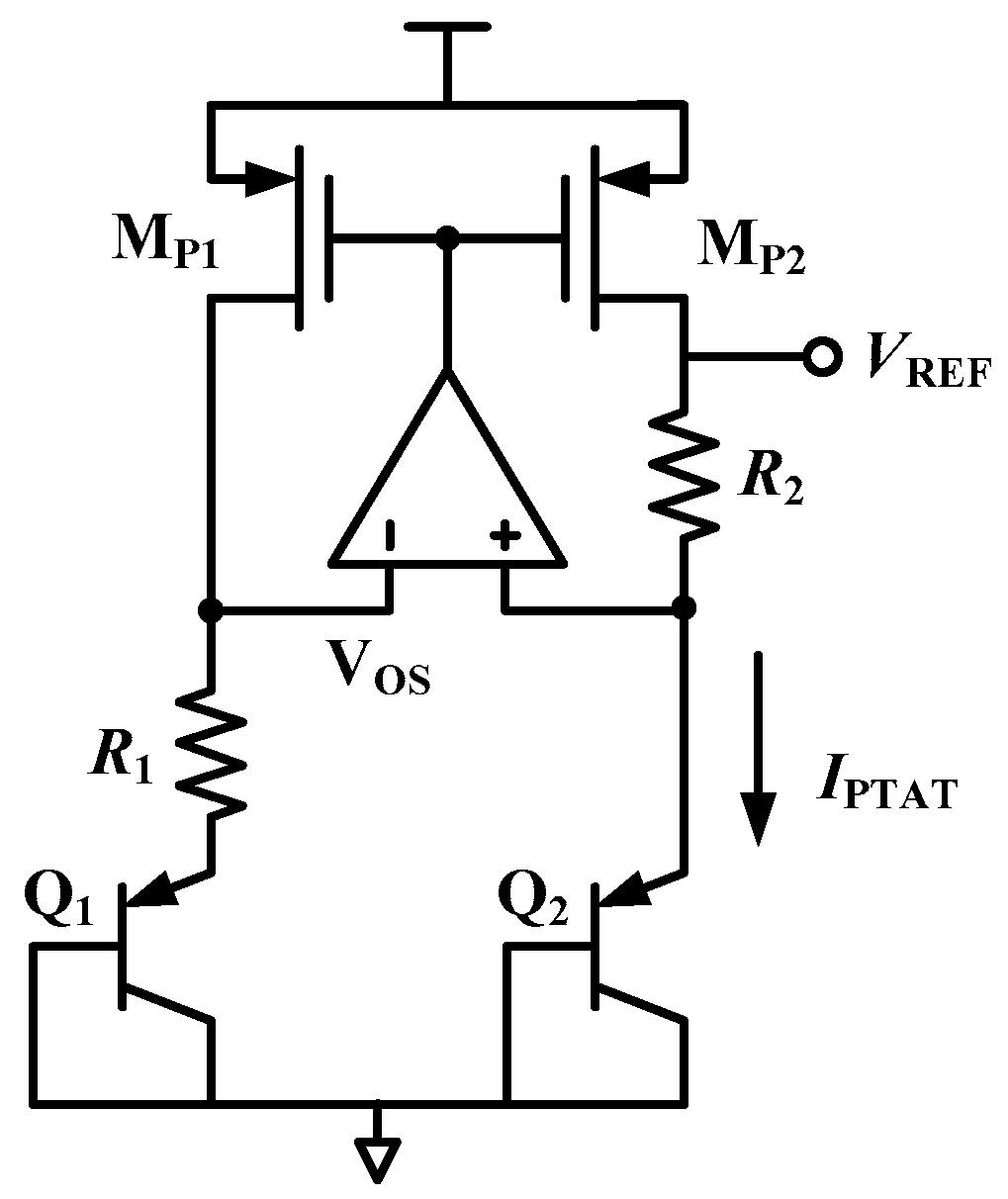

2. Proposed Bandgap Reference

2.1. Error Analysis of the BJT-Based BGR

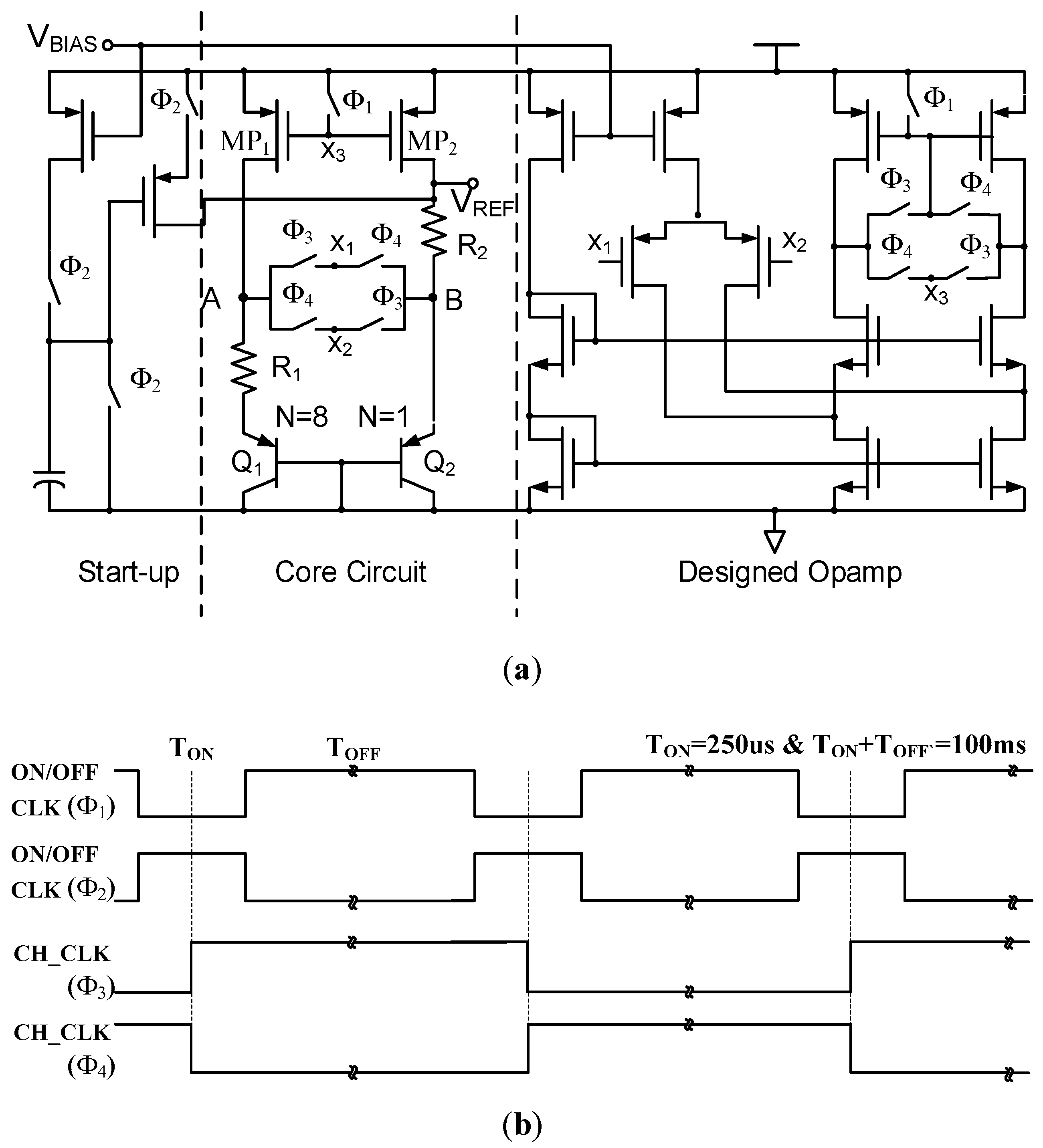

2.2. Architecture of the Proposed BGR Circuit

2.3. Chopper Mechanism and Correlated Double Sampling

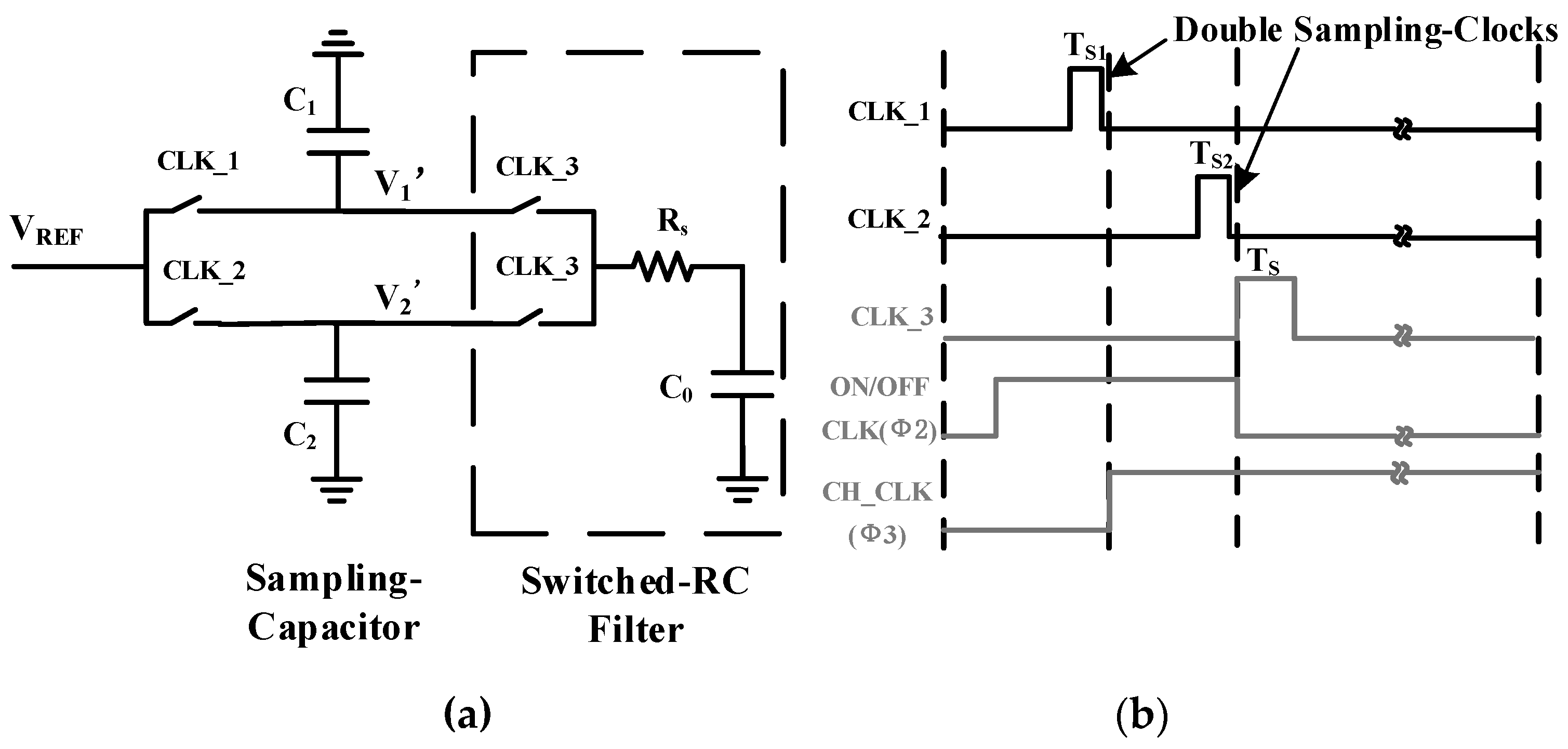

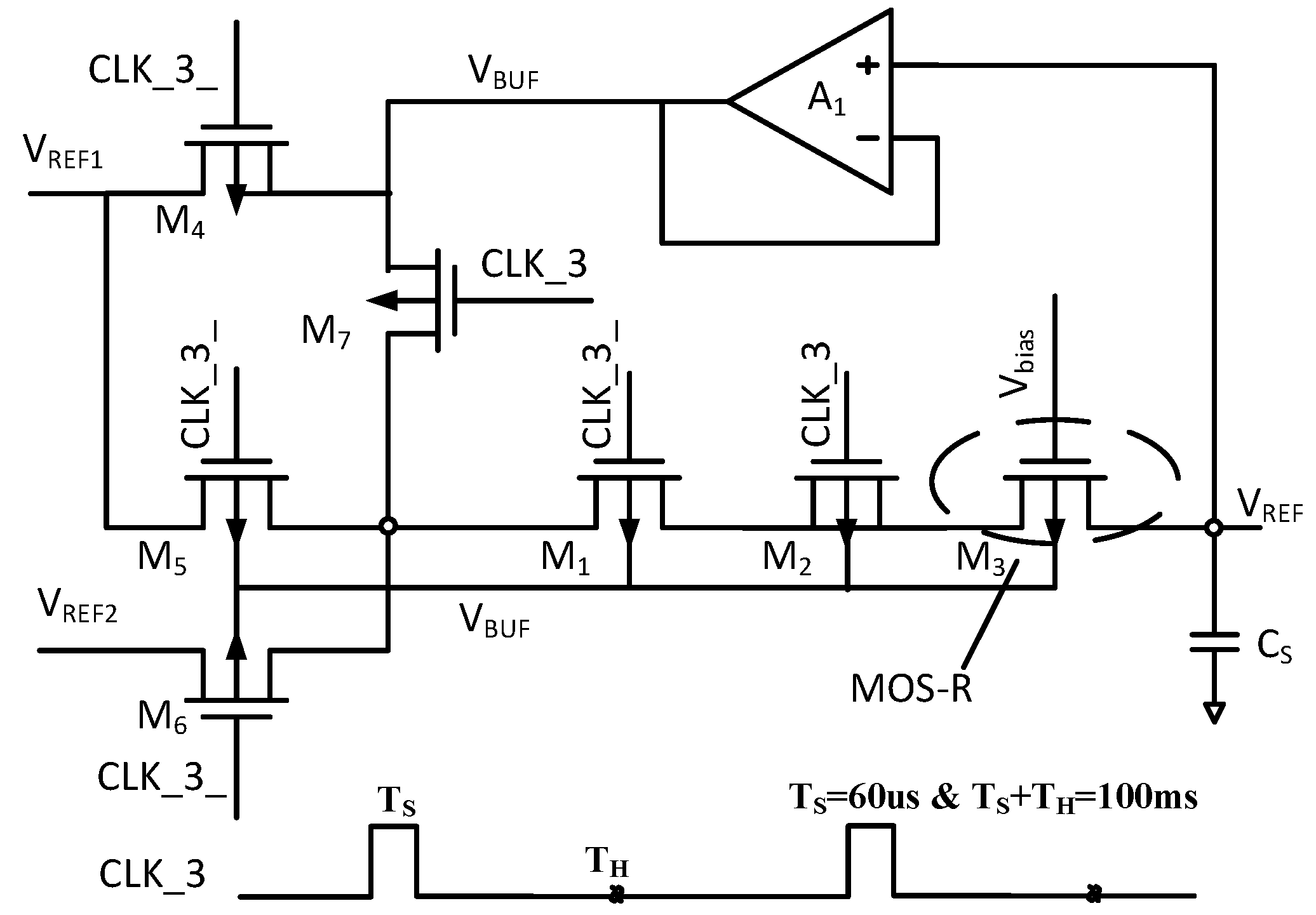

2.4. Sample-and-Hold Switched-RC Filter

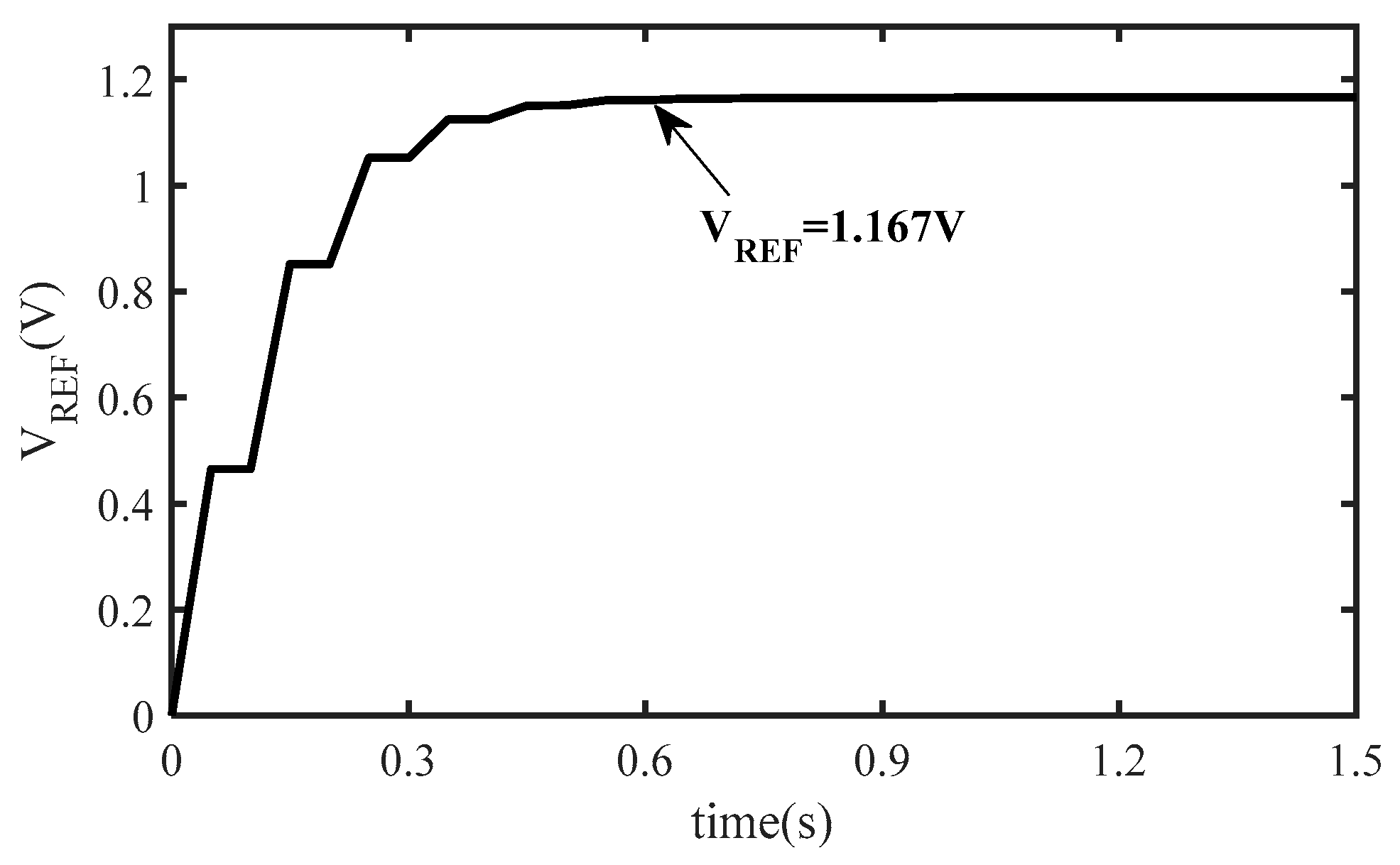

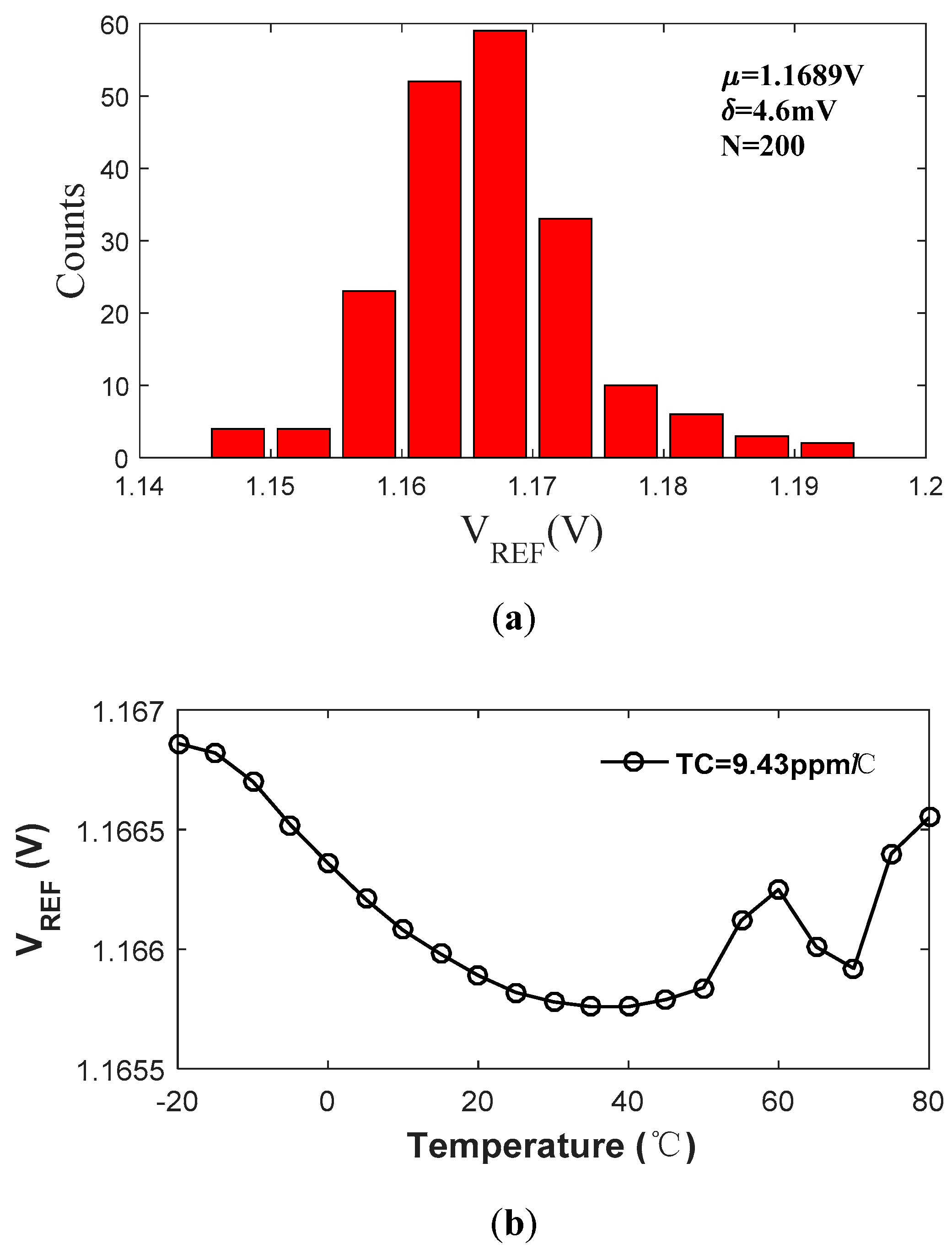

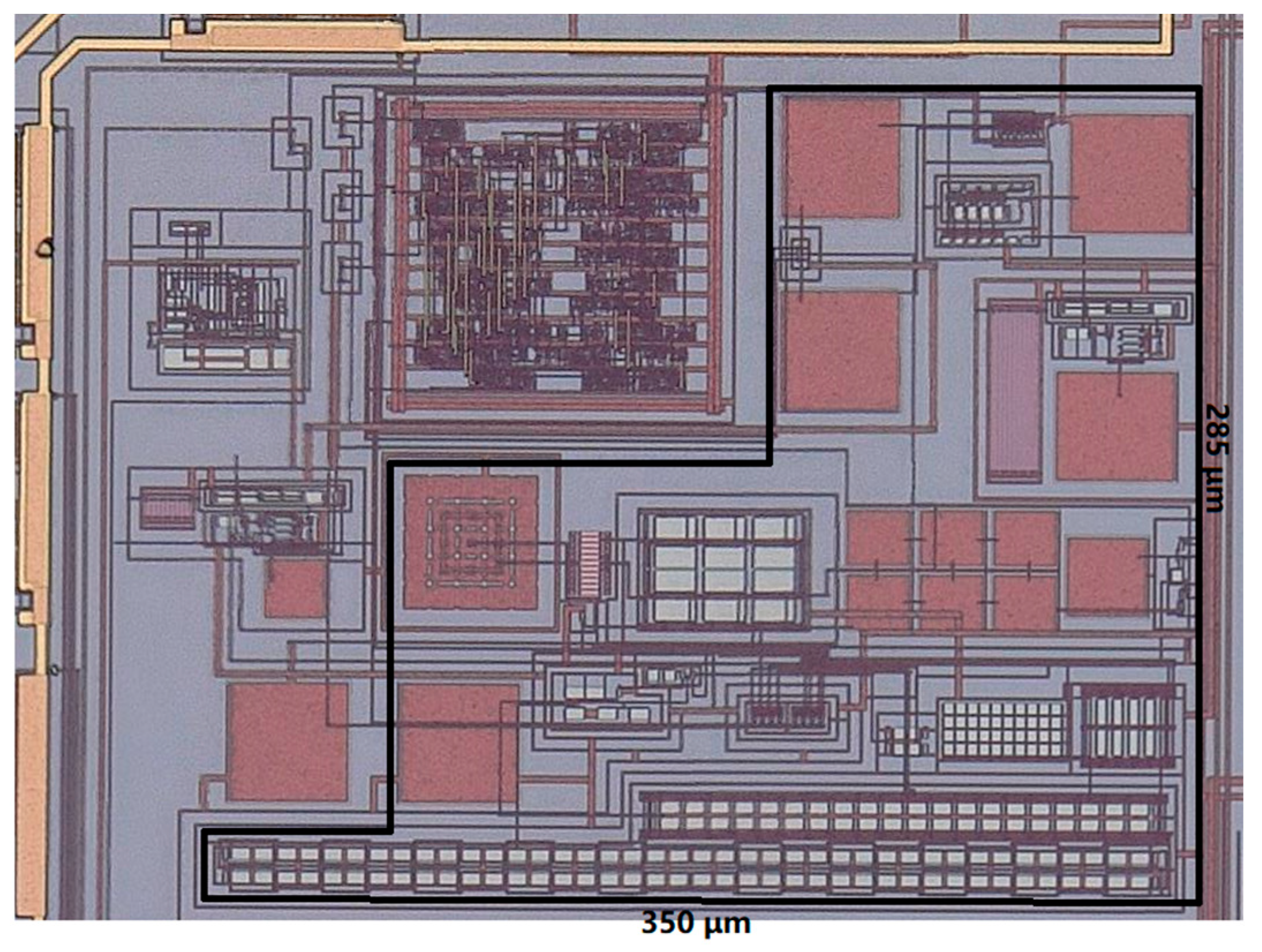

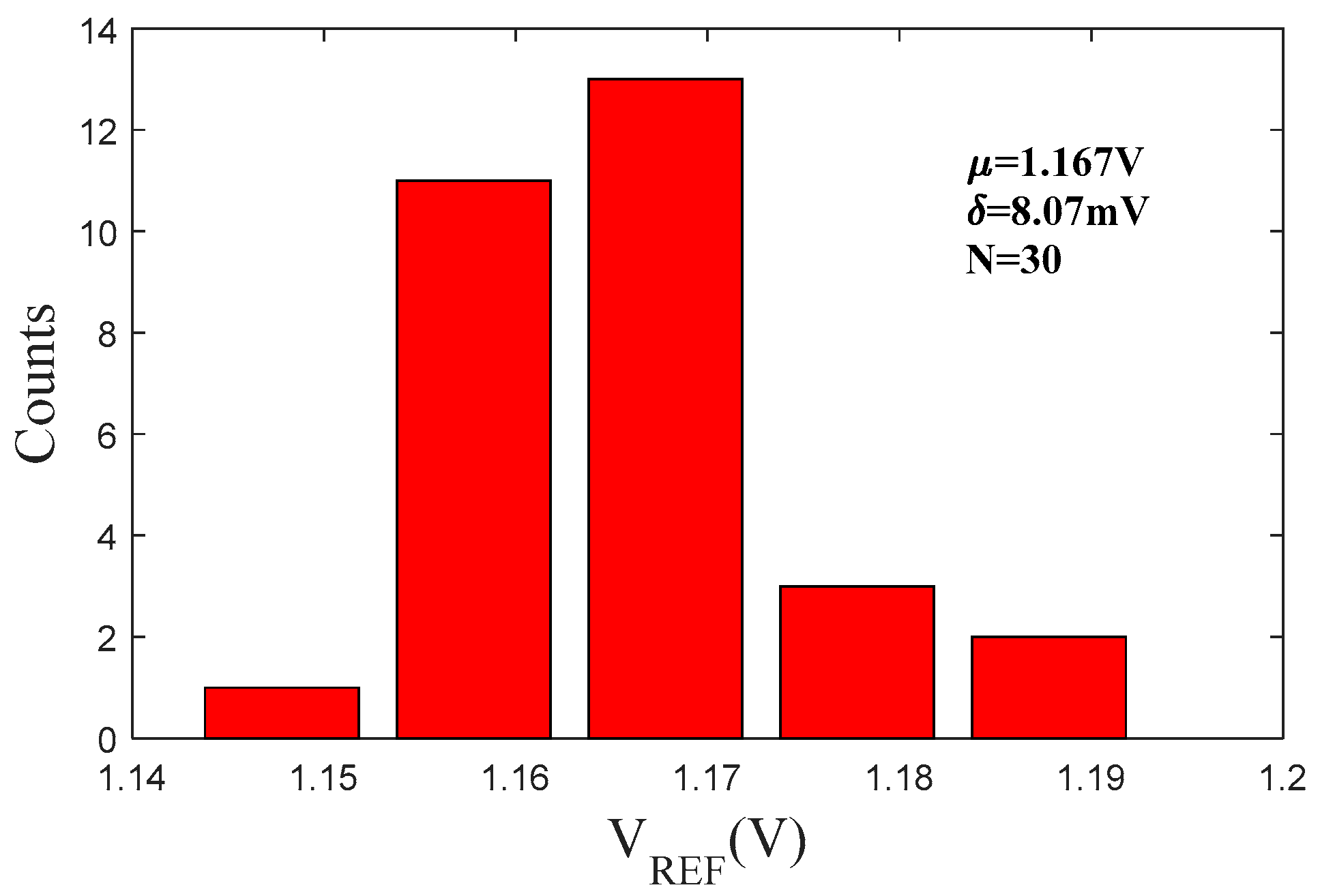

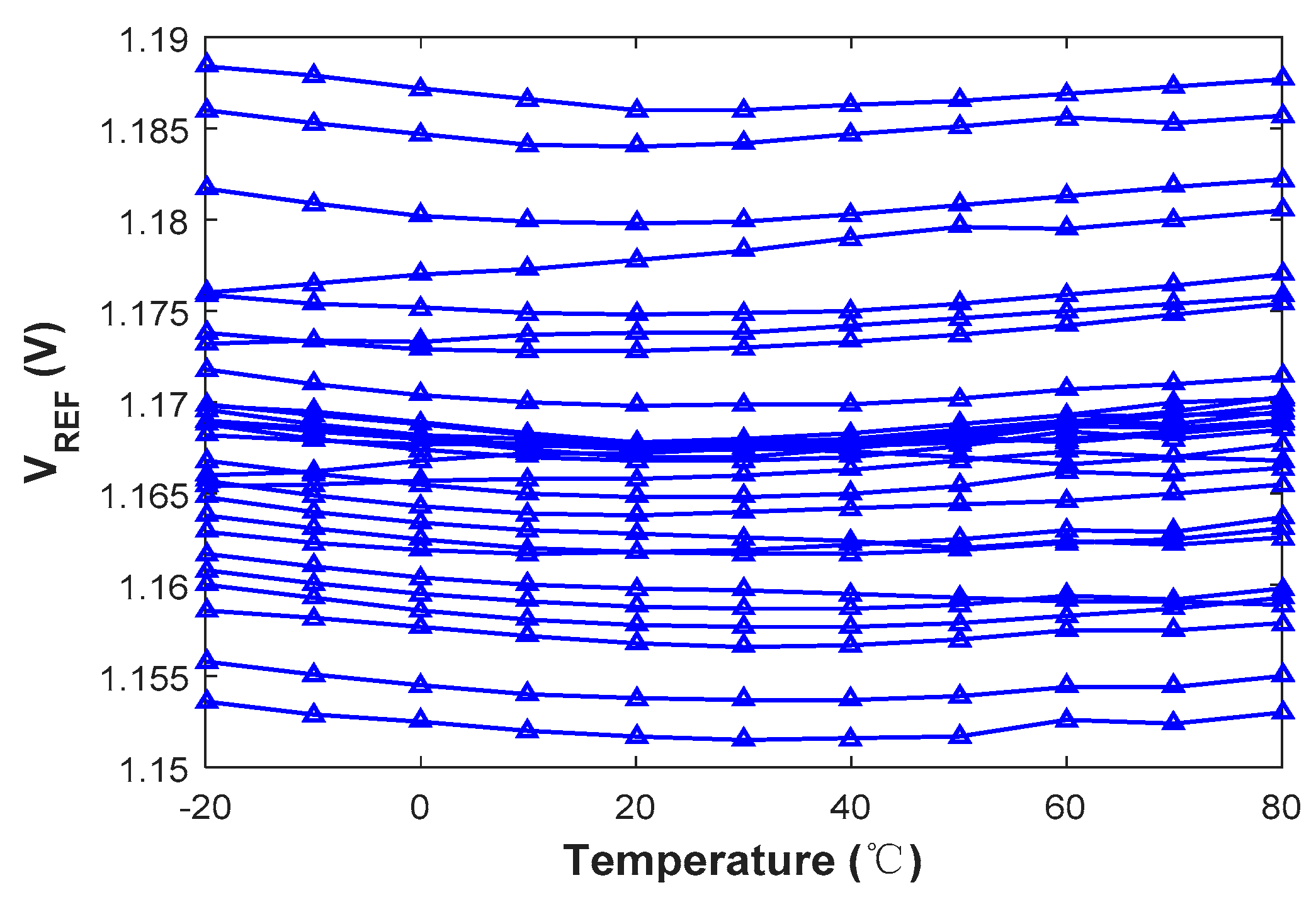

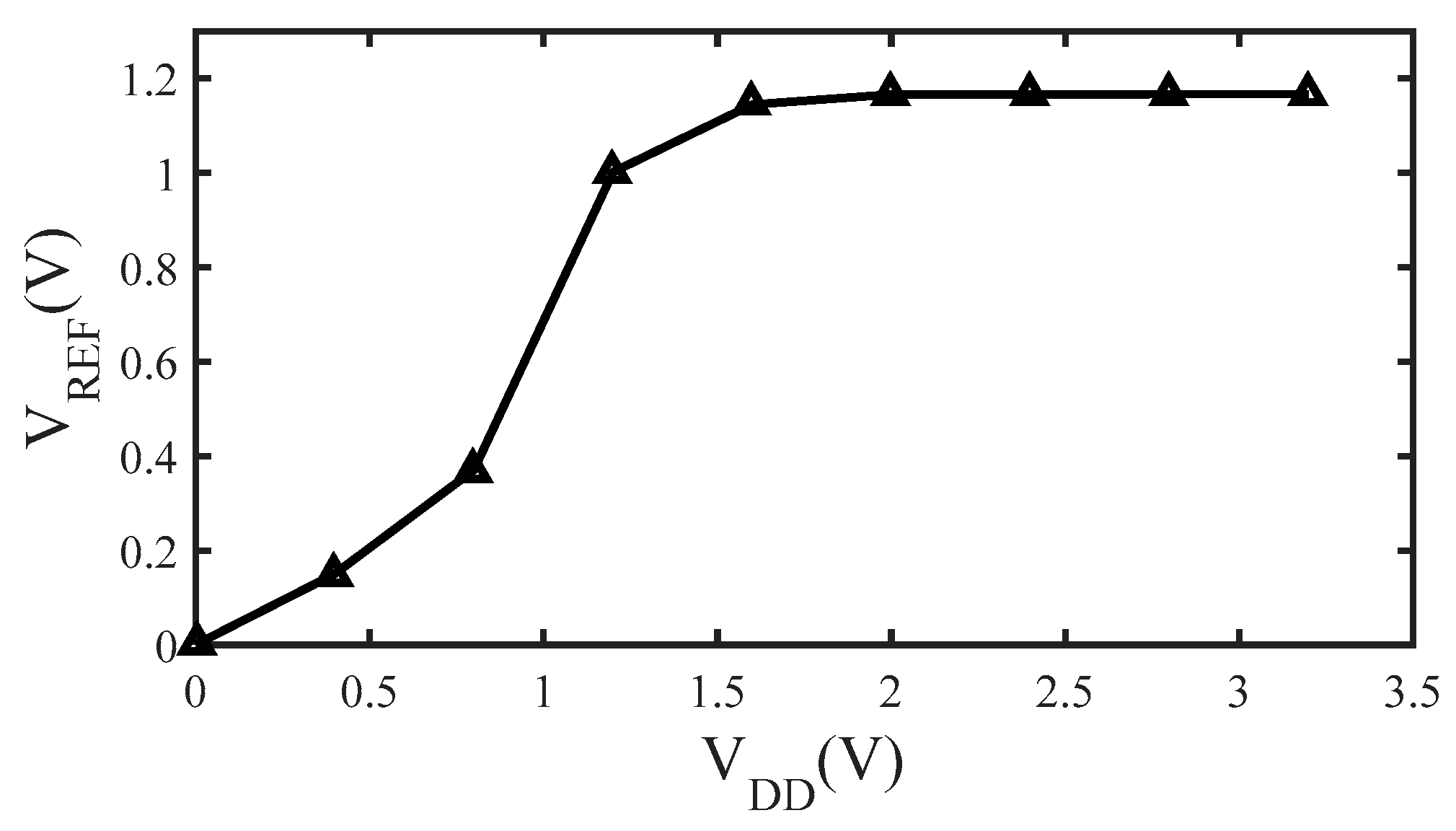

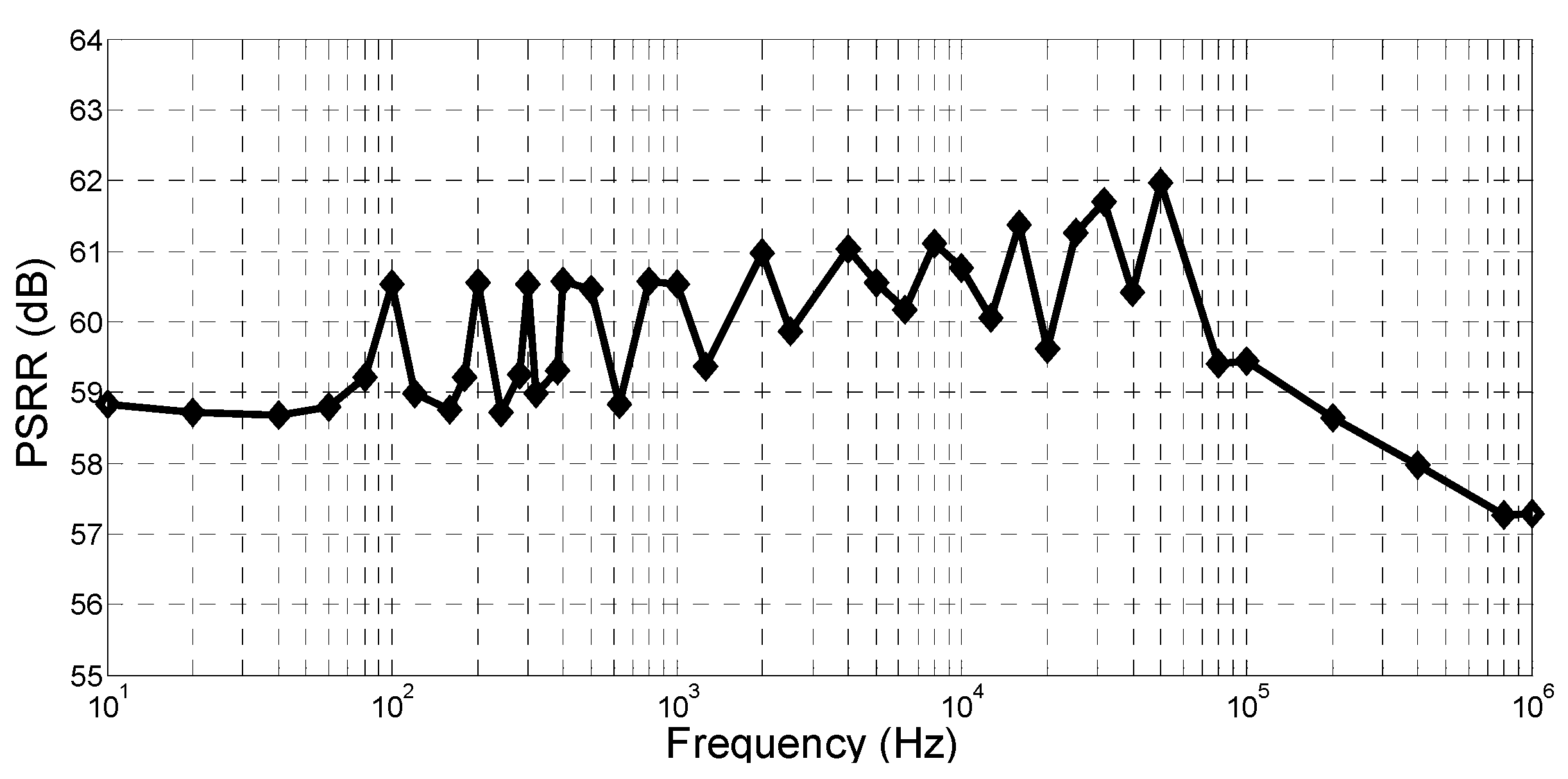

3. Simulation and Measurement Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Zhang, J.; Zhang, H.; Zhang, R.; Xu, J.; Yang, Z.; Zhang, M.; Li, J. A mixed-signal ASIC for triple-chamber cardiac pacemakers with heart resistance measurement. In Proceedings of the 2015 IEEE Asian Solid-State Circuits Conference (A-SSCC), Xiamen, China, 9–11 November 2015; pp. 33–36. [Google Scholar]

- Zhang, J.; Zhang, H.; Xu, J.; Zhao, Y.; Li, J.; Hu, G.; Wang, J.; Zhang, R.; Lian, Y. A low energy ASIC for triple-chamber cardiac pacemakers with contact resistance measurement. Microelectron. J. 2017, 60, 65–74. [Google Scholar] [CrossRef]

- Swampillai, J.; Stiles, M.K. Hazards of modern pacemaker programming: Less is more. J. Electrocardiol. 2013, 46, 140. [Google Scholar] [CrossRef] [PubMed]

- Fayomietal, C.J.B. Sub-1-V CMOS Bandgap Reference Design Techniques: A Survey. Analog Integr. Circuits Signal Process. 2010, 62, 141–157. [Google Scholar]

- Peng, K.; Xu, Y. Design of Low-Power Bandgap Voltage Reference for IoT RFID Communication. In Proceedings of the 2018 IEEE 3rd International Conference on Integrated Circuits and Microsystems (ICICM), Shanghai, China, 24–26 November 2018; pp. 345–348. [Google Scholar]

- Wu, C.; Goh, W.L.; Yang, Y.; Chang, A.; Zhu, X.; Wang, L. A start-up free 200nW bandgap voltage reference. In Proceedings of the 2016 14th IEEE International New Circuits and Systems Conference (NEWCAS), Vancouver, BC, Canada, 26–29 June 2016; pp. 1–4. [Google Scholar]

- Souliotis, G.; Plessas, F.; Vlassis, S. A high accuracy voltage reference generator. Microelectron. J. 2018, 75, 61–67. [Google Scholar] [CrossRef]

- Andreou, C.M.; Georgiou, J. A 0.7 V, 2.7 µW, 180 °C Temperature Range, 12.9 ppm/°C, 0.023 mm2, Subthreshold Voltage Reference. Int. J. Circuit Theory Appl. 2017, 45, 1349–1368. [Google Scholar] [CrossRef]

- Sarpeshkar, R. Ultra Low Power Bioelectronics; Cambridge University Press: Cambridge, UK, 2010. [Google Scholar]

- Ueno, K.; Hirose, T.; Asai, T.; Amemiya, Y. A 300 nW, 15 ppm/°C, 20 ppm/V CMOS Voltage Reference Circuit Consisting of Subthreshold MOSFETs. IEEE J. Solid-State Circuits 2009, 44, 2047–2054. [Google Scholar] [CrossRef]

- Abbasi, M.U.; Raikos, G.; Saraswat, R.; Rodriguez-Villegas, E.; Usaid, A.M. A high PSRR, ultra-low power 1.2V curvature corrected Bandgap reference for wearable EEG application. In Proceedings of the 2015 IEEE 13th International New Circuits and Systems Conference (NEWCAS), Grenoble, France, 7–10 June 2015; pp. 1–4. [Google Scholar]

- Mu, J.; Liu, L.; Zhu, Z.; Yang, Y. A 0.5 V, 40 nW voltage reference for WBAN devices. In Proceedings of the 2016 IEEE Biomedical Circuits and Systems Conference (BioCAS), Shanghai, China, 17–19 October 2016; pp. 504–507. [Google Scholar]

- Magod, R.; Suda, N.; Ivanov, V.; Balasingam, R.; Bakkaloglu, B. A Low-Noise Output Capacitorless Low-Dropout Regulator with a Switched-RC Bandgap Reference. IEEE Trans. Power Electron. 2017, 32, 2856–2864. [Google Scholar] [CrossRef]

- Hafiz, O.A.; Wang, X.; Hurst, P.J.; Lewis, S.H. Immediate Calibration of Operational Amplifier Gain Error in Pipelined ADCs Using Extended Correlated Double Sampling. IEEE J. Solid-State Circuits 2013, 48, 749–759. [Google Scholar] [CrossRef]

- Son, S.; Jeon, S.; Namgung, S.; Yoo, J.; Song, M.; Suho, S. A one-shot digital correlated double sampling with a differential difference amplifier for a high speed CMOS image sensor. In Proceedings of the 2015 IEEE International Symposium on Circuits and Systems (ISCAS), Lisbon, Portugal, 24–27 May 2015; pp. 1054–1057. [Google Scholar]

- Jiang, J.; Shu, W.; Chang, J.S. A 5.6 ppm/°C Temperature Coefficient, 87-dB PSRR, Sub-1-V Voltage Reference in 65-nm CMOS Exploiting the Zero-Temperature-Coefficient Point. IEEE J. Solid-State Circuits 2017, 52, 623–633. [Google Scholar] [CrossRef]

- Wang, Y.; Zhu, Z.; Yao, J.; Yang, Y. A 0.45-V, 14.6-nW CMOS Subthreshold Voltage Reference With No Resistors and No BJTs. IEEE Trans. Circuits Syst. 2015, 62, 621–625. [Google Scholar] [CrossRef]

- Shrivastava, A.; Craig, K.; Roberts, N.E.; Wentzloff, D.D.; Calhoun, B.H. A 32 nW bandgap reference voltage operational from 0.5 V supply for ultra-low power systems. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Basyurt, P.B.; Bonizzoni, E.; Aksin, D.Y.; Maloberti, F. A 0.4-V Supply Curvature-Corrected Reference Generator with 84.5-ppm/°C Average Temperature Coefficient within 40 °C to 130 °C. IEEE Trans. Circuits Syst. 2017, 64, 362–366. [Google Scholar] [CrossRef]

| Parameter | [16] | [17] | [18] | [19] | This Work |

|---|---|---|---|---|---|

| Process | 65 nm | 180 nm | 130 nm | 180 nm | 350 nm |

| Publication Year | JSSC 2017 | TCAS-II 2015 | ISSCC 2015 | TCAS-II 2017 | 2019 |

| Accuracy (σ/µ) | 0.39%(T) | 3.9%(UT) | 0.67%(UT) | 2%(T),1 | 0.69%(UT) |

| Type | VTH | VTH | VBE | VTH | VBE |

| TC (ppm/℃) | 5.6(T) | 64(T) | 75(UT) | 84.5(UT) | 19.6(UT) |

| Supply | 0.8 V | 0.45 V | 0.5 V | 0.4 V | 2.8 V |

| Output Voltage | 428 mV | 120 mV | 500 mV | 212 mV | 1.17 V |

| Current Consumption | 16.3 μA | 32.4 nA | 64 nA | 480 nA | 78 nA |

| Line regulation | 1 mV/V | 1.2 mV/V | 10 mV/V | 2 mV/V | 0.59 mV/V |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xu, J.; Wang, Y.; Wu, M.; Zhang, R.; Wei, S.; Zhang, G.; Yang, C.-F. A High-Accuracy Ultra-Low-Power Offset-Cancelation On-Off Bandgap Reference for Implantable Medical Electronics. Electronics 2019, 8, 814. https://doi.org/10.3390/electronics8070814

Xu J, Wang Y, Wu M, Zhang R, Wei S, Zhang G, Yang C-F. A High-Accuracy Ultra-Low-Power Offset-Cancelation On-Off Bandgap Reference for Implantable Medical Electronics. Electronics. 2019; 8(7):814. https://doi.org/10.3390/electronics8070814

Chicago/Turabian StyleXu, Jiangtao, Yawei Wang, Minshun Wu, Ruizhi Zhang, Sufen Wei, Guohe Zhang, and Cheng-Fu Yang. 2019. "A High-Accuracy Ultra-Low-Power Offset-Cancelation On-Off Bandgap Reference for Implantable Medical Electronics" Electronics 8, no. 7: 814. https://doi.org/10.3390/electronics8070814

APA StyleXu, J., Wang, Y., Wu, M., Zhang, R., Wei, S., Zhang, G., & Yang, C.-F. (2019). A High-Accuracy Ultra-Low-Power Offset-Cancelation On-Off Bandgap Reference for Implantable Medical Electronics. Electronics, 8(7), 814. https://doi.org/10.3390/electronics8070814