Zi-CAM: A Power and Resource Efficient Binary Content-Addressable Memory on FPGAs

Abstract

1. Introduction

2. Motivations and Key Contributions

2.1. Motivations

2.2. Key Contributions

- Unlike Xilinx CAM [16], there are no useless SRAM cells in the Zi-CAM architecture for any size of CAM implementation on FPGA.

- The update latency of the proposed CAM is only 64 clock cycles, compared to the 513 clock cycles of other RAM-based CAM architectures [23,24], which makes it more suitable for practical applications where the data is frequently updated. The update latency of Zi-CAM is independent of the size of CAM while in other RAM-based CAMs, it varies with the size of CAM.

3. Related Works

4. Proposed Architecture

4.1. Terminology

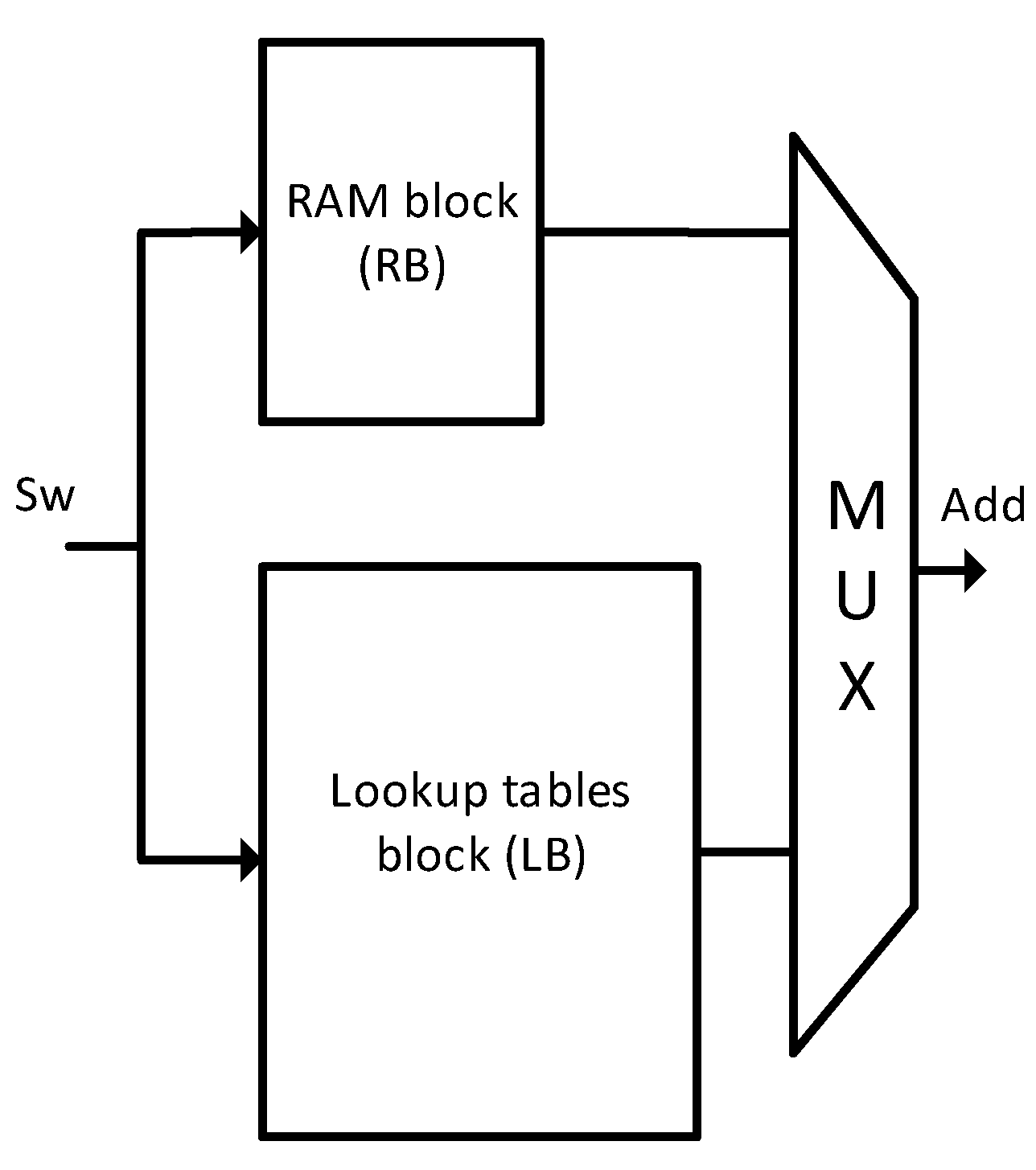

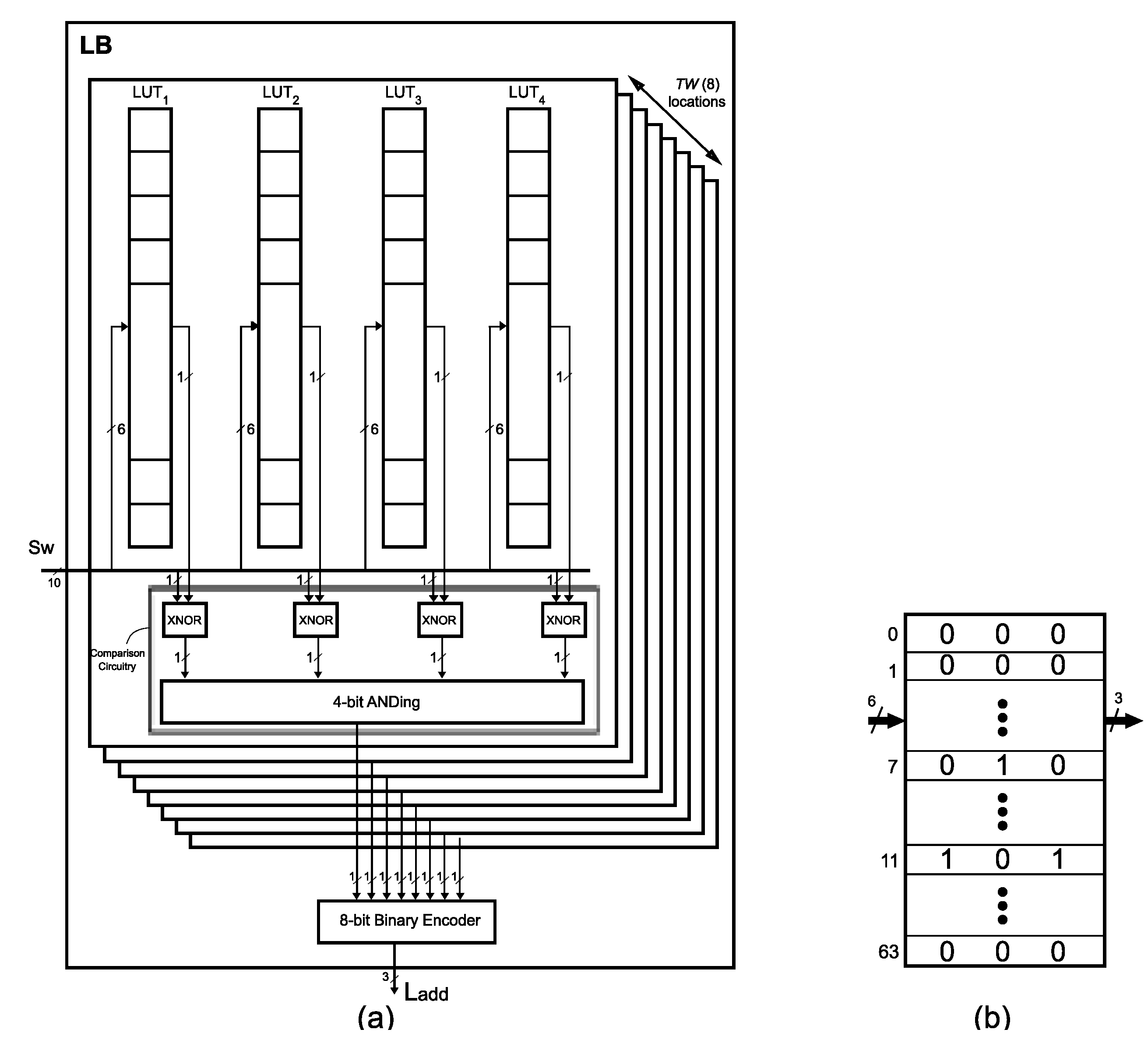

4.2. Zi-CAM Architecture

| Algorithm 1: Searching Operation in Zi-CAM (Size: 8 × 10) |

| Input: Search word (Sw) Output: Address of the search word in CAM

|

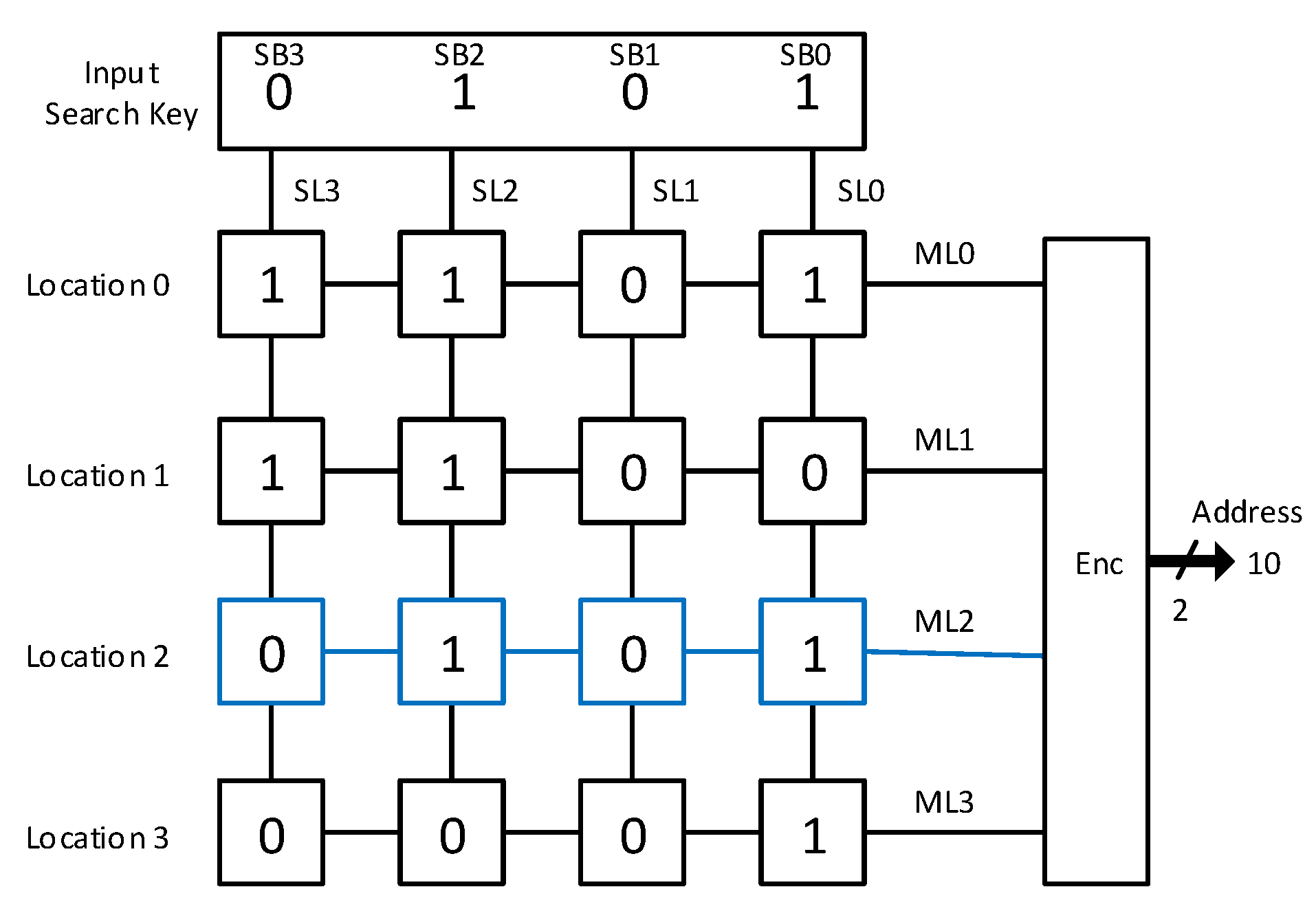

4.3. An Example

4.4. Searching Operation

4.5. Updating Mechanism

4.6. A Generalized Form

5. Implementation Results

6. Conclusions and Future Work

Author Contributions

Funding

Conflicts of Interest

References

- Han, Y.; Virupakshappa, K.; Vitor Silva Pinto, E.; Oruklu, E. Hardware/Software co-design of a traffic sign recognition system using zynq FPGAs. Electronics 2015, 4, 1062–1089. [Google Scholar] [CrossRef]

- Madhavan, A.; Sherwood, T.; Strukov, D.B. High-Throughput Pattern Matching With CMOL FPGA Circuits: Case for Logic-in-Memory Computing. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2018, 26, 2759–2772. [Google Scholar] [CrossRef]

- Joshi, S.; Li, D.; Ogrenci-Memik, S.; Deptuch, G.; Hoff, J.; Jindariani, S.; Liu, T.; Olsen, J.; Tran, N. Multi-Vdd Design for Content Addressable Memories (CAM): A Power-Delay Optimization Analysis. J. Low Power Electron. Appl. 2018, 8, 25. [Google Scholar] [CrossRef]

- Boguslawski, B.; Heitzmann, F.; Larras, B.; Seguin, F. Energy-Efficient Associative Memory Based on Neural Cliques. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 376–380. [Google Scholar] [CrossRef]

- Jothi, D.; Sivakumar, R. Design and Analysis of Power Efficient Binary Content Addressable Memory (PEBCAM) Core Cells. Circuits Syst. Signal Process. 2018, 37, 1422–1451. [Google Scholar] [CrossRef]

- Kittur, H.M.; Zackriya, V.M. Precharge-Free, Low-Power Content-Addressable Memory. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2016, 24, 2614–2621. [Google Scholar]

- Le, D.H.; Tran, B.T.; Inoue, K.; Pham, C.K. A CAM-based information detection hardware system for fast image matching on FPGA. IEICE Trans. Electron. 2014, 97, 65–76. [Google Scholar] [CrossRef]

- Mishra, S.; Dandapat, A. Energy-efficient adaptive match-line controller for large-scale associative storage. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 710–714. [Google Scholar] [CrossRef]

- Chen, T.S.; Lee, D.Y.; Liu, T.T.; Wu, A.Y. Dynamic Reconfigurable Ternary Content Addressable Memory for OpenFlow-Compliant Low-Power Packet Processing. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 1661–1672. [Google Scholar] [CrossRef]

- Mujahid, O.; Ullah, Z.; Mahmood, H.; Hafeez, A. Fast Pattern Recognition Through an LBP Driven CAM on FPGA. IEEE Access 2018, 6, 39525–39531. [Google Scholar] [CrossRef]

- Singh, S.; Shekhar, C.; Vohra, A. FPGA-based real-time motion detection for automated video surveillance systems. Electronics 2016, 5, 10. [Google Scholar] [CrossRef]

- Karam, R.; Puri, R.; Ghosh, S.; Bhunia, S. Emerging trends in design and applications of memory-based computing and content-addressable memories. Proc. IEEE 2015, 103, 1311–1330. [Google Scholar] [CrossRef]

- Nguyen, X.T.; Hoang, T.T.; Nguyen, H.T.; Inoue, K.; Pham, C.K. An FPGA-Based Hardware Accelerator for Energy-Efficient Bitmap Index Creation. IEEE Access 2018, 6, 16046–16059. [Google Scholar] [CrossRef]

- Ullah, Z.; Ilgon, K.; Baeg, S. Hybrid partitioned SRAM-based ternary content addressable memory. IEEE Trans. Circuits Syst. I Regul. Pap. 2012, 59, 2969–2979. [Google Scholar] [CrossRef]

- Ahmed, A.; Park, K.; Baeg, S. Resource-Efficient SRAM-Based Ternary Content Addressable Memory. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2017, 25, 1583–1587. [Google Scholar] [CrossRef]

- Locke, K. Parameterizable Content-Addressable Memory. Xilinx Application Note XAPP1151. 2011. Available online: https://www.xilinx.com/support/documentation/application_notes/xapp1151_Param_CAM.pdf (accessed on 24 March 2019).

- Irfan, M.; Ullah, Z. G-AETCAM: Gate-Based Area-Efficient Ternary Content-Addressable Memory on FPGA. IEEE Access 2017, 5, 20785–20790. [Google Scholar] [CrossRef]

- Ullah, Z. LH-CAM: Logic-Based Higher Performance Binary CAM Architecture on FPGA. IEEE Embed. Syst. Lett. 2017, 9, 29–32. [Google Scholar] [CrossRef]

- Mahmood, H.; Ullah, Z.; Mujahid, O.; Ullah, I.; Hafeez, A. Beyond the Limits of Typical Strategies: Resources Efficient FPGA-based TCAM. IEEE Embed. Syst. Lett. 2018. [Google Scholar] [CrossRef]

- Nash, J. Distributed-Memory-Based FFT Architecture and FPGA Implementations. Electronics 2018, 7, 116. [Google Scholar] [CrossRef]

- Ullah, Z.; Jaiswal, M.K.; Cheung, R.C.; So, H.K. UE-TCAM: An ultra efficient SRAM-based TCAM. In Proceedings of the TENCON 2015–2015 IEEE Region 10 Conference, Macao, China, 1–4 November 2015; pp. 1–6. [Google Scholar]

- Ullah, Z.; Jaiswal, M.K.; Cheung, R.C. Z-TCAM: An SRAM-based architecture for TCAM. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2015, 23, 402–406. [Google Scholar] [CrossRef]

- Ullah, I.; Ullah, Z.; Lee, J.A. EE-TCAM: An Energy-Efficient SRAM-Based TCAM on FPGA. Electronics 2018, 7, 186. [Google Scholar] [CrossRef]

- Syed, F.; Ullah, Z.; Jaiswal, M.K. Fast Content Updating Algorithm for an SRAM based TCAM on FPGA. IEEE Embed. Syst. Lett. 2017. [Google Scholar] [CrossRef]

- Somasundaram, M. Circuits to Generate a Sequential Index for an Input Number in a Pre-Defined List of Numbers. U.S. Patent 7,155,563, 26 December 2006. [Google Scholar]

- Somasundaram, M. Memory and Power Efficient Mechanism for Fast Table Lookup. U.S. Patent 7,296,113, 9 January 2007. [Google Scholar]

- Jiang, W. Scalable ternary content addressable memory implementation using FPGAs. In Proceedings of the Ninth ACM/IEEE Symposium on Architectures for Networking and Communications Systems, San Jose, CA, USA, 21–22 October 2013; pp. 71–82. [Google Scholar]

- Ullah, Z.; Jaiswal, M.K.; Cheung, R.C. E-TCAM: An efficient SRAM-based architecture for TCAM. Circuits Syst. Signal Process. 2014, 33, 3123–3144. [Google Scholar] [CrossRef]

- Lee, D.-Y.; Wang, C.-C.; Wu, A.-Y. Bundle-Updatable SRAM-Based TCAM Design for OpenFlow-Compliant Packet Processor. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019. [Google Scholar] [CrossRef]

- Nishikata, D.; Ali, M.A.B.M.; Hosoda, K.; Matsumoto, H.; Nakamura, K. Design and measurement of fully digital ternary content addressable memory using ratioless static random access memory cells and hierarchical-AND matching comparator. Jpn. J. Appl. Phys. 2018, 57, 04FF11. [Google Scholar] [CrossRef]

- Ullah, I.; Ullah, Z.; Lee, J.A. Efficient TCAM design based on multipumping-enabled multiported SRAM on FPGA. IEEE Access 2018, 6, 19940–19947. [Google Scholar] [CrossRef]

- Alfke, P. Creative Uses of Block RAM. White Paper: Virtex and Spartan FPGA Families, Xilinx. 2008. Available online: https://pubweb.eng.utah.edu/~cs3710/xilinx-docs/wp335.pdf (accessed on 24 March 2019).

- Xilinx. Virtex-6 FPGA Family. Available online: http://www.xilinx.com (accessed on 24 March 2019).

- Ullah, I.; Ullah, Z.; Afzaal, U.; Lee, J.-A. DURE: An Energy-and Resource-Efficient TCAM Architecture for FPGAs With Dynamic Updates. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019. [Google Scholar] [CrossRef]

- Yu, Y.; Belazzougui, D.; Qian, C.; Zhang, Q. Memory-Efficient and Ultra-Fast Network Lookup and Forwarding Using Othello Hashing. IEEE/ACM Trans. Netw. 2018, 26, 1151–1164. [Google Scholar] [CrossRef]

- Xilinx. Xpower Analyzer. Available online: https://www.xilinx.com/support/documentation/sw_manuals/xilinx11/xpa_c_filetypes.htm (accessed on 24 March 2019).

| Notation | Definition |

|---|---|

| Sw | Search Word |

| r | Number of bits in search word; Width of CAM memory |

| TW | Total words in CAM; Depth of CAM memory |

| M_bits | Most significant bits (MSBs) of search word; Number of bits in M_bits are represented by p |

| L_bits | Least significant bits (LSBs) of search word; Number of bits in L_bits are represented by q |

| LB | Lookup tables (LUTs) block |

| RB | Random-access memory (RAM) block |

| s_b | Stored bit, a single bit coming out of lookup table |

| Ladd | Address generated by LB |

| Radd | Address generated by RB |

| Add | Output of CAM. The address where search key is found. |

| Flag_bits | A one bit signal which activates/deactivates RB and LB |

| Location # | BCAM Data |

|---|---|

| 0 | 0 0 0 1 0 0 1 1 0 0 |

| 1 | 0 1 0 0 1 1 0 0 0 1 |

| 2 | 0 0 0 1 1 1 0 0 0 0 |

| 3 | 0 1 0 0 0 0 1 0 1 0 |

| 4 | 0 0 1 1 0 0 1 1 0 0 |

| 5 | 0 0 1 0 1 1 0 0 0 0 |

| 6 | 1 1 0 0 1 0 0 1 1 0 |

| 7 | 1 0 0 1 0 1 0 0 1 1 |

| CAM Type | CAM Size | Device | LUTs | BRAMs | SRAM | Power | Speed | E/bit/s | Latency |

|---|---|---|---|---|---|---|---|---|---|

| (64-bit) | Cells (#) | (mW) | (MHz) | (fJ) | (cc) | ||||

| HP-CAM [14] | 64 × 36 | Virtex-6 | 1292 | 32 (18k) | 672,512 | 58 | 165 | 251.7 | 5 |

| Z-CAM [22] | 64 × 36 | Virtex-6 | 630 | 32 (18k) | 630,144 | 41 | 180 | 177.9 | 4 |

| E-CAM [28] | 64 × 36 | Virtex-6 | 185 | 32 (18k) | 601,664 | 39 | 215 | 169.3 | 3 |

| UE-CAM [21] | 64 × 36 | Virtex-6 | 171 | 16 (18k) | 305,856 | 24 | 267 | 105.7 | 2 |

| REST [15] | 72 × 28 | Kintex-7 | 130 | 1 (36k) | 45,184 | 113 | 50 | 560.5 | 5 |

| Zi-CAM | 64 × 36 | Virtex-6 | 3254 | 0 | 208,256 | 16.6 | 51 | 72.04 | 2 |

| Zi-CAM | 512 × 36 | Virtex-6 | 2,4551 | 0 | 1,571,264 | 93.3 | 38 | 50.6 | 3 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Irfan, M.; Ullah, Z.; C. C. Cheung, R. Zi-CAM: A Power and Resource Efficient Binary Content-Addressable Memory on FPGAs. Electronics 2019, 8, 584. https://doi.org/10.3390/electronics8050584

Irfan M, Ullah Z, C. C. Cheung R. Zi-CAM: A Power and Resource Efficient Binary Content-Addressable Memory on FPGAs. Electronics. 2019; 8(5):584. https://doi.org/10.3390/electronics8050584

Chicago/Turabian StyleIrfan, Muhammad, Zahid Ullah, and Ray C. C. Cheung. 2019. "Zi-CAM: A Power and Resource Efficient Binary Content-Addressable Memory on FPGAs" Electronics 8, no. 5: 584. https://doi.org/10.3390/electronics8050584

APA StyleIrfan, M., Ullah, Z., & C. C. Cheung, R. (2019). Zi-CAM: A Power and Resource Efficient Binary Content-Addressable Memory on FPGAs. Electronics, 8(5), 584. https://doi.org/10.3390/electronics8050584