Gallium Nitride Normally-Off Vertical Field-Effect Transistor Featuring an Additional Back Current Blocking Layer Structure

Abstract

1. Introduction

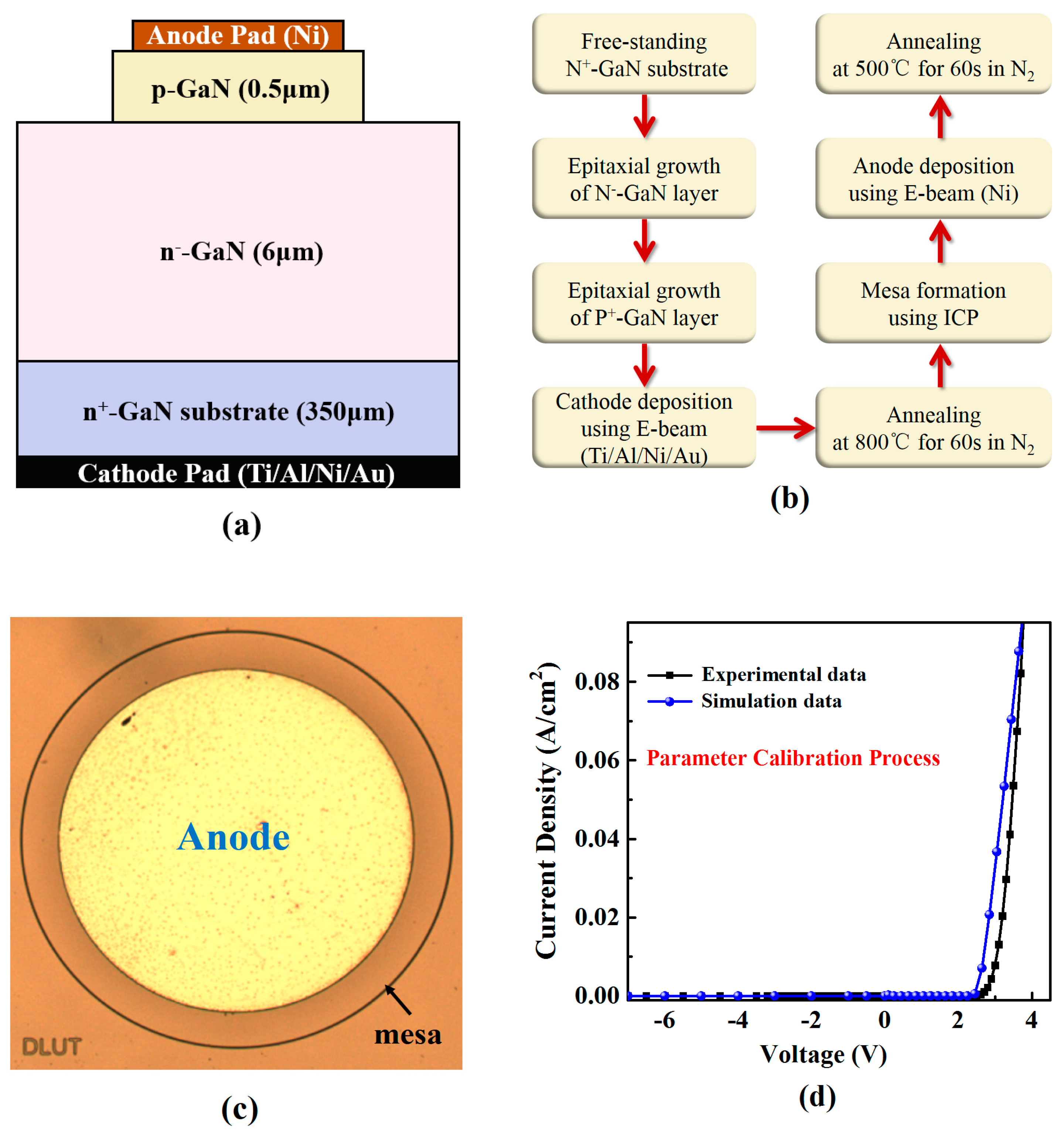

2. The Device Structure

3. Fabrication Work and Parameter Calibration

3.1. Fabrication Process of the PN-Junction Devices

3.2. Parameter Calibration Process

4. Results and Discussion

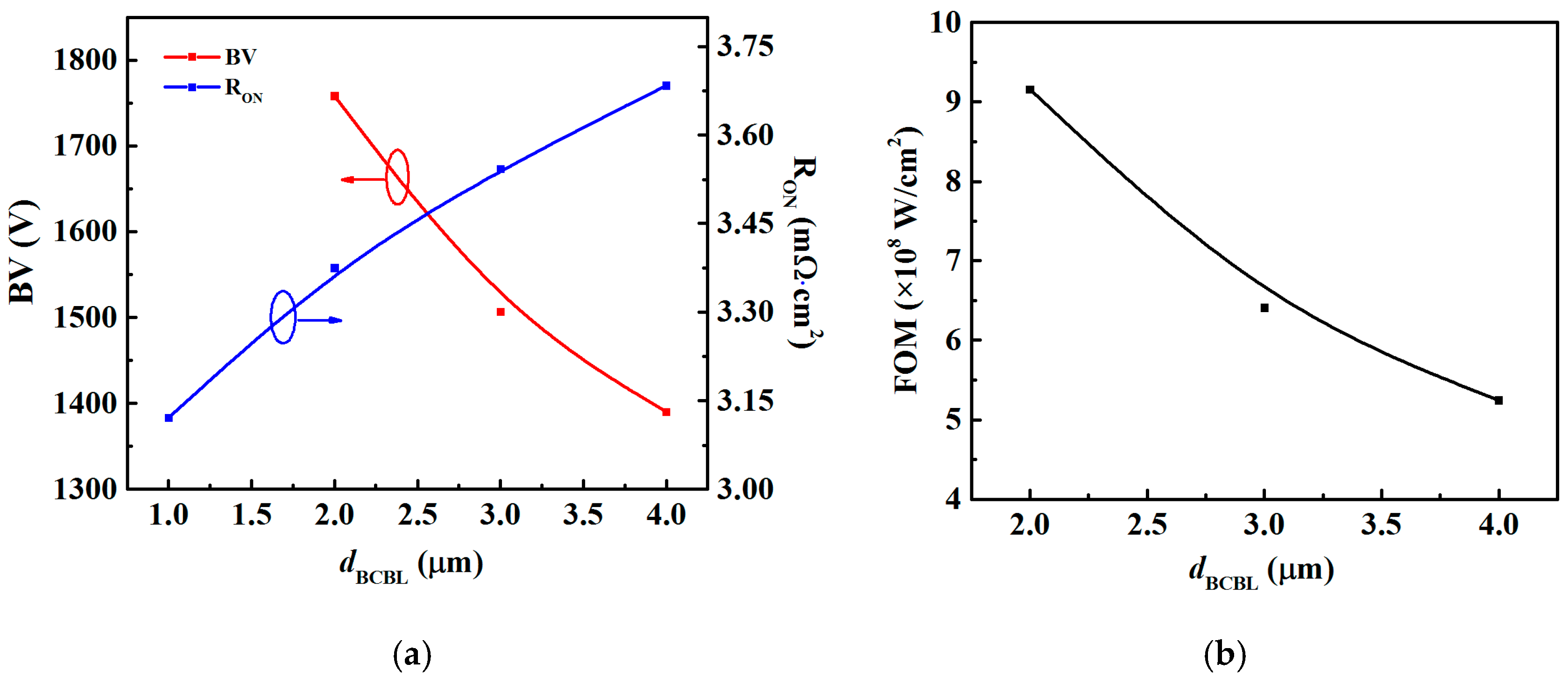

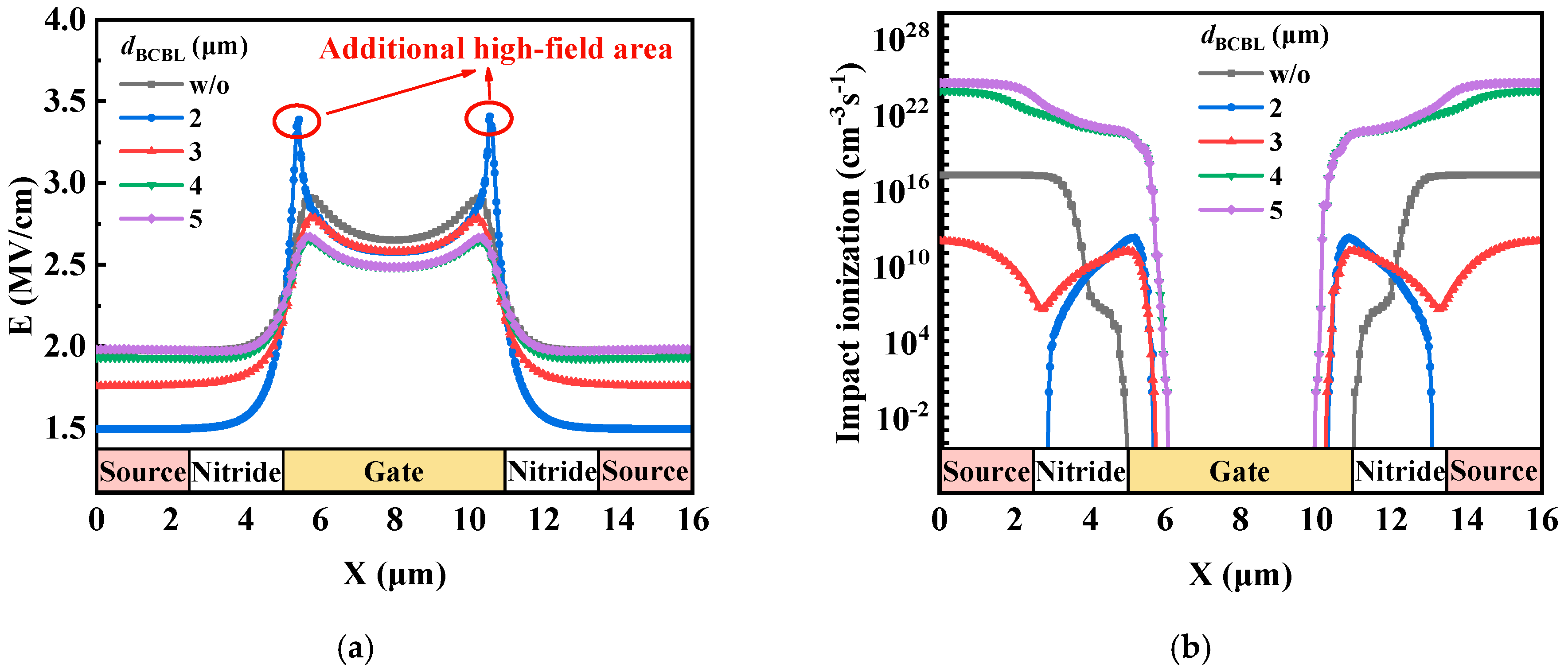

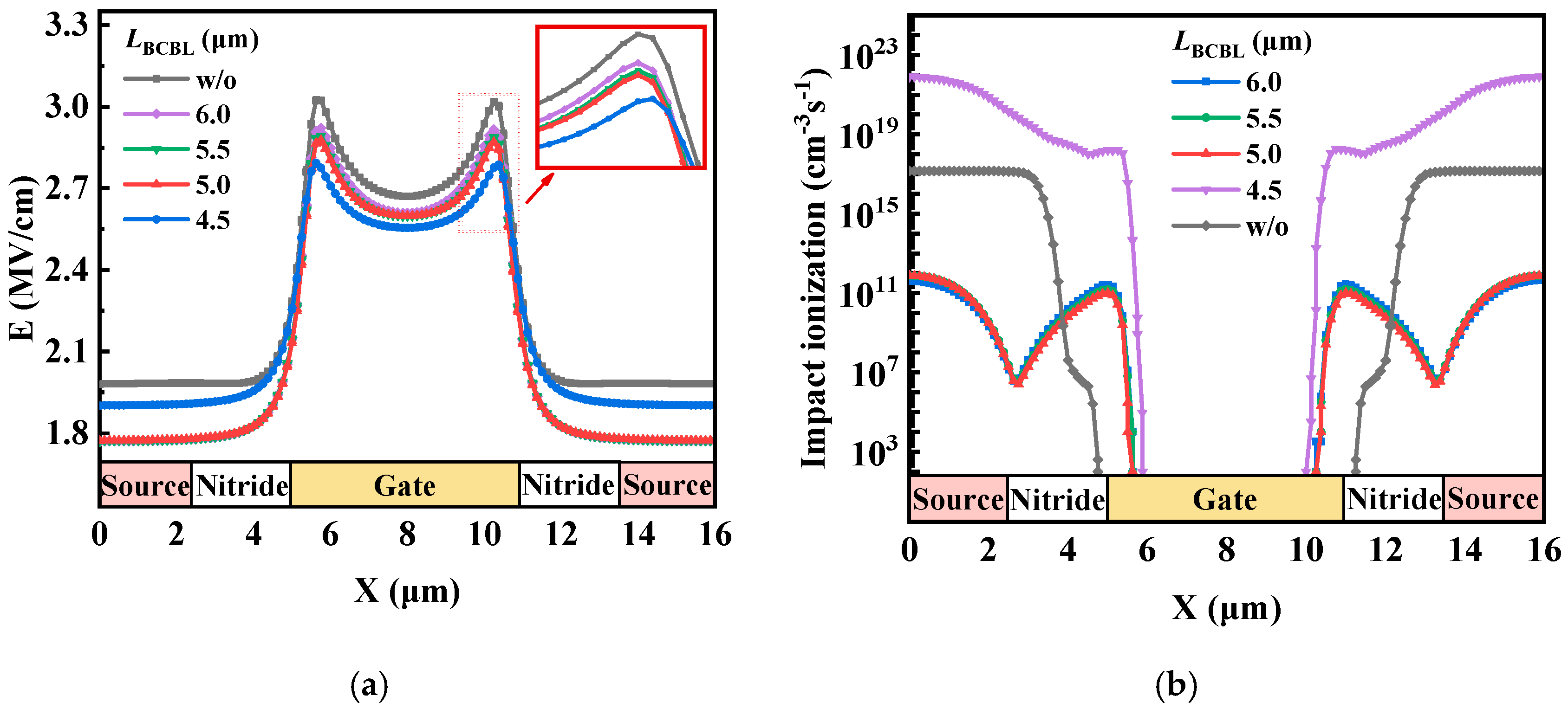

4.1. Parameter Optimization of the BCBL

4.1.1. Optimization of dBCBL

4.1.2. Optimization of LBCBL

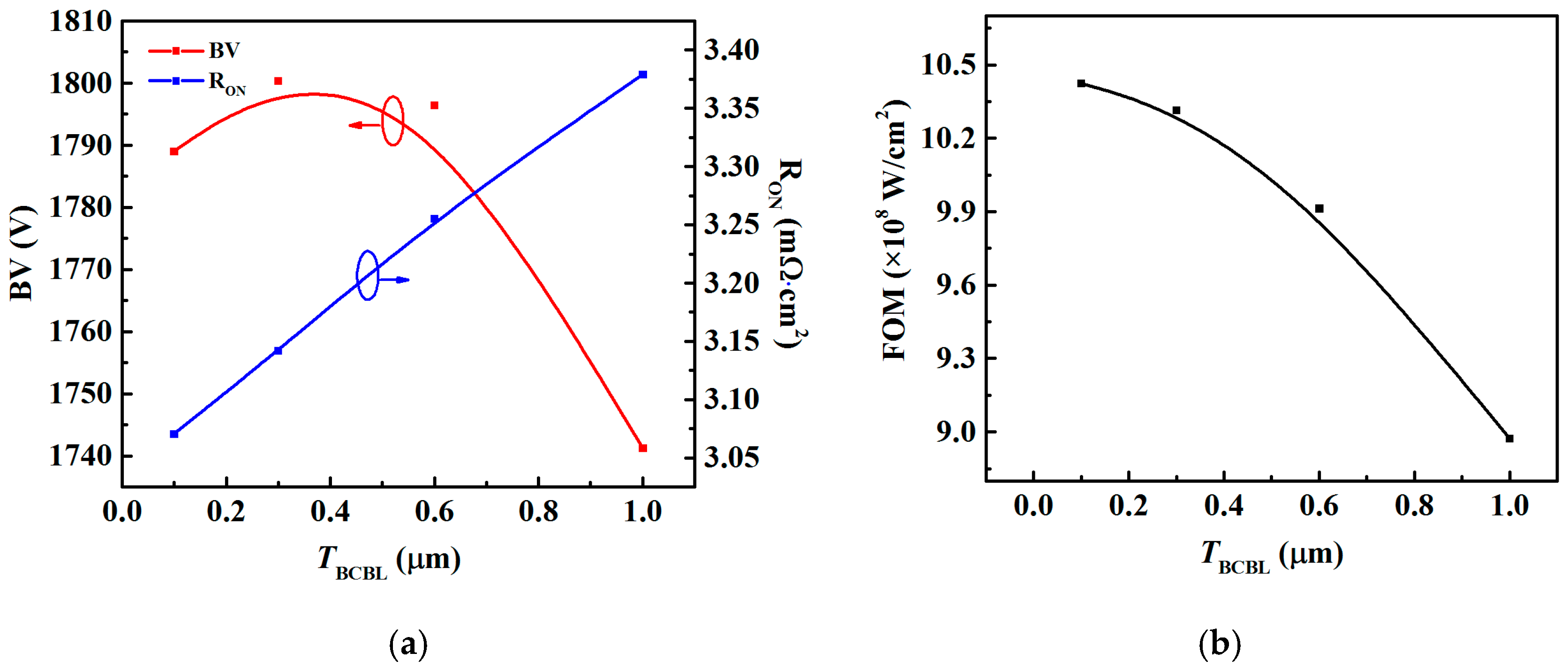

4.1.3. Optimization of TBCBL

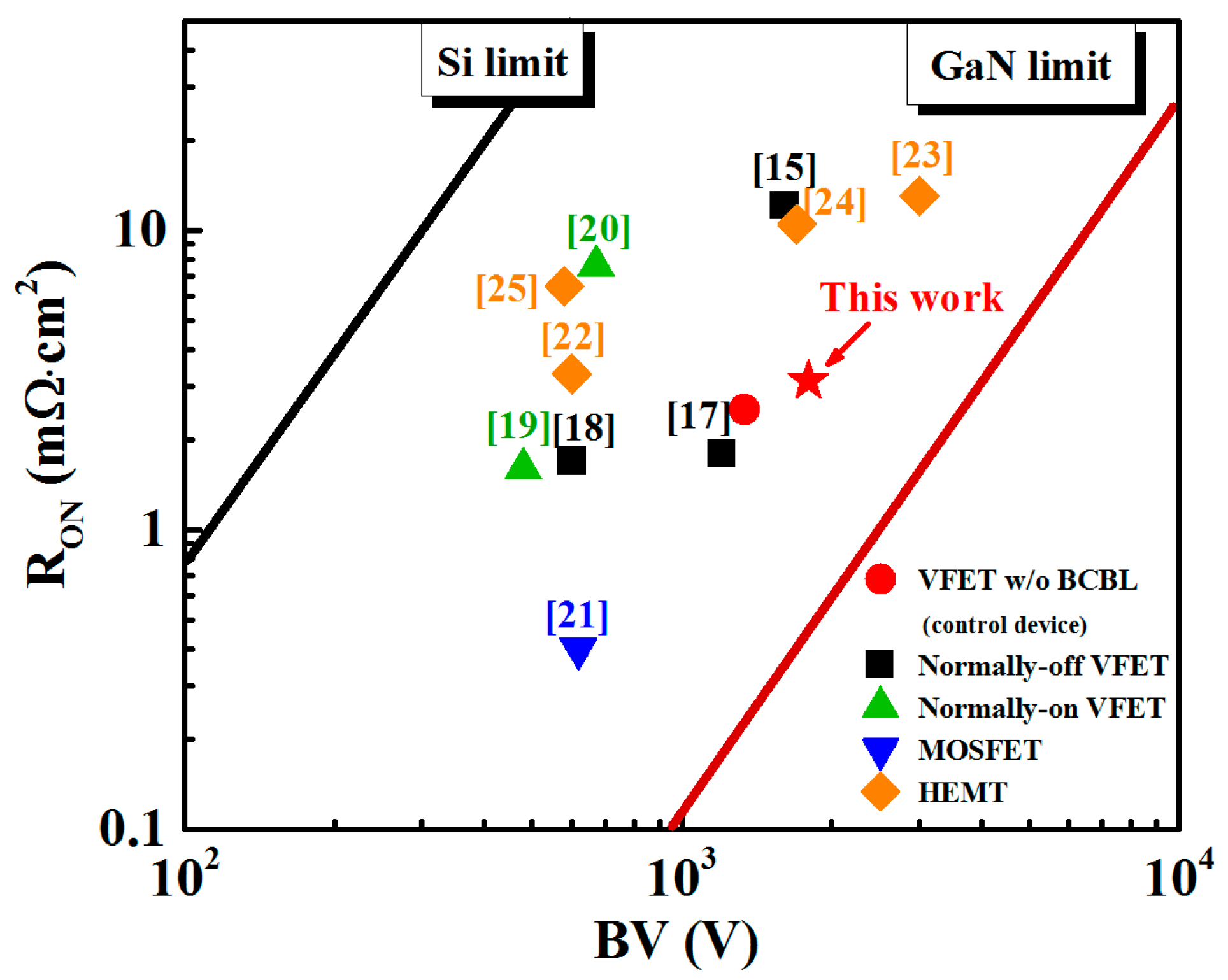

4.2. Performances of the Optimized BCBL-VFET

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Chen, K.J.; Haberlen, O.; Lidow, A.; Tsai, C.L.; Ueda, T.; Uemoto, Y.; Wu, Y.F. GaN-on-Si Power Technology: Devices and Applications. IEEE Trans. Electron. Devices 2017, 64, 779–795. [Google Scholar] [CrossRef]

- Kachi, T. Recent progress of GaN power devices for automotive applications. Jpn. J. Appl. Phys. 2014, 53, 100210. [Google Scholar] [CrossRef]

- Ambacher, O.; Foutz, B.; Smart, J.; Shealy, J.R.; Weimann, N.G.; Chu, K.; Murphy, M.; Sierakowski, A.J.; Schaff, W.J.; Eastman, L.F.; et al. Two dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures. J. Appl. Phys. 2000, 87, 334–344. [Google Scholar] [CrossRef]

- Miao, M.S.; Weber, J.R.; Van de Walle, C.G. Oxidation and the origin of the two-dimensional electron gas in AlGaN/GaN heterostructures. J. Appl. Phys. 2010, 107, 123713. [Google Scholar] [CrossRef]

- Oka, T.; Nozawa, T. AlGaN/GaN Recessed MIS-Gate HFET With High-Threshold-Voltage Normally-Off Operation for Power Electronics Applications. IEEE Electron. Device Lett. 2008, 29, 668–670. [Google Scholar] [CrossRef]

- Lee, F.; Su, L.; Wang, C.; Wu, Y.; Huang, J. Impact of Gate Metal on the Performance of p-GaN/AlGaN/GaN High Electron Mobility Transistors. IEEE Electron. Device Lett. 2015, 36, 232–234. [Google Scholar] [CrossRef]

- Jiang, H.; Tang, C.W.; Lau, K.M. Enhancement-Mode GaN MOS-HEMTs With Recess-Free Barrier Engineering and High-k ZrO2 Gate Dielectric. IEEE Electron. Device Lett. 2018, 39, 405–408. [Google Scholar] [CrossRef]

- Dai, S.; Zhou, Y.; Zhong, Y.; Zhang, K.; Zhu, G.; Gao, H.; Sun, Q.; Chen, T.; Yang, H. High fT AlGa(In)N/GaN HEMTs Grown on Si With a Low Gate Leakage and a High ON/OFF Current Ratio. IEEE Electron. Device Lett. 2018, 39, 576–579. [Google Scholar] [CrossRef]

- Anderson, T.J.; Tadjer, M.J.; Hite, J.K.; Greenlee, J.D.; Koehler, A.D.; Hobart, K.D.; Kub, F.J. Effect of Reduced Extended Defect Density in MOCVD Grown AlGaN/GaN HEMTs on Native GaN Substrates. IEEE Electron. Device Lett. 2016, 37, 28–30. [Google Scholar] [CrossRef]

- Huang, H.L.; Liang, Y.C. Formation of combined partially recessed and multiple fluorinated-dielectric layers gate structures for high threshold voltage GaN-based HEMT power devices. Solid-State Electron. 2015, 114, 148–154. [Google Scholar] [CrossRef]

- Ben-Yaacov, I.; Seck, Y.K.; Mishra, U.K.; DenBaars, S.P. AlGaN/GaN current aperture vertical electron transistors with regrown channels. J. Appl. Phys. 2004, 95, 2073–2078. [Google Scholar] [CrossRef]

- Kanechika, M.; Sugimoto, M.; Soejima, N.; Ueda, H.; Ishiguro, O.; Kodama, M.; Hnyashi, E.; Itoh, K.; Uesugi, T.; Kachi, T. A vertical insulated gate AlGaN/GaN heterojunction field-effect transistor. Jpn. J. Appl. Phys. 2007, 46, L503–L505. [Google Scholar] [CrossRef]

- Ozbek, A.M.; Baliga, B.J. Planar Nearly Ideal Edge-Termination Technique for GaN Devices. IEEE Electron. Device Lett. 2011, 32, 300–302. [Google Scholar] [CrossRef]

- Chowdhury, S.; Wong, M.H.; Swenson, B.L.; Mishra, U.K. CAVET on Bulk GaN Substrates Achieved With MBE-Regrown AlGaN/GaN Layers to Suppress Dispersion. IEEE Electron. Device Lett. 2012, 33, 41–43. [Google Scholar] [CrossRef]

- Oka, T.; Ueno, Y.; Ina, T.; Hasegawa, K. Vertical GaN-based trench metal oxide semiconductor field-effect transistors on a free-standing GaN substrate with blocking voltage of 1.6 kV. Appl Phys Express 2014, 7, 021002. [Google Scholar] [CrossRef]

- Baliga, B.J. Fundamentals of Power Semiconductor Devices; Springer Science & Business Media: Berlin, Germany, 2008; pp. 359–365. [Google Scholar]

- Oka, T.; Ina, T.; Ueno, Y.; Nishii, J. 1.8 mΩ·cm2 vertical GaN-based trench metal–oxide–semiconductor field-effect transistors on a free-standing GaN substrate for 1.2-kV-class operation. Appl. Phys. Express 2015, 8, 054101. [Google Scholar] [CrossRef]

- Li, R.; Cao, Y.; Chen, M.; Chu, R. 600 V/1.7 Ω Normally-Off GaN Vertical Trench Metal–Oxide–Semiconductor Field-Effect Transistor. IEEE Electron Device Lett. 2016, 37, 1466–1469. [Google Scholar] [CrossRef]

- Shrestha, N.M.; Li, Y.M.; Chang, E.Y. Optimal design of the multiple-apertures-GaN-based vertical HEMTs with SiO2 current blocking layer. J. Comput. Electron. 2016, 15, 154–162. [Google Scholar] [CrossRef]

- Yaegassi, S.; Okada, M.; Saitou, Y.; Yokoyama, M.; Nakata, K.; Katayama, K.; Ueno, M.; Kiyama, M.; Katsuyama, T.; Nakamura, T. Vertical heterojunction field-effect transistors utilizing re-grown AlGaN/GaN two-dimensional electron gas channels on GaN substrates. Phys. Status Solidi C 2011, 8, 450–452. [Google Scholar] [CrossRef]

- Kang, E.G.; Kim, Y.T. Design of Trench Gate GaN Power MOSFET using Al2O3 Gate Oxide. J. Phys. Conf. Ser. 2012, 352, 012025. [Google Scholar] [CrossRef]

- Saito, W.; Takada, Y.; Kuraguchi, M.; Tsuda, K.; Omura, I.; Ogura, T. Design and demonstration of high breakdown voltage GaN high electron mobility transistor (HEMT) using field plate structure for power electronics applications. Jpn. J. Appl. Phys. 2004, 43, 2239–2242. [Google Scholar] [CrossRef]

- Dogmus, E.; Zegaoui, M.; Medjdoub, F. GaN-on-silicon high-electron-mobility transistor technology with ultra-low leakage up to 3000 V using local substrate removal and AlN ultra-wide bandgap. Appl. Phys. Express 2018, 11, 034102. [Google Scholar] [CrossRef]

- Zhao, Z.Q.; Zhao, Z.Y.; Luo, Q.; Du, J.F. High-voltage RESURF AlGaN/GaN high electron mobility transistor with back electrode. Electron. Lett. 2013, 49, 1638–1640. [Google Scholar] [CrossRef]

- Huang, H.; Liang, Y.C.; Samudra, G.S.; Ngo, C.L.L. Normally-Off AlGaN/GaN-on-Si MIS-HEMTs Using Combined Partially Recessed and Fluorinated Trap-Charge Gate Structures. IEEE Electron. Device Lett. 2014, 35, 569–571. [Google Scholar] [CrossRef]

- Campbell, C.F.; Balistreri, A.; Kao, M.Y.; Dumka, D.C.; Hitt, J. GaN Takes the Lead. IEEE Microw. Mag. 2012, 13, 44–53. [Google Scholar] [CrossRef]

- Crupi, G.; Raffo, A.; Avolio, G.; Schreurs, D.M.M.P.; Vannini, G.; Caddemi, A. Temperature Influence on GaN HEMT Equivalent Circuit. IEEE Microw. Wirel. Components 2016, 26, 813–815. [Google Scholar] [CrossRef]

- Nalli, A.; Raffo, A.; Crupi, G.; D’Angelo, S.; Resca, D.; Scappaviva, F.; Salvo, G.; Caddemi, A.; Vannini, G. GaN HEMT Noise Model Based on Electromagnetic Simulations. IEEE Trans. Microw. Theory 2015, 63, 2498–2508. [Google Scholar] [CrossRef]

- Huang, H.; Li, F.; Sun, Z.; Cao, Y. Model Development for Threshold Voltage Stability Dependent on High Temperature Operations in Wide-Bandgap GaN-Based HEMT Power Devices. Micromachines 2018, 9, 658. [Google Scholar] [CrossRef] [PubMed]

- Quaglia, R.; Camarchia, V.; Pirola, M.; Ghione, G. GaN Monolithic Power Amplifiers for Microwave Backhaul Applications. Electronics 2016, 5, 25. [Google Scholar] [CrossRef]

| Parameters | Units | Values | Parameter Captions |

|---|---|---|---|

| LD | μm | 16.0 | Drain length |

| LCA | μm | 5.0 | Length of vertical current aperture |

| LG | μm | 5.0 | Length of the recessed gate |

| LTOP-CBL | μm | 5.5 | Length of the top p-GaN |

| TTOP-CBL | μm | 0.75 | Thickness of the top p-GaN |

| TBUF | μm | 10.0 | Thickness of the buffer layer |

| Symbols | Units | Values | Parameter Descriptions |

|---|---|---|---|

| Eg | eV | 3.4 | Band gap of GaN at 300 K |

| εr | -- | 9.4 | Relative permittivity of GaN |

| λS | eV | 3.4 | Affinity of GaN |

| μn | cm2/Vs | 600 | Electron mobility of GaN |

| μp | cm2/Vs | 20 | Hole mobility of GaN |

| vsat | cm/s | 1.2 × 107 | Electron saturation velocity of GaN |

| Em | V/cm | 3.5 × 106 | Critical electric field of GaN |

| NC | cm−3 | 2.2 × 1018 | Conduction band state density |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Huang, H.; Li, F.; Sun, Z.; Sun, N.; Zhang, F.; Cao, Y.; Zhang, H.; Tao, P. Gallium Nitride Normally-Off Vertical Field-Effect Transistor Featuring an Additional Back Current Blocking Layer Structure. Electronics 2019, 8, 241. https://doi.org/10.3390/electronics8020241

Huang H, Li F, Sun Z, Sun N, Zhang F, Cao Y, Zhang H, Tao P. Gallium Nitride Normally-Off Vertical Field-Effect Transistor Featuring an Additional Back Current Blocking Layer Structure. Electronics. 2019; 8(2):241. https://doi.org/10.3390/electronics8020241

Chicago/Turabian StyleHuang, Huolin, Feiyu Li, Zhonghao Sun, Nan Sun, Feng Zhang, Yaqing Cao, Hui Zhang, and Pengcheng Tao. 2019. "Gallium Nitride Normally-Off Vertical Field-Effect Transistor Featuring an Additional Back Current Blocking Layer Structure" Electronics 8, no. 2: 241. https://doi.org/10.3390/electronics8020241

APA StyleHuang, H., Li, F., Sun, Z., Sun, N., Zhang, F., Cao, Y., Zhang, H., & Tao, P. (2019). Gallium Nitride Normally-Off Vertical Field-Effect Transistor Featuring an Additional Back Current Blocking Layer Structure. Electronics, 8(2), 241. https://doi.org/10.3390/electronics8020241