Partial Isolation Type Saddle-FinFET(Pi-FinFET) for Sub-30 nm DRAM Cell Transistors

Abstract

:1. Introduction

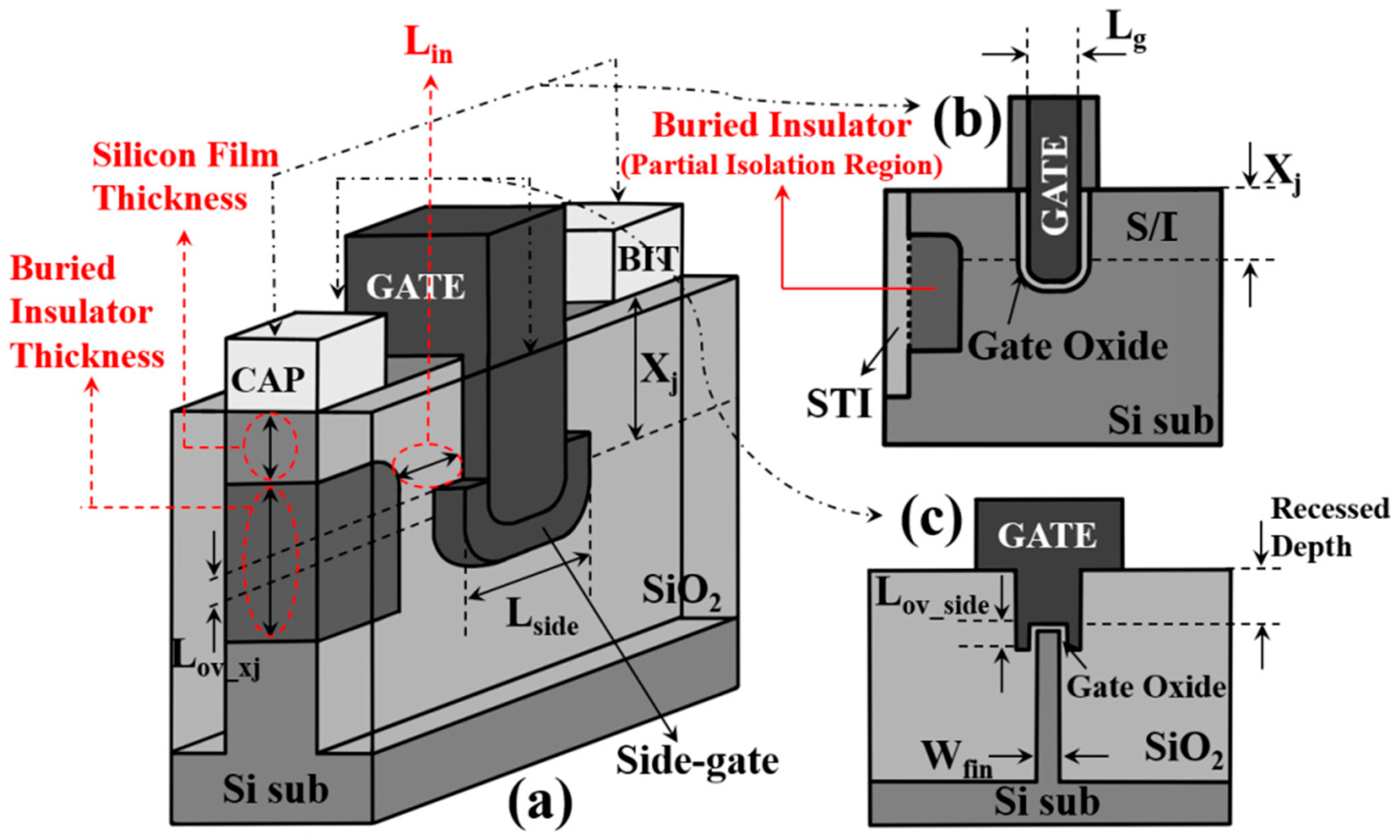

2. Device Structure

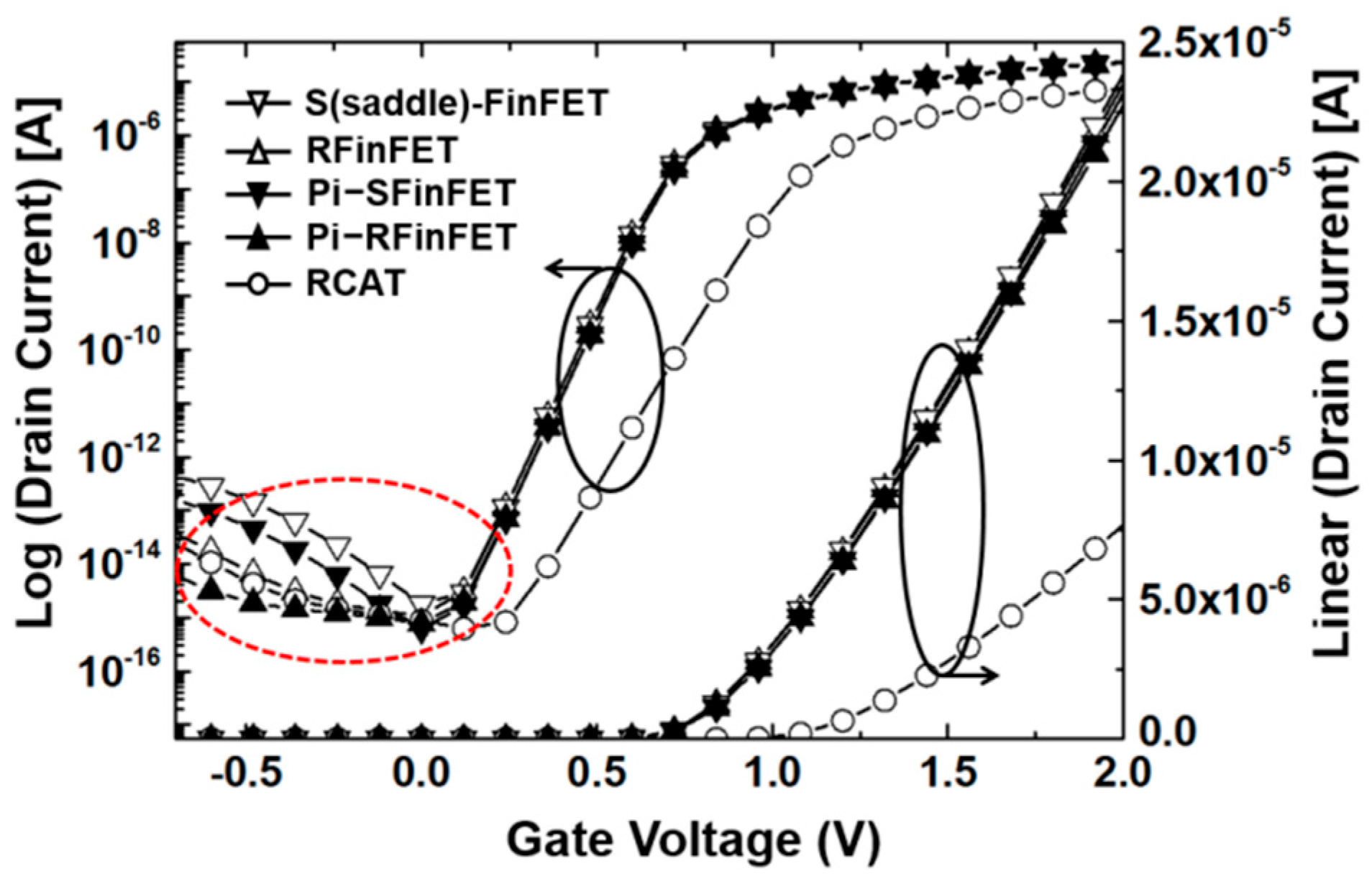

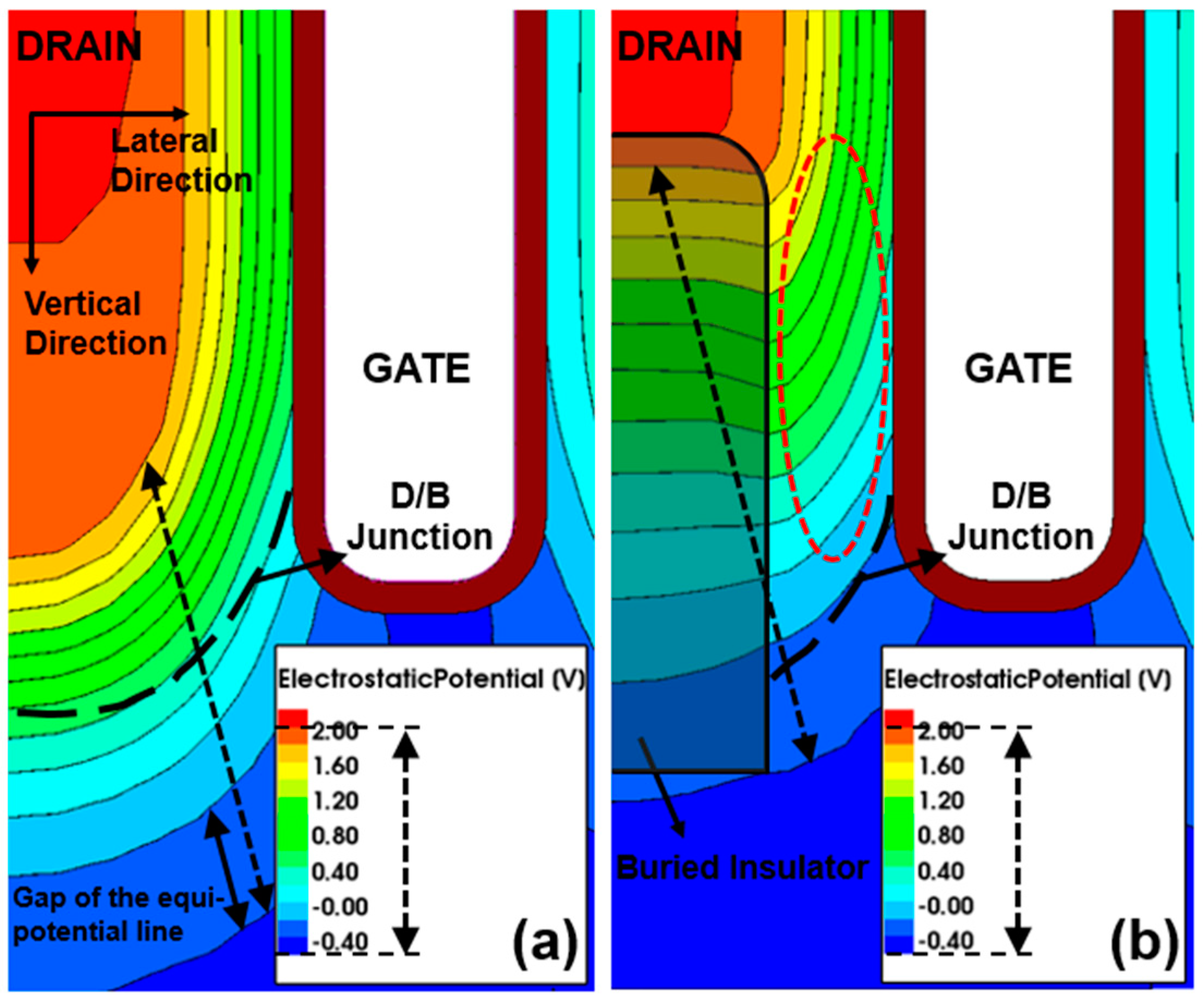

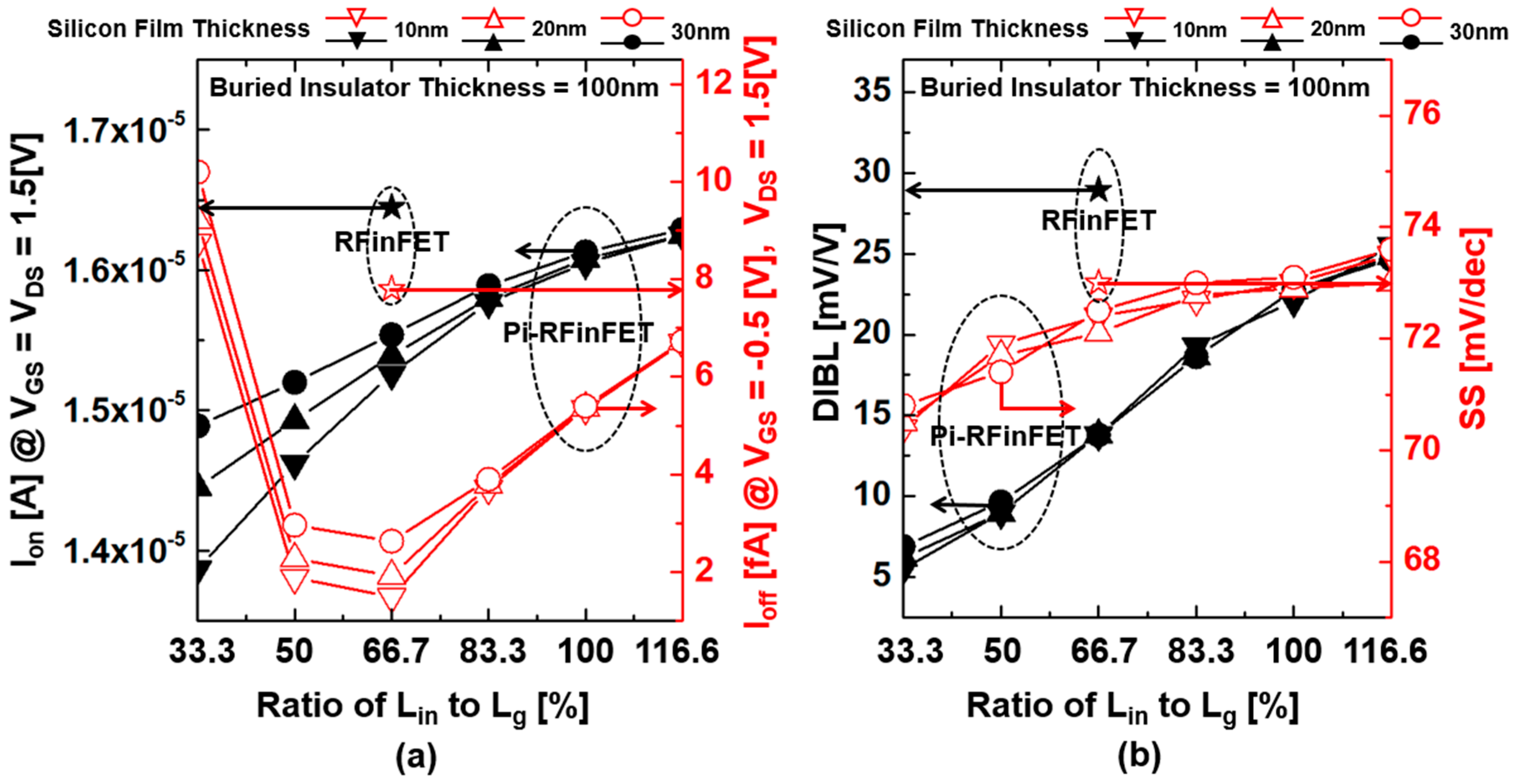

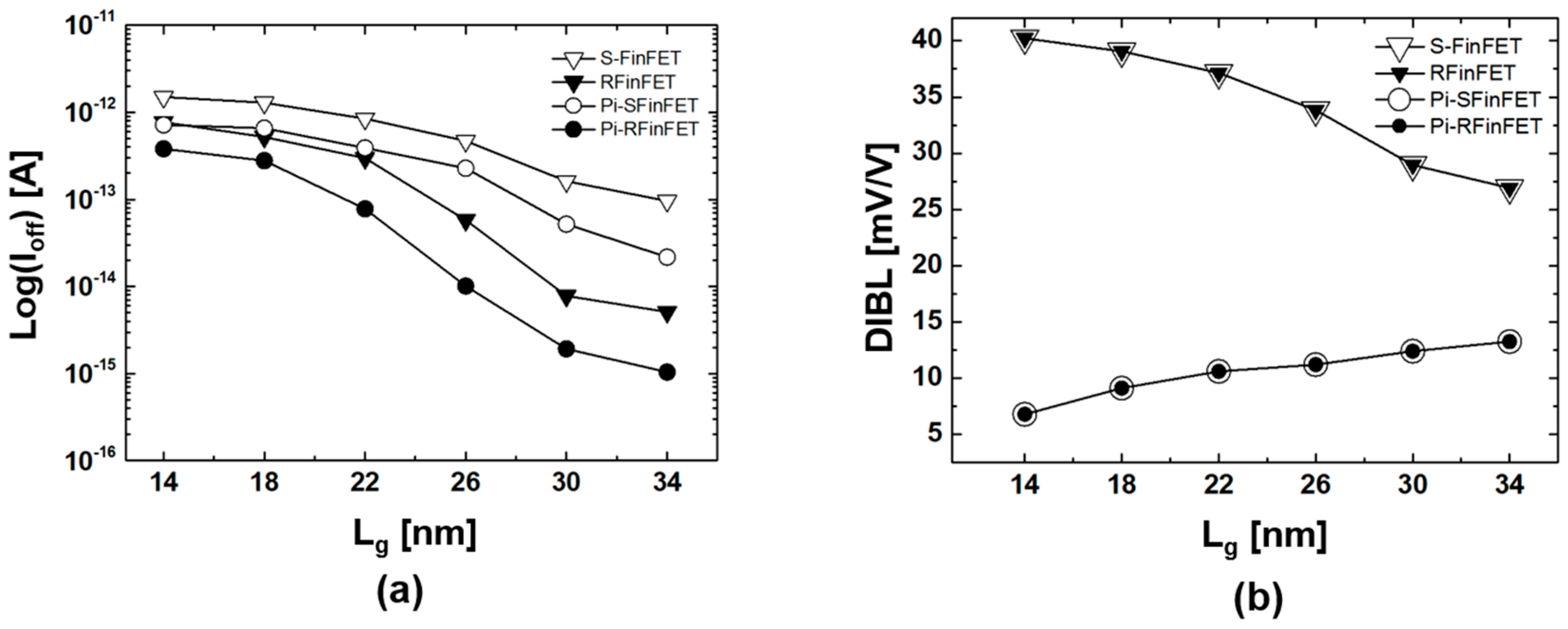

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Kim, L.J.Y.; Oh, H.J.; Lee, D.S.; Kim, D.H.; Kim, S.E.; Ha, G.W.; Kim, H.J.; Kang, N.J.; Park, J.M.; Hwang, Y.S.; et al. S-RCAT (sphere-shaped-recesschannel-array transistor) technology for 70 nm DRAM feature size and beyond. In Proceedings of the VLSI symposium, Kyoto, Japan, 14–16 June 2005; pp. 34–35. [Google Scholar]

- Chung, S.W.; Lee, S.D.; Jang, S.A.; Yoo, M.S.; Kim, K.O.; Chung, C.O.; Cho, S.Y.; Cho, H.J.; Lee, L.H.; Hwang, S.H.; et al. Highly scalable saddle-fin (S-Fin) transistor for sub 50 nm DRAM technology. In Proceedings of the VLSI symposium, Honololu, HI, USA, 13–15 June 2006; pp. 147–148. [Google Scholar]

- Crupi, G.; Schreurs, D.; Raskin, J.P.; Caddemi, A. A comprehensive review on microwave FinFET modeling for progressing beyond the state of art. Solid State Electron. 2013, 80, 81–95. [Google Scholar] [CrossRef]

- Poljak, M.; Jovanovic, V.; Suligoj, T. Improving bulk FinFET DC performance in comparison to SOI FinFET. Microelectron. Eng. 2009, 86, 2078–2085. [Google Scholar] [CrossRef]

- Lee, M.J.; Jin, S.H.; Baek, C.K.; Hong, S.M.; Park, S.Y.; Park, H.H.; Lee, S.D.; Chung, S.W.; Jeong, J.G.; Hong, S.G.; et al. A proposal on an optimized device structure with experimental studies on recent devices for the DRAM cell transistor. IEEE Trans. Electron Devices 2007, 54, 3325–3335. [Google Scholar] [CrossRef]

- Ryu, S.W.; Min, K.; Shin, J.; Kwon, H.; Nam, D.; Oh, T.; Jang, T.S.; Yoo, M.; Kim, Y.; Hong, S. Overcoming the reliability limitation in the ultimately scaled DRAM using silicon migration technique by hydrogen anneling. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 21.6.1–21.6.4. [Google Scholar]

- Lee, M.J.; Cho, J.H.; Lee, S.D.; Ahn, J.H.; Kim, J.W.; Park, S.W.; Park, Y.J.; Min, H.S. Partial SOI type isolation for improvement of DRAM cell transistor characteristics. IEEE Electron Device Lett. 2005, 26, 332–334. [Google Scholar]

- Kim, Y.K.; Lee, J.S.; Kim, G.; Park, T.; Kim, H.J.; Cho, Y.P.; Park, Y.J.; Lee, M.J. Simulation analysis in sub-0.1μm for partial isolation Field-Effect Transistors. Electronics 2018, 7, 227. [Google Scholar] [CrossRef]

- Sysnopsis Inc. TCAD Sentaurus Manual, Sysnopsis®, version D-2013.03; Sysnopsis Inc.: Mountain View, CA, USA, 2013.

- Hurkx, G.A.M.; Klaassen, D.B.M.; Knuvers, M.P.G. A new recombination model for device simulation including tunneling. IEEE Trans. Electron Devices 1992, 39, 331–338. [Google Scholar] [CrossRef]

- Jin, S.; Lee, M.J.; Yi, J.H.; Choi, J.H.; Kang, D.G.; Chung, I.Y.; Park, Y.J.; Min, H.S. A new direct evaluation method to obtain the data retention time distribution of DRAM. IEEE Trans. Electron Devices 2006, 53, 2344–2350. [Google Scholar] [CrossRef]

- Jang, E.; Shin, S.; Jung, J.W.; Kim, K.R. Gate induced drain leakage reduction with analysis of gate fringing field effect on high-κ/metal gate CMOS technology. Jpn. J. Appl. Phys. 2015, 54, 06FG10-1-4. [Google Scholar] [CrossRef]

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, Y.K.; Lee, J.S.; Kim, G.; Park, T.; Kim, H.J.; Cho, Y.P.; Park, Y.J.; Lee, M.J. Partial Isolation Type Saddle-FinFET(Pi-FinFET) for Sub-30 nm DRAM Cell Transistors. Electronics 2019, 8, 8. https://doi.org/10.3390/electronics8010008

Kim YK, Lee JS, Kim G, Park T, Kim HJ, Cho YP, Park YJ, Lee MJ. Partial Isolation Type Saddle-FinFET(Pi-FinFET) for Sub-30 nm DRAM Cell Transistors. Electronics. 2019; 8(1):8. https://doi.org/10.3390/electronics8010008

Chicago/Turabian StyleKim, Young Kwon, Jin Sung Lee, Geon Kim, Taesik Park, Hui Jung Kim, Young Pyo Cho, Young June Park, and Myoung Jin Lee. 2019. "Partial Isolation Type Saddle-FinFET(Pi-FinFET) for Sub-30 nm DRAM Cell Transistors" Electronics 8, no. 1: 8. https://doi.org/10.3390/electronics8010008

APA StyleKim, Y. K., Lee, J. S., Kim, G., Park, T., Kim, H. J., Cho, Y. P., Park, Y. J., & Lee, M. J. (2019). Partial Isolation Type Saddle-FinFET(Pi-FinFET) for Sub-30 nm DRAM Cell Transistors. Electronics, 8(1), 8. https://doi.org/10.3390/electronics8010008