1. Introduction

The automotive industry is evolving through interconnected and autonomous vehicles that bring reduced traffic congestion, reduced environmental impact, and reduced capital costs. Vehicle to everything (V2X) technology is the key to intelligent transportation systems (ITS) based on 5G wireless network evolution. The ITS combines many different types of information and communication technologies to create intelligent wireless networks. Such a smart ITS network is needed for reasons such as improving traffic safety (real-time weather monitoring, warning sign notifications, speed limitation, emergency alerts), reducing infrastructure damage (overloaded machines can be identified and eliminated from traffic participation, thus avoiding damage to the road), and traffic control (traffic management can be adaptive depending on traffic flow). These benefits of an ITS can make traffic safer, faster, and more convenient. To create an ITS network, transmitters are required that generate signals of a certain frequency using a frequency synthesizer based on the LC digitally controlled oscillator (LC DCO).

Most LC DCOs around 10 GHz are designed using 65 nm and newer technology, resulting in a significant increase in the cost of the final product. The used area of silicon is not reduced by much since most of the design is occupied by an inductor. The basic idea behind this article was to design a standard N-channel metal oxide semiconductor (NMOS) architecture, low power, low occupancy, low phase noise, wide tuning range—and most importantly—cheap DCO using low-cost 130 nm technology. The application of this low-cost DCO in the constantly evolving intelligent transport systems was the main goal. The main difficulty was getting the required parameters and performance using a mature low-cost 130 nm IBM radio frequency (RF) integrated circuit (IC) technology. High-quality RF transistors and high-quality factor Q copper inductors were used in this technology with correlating results of the simulations and measurements. In this technology, copper and aluminum wiring with a thick top metal was used. The 130 nm technology is a semiconductor technology for low-cost and high-performance wireless applications. Unfortunately, specific and more detailed information about this technology is under a non-disclosure agreement.

The aim of this work was to create an LC DCO whose output signal’s frequency range is suitable for USA and Japan 5G ITS bands. The LC DCO output signal frequency should correspond to the 2.5 LTE B24 and 600 MHz USA 5G band, as well as the —4.4–4.9 GHz Japan 5G band [

1]. DCO may be used in other communication systems.

The LC DCO alone could not generate a stable frequency, thus additional blocks were used that collectively formed a digital or analog phase locked loop (PLL), which was applied in multiband multistandard radio frequency (RF) transceivers.

As one of the most important blocks of any wireless multiband, the multistandard transceiver is the PLL. The main PLL applications are signal synthesis, synchronization, modulation, demodulation, as well as signal tracking. There are two main types of PLLs: conventional PLL (CPLL) and all digital PLLs (ADPLL). The CPLLs main advantages are frequency synthesis with good performance and a high frequency range, but the disadvantages are the high power consumption and large chip area. ADPLLs are characterized by low power consumption, small area, and scalability across different technology nodes. The blocks of these PLLs are presented in the following paragraphs.

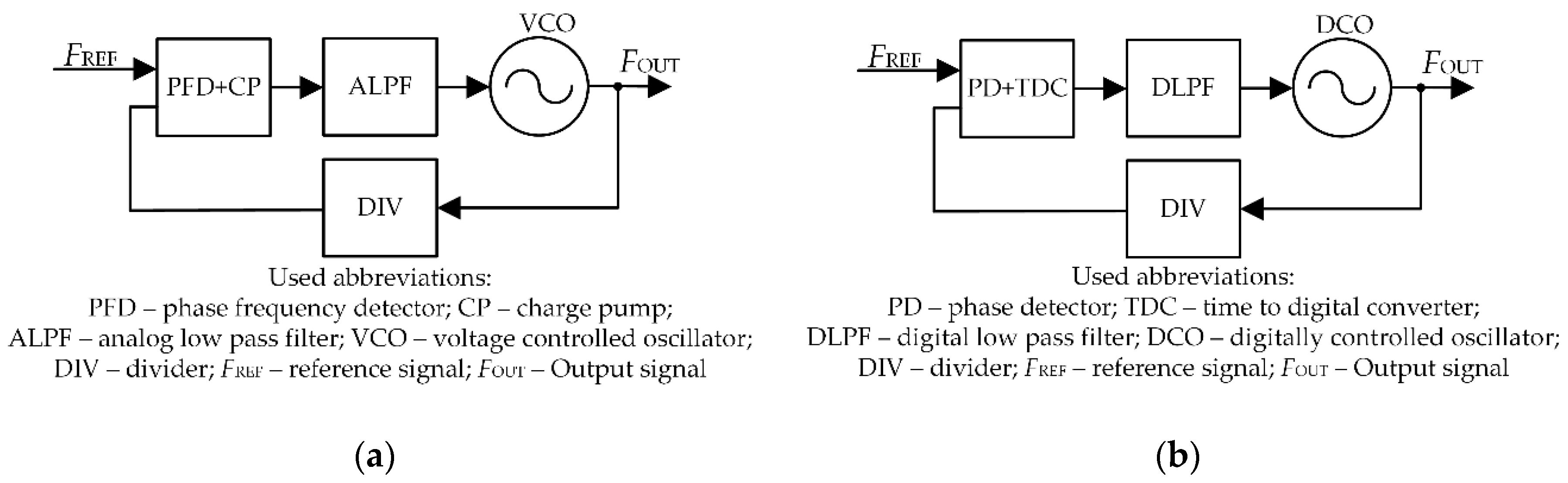

The basic PLL block diagram is shown in

Figure 1a. In a typical PLL, a voltage controlled oscillator (VCO) generates unstable output signal frequency

FOUT. The transceiver cannot function properly when the frequency of the generated signal is unstable, thus an additional reference signal (

FREF) is used to stabilize the frequency. The

FOUT adjustment is as follows: the feedback divider (DIV) generates a comparison frequency using the VCO output signal

FOUT divided by coefficient

N; phase frequency detector (PFD) compares the phase/frequency of two signals with frequencies

FREF and

FOUT/

N at its input. The purpose of the PFD is to detect the phase difference between

FREF and

FOUT/N. It is considered that the PLL is locked when the

FREF signal is equal to the signal

FOUT/

N. The main purpose of a charge pump (CP) is to convert the logic states of the phase frequency detector into analog signals suitable to control the VCO. The output of the charge pump is connected to an analog low pass filter (ALPF) that integrates the charge pump output current to an equivalent VCO control voltage [

2].

The basic ADPLL synthesizer block diagram is shown in

Figure 1b. In the digital controlled oscillator, DCO replaces the VCO. The time-to-digital converter (TDC) with the phase detector (PD) replaces the phase frequency detector and the charge-pump of the ADPLL. The digital low pass filter (DLPF) replaces the analog low pass filter of the PLL. The main advantages of the ADPLL are less chip area, elimination of additional external control voltage (mostly, the ALPF is realized on the printed circuit board (PCB) side, the DLPF is integrated inside the chip), the chip cost is lower, and, with digitalized block controls, all system programming is simplified [

3]. The main advantages of LC DCO versus LC VCO are the lower occupied area, lower phase noise, lower power consumption, and the ability to digitize further deployable systems. The following paragraphs outline the main architectures of LC DCO.

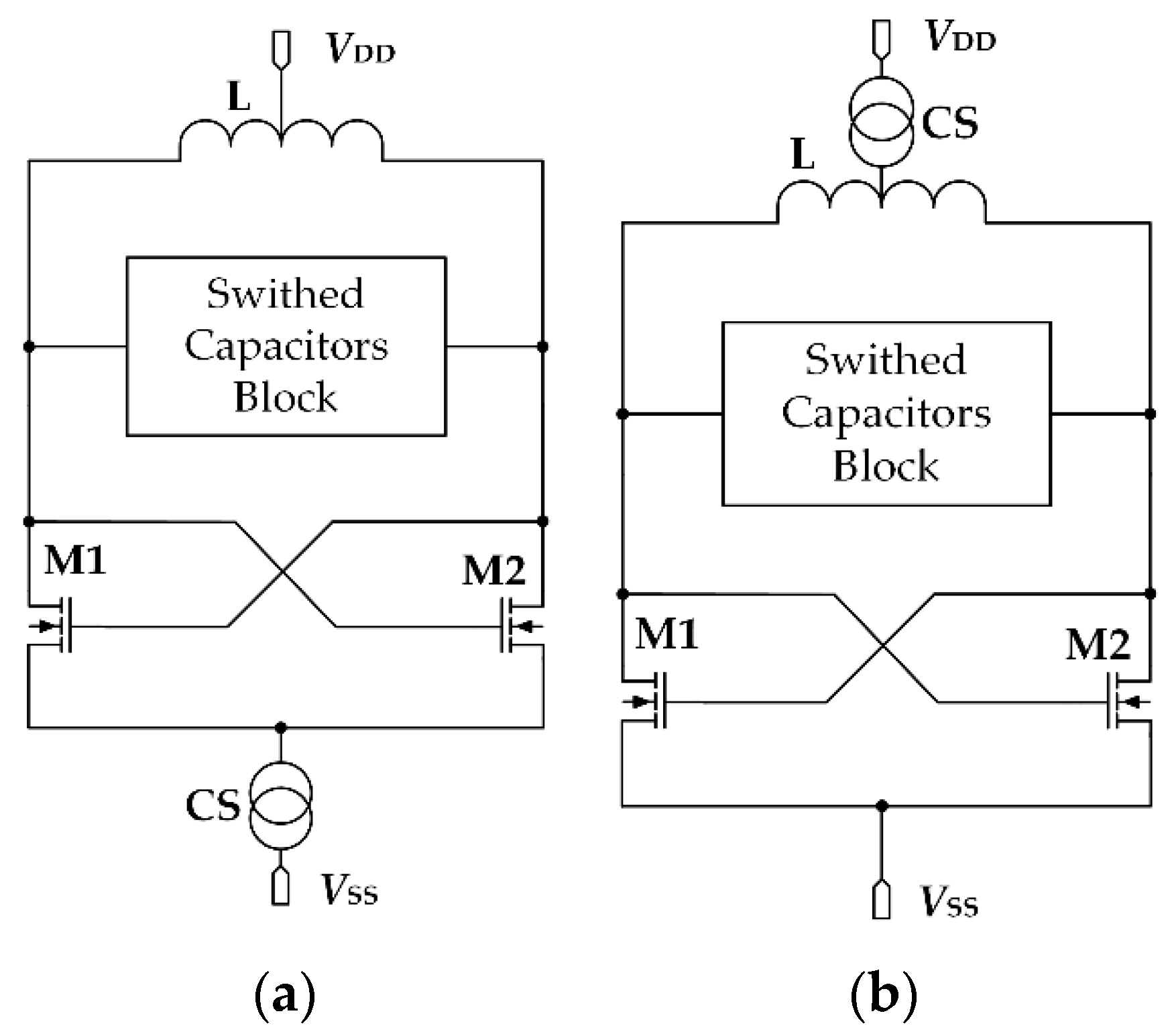

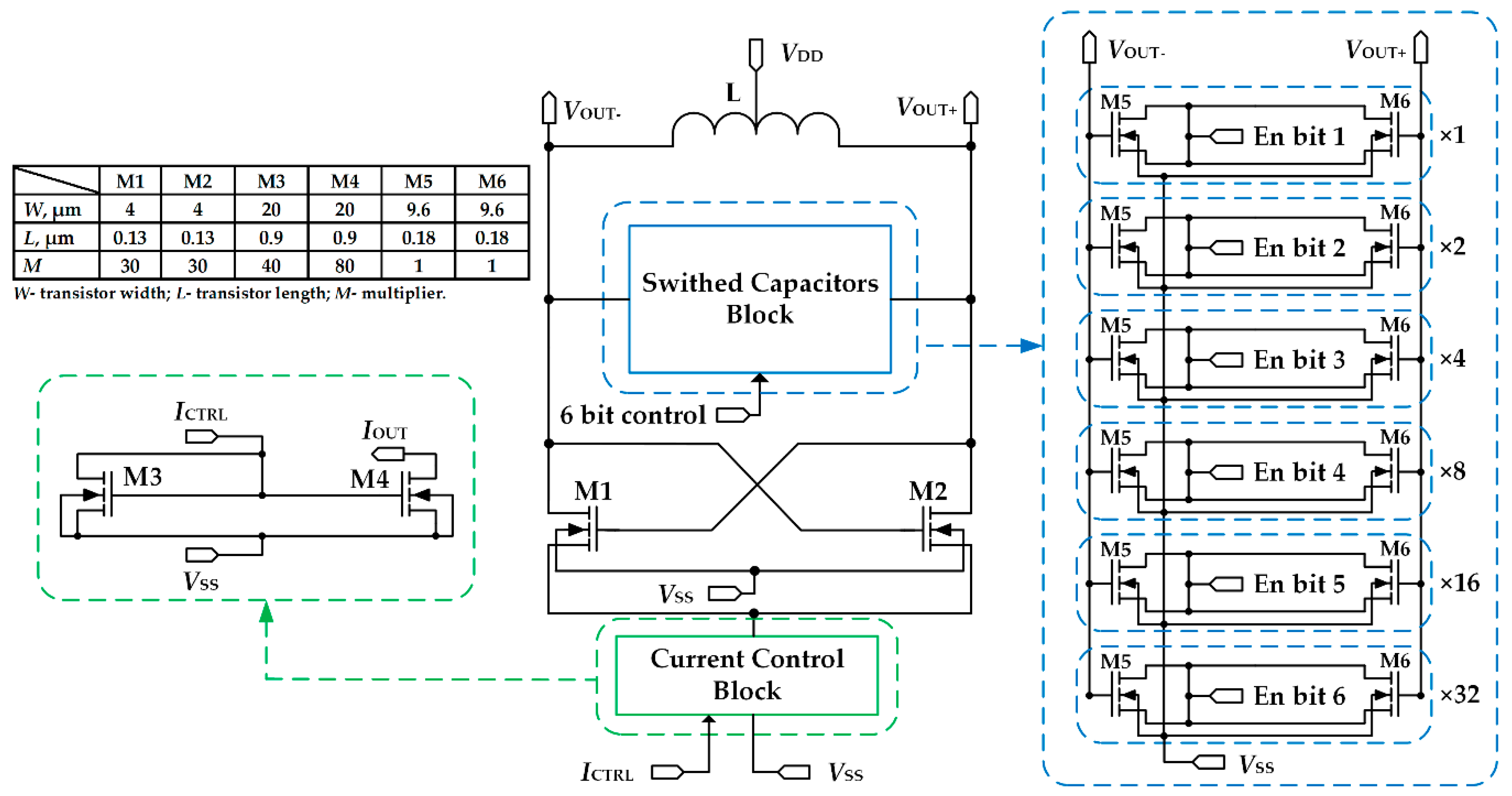

The basic architectures of N-channel metal oxide semiconductor (NMOS) LC DCO cores are presented in

Figure 2a,b. The current source connected to the ground architecture (

Figure 2a) has the lowest sensitivity to noise on the ground line but the highest sensitivity to power supply source noise. This architecture is characterized by lower flicker noise in the output compared to architecture, as shown in

Figure 2b. This is achieved due to a more correct output signal waveform. Reduced flicker noise causes lower distortion of the output signal. Using this architecture’s output signal swing can be doubled compared to the used supply voltage and can be used for phase noise reduction [

4].

The basic architectures of P-channel metal oxide semiconductor (PMOS) LC DCO cores are presented in

Figure 2b,c. In order to obtain the same operating frequency, a PMOS-based LC DCO core would require a transistor that is twice as large as the one in an NMOS-based LC DCO core. This increases both the occupied chip area and the power consumption but improves phase noise due to the lower PMOS transistor flicker noise in comparison to that of NMOS devices.

Hybrid NMOS and PMOS transistor architectures are also possible. Such architecture consists of a PMOS transistor pair connected to the power supply while an NMOS transistors pair is connected to the ground. This results in two pairs of transistors, allowing half of the energy to be consumed by the same negative resistance. This architecture receives output swing close to the supply voltage, thus the generated signal is limited by the voltage supply, which depends on the technology of the integrated circuits. With a low output signal swing, the phase noise gets worse and further signal processing becomes more complex.

We decided to use the

Figure 2a LC DCO design architecture with an NMOS LC DCO core when the current source (CS) connected to the ground in order to fulfill the requirements of reducing the occupied space but maintaining a double output signal voltage swing when compared to the supply voltage (the signal generated by the LC DCO is processed by other blocks). The LC DCO’s operating frequency is high, around 10 GHz, as NMOS transistors are faster than the PMOS, thus a higher frequency can be achieved when using NMOS architecture.

A previous work titled “CMOS Technology based LC VCO Review” contains a review and a comparison of 44 different LC oscillators published in papers [

5]. In order to quantify the comparison of the latter LC oscillators, an FOM

T was used. According to the acquired LC oscillators FOM

T results, the best overall performance was achieved when the circuit was implemented in the 130 nm CMOS process, and the second best was achieved when using the 65 nm CMOS process. Therefore, in order to design an LC DCO with low phase noise, low power consumption, and wide tuning range while also reducing the overall price, the 130 nm CMOS process was chosen.

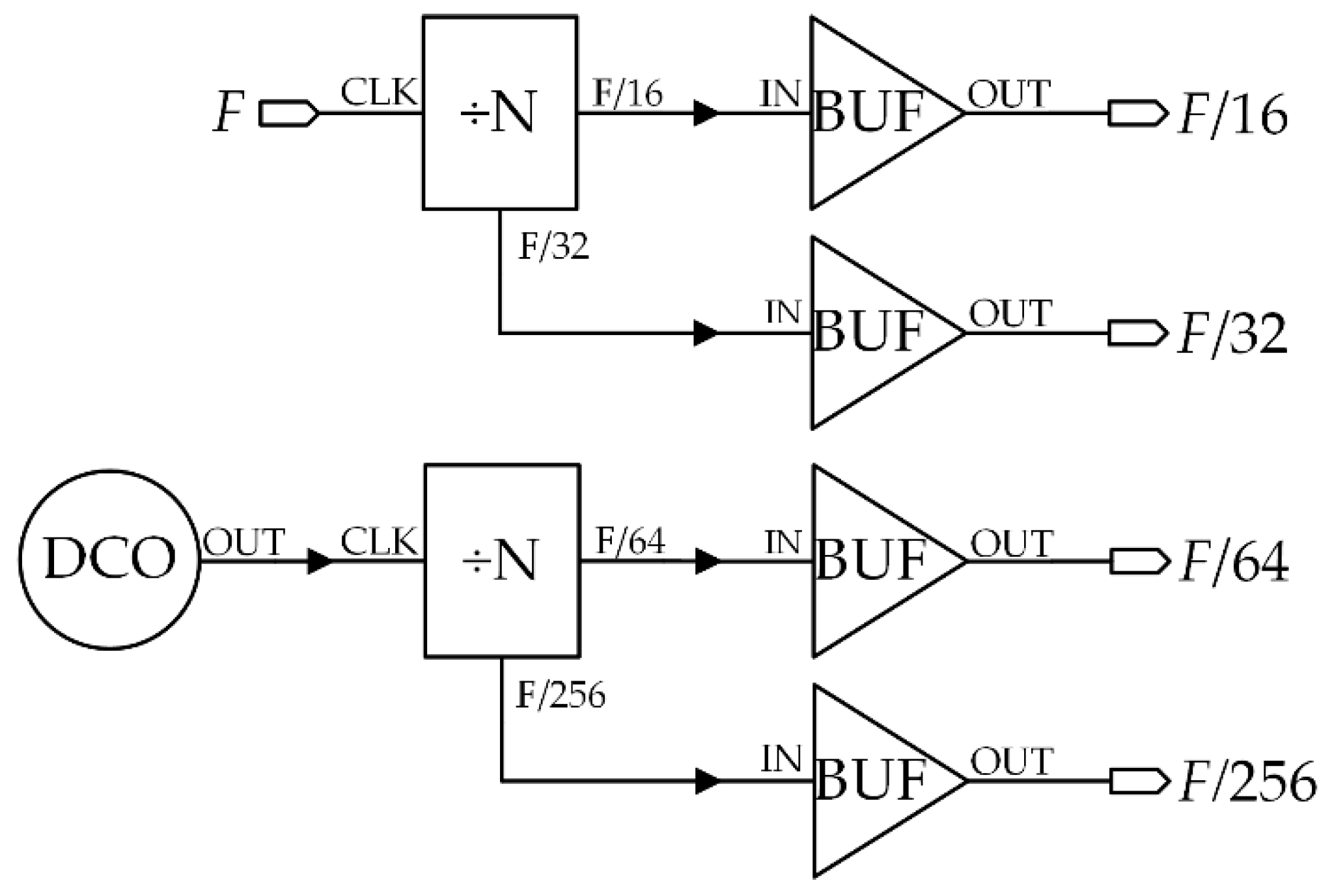

3. Simulation and Measurements

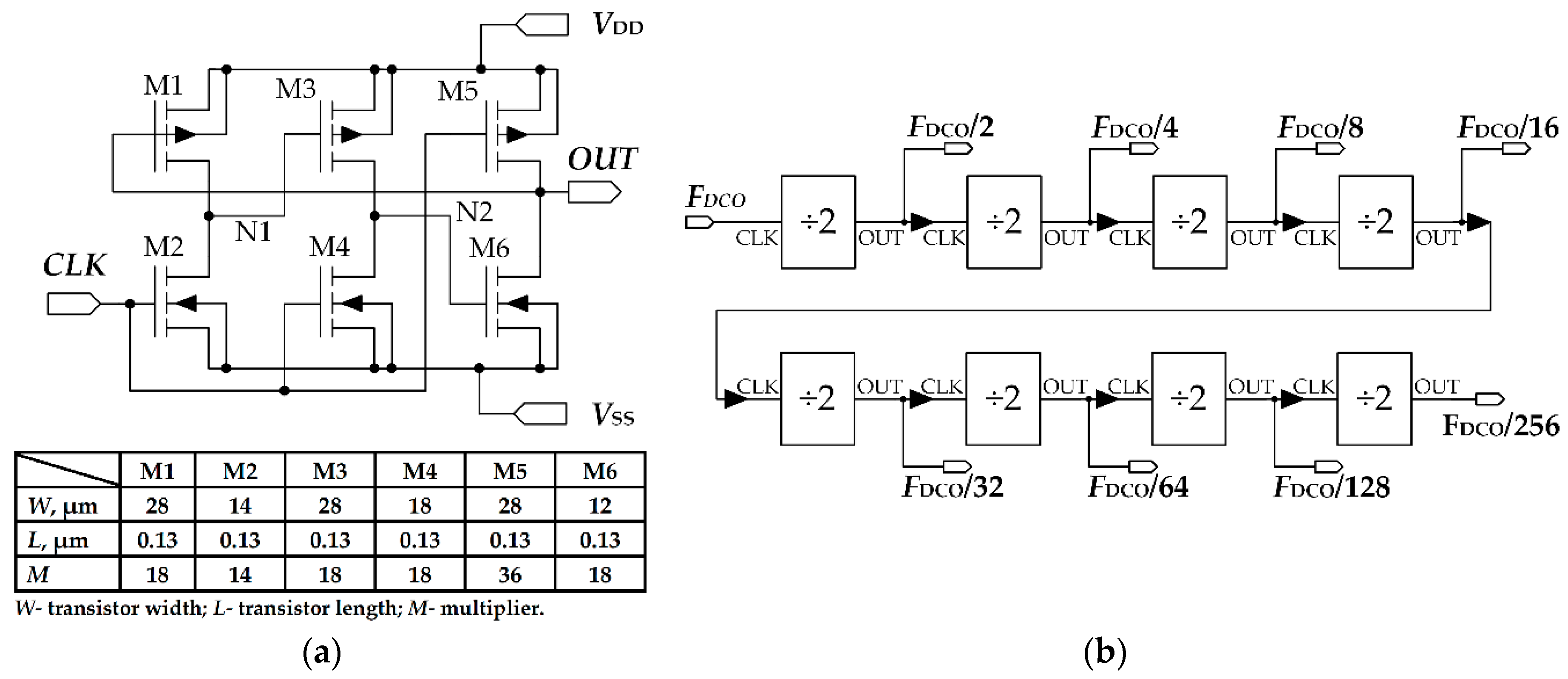

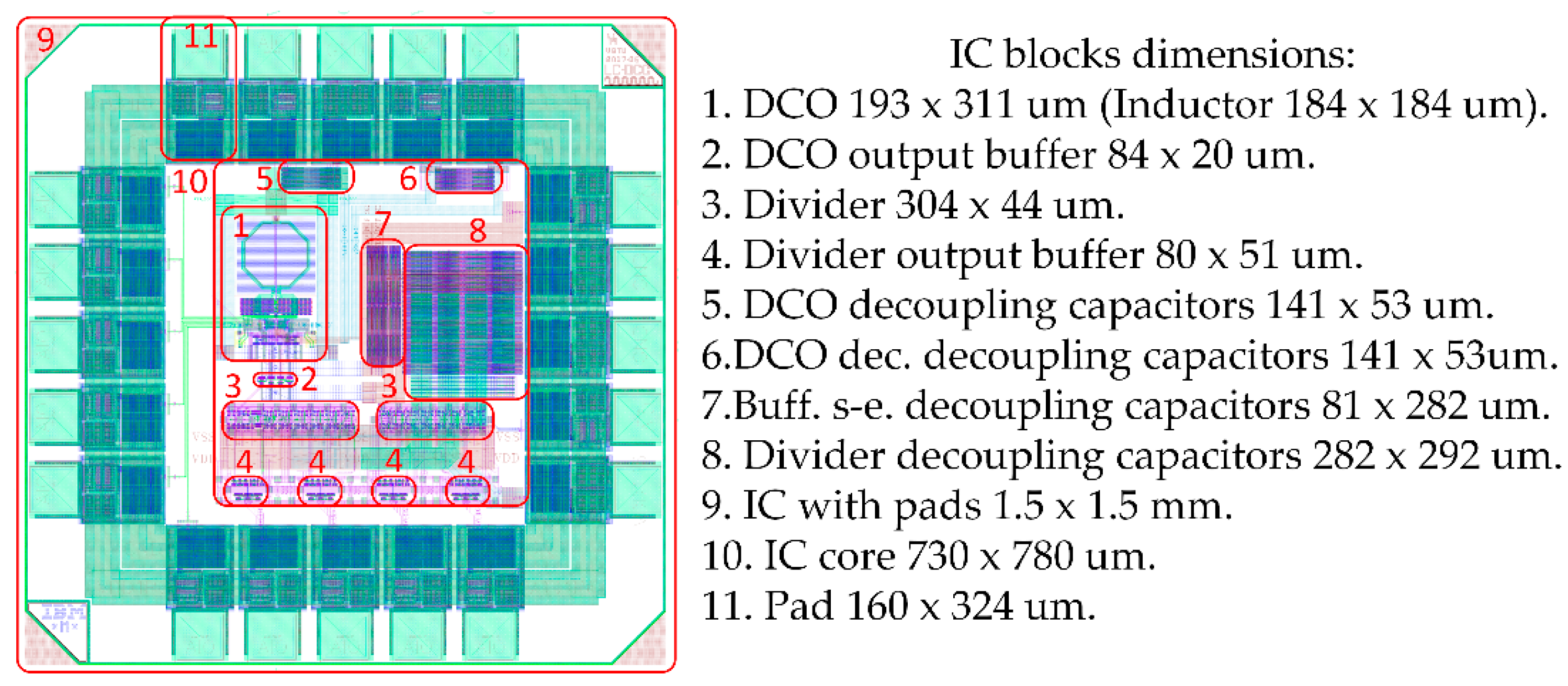

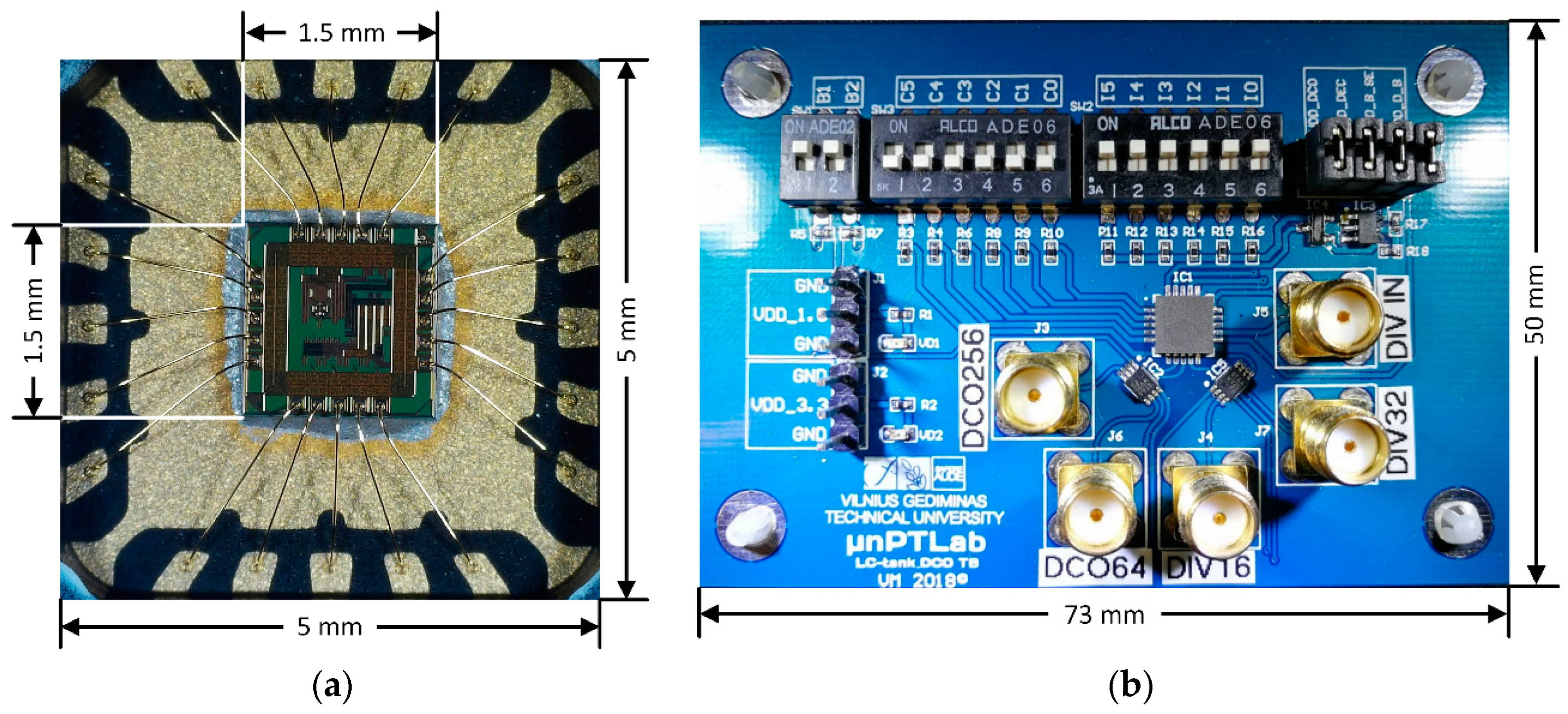

The proposed LC-DCO and frequency divider were designed in 130 nm RF CMOS technology in the Cadence IC software package. The design and simulation process was as follows. Firstly, a basic electrical schematic was designed and its simulations were carried out. The schematic was adjusted if the results obtained after the simulations did not meet the required conditions. Upon obtaining the required results, layout design was performed. Parasitics were extracted from the designed layout, then simulation of the layout was performed. In the absence of the required results, the electric schematic and layout were once again corrected, the layout was extracted, and simulations were performed. After obtaining the required simulation results, the main blocks were connected, which were also connected to the pads. After these steps, the whole system was verified. After making the chip, the basic parameters were measured and compared with the parameters obtained during the simulation. Simulations were performed in nominal conditions using 1.8 V supply voltage and 40 °C temperature. The main parameters of the simulations and measurements are presented in

Table 1.

To evaluate the overall performance of the frequency oscillators, an FOM (1) and FOM

T (2), including the tuning range, was used:

where

PN(Δ

f) is the phase noise at an offset frequency Δ

f,

F0 is the carrier frequency,

P is the power consumption in mW, and Δ

F is a percentage of the frequency tuning range [

5]. The proposed LC DCO and E-TSPC divider schematics, post-layout, and chip main parameters are presented in

Table 1.

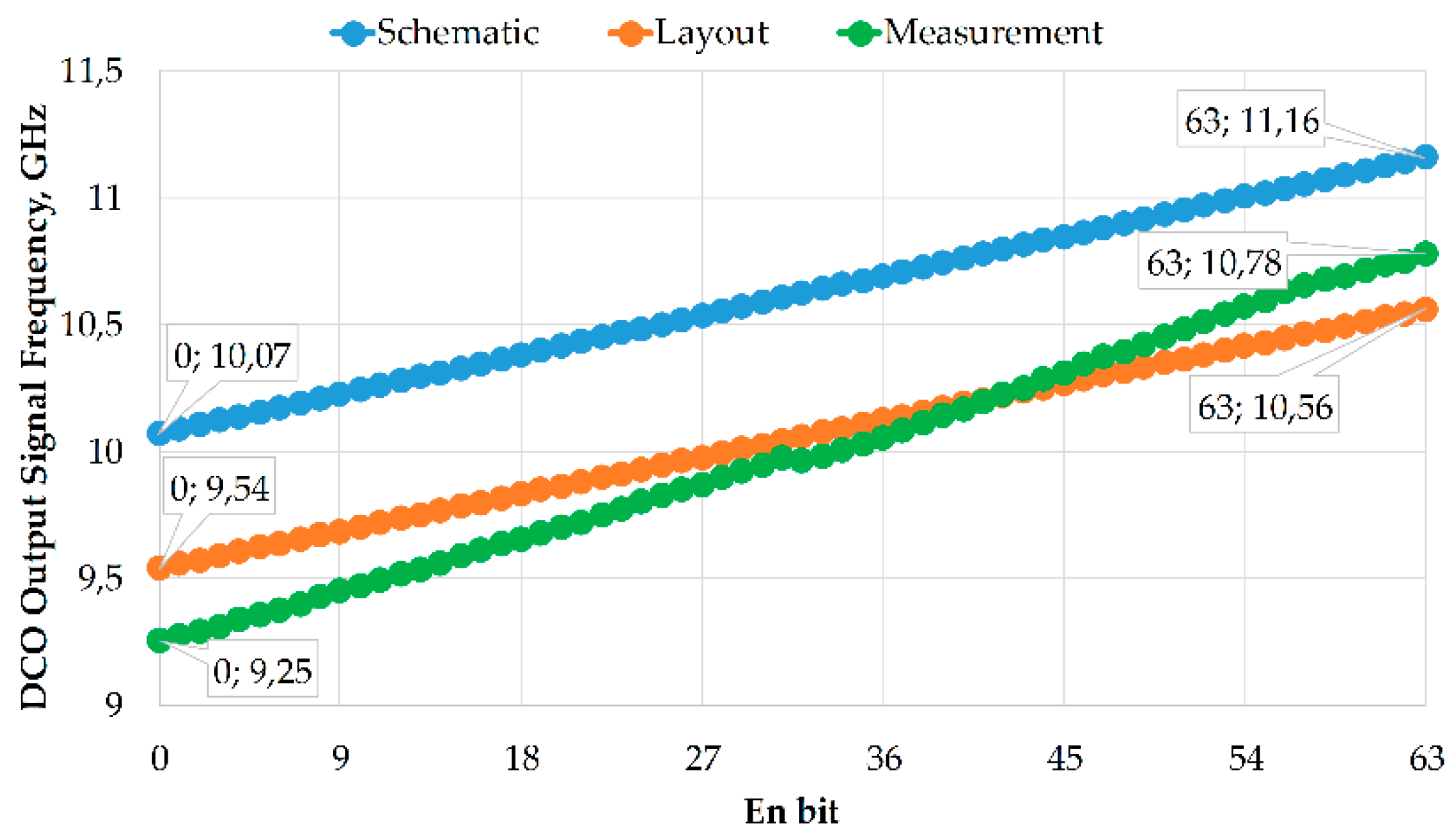

Figure 6 describes the tuning range of the proposed LC DCO. The LC DCO achieved a wide tuning range from 10.07 GHz to 11.16 GHz during schematic simulations. The tuning range reduced to 9.54–10.56 GHz during the post-layout simulation. The measured tuning range was 9.25–10.78 GHz, which was better than both the schematic and the post-layout simulation, and reached a 1.53 GHz bandwidth, which was 0.51 GHz wider than the results obtained in the post-layout simulation.

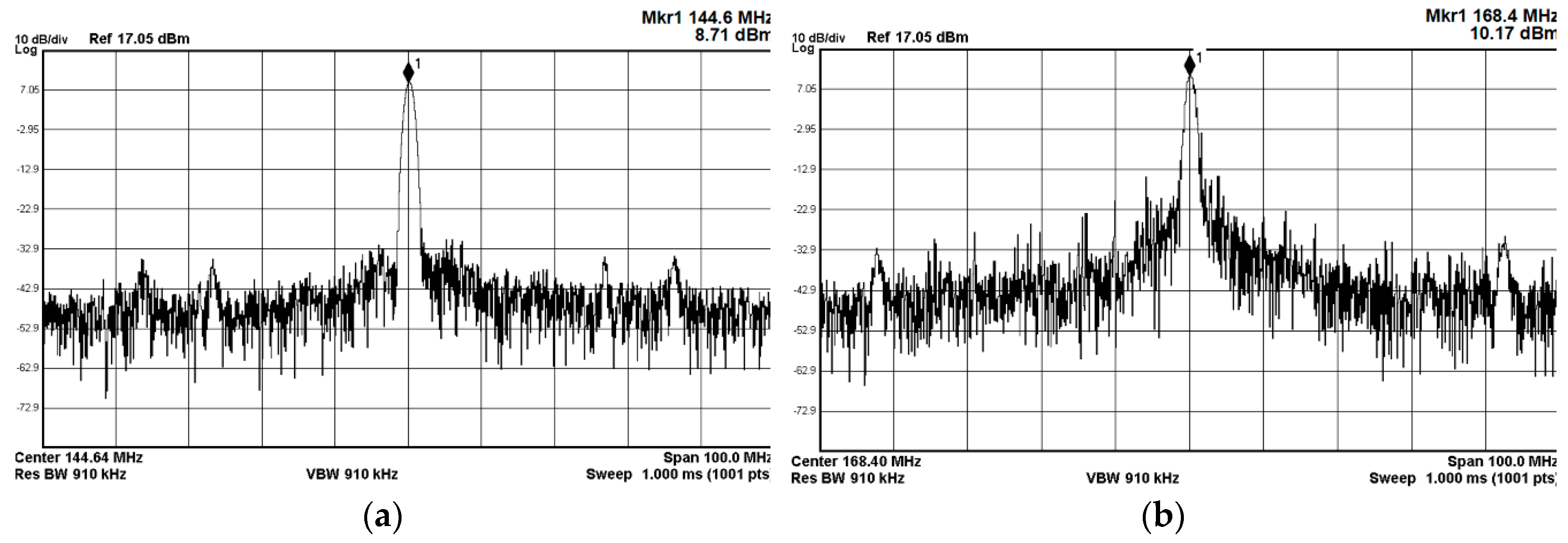

The frequency spectrum measurement results of the proposed LC DCO divided by a 64 output when operating at the lowest and highest operating frequencies are shown in

Figure 7. From the latter picture (a), it is seen that the lowest output signal frequency (when dividing by 64) was 144.6 MHz. This resulted in the proposed LC DCO generating a 144.6 MHz × 64 = 9.25 GHz frequency signal. The highest output signal frequency (when dividing from 64) was 168.4 MHz, which is shown in

Figure 7b. The LC DCO generated a 168.4 MHz × 64 = 10.78 GHz frequency signal.

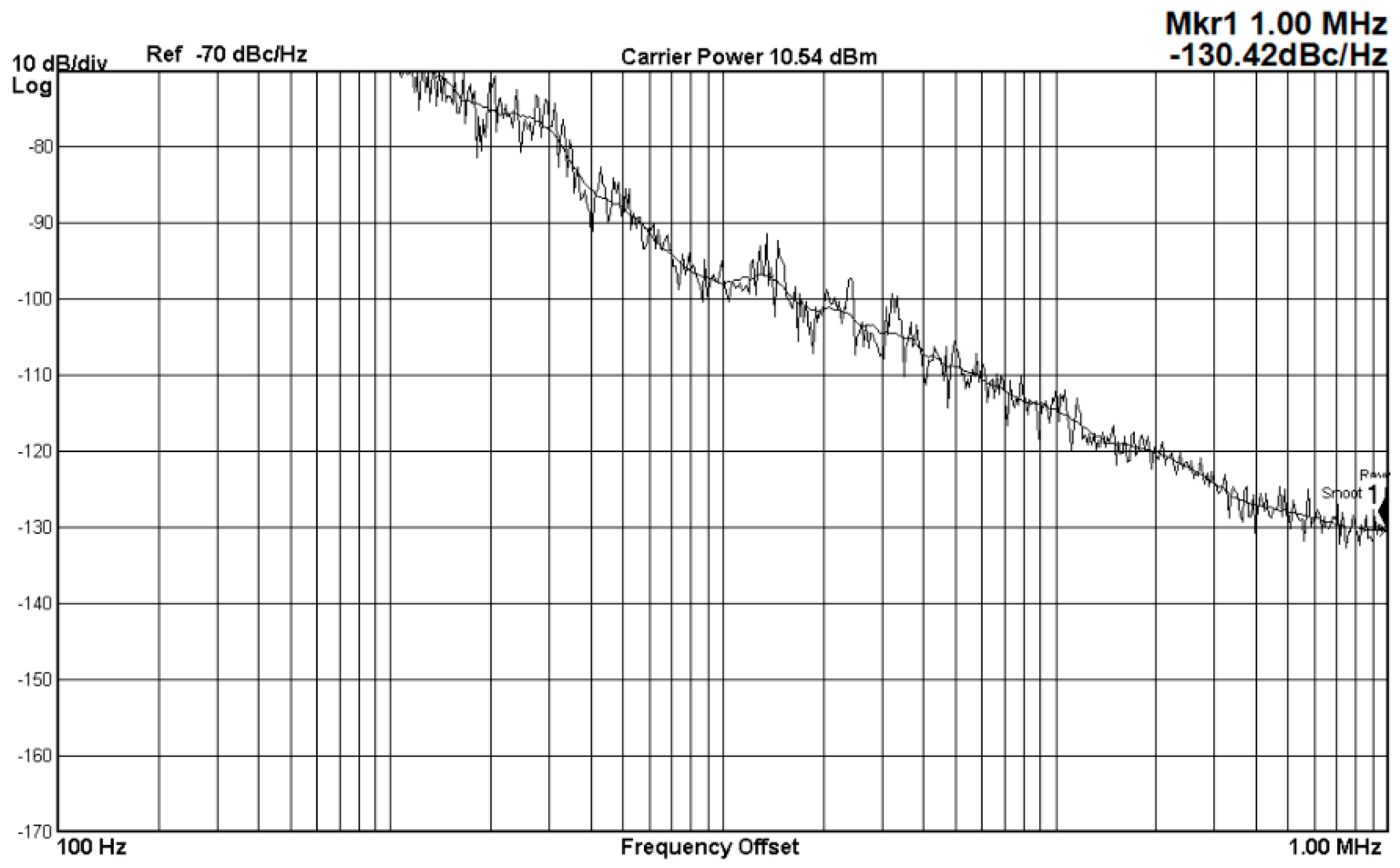

The phase noise at the designed LC DCO output (divided by 64 when operating at the lowest frequency) is shown in

Figure 8. From this, it is visible that the phase noise at 1 MHz offset frequency from the DCO lowest (En bit = 0) carrier frequency was −130.42 dBc/Hz output of the frequency divider when operating at the lowest frequencies.

It was noted that the phase noise at 1 Mhz offset from frequency divider’s output frequency when the DCO was operating at the lowest frequency (En bit = 0,

FMIN = 144.6 MHz) was −130.42 dBc/Hz at the divider output. The phase noise at 1 MHz offset frequency from the DCO highest carrier frequency (En bit = 63,

FMAX = 168.4 GHz) was −128.13 dBc/Hz at the divider output. These parameters were obtained by measuring the phase noise at the divide-by-64 output. This theory revealed that at each divider cascade, phase noise improved by 3 dBc/Hz [

11]. Therefore, it was possible to estimate the real LC DCO phase noise at the input of the first of the six divider cascades (F/64): −130.42 + (3 × 6) = −113.42 dBc/Hz at 1 MHz offset from the lowest LC DCO carrier frequency (

FMIN = 9.25 GHz) and −128.51 + (3 × 6) = −110.51 dBc/Hz at 1 MHz offset from the highest LC DCO carrier frequency (

FMAX = 10.78 GHz). During the post-layout simulations, the following phase noise values were obtained: −114.79 dBc/Hz at 1 MHz offset from the lowest LC DCO carrier frequency and −113.62 dBc/Hz at 1 MHz offset from the highest LC DCO carrier frequency.

Table 2 shows the proposed LC DCO performance compared with other reported LC DCOs. The table shows that all compared DCOs were designed using 65 nm technology, while this paper’s proposed LC DCO, which was designed using 130 nm technology, lead to reduced production cost of the chip. The lowest supply voltage was used in [

12] and was equal to 1.1 V, which affected the lowest power consumption of the LC DCO core −3.3 mW. All of the reviewed and reported DCOs had a carrier frequency that varied around 10 GHz. The widest DCO tuning range was [

13] DCO (15.12%). The lowest phase noise result was in the proposed LC DCO and reached –113.42 dBc/Hz at 1 MHz offset frequency from the lowest carrier frequency. It was possible to achieve such low phase noise due to the high quality inductor. The

FOM and

FOMT values of the proposed LC DCO were –183.52 dBc/Hz and –187.20 dBc/Hz, respectively. These results were achieved due to very low phase noise (–113.52 dBc/Hz) and wide frequency tuning range (15.28%).

5. Conclusions

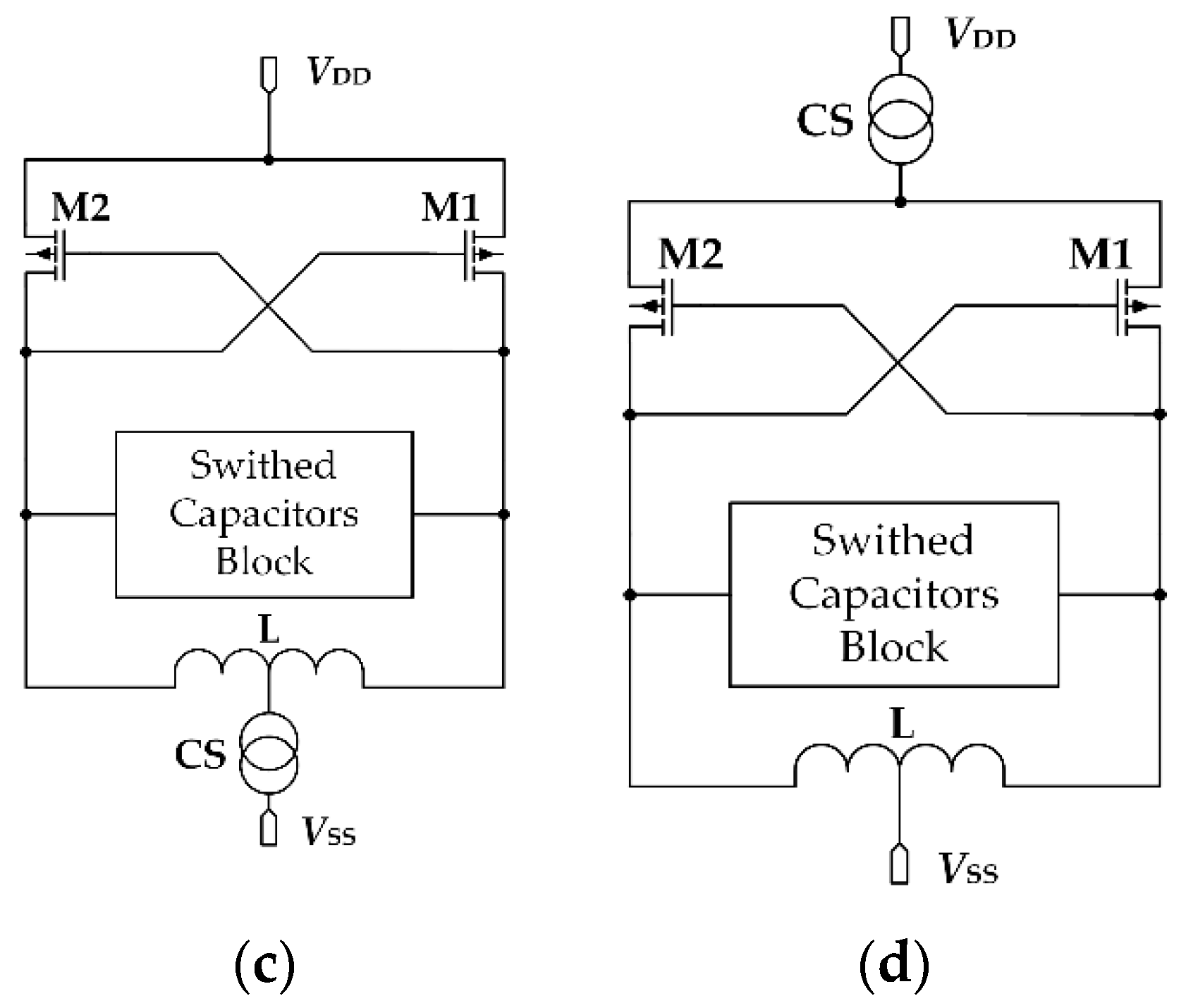

The main goal of this work was to design a low power, low phase noise, wide tuning range, low-area, and low-cost LC DCO and frequency divider IC for ITS systems working on a 5G network. The main difficulty was getting the required parameters and performance using the 130 nm IC technology, but the main advantage of the IC technology was the cheapness of the ICs produced. The proposed LC DCO was designed for USA and Japan 5G frequency bands. The proposed LC DCO output signal frequency divided by four and sixteen could be applied to the USA 5G network (2.5 LTE B24 and 600 MHz USA 5G bands), and the output signal frequency divided by two could be applied to the 4.4–4.9 GHz Japan 5G band.

The designed IC consisted of two parts: the LC DCO frequency generation and division circuit and the divider testing circuit. The LC DCO frequency generation and division circuit in two outputs generated a LC DCO signal frequency divided by 64 and 256 times. The divider testing circuit divided the frequency of the input signal by 16 and by 32. Using the proposed high frequency E-TSPC divider, the output frequency of the LC DCO could be divided from two to 256 times.

Simulations and measurements were performed in nominal conditions using 1.8 V supply voltage and 40 °C temperature. The LC DCO achieved a wide tuning range from 10.07 GHz to 11.16 GHz when schematics were simulated. Frequency varied from 9.54 GHz to 10.56 GHz when the post-layout was simulated, and frequency varied from 9.25 GHz to 10.78 GHz when the chip was measured.

Measured phase noise at 1 MHz offset frequency from the LC DCO lowest carrier frequency was −113.42 dBc/Hz, and phase noise at 1 MHz offset frequency from the LC DCO highest carrier frequency was −110.51 dBc/Hz. During the post-layout simulations, the following phase noises were obtained: −114.79 dBc/Hz at 1 MHz offset from the lowest LC DCO carrier frequency and −113.62 dBc/Hz at 1 MHz offset from the highest LC DCO carrier frequency.

The measured average power consumption of the proposed LC DCO IC core was 10.02 mW, which was higher than it was during both the schematic and the post-layout simulations, which were equal to 8.73 mW and 9.15 mW, respectively. The measured power consumption average of the proposed E-TSPC divider IC was 97.52 mW, which was also higher than it was during both the schematic and the post-layout simulations, which were 90.05 mW and 93.21 mW, respectively. To optimize power consumption, it is possible to limit the current to optimum using the “current control” block.

The FOM and FOMT values of the proposed LC DCO were −183.52 dBc/Hz and −187.20 dBc/Hz, respectively. These results were achieved due to very low phase noise (−113.52 dBc/Hz) and wide frequency tuning range (15.28%).

The total layout area with pads was 1.5 mm × 1.5 mm. The largest part of the layout was occupied by the proposed LC DCO, with an area of about 193 µm × 311 µm, while the largest part of the LC DCO was the inductor L—184 µm × 184 µm.