A Novel High-Performance Low-Cost Double-Upset Tolerant Latch Design

Abstract

:1. Introduction

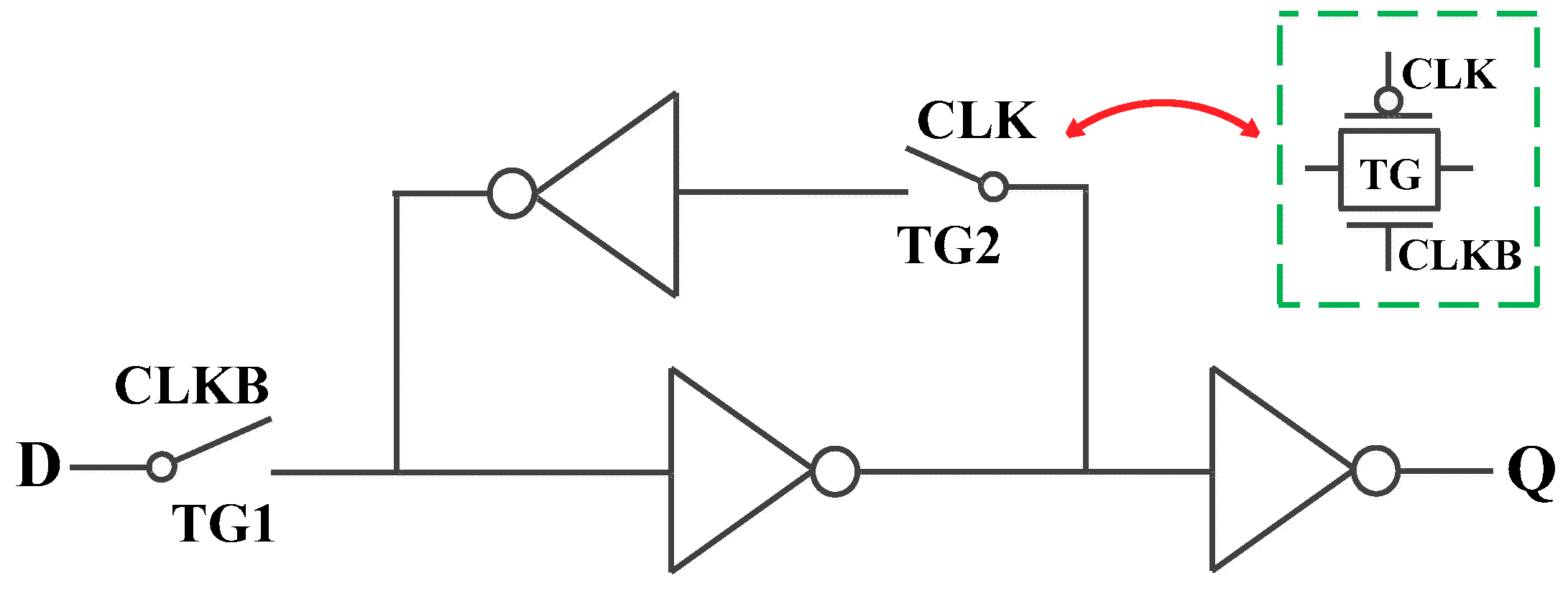

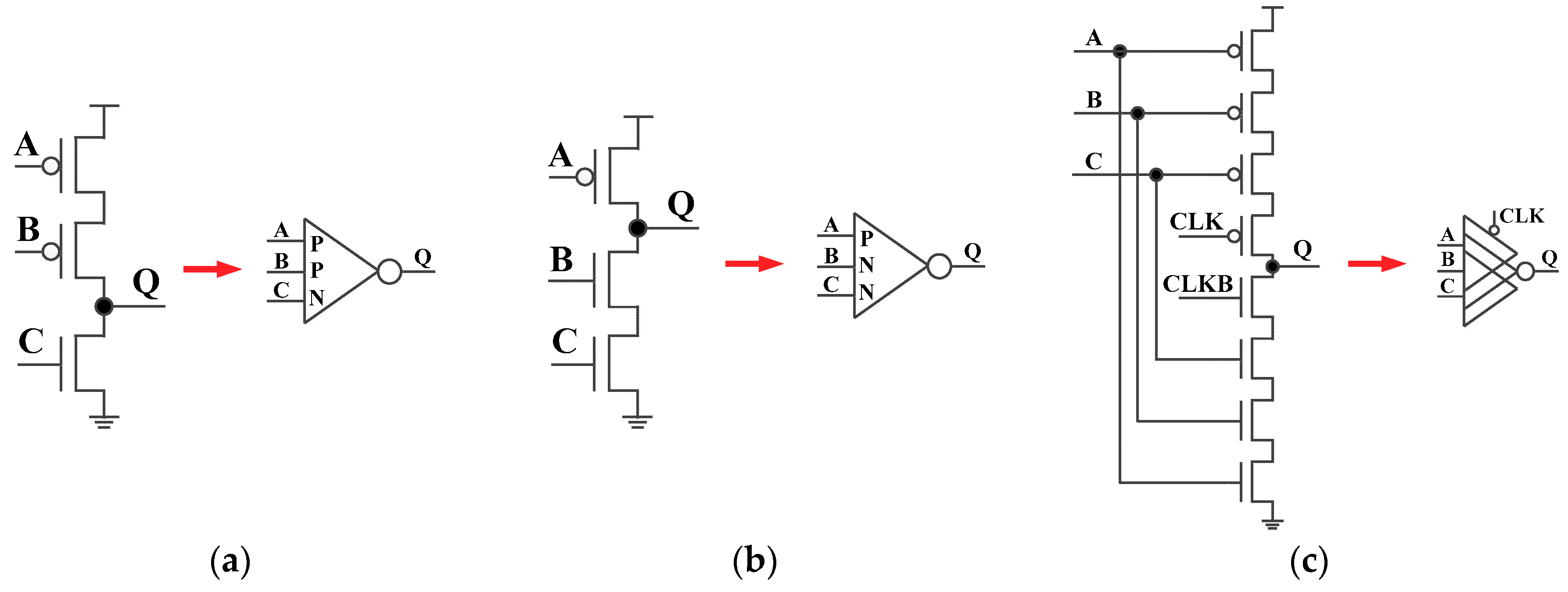

2. Proposed HLDUT Latch

2.1. Circuit Structure and Behavior

- (1)

- <SX, SX+1>: <S1, S2>, <S2, S3>, <S3, S4>, <S4, S5>, <S5, S6>, <S6, S1>;

- (2)

- <SX, SX+2>: <S1, S3>, <S2, S4>, <S3, S5>, <S4, S6>, <S5, S1>, <S6, S2>;

- (3)

- <SX, SX+3>: <S1, S4>, <S2, S5>, <S3, S6>.

- At first, we take the upset of node pair <S1, S2> in (1) into consideration. If nodes S1 and S2 are affected (i.e., S1 is discharged to 0 and S2 is charged to 1), the NMOS biased by S2 in I1 and the PMOS in I2 are turned on, while the PMOS transistors biased by S2 in I3 and I5, and the NMOS transistors biased by S1 in I4 and I6, are turned off. Since I3 and I5 are 2P1N inverters, and I4 and I6 are 1P2N inverters, S3, S4, S5 and S6 will be in high impedance state and their logic state will be kept temporarily. Thus, the PMOS and NMOS transistors in I1 and I2 are turned on, S1 and S2 will be unstable. The storage nodes except for S1 and S2 are not affected, thus S1 will be biased by S4 and S6 to its original logic 1 state, while S2 will be biased by S5 and S3 to its original logic 0 state. In this situation, node pair <S1, S2> belongs to type 1. Analyses are similar to that of node pairs <S3, S4> and <S5, S6> when they are affected by DUs, which means they belong to type 1.

- If node pair <S2, S3> is affected by DUs (i.e., S2 is charged to 1 and S3 is discharged to 0), the NMOS biased by S2 in I1 and the PMOS in I4 are turned on, while the PMOS transistors biased by S2 in I3 and I5, and the NMOS transistors biased by S3 in I2 and I6, are turned off. Due to the fact that the PMOS and NMOS transistors in I1 and I4 are turned on temporarily, S1 and S4 are unstable. If the DUs are strong to upset the S1 and S4, the nodes S1, S2, S3 and S4 are affected, and they cannot recover to their original logic states. The PMOS transistors biased by S4 and S2 in I5 and the NMOS transistors in I6 are turned off, making S5 and S6 get into high impedance state and their logic state will be kept. Since S2, S4 and S6 are not in the same logic state, the soft error will be blocked by the clocked three-input MCE. The output Q is not affected, and the right logic state is maintained. Hence, node pair <S2, S3> belongs to type 2. Analyses are similar to that of node pairs <S4, S5>, <S6, S1>, and all of the node pairs in (2) and (3) when they are affected by DUs, which means they all belong to type 2.

2.2. Implementation and Verification

3. Evaluation

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Narasimham, B.; Gupta, S.; Reed, D.; Wang, J.K.; Hendrickson, N.; Taufique, H. Scaling trends and bias dependence of the soft error rate of 16 nm and 7 nm FinFET SRAMs. In Proceedings of the IRPS, Burlingame, CA, USA, 11–15 March 2018. [Google Scholar]

- Bohr, M.T.; Yong, I.A. CMOS scaling trends and beyond. IEEE Micro 2017, 37, 20–29. [Google Scholar] [CrossRef]

- Ibe, E.; Taniguchi, H.; Yahagi, Y.; Shimbo, K.; Toba, T. Impact of scaling on neutron induced soft error in SRAMs from an 250 nm to a 22 nm design rule. IEEE Trans. Electron Devices 2010, 57, 1527–1538. [Google Scholar] [CrossRef]

- Ferlet-Cavrois, V.; Massengill, L.W.; Gouker, P. Single event transients in digital CMOS—A review. IEEE Trans. Nucl. Sci. 2013, 60, 1767–1790. [Google Scholar] [CrossRef]

- Baumann, R.C. Radiation-induced soft errors in advanced semiconductor technologies. IEEE Trans. Device Mater. Rel. 2005, 5, 305–316. [Google Scholar] [CrossRef]

- Calin, T.; Nicolaidis, M.; Velazco, R. Upset hardened memory design for submicron CMOS technology. IEEE Trans. Nucl. Sci. 1996, 43, 2874–2878. [Google Scholar] [CrossRef]

- Omana, M.; Rossi, D.; Metra, C. High-performance robust latches. IEEE Trans. Comput. 2010, 59, 1455–1465. [Google Scholar] [CrossRef]

- Nan, H.; Choi, K. High performance, low cost, and robust soft error tolerant latch designs for nanoscale CMOS technology. IEEE Trans. Circuits Syst. I Reg. Pap. 2012, 59, 1445–1457. [Google Scholar] [CrossRef]

- Balbekov, A.O.; Gorbunov, M.S.; Zebrev, G.I. Circuit-level layout-aware modeling of single-event effects in 65-nm CMOS ICs. IEEE Trans. Nucl. Sci. 2018, 65, 1914–1919. [Google Scholar] [CrossRef]

- Chen, R.; Zhang, F.; Chen, W.; Ding, L.; Guo, X.; Shen, C.; Luo, Y.; Zhao, W.; Zheng, L.; Guo, H.; et al. Single-event multiple transients in conventional and guard-ring hardened inverter chains under pulsed laser and heavy-ion irradiation. IEEE Trans. Nucl. Sci. 2017, 64, 2511–2518. [Google Scholar] [CrossRef]

- Blum, D.R.; Delgado-Frias, J.G. Schemes for eliminating transient width clock overhead from set-tolerant memory-based systems. IEEE Trans. Nucl. Sci. 2006, 53, 1564–1573. [Google Scholar] [CrossRef]

- Jiang, J.; Xu, Y.; Ren, J.; Zhu, W.; Lin, D.; Kong, W.; Zou, S. Low-cost single event double-upset tolerant latch design. Electron. Lett. 2018, 54, 554–556. [Google Scholar] [CrossRef]

- Katsarou, K.; Tsiatouhas, Y. Soft error interception latch: Double node charge sharing SEU tolerant design. Electron. Lett. 2015, 51, 330–332. [Google Scholar] [CrossRef]

- Hui, X.; Yun, Z. Circuit and layout combination technique to enhance multiple nodes upset tolerance in latches. IEICE Electron. Exp. 2015, 12, 1–7. [Google Scholar] [CrossRef]

- Eftaxiopoulos, N.; Axelos, N.; Zervakis, G.; Tsoumanis, K.; Pekmestzi, K. Delta DICE: A double node upset resilient latch. In Proceedings of the IEEE International Midwest Symposium on Circuits Systems, Fort Collins, CO, USA, 2–5 August 2015; pp. 1–4. [Google Scholar]

- Eftaxiopoulos, N.; Axelos, N.; Pekmestzi, K. DONUT: A double node upset tolerant latch. In Proceedings of the IEEE Computer Society Annual Symposium on VLSI, Montpellier, France, 10–15 July 2015; pp. 509–514. [Google Scholar]

- Yan, A.B.; Huang, Z.; Yi, M.; Xu, X.; Ouyang, Y.; Liang, H. Double-node-upset-resilient latch design for nanoscale CMOS technology. IEEE Trans. VLSI Syst. 2017, 25, 1978–1982. [Google Scholar] [CrossRef]

- Dharchoudhury, A.; Kang, S.M.; Cha, H.; Patel, J.H. Fast timing simulation of transient faults in digital circuits. In Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, San Jose, CA, USA, 6–10 November 1994; pp. 719–722. [Google Scholar]

- Lu, Y.; Lombardi, F.; Pontarelli, S.; Ottavi, M. Design and analysis of single-event tolerant slave latches for enhanced scan delay testing. IEEE Trans. Device Mater. Reliab. 2014, 14, 333–343. [Google Scholar]

| Latch | SU Tolerant? | DU Tolerant? | Delay (ps) | Power (μW) | Area (UST) | DPAP (×104) |

|---|---|---|---|---|---|---|

| The traditional | × | × | 84.99 | 2.91 | 49.6 | 1.23 |

| HiPeR [7] | √ | × | 44.83 | 2.83 | 91.9 | 1.17 |

| HLR-CG1 [8] | √ | × | 52.61 | 5.48 | 85.5 | 2.46 |

| DNCS [13] | √ | √ | 251.24 | 6.91 | 171.1 | 29.70 |

| CLCT [14] | √ | √ | 166.39 | 5.05 | 148.9 | 12.51 |

| Delta DICE [15] | √ | √ | 108.23 | 10.59 | 198.6 | 22.76 |

| DONUT [16] | √ | √ | 129.28 | 10.31 | 164.6 | 21.94 |

| DNURL [17] | √ | √ | 31.76 | 6.89 | 268.5 | 5.88 |

| HLDUT | √ | √ | 29.19 | 3.91 | 179.3 | 2.05 |

| Latch | ΔD | ΔP | ΔA | ΔDPAP |

|---|---|---|---|---|

| The traditional | 191.2% | −25.6% | −72.3% | −40.0% |

| HiPeR [7] | 53.6% | −27.6% | −48.7% | −42.9% |

| HLR-CG1 [8] | 80.2% | 40.2% | −52.3% | 20.0% |

| DNCS [13] | 760.7% | 76.7% | −4.6% | 1348.8% |

| CLCT [14] | 470.0% | 29.2% | −17.0% | 510.2% |

| Delta DICE [15] | 270.8% | 170.8% | 10.8% | 1010.2% |

| DONUT [16] | 342.9% | 163.7% | −8.2% | 970.2% |

| DNURL [17] | 8.8% | 76.2% | 49.7% | 186.8% |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jiang, J.; Zhu, W.; Xiao, J.; Zou, S. A Novel High-Performance Low-Cost Double-Upset Tolerant Latch Design. Electronics 2018, 7, 247. https://doi.org/10.3390/electronics7100247

Jiang J, Zhu W, Xiao J, Zou S. A Novel High-Performance Low-Cost Double-Upset Tolerant Latch Design. Electronics. 2018; 7(10):247. https://doi.org/10.3390/electronics7100247

Chicago/Turabian StyleJiang, Jianwei, Wenyi Zhu, Jun Xiao, and Shichang Zou. 2018. "A Novel High-Performance Low-Cost Double-Upset Tolerant Latch Design" Electronics 7, no. 10: 247. https://doi.org/10.3390/electronics7100247

APA StyleJiang, J., Zhu, W., Xiao, J., & Zou, S. (2018). A Novel High-Performance Low-Cost Double-Upset Tolerant Latch Design. Electronics, 7(10), 247. https://doi.org/10.3390/electronics7100247