1. Introduction

With increasing demand for larger display sizes and improved quality, OLED displays have gained a reputation as a cost-effective solution in recent years. As usual, a significant portion of the power consumed by electronic devices is used by the displays, making compact, highly efficient DC-DC converter solutions critical for IoTs and wearable devices.

Traditional OLED display power supplies, although practical and straightforward, struggle with on-chip integration due to two bulky inductors since they consist of two different power converters, a boost and an inverting buck–boost converter, to generate both positive and negative voltage. The simplicity of conventional OLED display power supplies comes at the cost of enormous inductor sizes. At the same time, their performance is tied to the efficiency of their internal buck–boost converter, which also suffers from high-voltage stress on power switches. This combination of downsides has driven up fabrication costs and limited circuit performance [

1,

2,

3].

Conventional single-inductor bipolar-output (SIBO) converters have been widely adopted for OLED applications due to their reduced component count; however, they suffer from several inherent limitations, including cross-regulation between positive and negative outputs, increased inductor current ripple under unbalanced loads, and limited efficiency at light-load conditions. These issues have been reported in prior works [

4,

5,

6].

Alternative solutions to SIBO converters include dual-inductor, dual-output converters [

4] and switched-capacitor-based bipolar converters [

7]. While these approaches can mitigate cross-regulation or improve efficiency under certain conditions, they generally incur higher silicon area, increased external component count, or degraded transient performance. In particular, prior flying-capacitor-assisted SIBO architectures have typically incorporated only a single capacitor [

8,

9,

10]. While effective in reducing switch voltage stress and inductor current to some degree, they leave room for further optimization of inductor current ripple and conduction loss, especially under significant load imbalance. The selection of power switches—using large-sized NMOS transistors for switches connected to lower-voltage nodes (like S

2, S

3, and S

4) to minimize on-resistance R

ON, and PMOS transistors for switches connected to higher-voltage rails (like S

1, S

5, and S

6)—is critical for reducing conduction loss and managing voltage stress across different phases of operation.

Recent hybrid bipolar-output converter designs have favored single-inductor bipolar-output (SIBO) topologies, which now require only a single inductor for both power rails, significantly reducing production costs and product size [

4,

11,

12]. However, they still possess drawbacks. First, the voltage stress on power switches is often greater than 5 V, requiring high-voltage devices. Second, instead of two conducting paths for each inductor, there is now only a single current path; consequently, the inductor current increases, and a larger inductor with a lower DC resistance is needed to avoid conduction loss, ensuring high current and optimal inductance [

10,

11]. To mitigate these problems, the designs in [

12,

13,

14] have added a flying capacitor, effectively dividing the conduction path into two, charging both the inductor and the flying capacitor, reducing inductor current while simultaneously sharing a voltage of V

IN with the flying capacitor, thus decreasing the |V

IN + V

ON| stress placed on power switches in conventional SIBO converters.

The principal novelty of this work is the introduction of a second flying capacitor on the VOP output line, forming a dual flying-capacitor architecture. This modification, combined with a PWM control scheme featuring an adaptive ramp generator, creates a more effective dynamic feedback loop. This approach achieves a greater reduction in peak inductor current and output-voltage ripple compared to single flying-capacitor SIBO topologies, without the increase in circuit complexity or silicon area. In this paper, we propose a hybrid bipolar-output converter that uses a single inductor and two flying capacitors to reduce voltage stress and inductor current, employing a PWM control scheme with an adaptive ramp generator to form a dynamic feedback loop, thereby minimizing inductor current and output-voltage ripple on both power rails. Implemented in the 180 nm CMOS process, the converter achieves a 93% peak efficiency at a 350 mA load current and an 84% average efficiency over 150–500 mA, with an output-voltage ripple under 20 mV at any given condition and load.

2. Circuit Implementation

Figure 1 illustrates the overall architecture of the designed SIBO converter. The converter generates output voltages V

OP and V

ON of 4.9 V and −4.7 V, respectively, from a 3.7 V battery supply. The core operational principle involves time-multiplexing the single inductor between the positive and negative output rails across the following four distinct switching phases: two main phases Φ

1 and Φ

2 for balanced energy delivery and two auxiliary phases Φ

P and Φ

N for correcting load imbalance. Switches S

1÷3 and S

4÷6 are controlled by a PWM controller, generating two symmetric main phases and two auxiliary phases for balancing the I

OP and I

ON currents. During the main phases, energy is transferred from the input to both outputs in a balanced manner. The auxiliary phases are selectively activated by the control loop to direct energy preferentially to the output rail with higher demand, thereby maintaining voltage regulation under unbalanced load conditions. Large passive components are the inductor L = 2.2 µH and capacitors C

F1 = C

F2 = 4.7 µF; they are all implemented off-chip and connected to the integrated circuit via the PCB after fabrication and packaging. All switches and level shifters (LSs) are powered internally from V

IN, V

ON, V

OP, or the C

F1/C

F2 capacitors, eliminating the need for external supply rails. A dedicated level shifter (LS

2) ensures proper operation of the S

2 gate driver across the voltage swing on capacitor C

F1. Similarly, level shifter LS

3 is designed for S

3 to translate signals from 0 V to the V

ON level, ensuring a sufficient V

GS for switching. In contrast, switches S

4–S

6 are driven by an on-chip LDO generating V

OP_1.8, V

IN_1.8, and V

DD, while S

1’s driver is supplied directly by V

IN. In the power stage, switches S

2, S

3, and S

4 are implemented with large-sized NMOS transistors to minimize on-resistance, while S

1, S

5, and S

6 use PMOS transistors.

The inductor value L is determined by limiting the inductor current ripple, which is given based on the work in [

15]:

To ensure continuous conduction and limit the current ripple to approximately 30% of the average inductor current under maximum load conditions, an inductance in the range of 1.8–2.5 µH is required for a 1 MHz switching frequency. Therefore, an inductance of 2.2 µH is selected as a trade-off between current ripple, conduction loss, and transient response. The flying capacitor is chosen based on the voltage ripple caused by charge transfer, which is calculated in [

16]:

Under the maximum load current, maintaining the flying-capacitor voltage ripple below a few millivolts requires a minimum capacitance of approximately 4 µF. Consequently, a 4.7 µF flying capacitor is selected to provide sufficient margin against load variation and process mismatch. The switching frequency is set to 1 MHz to balance switching loss, passive component size, and output-voltage ripple. Operating at this frequency enables compact passive components while maintaining high efficiency and low ripple, which are critical for OLED display applications.

The converter operates through four distinct states (two primary and two auxiliary phases), requiring at least two PWM control signals. As shown in

Table 1, switches S

1–S

3 maintain identical or complementary switching states across all four phases, allowing them to be driven by a single PWM signal (PWM

1, duty cycle D

1). The same principle applies to switches S

4–S

6, which are controlled by a second, synchronized PWM signal (PWM

2, duty cycle D

2).

In the designed bipolar-output DC-DC converter for OLED displays, it is ideal for the VOP and VON sources to have perfectly balanced power. The separate current balancing for the VOP and VON outputs underscores the requirement for identical energy delivery. However, load current imbalance can arise from internal circuits drawing different currents from VOP and VON, or from specific application requirements for independent regulation of these rails. For instance, during startup, the output capacitors (COP and CON) are discharged to 0V and can be charged to different values, leading to a voltage imbalance. If VOP is lower than |VON|, it indicates a greater energy demand for VON, resulting in a higher load current for VON (ION) compared to VOP (IOP), and vice versa.

To address this potential imbalance, dedicated auxiliary phases are implemented to transfer energy specifically to V

OP or V

ON. When I

OP > I

ON, indicating a higher energy demand for V

OP, the phase Φ

P is activated, turning on switches S

1, S

2, and S

5 to transfer energy exclusively to V

OP. Conversely, phase Φ

N is activated to transfer energy only to V

ON via switches S

3, S

4, and S

6. These two phases are illustrated in

Figure 2c,d.

Figure 3 shows the oscillator block, a ring of cross-coupled inverters M

23,24, controls the charge/discharge cycle of timing capacitor C

O1. Resistor R

O1 sets the discharge rate. The output at node C

LK is a 1 MHz clock signal used to create the control triangle waves, V

RAMP1 and V

RAMP2, which are essential for regulating the converter’s output voltage. A ring of cross-coupled inverter gates charges and discharges capacitor C

O1 in a stable, continuous cycle. The values of C

O1 and R

O1 determine the oscillation frequency. Transistors M

23 and M

24 function as inverters without a constant-current source, connected in series to minimize noise and achieve the sharpest possible transition slope. The oscillator, supplied by V

DD, was designed with the parameters shown in

Figure 3. To achieve a target T

ON period of 210 ns, transistor M

24 was sized to have a high on-resistance. This intentionally introduces a turn-on delay, creating a small duty cycle where T

ON is less than the whole clock period.

Figure 4 shows the schematic for our negative voltage reference circuit; the operation is sequenced by three non-overlapping clock signals C

LKP1,2,3 controlling T-gate switches similar to M

28,39. The charge-pump stage creates V

REFN, which is then regulated via feedback through PMOS switches M

52,53 and operational transconductance amplifier OTA

2, in which three control clock signals C

LKP1,2,3 have a 110 ns pulse width and are turned on sequentially in incremental order of their numbering. A default symmetrical negative voltage is generated using the fundamental principle of a capacitor’s two plates. To create a negative voltage, a positive voltage is first stored across a capacitor. This voltage is then inverted to a negative value at the opposite plate via charge transfer. This charging and inverting process requires precisely timed clock signals to control the switching sequence. The circuit employs T-gate switches M28 and M39, which use complementary CMOS pairs to achieve lower on-resistance than conventional switches. Three clock signals C

LKP1,2,3 with the same frequency but a 90-degree phase shift between each other are used to generate a negative voltage V

REFN with minimal ripple. The generated V

REFN is fed through PMOS switches M

52,53 to regulate the V

NFB node. In operation, any variation in V

REFN due to load changes is detected. The operational transconductance amplifier (OTA2) then outputs an error voltage to stabilize V

REFN through this closed-loop feedback mechanism. This ensures V

NFB remains stable and symmetrical to the positive reference voltage V

REFP. V

REFN and V

REFP serve as the converter’s built-in reference voltages. Conventional converters that lack an integrated negative reference generator require an external reference, increasing the off-chip component area and overall system size.

A differential amplifier with four inputs and two outputs, V

PCM and V

NCM, are shown in

Figure 5 to perform signal summation and generate the required error voltages. The amplifier core is based on a stacked folded cascode topology, incorporating PMOS M

59,60,61,62 and NMOS M

63,64,65,66 differential input pairs. This configuration enhances precision by applying the input signal to both PMOS and NMOS transistors, thereby extending the input common-mode range and achieving higher gain. The designed amplifier, denoted as A

CM, consumes a low quiescent power of 6.3 µW. It achieves a high gain of over 90 dB with a small bandwidth of 1.3 kHz, which will help limit amplification at high frequencies and instead compare only low-frequency DC signal differences.

As shown in

Figure 6, OTA

1 is a single-stage OTA with two inputs, V

IN and V

IP, and one output V

O1. The design in

Figure 6a employs both PMOS and NMOS differential input pairs to enhance precision, providing a wide input range and high gain. Switches M

106,107 are biased to serve as active resistors. They create different reference voltages for the folded-cascode transistors M

102,103 and M

101,111 to control the current consumption in the stacked stage. OTA

1 is designed for low power consumption and low bandwidth, as it is intended for integration within a Type II compensator network. OTA

2 utilizes a current-mirror OTA architecture. The schematic in

Figure 6b shows the design of OTA

2, where the quiescent current in each branch M

113,114 is set to 3.7 μA to provide sufficient drive strength. Both OTAs are designed to create stable, fast, and precise current-controlled circuits.

In a bipolar-output DC-DC converter, the V

OP and V

ON voltages can become imbalanced due to constantly varying output loads. To mitigate the difference between the I

ON and I

OP currents, a triangle-wave generator with an adaptive pulse width is implemented; it responds to changes in the V

NDM and V

PDM control signals.

Figure 7 shows the schematic and design parameters of this adaptive pulse triangle-wave generator. The circuit uses the previously designed OTA

2 as a controlled current source, acting as a small LDO whose output is modulated by the V

NDM and V

PDM voltages. A fixed bias current is provided, ensuring the ramp signal is never completely turned off during startup, even when V

PDM and V

NDM are at the V

SS or V

DD rails. The ramp signal is generated by exploiting the charging and discharging characteristics of capacitors C

A1 and C

A2, which are controlled by the clock signal C

LK from the oscillator block.

In

Figure 8a, the schematic of the first level shifter LS1 is shown. It converts an input square wave S

IN with a 1.8 V upper rail and a 0 V lower rail to an output wave whose rails are defined by the applied voltages V

H and V

L, spanning from V

IN down to 0 V. Furthermore,

Figure 8b presents the schematic of the second level shifter LS2. While its input is also a 1.8 V/0 V square wave, LS2 is supplied with a negative voltage at V

LN2 and a positive voltage at V

HN2. This is because the LS2 block is designed to drive switches S

2 and S

3 with a negative ON voltage V

ON.

Both the LS1 and LS2 blocks employ a current-mirror structure. When the SIN signal transitions, the control switches toggle, creating a voltage imbalance. The current-mirror configuration detects this minute change and swiftly generates the corresponding output-voltage levels (VH/VL for LS1 and VHN2/VLN2 for LS2). To ensure the level-shifted output signal has sufficient current strength to drive the switches S1÷6, the core inverter stages within the shifter are sized up to increase the charging current.

3. Results

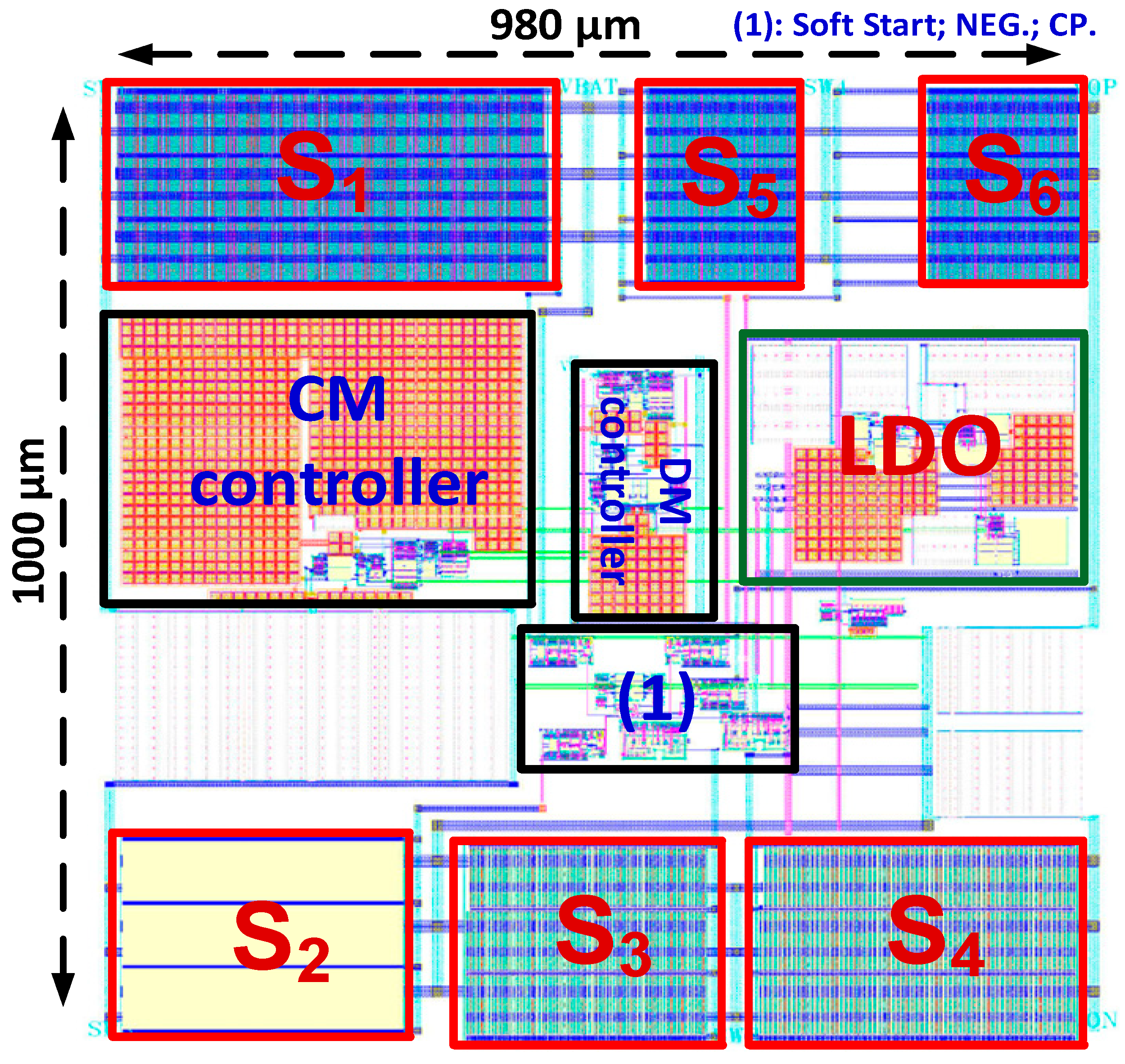

Figure 9 illustrates the layout arrangement of the complete bipolar-output DC-DC converter, including the placement of the power switches S

1÷6. With a chip area of 0.98mm

2, the converter consists of two main control blocks, namely the DM (differential mode) controller and the CM (common mode) controller, which are placed at the center of the chip in order to deliver control clock signals to other blocks, mainly the level shifters, with as little delay time as possible. The power switches S

1÷6 are placed on the outskirt of the chip for easy access to I/O pads. The layout was verified using Calibre through LVS and DRC checks. Parasitic components in the layout were carefully optimized to ensure high accuracy and reliability during fabrication.

Figure 10a shows that the output voltages require approximately 500 μs to stabilize from startup, reaching steady-state values of V

OP = 4.9 V and V

ON = −4.7 V. The simulation was performed using 0.18 μm technology node with the following parameters: a default positive reference voltage V

REFP = 450 mV, a negative reference voltage V

REFN = −430 mV, an inductor L = 2.2 μH, output capacitors C

OP = C

ON = 10 μF, a switching frequency of 1 MHz, and a supply voltage of 3.7 V.

Figure 10b shows the V

PCM and V

NCM signals during the stable operation of the bipolar-output DC-DC converter. At initial startup, the voltage difference between V

FBN/V

FBP and V

REFN/V

REFP is large, causing the A

CM block to act as a comparator. Once the converter stabilizes at the desired output voltages, the V

PCM and V

NCM signals become equal.

Figure 11a shows the waveforms of V

PDM and V

NDM. During the initial startup phase, these signals continuously adjust to balance the I

OP and I

ON currents by controlling the auxiliary phases of the power switches network.

Figure 11b illustrates the corresponding modulation of the D

1 and D

2 duty cycles to correct any imbalance between I

OP and I

ON. A disparity between the D

1 and D

2 duty cycles triggers the automatic activation of an auxiliary phase to restore balance. This balancing occurs both at startup and during load transients, such as transitions from high to low load. The modulation is achieved by varying the peak of the triangle wave while keeping the VSUM signal constant, necessitating adjustments to the D

1 and D

2 duty cycles.

Figure 12a shows the waveforms of V

ON, V

OP, and the inductor current under a 300 mA load. The voltage ripple on V

ON and V

OP is 14 mV, and the inductor current ripple is 440 mA. It can be observed that, despite variations in load current, V

ON and V

OP remain stable at approximately −4.7 V and 4.9 V, respectively. Furthermore, a lower load current results in reduced voltage ripple on V

ON and V

OP, as the inductor current ripple decreases.

Figure 12b shows the converter’s efficiency as a function of the load current. This result was plotted with all the losses accounted for, including the power consumptions of different blocks (gate driver, level shifter, ….) as well as switching loss and conduction loss inflicted onto the MOSFETs inside the power stage. The peak efficiency is 93%, which occurs at an output current of 0.35 A.

Table 2 presents a performance comparison between the proposed converter and similar state-of-the-art SIBO converters. The proposed design, implemented in a 0.18 µm CMOS process, achieves a peak efficiency of 93% at 350 mA, which is competitive with the 94% efficiency of [

13] and superior to the 88–89% efficiencies of [

17,

18]. A key advantage of this work is its significantly wider output current range of 100–500 mA, supporting heavier loads than the compared designs. Furthermore, it accomplishes this with a substantially smaller inductor value of 2.2 µH, a reduction of over 75% compared to the 10 µH required by [

13,

17,

18], which is crucial for system miniaturization. This design also achieves the smallest active chip area of 0.98 mm

2, demonstrating a more area-efficient integration despite not using the most advanced process node.