Design of a CMOS Self-Bootstrapping Rectifier with Latch-up Protection for Wireless Power Harvesting Systems

Abstract

1. Introduction

2. Typical Rectifier Circuits

2.1. Full-Wave Diode Rectifier

2.2. Gate Cross-Coupled Rectifier

2.3. Mixed Cross-Coupled Rectifier

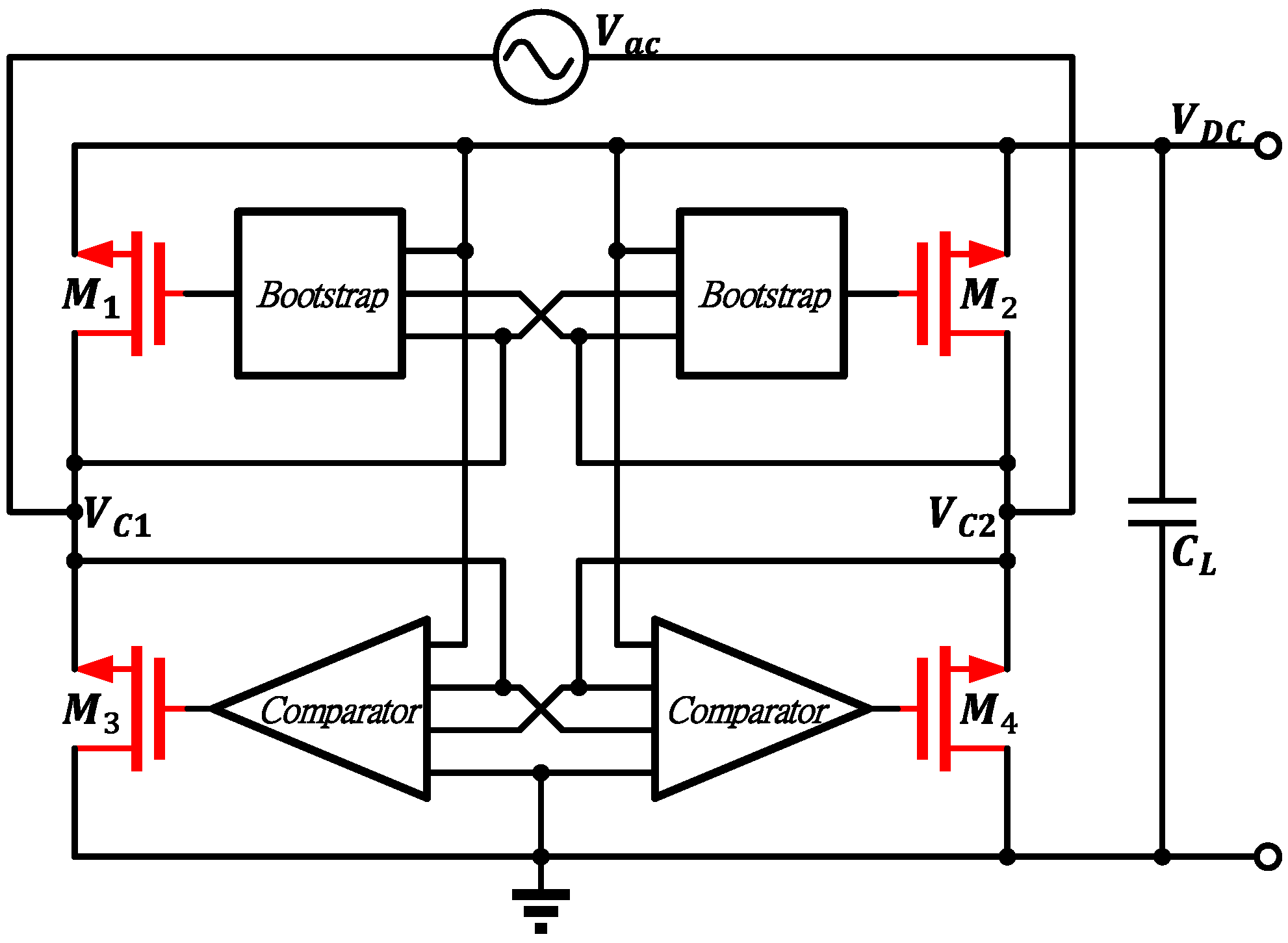

3. Proposed Boost-Comparator Rectifier

3.1. Bootstrap Circuit

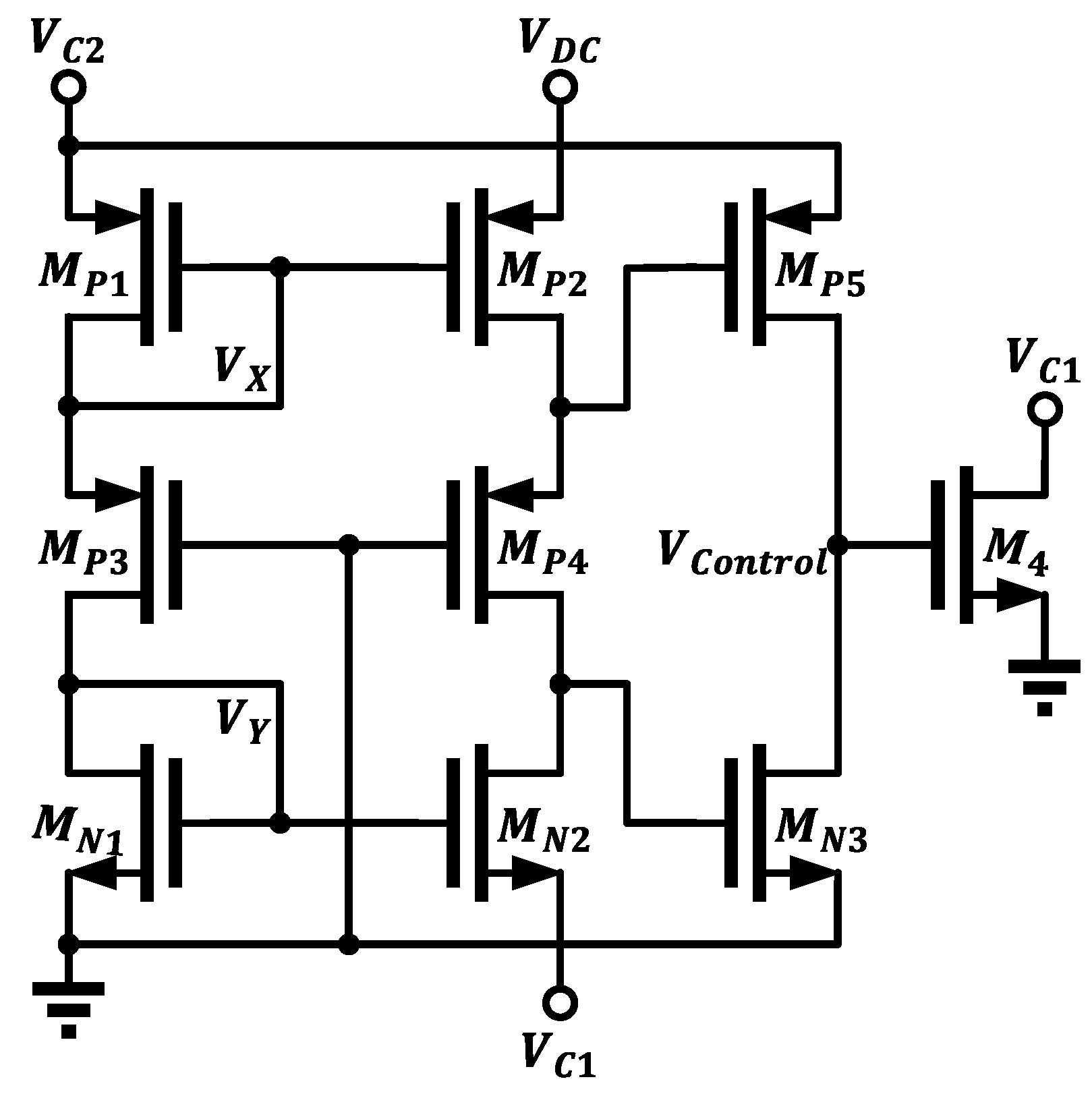

3.2. 4-Input Comparator Circuit

4. Simulation and Measurement

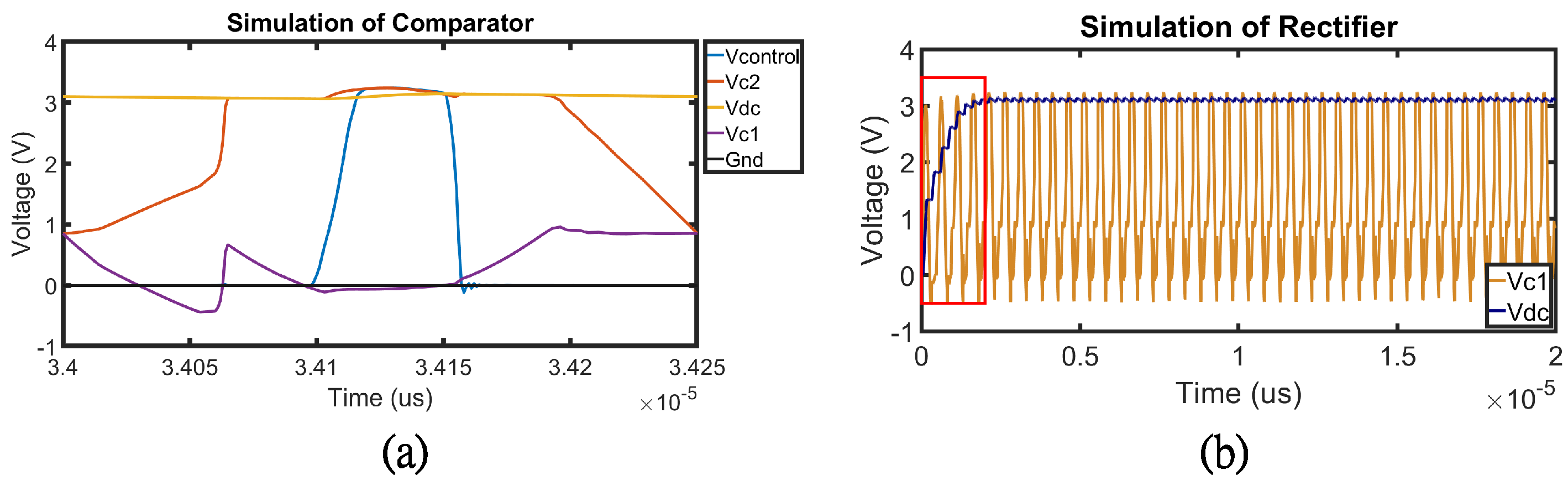

4.1. Simulation

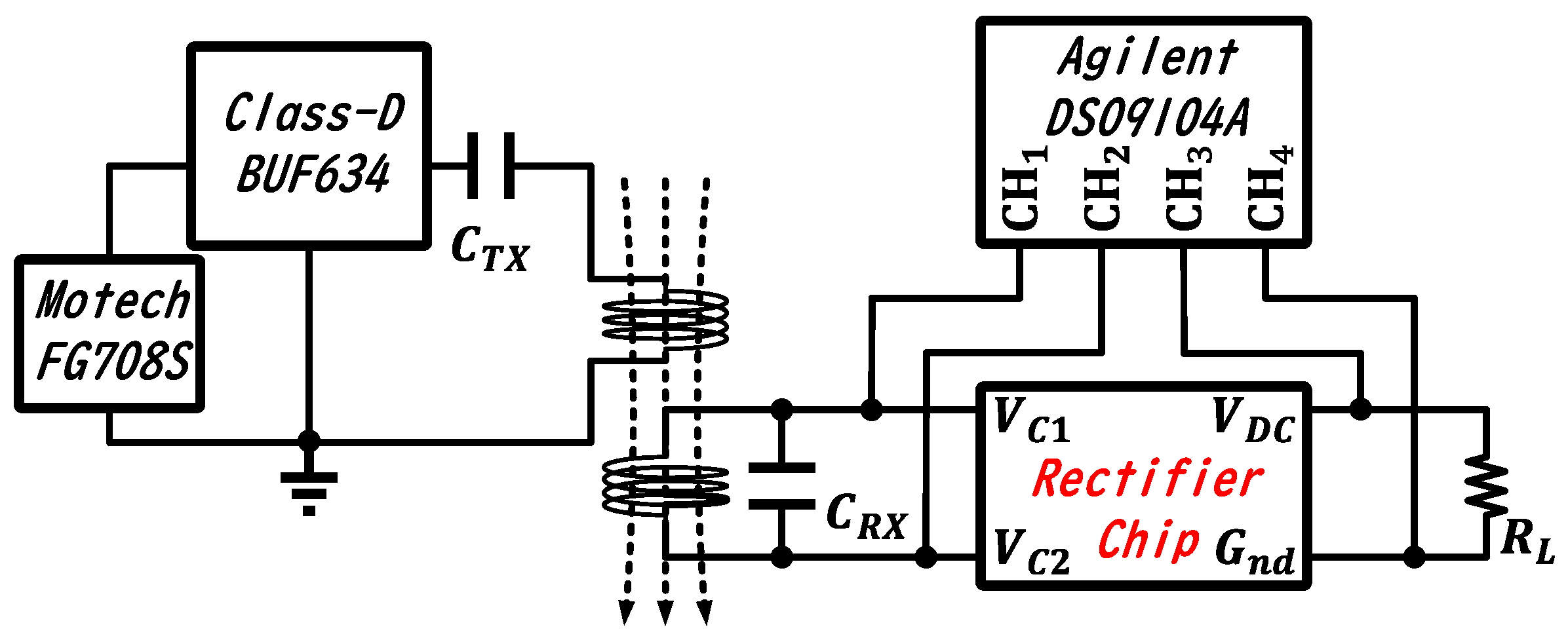

4.2. Measurement

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Lambiase, P.D.; Theuns, D.A.; Murgatroyd, F.; Barr, C.; Eckardt, L.; Neuzil, P.; Scholten, M.; Hood, M.; Kuschyk, J.; Brisben, A.J.; et al. Subcutaneous implantable cardioverter-defibrillators: Long-term results of the EFFORTLESS study. Eur. Heart J. 2022, 43, 2037–2050. [Google Scholar] [CrossRef] [PubMed]

- Yip, M.; Jin, R.; Nakajima, H.H.; Stankovic, K.M.; Chandrakasan, A.P. A Fully-Implantable Cochlear Implant SoC with Piezoelectric Middle-Ear Sensor and Arbitrary Waveform Neural Stimulation. IEEE J. Solid-State Circuits 2015, 50, 214–229. [Google Scholar] [CrossRef]

- Ahn, W.; Kim, D.; Park, J.; Park, J.H.; Lee, T.; Jeong, K. A Reconfigurable Neural Stimulation IC with a High-Resolution Strength Control and In-Situ Neural Recording Function for Cochlear Implant Systems. IEEE Solid-State Circuits Lett. 2022, 5, 162–165. [Google Scholar] [CrossRef]

- Weiland, J.D.; Humayun, M.S. Visual Prosthesis. Proc. IEEE 2008, 96, 1076–1084. [Google Scholar] [CrossRef]

- Wu, K.Y.; Mina, M.; Sahyoun, J.-Y.; Kalevar, A.; Tran, S.D. Retinal Prostheses: Engineering and Clinical Perspectives for Vision Restoration. Sensors 2023, 23, 5782. [Google Scholar] [CrossRef]

- Lo, Y.K.; Kuan, Y.-C.; Culaclii, S.; Kim, B.; Wang, P.-M.; Chang, C.-W. A Fully Integrated Wireless SoC for Motor Function Recovery After Spinal Cord Injury. IEEE Trans. Biomed. Circuits Syst. 2017, 11, 497–509. [Google Scholar] [CrossRef]

- Mao, G.; Zhou, Z.; Su, H.; Chen, Y.; Zhang, J.; Zhang, C. A Fully Implantable and Programmable Epidural Spinal Cord Stimulation System for Rats with Spinal Cord Injury. IEEE Trans. Neural Syst. Rehabil. Eng. 2023, 31, 818–828. [Google Scholar] [CrossRef]

- Ramadass, Y.K.; Chandrakasan, A.P. An Efficient Piezoelectric Energy Harvesting Interface Circuit Using a Bias-Flip Rectifier and Shared Inductor. IEEE J. Solid-State Circuits 2010, 45, 189–204. [Google Scholar] [CrossRef]

- Hashemi, S.S.; Sawan, M.; Savaria, Y. A High-Efficiency Low-Voltage CMOS Rectifier for Harvesting Energy in Implantable Devices. IEEE Trans. Biomed. Circuits Syst. 2012, 6, 326–335. [Google Scholar] [CrossRef] [PubMed]

- Roy, S.; Azad, A.N.M.W.; Baidya, S.; Alam, M.K.; Khan, F. Powering Solutions for Biomedical Sensors and Implants Inside the Human Body: A Comprehensive Review on Energy Harvesting Units, Energy Storage, and Wireless Power Transfer Techniques. IEEE Trans. Power Electron. 2022, 37, 12237–12263. [Google Scholar] [CrossRef]

- Vu, V.B.; Ramezani, A.; Triviño, A.; González-González, J.M.; Kadandani, N.B.; Dahidah, M. Operation of Inductive Charging Systems Under Misalignment Conditions: A Review for Electric Vehicles. IEEE Trans. Transp. Electrif. 2023, 9, 1857–1887. [Google Scholar] [CrossRef]

- Liu, Y.; Wu, T.; Fu, M. Interleaved Capacitive Coupler for Wireless Power Transfer. IEEE Trans. Power Electron. 2021, 36, 13526–13535. [Google Scholar] [CrossRef]

- Maleki, T.; Cao, N.; Song, S.H.; Kao, C.; Ko, S.-C.A.; Ziaie, B. An Ultrasonically Powered Implantable Micro-Oxygen Generator (IMOG). IEEE Trans. Biomed. Eng. 2011, 58, 3104–3111. [Google Scholar] [CrossRef]

- ISO 13485:2016; Medical Devices—Quality Management Systems—Requirements for Regulatory Purposes. ISO: Geneva, Switzerland, 2016.

- ISO 14708-1:2014; Implants for Surgery—Active Implantable Medical Devices—Part 1: General Requirements for Safety, Marking and for Information to be Provided by the Manufacturer. ISO: Geneva, Switzerland, 2014.

- Hu, J.; He, Y.; Min, H. High efficient rectifier circuit eliminating threshold voltage drop for RFID transponders. In Proceedings of the 2005 6th International Conference on ASIC, Shanghai, China, 24–27 October 2005; pp. 607–610. [Google Scholar]

- Kotani, K.; Ito, T. High efficiency CMOS rectifier circuits for UHF RFIDs using Vth cancellation techniques. In Proceedings of the 2009 IEEE 8th International Conference on ASIC, Changsha, China, 20–23 October 2009; pp. 549–552. [Google Scholar]

- Rakers, P.; Connell, L.; Collins, T.; Russell, D. Secure contactless smartcard ASIC with DPA protection. IEEE J. Solid-State Circuits 2001, 36, 559–565. [Google Scholar] [CrossRef]

- Ghovanloo, M.; Najafi, K. Fully integrated wideband high-current rectifiers for inductively powered devices. IEEE J. Solid-State Circuits 2004, 39, 1976–1984. [Google Scholar] [CrossRef]

- Hu, J.; Min, H. A low power and high performance analog front end for passive RFID transponder. In Proceedings of the 2005 4th IEEE Workshop on Automatic Identification Advanced Technologies (AutoID’05), Buffalo, NY, USA, 17–18 October 2005; pp. 199–204. [Google Scholar]

- Bawa, G.; Ghovanloo, M. Analysis, design, and implementation of a high-efficiency full-wave rectifier in standard CMOS technology. Analog. Integr. Circuits Signal Process. 2009, 60, 71–81. [Google Scholar] [CrossRef]

- Cha, H.K.; Park, W.-T.; Je, M. A CMOS Rectifier with a Cross-Coupled Latched Comparator for Wireless Power Transfer in Biomedical Applications. IEEE Trans. Circuits Syst. II Express Briefs 2012, 59, 409–413. [Google Scholar] [CrossRef]

- Chen, Y.; Song, Y.; Wu, B.; Liu, F.; Deng, Y.; Kang, P.; Huang, X.; Wu, Y.; Gao, D.; Xu, K. Optimization of Impact Ionization in Metal–Oxide–Semiconductor Field-Effect Transistors for Improvement of Breakdown Voltage and Specific On-Resistance. Electronics 2024, 13, 4101. [Google Scholar] [CrossRef]

- Zhou, Y.; Wang, K.; Yin, S.; Li, W.-Y.; Meng, F.; Wang, Z.-G. A Fully Integrated Stimulator with High Stimulation Voltage Compliance Using Dynamic Bulk Biasing Technique in a Bulk CMOS Technology. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 71, 2525–2537. [Google Scholar] [CrossRef]

- Gong, C.-S.A.; Li, S.-W.; Shiue, M.-T. A Bootstrapped Comparator-Switched Active Rectifying Circuit for Wirelessly Powered Integrated Miniaturized Energy Sensing Systems. Sensors 2019, 19, 4714. [Google Scholar] [CrossRef]

- Guo, S.; Lee, H. An Efficiency-Enhanced CMOS Rectifier with Unbalanced-Biased Comparators for Transcutaneous-Powered High-Current Implants. IEEE J. Solid-State Circuits 2009, 44, 1796–1804. [Google Scholar] [CrossRef]

- Rashidi, A.; Laursen, K.; Hosseini, S.; Huynh, H.-A.; Moradi, F. An Implantable Ultrasonically Powered System for Optogenetic Stimulation with Power-Efficient Active Rectifier and Charge-Reuse Capability. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 1362–1371. [Google Scholar] [CrossRef] [PubMed]

- Erfani, R.; Marefat, F.; Nag, S.; Mohseni, P. A 1–10-MHz Frequency-Aware CMOS Active Rectifier with Dual-Loop Adaptive Delay Compensation and >230-mW Output Power for Capacitively Powered Biomedical Implants. IEEE J. Solid-State Circuits 2020, 55, 756–766. [Google Scholar] [CrossRef]

- Zheng, K.; Hou, Y.; Wang, X.; Liu, Y. An Active Rectifier with Pulse Width Modulation (PWM) Mode On- and Off-Delay Compensation for Wireless Power Transfer (WPT) System. IEEE Access 2023, 11, 118204–118216. [Google Scholar] [CrossRef]

| Comparator Operation | MOS Switch | |

|---|---|---|

| ON | ||

| OFF | ||

| OFF/ON | ||

| Pre-Simulation | Post-Simulation | Measurement | |

|---|---|---|---|

| Supply voltage (V) | 3.3 | 3.3 | 3.3 |

| Operation Frequency (Hz) | 2 M | 2 M | 2 M |

| Maximum current (mA) | 5 | 5 | 5 |

| Power dissipation (mW) | 13.16 | 12.77 | 12.35 |

| VCE (%) (8 KΩ) | 97 | 96.92 | 89.02 |

| PCE (%) (500 ) | 82.95 | 83.49 | 84.73 |

| [26] | [27] | [28] | [29] | This Work | |

|---|---|---|---|---|---|

| Technology | 0.35 μm | 0.18 μm | 0.18 μm | 0.18 μm | 0.18 μm |

| Frequency | 1.5 MHz | 2.7 MHz | 1–10 MHz | 2 MHz | 2 MHz |

| 2.4 V | 3 V | 1.8 V | 2.4 V | 3.3 V | |

| 2.28 V | 2.84 V | 1.59 V | 2.25 V | 2.94 V | |

| 20 mA | N/A | N/A | N/A | 5 mA | |

| VCE | 97% (2 KΩ) | 93.57% (500 Ω) | 88.6% (300 Ω) | 93.7% (500 Ω) | 89.02% (8 KΩ) |

| PCE | 87% (100 Ω) | 94.51% (500 Ω) | 84.4% (300 Ω) | 91.7% (200 Ω) | 84.73% (500 Ω) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2026 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.

Share and Cite

Shiue, M.-T.; Lo, Y.-F.; Gong, C.-S.A. Design of a CMOS Self-Bootstrapping Rectifier with Latch-up Protection for Wireless Power Harvesting Systems. Electronics 2026, 15, 415. https://doi.org/10.3390/electronics15020415

Shiue M-T, Lo Y-F, Gong C-SA. Design of a CMOS Self-Bootstrapping Rectifier with Latch-up Protection for Wireless Power Harvesting Systems. Electronics. 2026; 15(2):415. https://doi.org/10.3390/electronics15020415

Chicago/Turabian StyleShiue, Muh-Tian, Yu-Fan Lo, and Cihun-Siyong Alex Gong. 2026. "Design of a CMOS Self-Bootstrapping Rectifier with Latch-up Protection for Wireless Power Harvesting Systems" Electronics 15, no. 2: 415. https://doi.org/10.3390/electronics15020415

APA StyleShiue, M.-T., Lo, Y.-F., & Gong, C.-S. A. (2026). Design of a CMOS Self-Bootstrapping Rectifier with Latch-up Protection for Wireless Power Harvesting Systems. Electronics, 15(2), 415. https://doi.org/10.3390/electronics15020415