Three-Channel Fully Integrated Galvanic Isolation Interface in GaN Technology

Abstract

1. Introduction

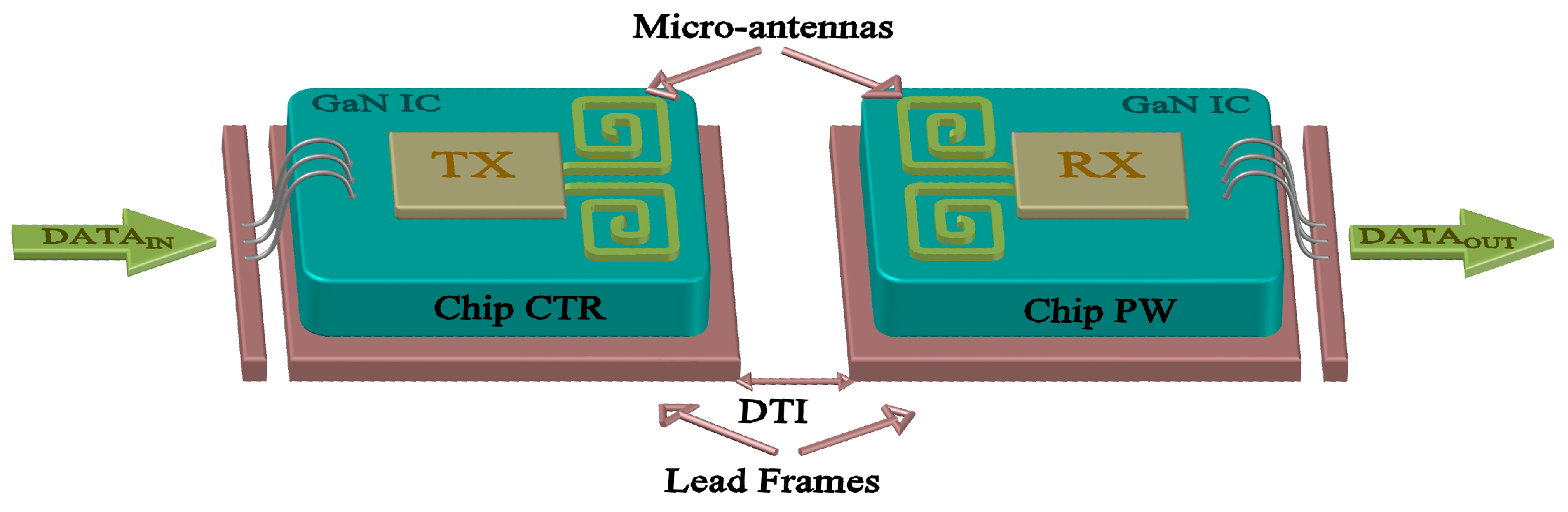

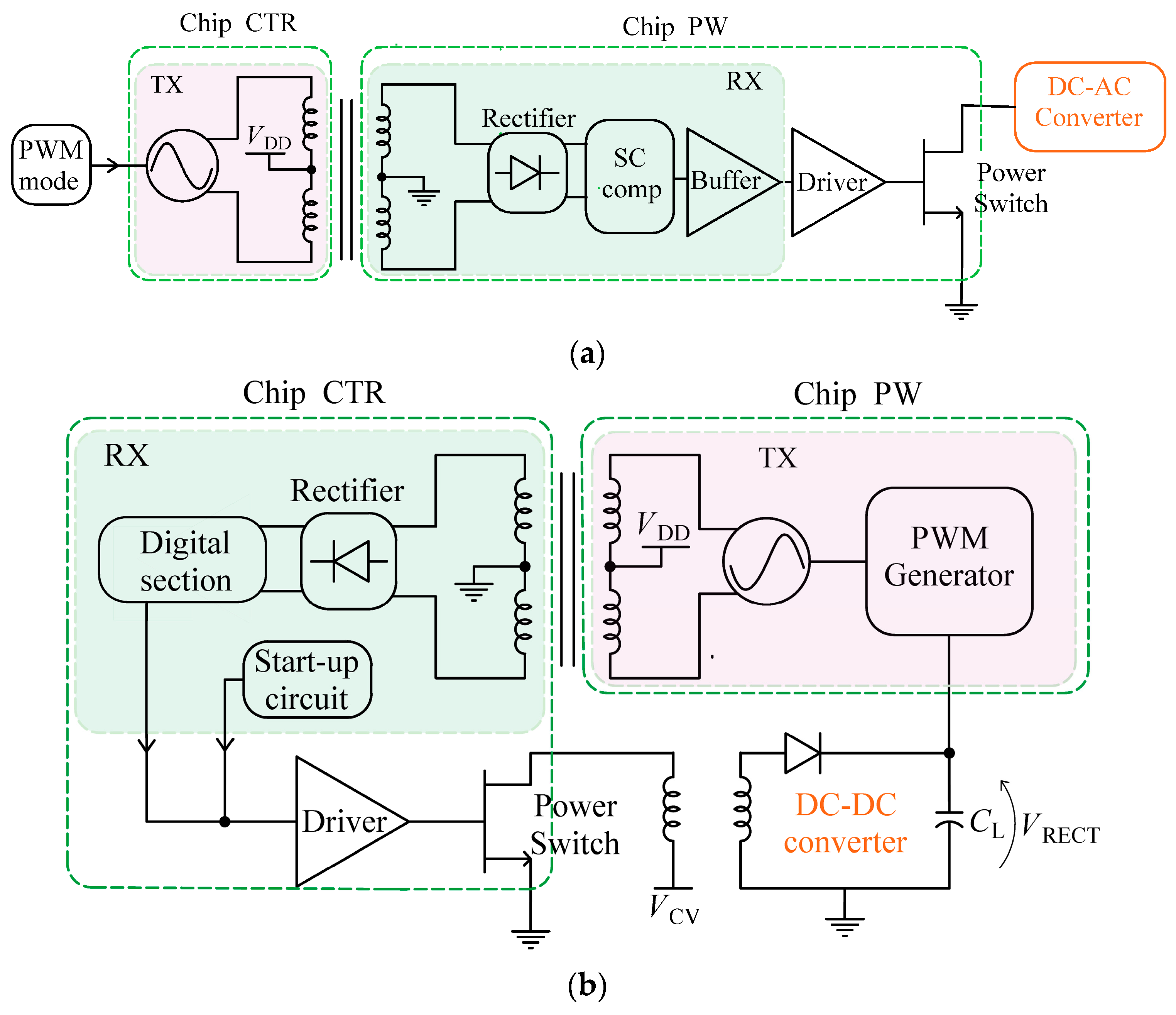

2. System Architecture

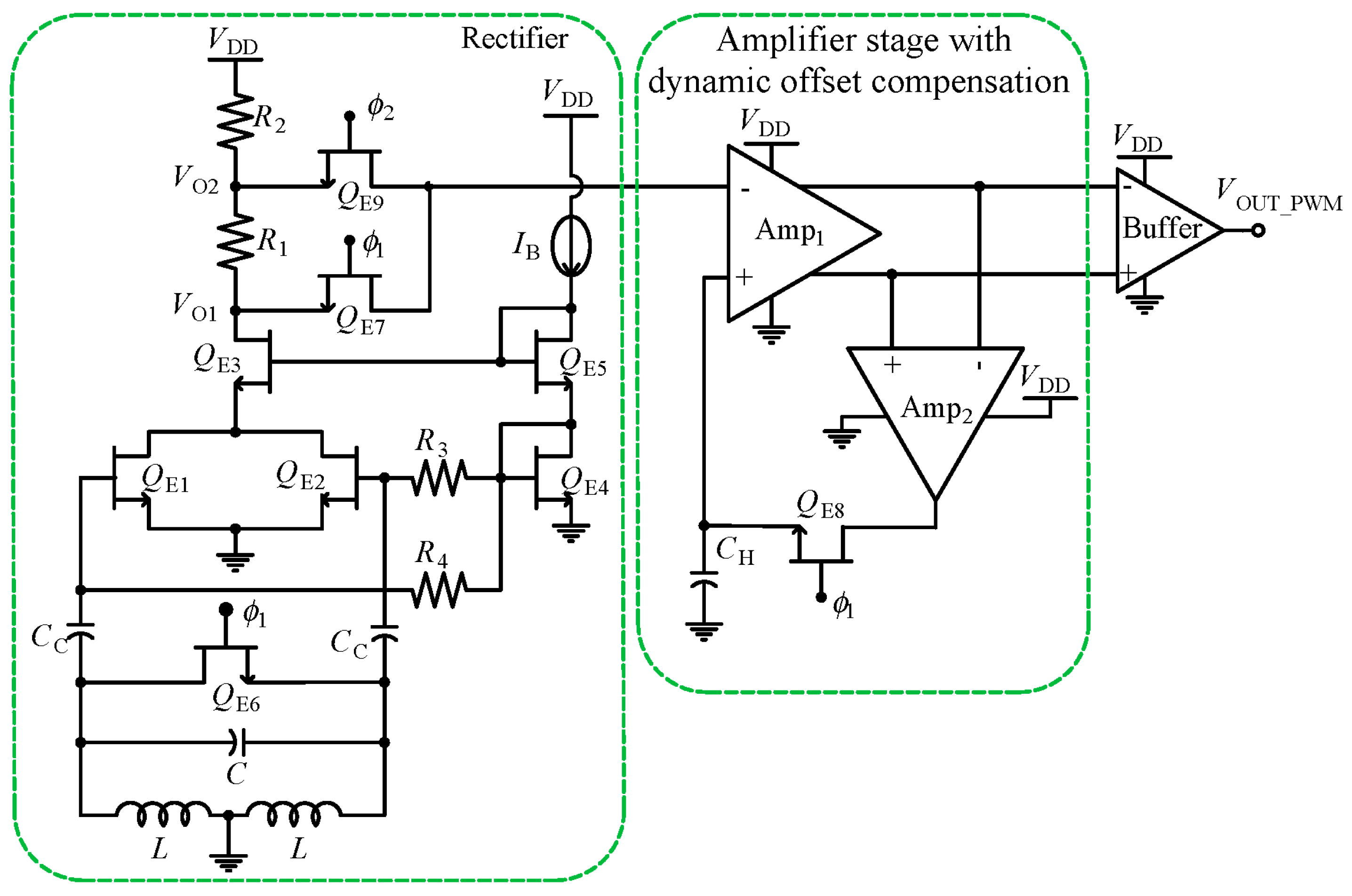

3. Receiver

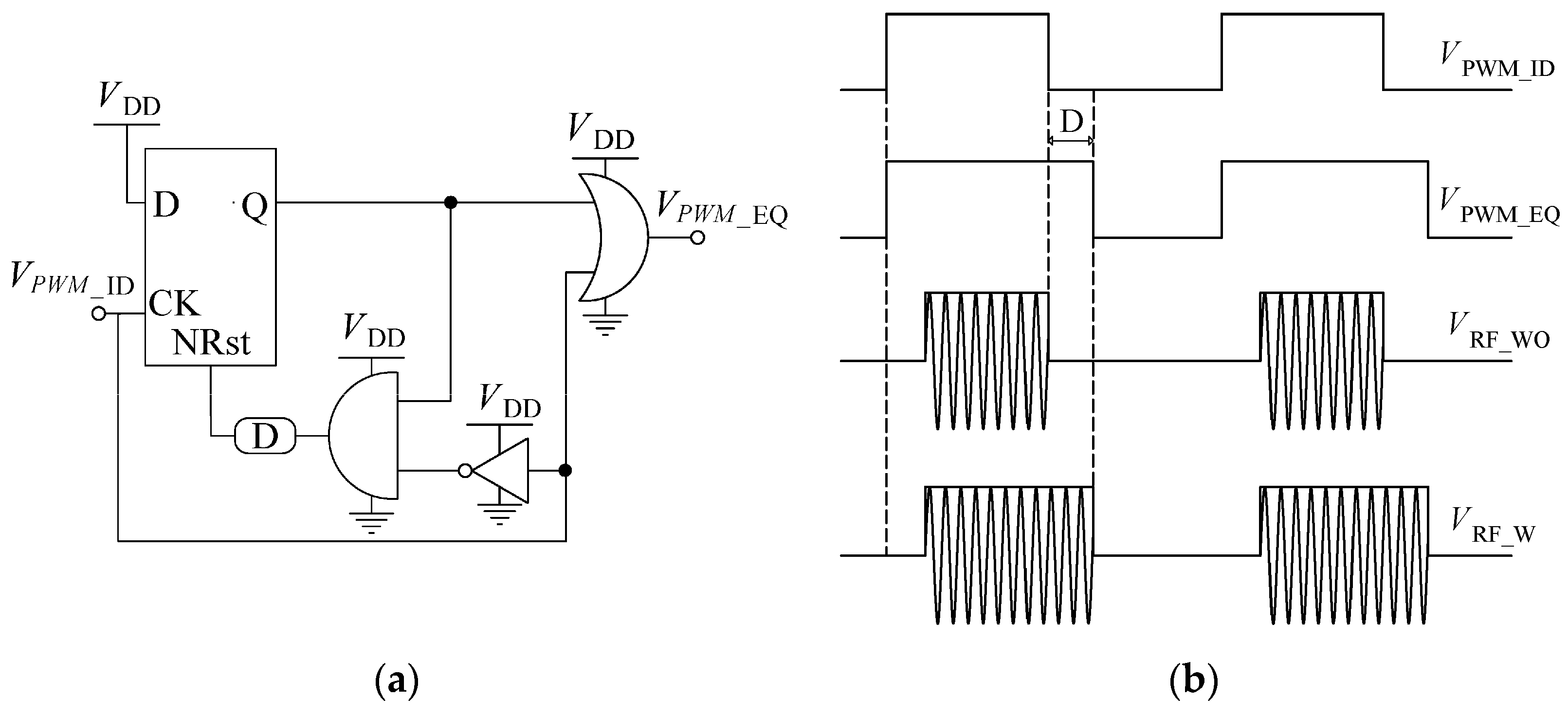

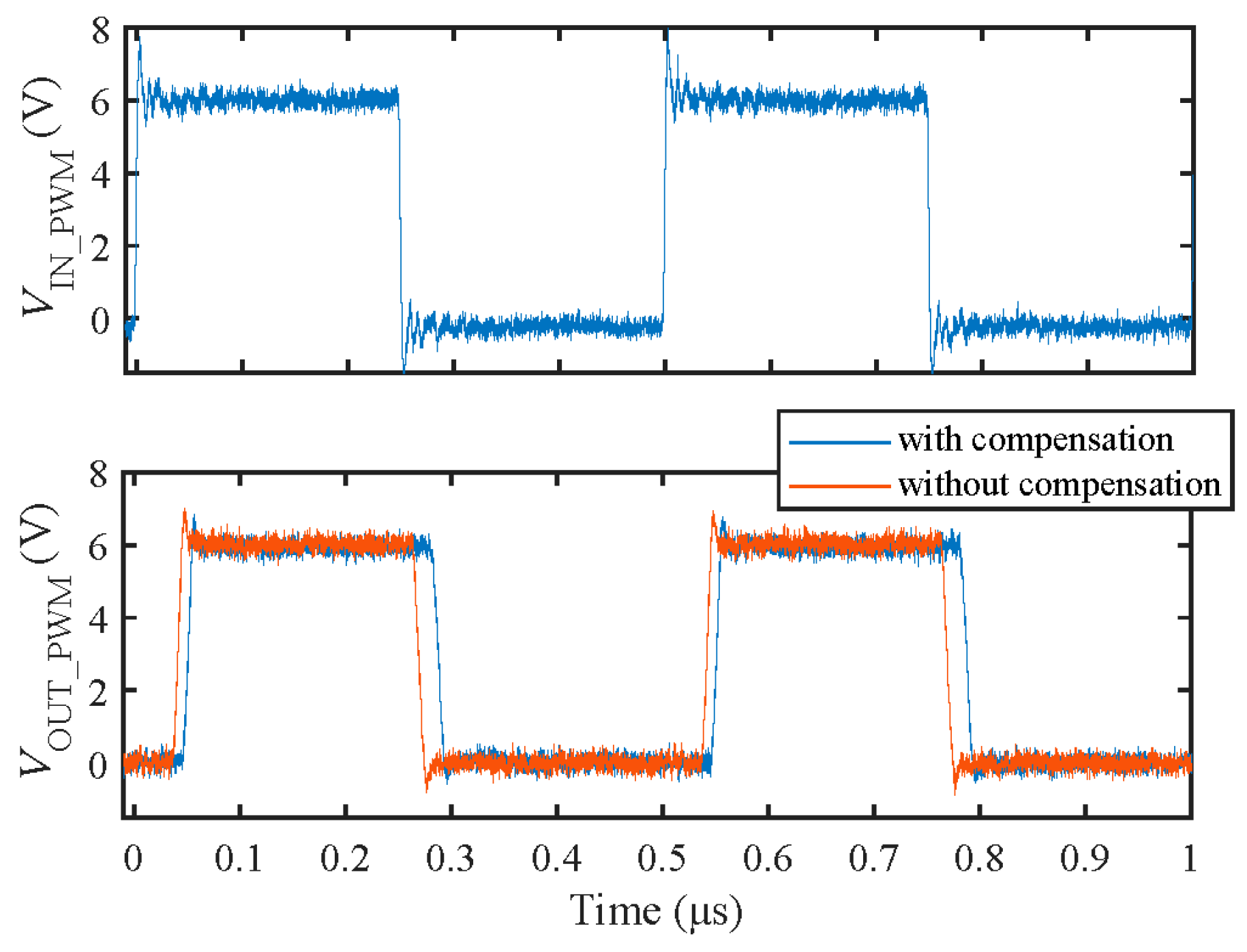

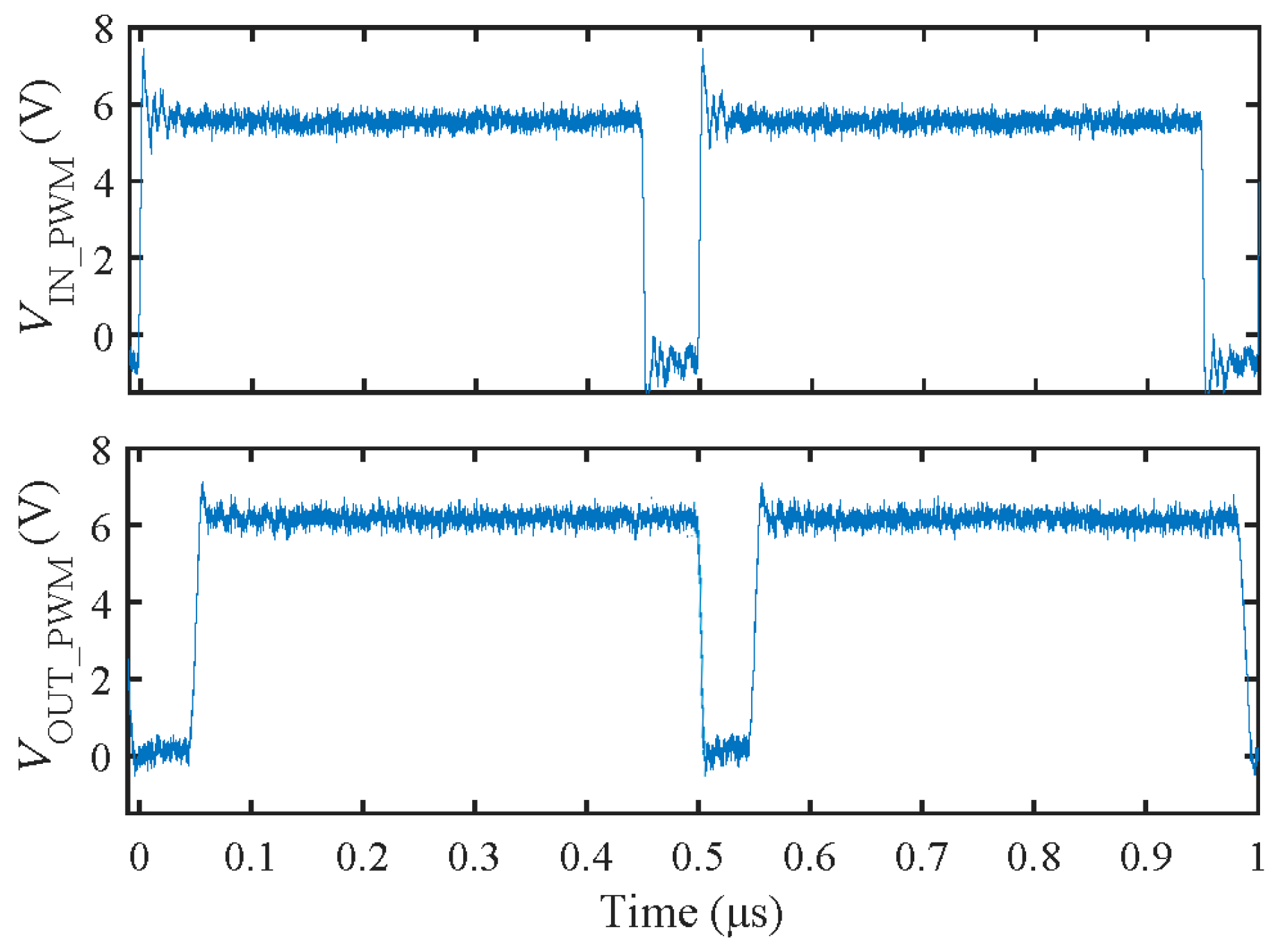

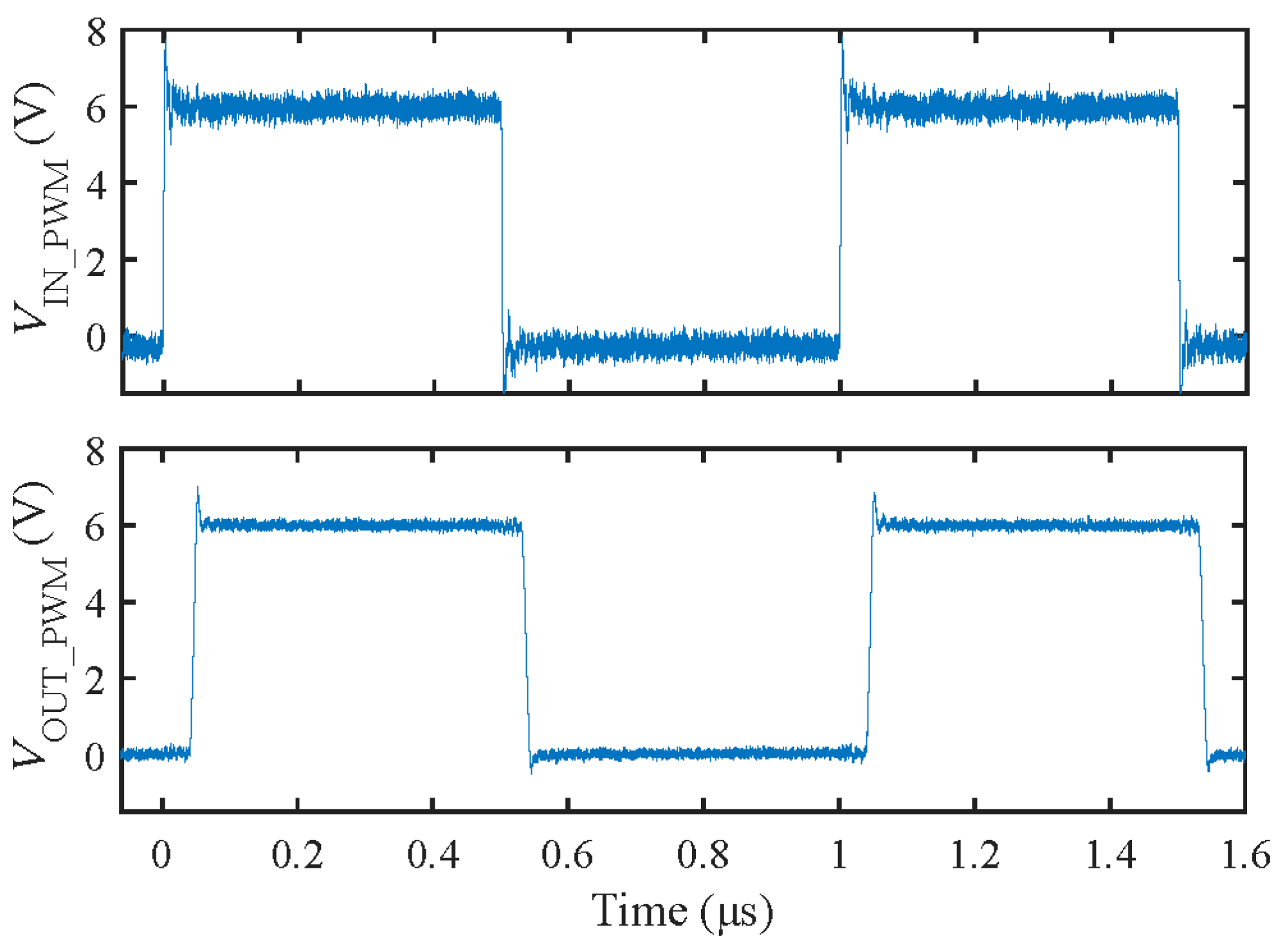

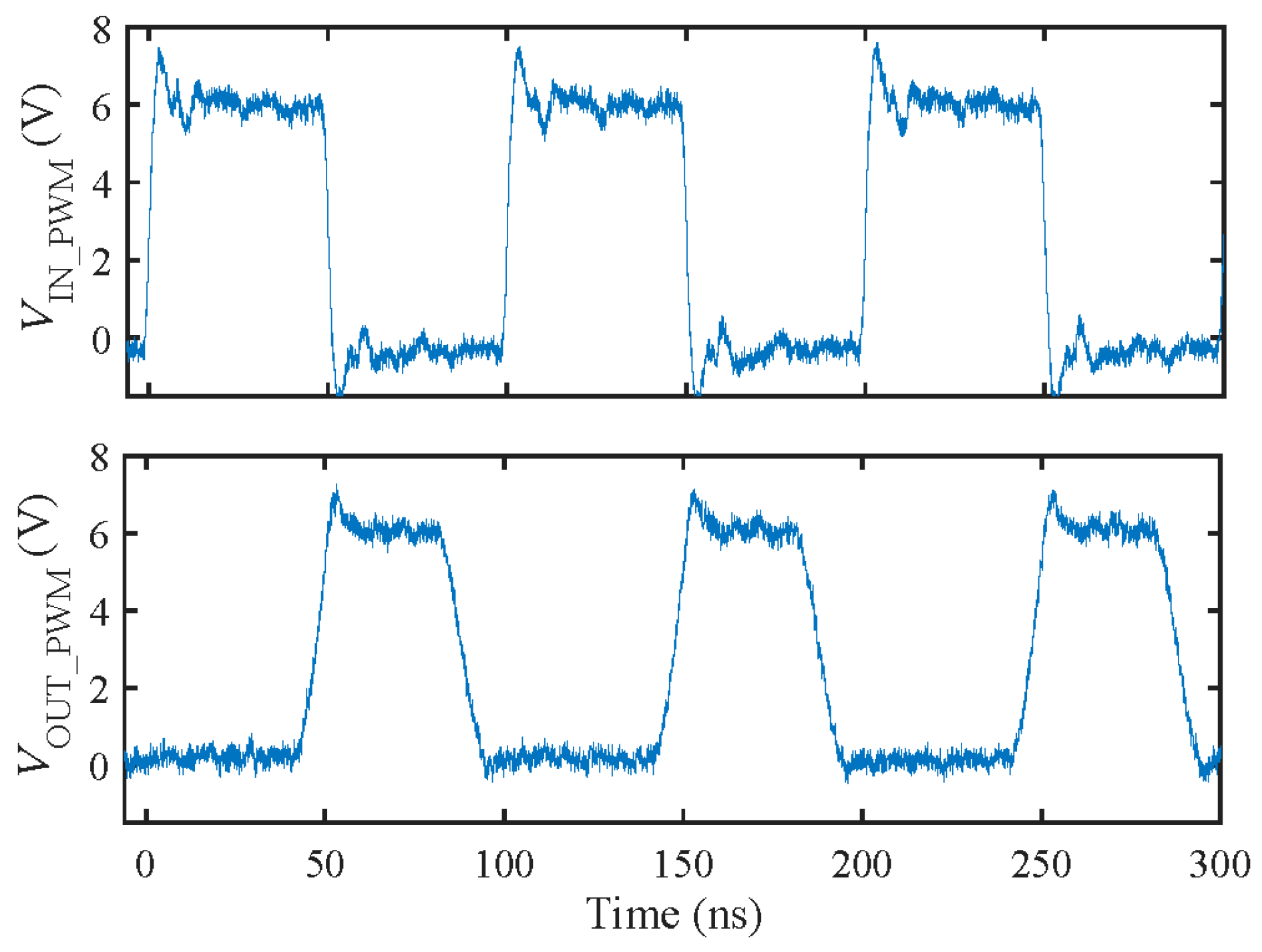

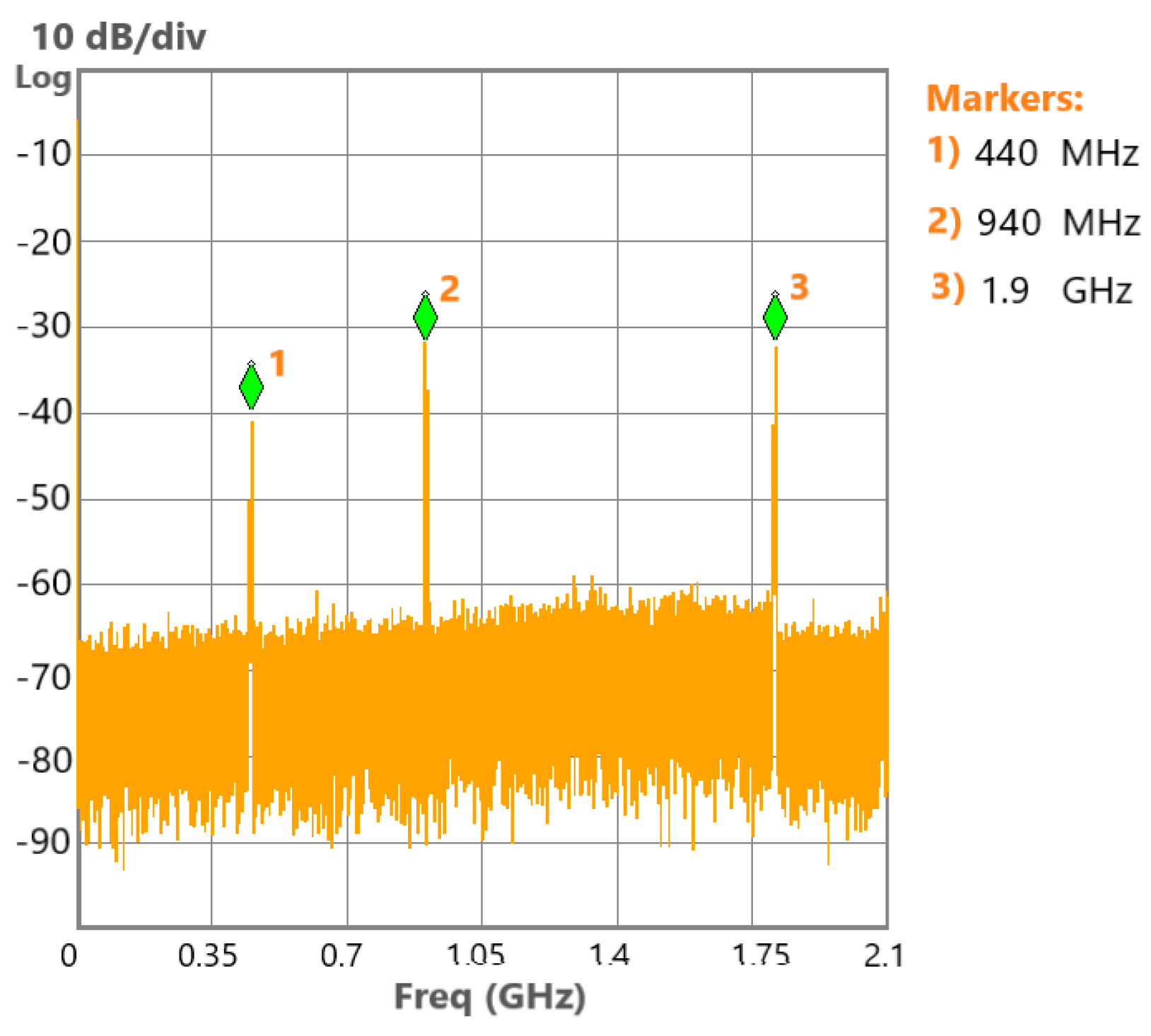

4. Duty Cycle Distortion Compensator

5. Experimental Results

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Sun, R.; Liang, Y.C.; Yeo, Y.-C.; Zhao, C.; Chen, W.; Zhang, B. All-GaN Power Integration: Devices to Functional Subcircuits and Converter ICs. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 8, 31–41. [Google Scholar] [CrossRef]

- Ikeda, N.; Niiyama, Y.; Kambayashi, H.; Sato, Y.; Nomura, T.; Kato, S.; Yoshida, S. GaN Power Transistors on Si Substrates for Switching Applications. Proc. IEEE 2010, 98, 1151–1161. [Google Scholar] [CrossRef]

- Hassan, A.; Savaria, Y.; Sawan, M. GaN Integration Technology, an Ideal Candidate for High-Temperature Applications: A Review. IEEE Access 2018, 6, 78790–78802. [Google Scholar]

- Meneghini, M.; Meneghesso, G.; Zanoni, E. (Eds.) Gallium Nitride Enabled High Frequency and High Efficiency Power Conversion, 1st ed.; Springer: Berlin/Heidelberg, Germany, 2018. [Google Scholar]

- Chen, K.J.; Haberlen, O.; Lidow, A.; Tsai, C.L.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si Power Technology: Devices and Applications. IEEE Trans. Electron Devices 2017, 64, 779–795. [Google Scholar]

- Sun, R.; Lai, J.; Chen, W.; Zhang, B. GaN Power Integration for High Frequency and High Efficiency Power Applications: A Review. IEEE Access 2020, 8, 15529–15542. [Google Scholar]

- Ke, X.; Sankman, J.; Chen, Y.; He, L.; Ma, D.B. A Tri-Slope Gate Driving GaN DC–DC Converter with Spurious Noise Compression and Ringing Suppression for Automotive Applications. IEEE J. Solid-State Circuits 2018, 53, 247–260. [Google Scholar]

- Seidel, A.; Wicht, B. Integrated Gate Drivers Based on High-Voltage Energy Storing for GaN Transistors. IEEE J. Solid-State Circuits 2018, 53, 3446–3454. [Google Scholar]

- Chen, C.-J.; Chiu, P.-K.; Chen, Y.-M.; Wang, P.-Y.; Chang, Y.-C. An Integrated Driver with Adaptive Dead-Time Control for GaN-Based Synchronous Buck Converter. IEEE Trans. Circuits Syst. II Express Briefs 2022, 69, 539–543. [Google Scholar] [CrossRef]

- Majima, H.; Ishihara, H.; Ikeuchi, K.; Ogawa, T.; Sawahara, Y.; Ogawa, T.; Takaya, S.; Onizuka, K.; Watanabe, O. Cascoded GaN half-bridge with 17 MHz wide-band galvanically isolated current sensor. Jpn. J. Appl. Phys. 2022, 61, SC1052. [Google Scholar]

- Meneghini, M.; Ronchi, N.; Stocco, A.; Meneghesso, G.; Mishra, U.K.; Pei, Y.; Zanoni, E. Investigation of Trapping and Hot-Electron Effects in GaN HEMTs by Means of a Combined Electrooptical Method. IEEE Trans. Electron Devices 2011, 58, 2996–3003. [Google Scholar]

- Sayadi, L.; Iannaccone, G.; Sicre, S.; Häberlen, O.; Curatola, G. Threshold Voltage Instability in p-GaN Gate AlGaN/GaN HFETs. IEEE Trans. Electron Devices 2018, 65, 2454–2460. [Google Scholar] [CrossRef]

- Tang, S.W.; Bakeroot, B.; Huang, Z.H.; Chen, S.C.; Lin, W.S.; Lo, T.C.; Borga, M.; Wellekens, D.; Posthuma, N.; Decoutere, S.; et al. Using Gate Leakage Conduction to Understand Positive Gate Bias Induced Threshold Voltage Shift in p-GaN Gate HEMTs. IEEE Trans. Electron Devices 2023, 70, 449–453. [Google Scholar] [CrossRef]

- Trani, R.; Catalano, A.P.; Castellazzi, A.; D’Alessandro, V. Thermal management solutions for a lightweight 3 L GaN inverter. In Proceedings of the IEEE 10th International Conference on Power Electronics and ECCE, Asia (ICPE 2019–ECCE Asia), Busan, Republic of Korea, 27–31 May 2019; pp. 2173–2178. [Google Scholar]

- Kozak, J.P.; Zhang, R.; Porter, M.; Song, Q.; Liu, J.; Wang, B.; Wang, R.; Saito, W.; Zhang, Y. Stability, Reliability, and Robustness of GaN Power Devices: A Review. IEEE Trans. Power Electron. 2023, 38, 8442–8471. [Google Scholar] [CrossRef]

- Wong, K.-Y.; Chen, W.; Chen, K.J. Integrated Voltage Reference Generator for GaN Smart Power Chip Technology. IEEE Trans. Electron Devices 2010, 57, 952–955. [Google Scholar] [CrossRef]

- Liu, X.; Chen, K.J. GaN Single-Polarity Power Supply Bootstrapped Comparator for High-Temperature Electronics. IEEE Electron Device Lett. 2011, 32, 27–29. [Google Scholar] [CrossRef]

- Hong, Y.-P.; Mukai, K.; Gheidi, H.; Shinjo, S.; Asbeck, P.M. High efficiency GaN switching converter IC with bootstrap driver for envelope tracking applications. In Proceedings of the 2013 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Seattle, WA, USA, 2–4 June 2013. [Google Scholar]

- Wang, H.; Kwan, A.M.H.; Jiang, Q.; Chen, K.J. A GaN Pulse Width Modulation Integrated Circuit for GaN Power Converters. IEEE Trans. Electron Devices 2015, 62, 1143–1149. [Google Scholar]

- Zhang, Y.; Rodríguez, M.; Maksimović, D. Very High Frequency PWM Buck Converters Using Monolithic GaN Half-Bridge Power Stages with Integrated Gate Drivers. IEEE Trans. Power Electron. 2016, 31, 7926–7942. [Google Scholar]

- Tang, G.; Kwan, A.M.H.; Wong, R.K.Y.; Lei, J.; Su, R.Y.; Yao, F.W.; Lin, Y.M.; Yu, J.L.; Tsai, T.; Tuan, H.C.; et al. Digital Integrated Circuits on an E-Mode GaN Power HEMT Platform. IEEE Electron Device Lett. 2017, 38, 1282–1285. [Google Scholar] [CrossRef]

- Zhu, M.; Matioli, E. Monolithic integration of GaN-based NMOS digital logic gate circuits with E-mode power GaN MOSHEMTs. In Proceedings of the IEEE 30th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 236–239. [Google Scholar]

- Li, X.; Geens, K.; Guo, W.; You, S.; Zhao, M.; Fahle, D.; Odnoblyudov, V.; Groeseneken, G.; Decoutere, S. Demonstration of GaN Integrated Half-Bridge with On-Chip Drivers on 200-mm Engineered Substrates. IEEE Electron Device Lett. 2019, 40, 1499–1502. [Google Scholar] [CrossRef]

- Pennisi, S.; Pulvirenti, F.; Samperi, K. Frequency compensation scheme for a full GaN OpAmp driving 1-nF load. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Austin, TX, USA, 27 May–1 June 2022; pp. 2042–2046. [Google Scholar]

- Catalano, A.P.; Scognamillo, C.; d’Alessandro, V.; Codecasa, L. In-Situ Extraction of the Thermal Impedance of GaN Power HEMTs Embedded in PCB-based Power Circuits. In Proceedings of the IEEE 35th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Hong Kong, China, 28 May–1 June 2023; pp. 310–313. [Google Scholar]

- Yan, D.; Ma, D.B. A Monolithic GaN Power IC with On-Chip Gate Driving, Level Shifting, and Temperature Sensing, Achieving Direct 48-V/1-V DC–DC Conversion. IEEE J. Solid-State Circuits 2022, 57, 3865–3876. [Google Scholar] [CrossRef]

- Li, A.; Shen, Y.; Li, Z.; Li, F.; Sun, R.; Mitrovic, I.Z.; Wen, H.; Lam, S.; Liu, W. A 4-Transistor Monolithic Solution to Highly Linear On-Chip Temperature Sensing in GaN Power Integrated Circuits. IEEE Electron Device Lett. 2023, 44, 333–336. [Google Scholar]

- Pan, C.; Yu, X.; Li, F.; Gong, H.; Wang, D.; Zhou, J.; Li, Z.; Liu, W.; Chen, D.; Gu, S.; et al. Monolithically Integrated Logic Circuits Based on p-NiO Gated E-Mode GaN HEMTs. IEEE Electron Device Lett. 2024, 45, 164–167. [Google Scholar]

- Analog Devices. Surging Across the Barrier: Digital Isolators Set the Standard for Reinforced Insulation. Available online: https://www.analog.com (accessed on 8 January 2025).

- NVE Corporation, Isolator High Voltage Safety Standards. Available online: https://www.nve.com (accessed on 6 February 2025).

- Chen, B. Fully integrated isolated dc-dc converter using micro-transformers. In Proceedings of the IEEE Applied Power Electronics Conference and Exposition, (APEC), Austin, TX, USA, 24–28 February 2008; pp. 335–338. [Google Scholar]

- Lombardo, P.; Fiore, V.; Ragonese, E.; Palmisano, G. A fully integrated half-duplex data/power transfer system with up to 40 Mbps data rate, 23 mW output power and on-chip 5 kV galvanic isolation. In Proceedings of the IEEE International Solid-State Circuits Conference: Digest of Technical Papers, San Francisco, CA, USA, 31 January–4 February 2016; pp. 300–301. [Google Scholar]

- Shi, G.; Yan, R.; Xi, J.; He, L.; Ding, W.; Pan, W.; Liu, Z.; Yang, F.; Chen, D. A compact 6 ns propagation delay 200 Mbps 100 kV/μs CMR capacitively coupled direction configurable 4-channel digital isolator in standard CMOS. In Proceedings of the IEEE International Conference on Electronics, Circuits and Systems, Bordeaux, France, 9–12 December 2018; pp. 721–724. [Google Scholar]

- Fiore, V.; Ragonese, E.; Palmisano, G. A fully integrated watt-level power transfer system with on-chip galvanic isolation in silicon technology. IEEE Trans. Power Electron. 2017, 32, 1984–1995. [Google Scholar]

- Zhuo, Y.; Ma, S.; Zhao, T.; Qin, W.; Zhao, Y.; Guo, Y.; Yan, H.; Chen, B. A 52% Peak Efficiency > 1-W Isolated Power Transfer System Using Fully Integrated Transformer with Magnetic Core. IEEE J. Solid-State Circuits 2019, 54, 3326–3335. [Google Scholar]

- Greco, N.; Parisi, A.; Lombardo, P.; Spina, N.; Ragonese, E.; Palmisano, G. A double-isolated DC-DC converter based on integrated LC resonant barriers. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 4423–4433. [Google Scholar]

- Ragonese, E.; Spina, N.; Castorina, A.; Lombardo, P.; Greco, N.; Parisi, A.; Palmisano, G. A fully integrated galvanically isolated DC-DC converter with data communication. IEEE Trans. Circuits Syst. I Regul. Pap. 2018, 65, 1432–1441. [Google Scholar]

- Parisi, A.; Ragonese, E.; Spina, N.; Palmisano, G. Galvanically isolated DC-DC converter using a single isolation transformer for multi-channel communication. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 4434–4444. [Google Scholar]

- Uchida, S.; Kaeriyama, S.; Nagase, H.; Takeda, K.; Nakashiba, Y.; Maeda, T.; Ishihara, K. A face-to-face chip stacking 7 kV RMS digital isolator for automotive and industrial motor drive applications. In Proceedings of the IEEE 26th International Symposium on Power Semiconductor Devices IC’s (ISPSD), Waikoloa, HI, USA, 15–19 June 2014; pp. 442–445. [Google Scholar]

- Renna, C.M.-A.; Scuderi, A.; Magro, C.; Spina, N.; Ragonese, E.; Marano, B.; Palmisano, G. Microstructure Device Comprising a Face to Face Electromagnetic Near Field Coupling Between Stacked Device Portions and Method of Forming the Device. U.S. Patent 9018730 B2, April 2015. [Google Scholar]

- Spina, N.; Girlando, G.; Smerzi, S.A.; Palmisano, G. Integrated Galvanic Isolator Using Wireless Transmission. U.S. Patent 8364195 B2, 28 January 2013. [Google Scholar]

- Mukherjee, S.; Bhat, A.N.; Shrivastava, K.A.; Bonu, M.; Sutton, B.; Gopinathan, V.; Thiagarajan, G.; Patki, A.; Malakar, J.; Krishnapura, N. A 500 Mb/s 200 pJ/b Die-to-Die Bidirectional Link with 24 kV Surge Isolation and 50 kV/μs CMR using Resonant Inductive Coupling in 0.18 μm CMOS. In Proceedings of the IEEE International Solid-State Circuits Conference: Digest of Technical Papers, San Francisco, CA, USA, 5–9 February 2017; pp. 434–435. [Google Scholar]

- Ragonese, E.; Spina, N.; Parisi, A.; Palmisano, G. A CMOS data transfer system based on planar RF coupling for reinforced galvanic isolation with 25-kV surge voltage and 250-kV/µs CMTI. Electronics 2020, 9, 943. [Google Scholar] [CrossRef]

- Ragonese, E.; Parisi, A.; Spina, N.; Palmisano, G. Compact galvanically isolated architectures for low-power dc-dc converters with data transmission. Electronics 2021, 10, 2328. [Google Scholar] [CrossRef]

- Spina, N.; Raimondi, M.; Castorina, A.; Ragonese, E.; Palmisano, G. A 3-Channel Package-Scale Galvanic Isolation Interface for Wide Bandgap Gate Drivers. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2024, 32, 1389–1399. [Google Scholar] [CrossRef]

- Spina, N.; Samperi, K.; Pavlin, A.; Pennisi, S.; Palmisano, G. Fully Integrated Galvanic Isolation Interface in GaN Technology. IEEE Trans. Circuits Syst. I Regul. Pap. 2023, 70, 4605–4614. [Google Scholar] [CrossRef]

- Samperi, K.; Spina, N.; Pennisi, S.; Palmisano, G. Integrated GaN digital soft start-up for switching power converters. In Proceedings of the 18th Conference on Ph.D Research in Microelectronics and Electronics (PRIME), Valencia, Spain, 18–21 June 2023; pp. 193–196. [Google Scholar]

- Samperi, K.; Spina, N.; Castorina, A.; Pavlin, A.; Pennisi, S.; Palmisano, G. GaN Monolithic PWM Generator with Dynamic Offset Compensation. IEEE Access 2023, 11, 126892–126899. [Google Scholar] [CrossRef]

- Samperi, K.; Pennisi, S.; Pulvirenti, F. High-Speed all-GaN Gate Driver with reduced power consumption. In Proceedings of the 21st IEEE Interregional NEWCAS Conference (NEWCAS), Edinburgh, UK, 26–28 June 2023; pp. 1–5. [Google Scholar]

- ADuM4221, Isolated, Half Bridge Gate Drivers with Adjustable Dead Time, 4 A Output, Analog Devices, Norwood, MA, USA [Online]. Available online: https://www.analog.com/en/index.html (accessed on 8 January 2025).

- UCC2154x Reinforced Isolation Dual-Channel Gate Driver with 3.3-mm Channel-to-Channel Spacing Option, Texas Instruments, Dallas, TX, USA. Available online: https://www.ti.com/lit/ds/symlink/ucc21542.pdf?ts=1663549023521 (accessed on 8 January 2025).

| Parameters | [42] | [45] | [46] | [50] | [51] | This Work |

|---|---|---|---|---|---|---|

| Application | n.a. | Gate drivers | Gate drivers | Gate drivers | Gate drivers | Gate drivers |

| No of isolation channels | 2 | 3 | 2 | 2 | 2 | 3 |

| Max rate | 500 Mbit/s | 0.4 MHz (1) 15 MHz (2) | 2 MHz (1) | 1 MHz | 1 MHz | 2 MHz (1) 10 MHz (2) |

| Propagation delay [ns] | n.a. | 34 | 30 | 44 | 28 | 40 |

| PWM distortion [ns] | n.a. | n.a | 18 | n.a. | 6.5 | 10 |

| Isolation technology | Chip-to-chip RF communication | Chip-to-chip RF communication | Chip-to-chip RF communication | Polyimide transformers | On-chip SiO2 capacitors | Chip-to-chip RF communication |

| Isolation level | Reinforced (>10 kVPK) | Reinforced (>10 kVPK) (3) | Reinforced (>10 kVPK) (3) | Basic (5.7 VRMS) | Reinforced (8 kVPK) | Reinforced (>10 kVPK) (3) |

| CMTI [kV/μs] | 50 | n.a. (4) | n.a. (4) | 150 | 100 | n.a. (4) |

| Supply voltage [V] | 1.8 | 3 | 6 | 5 | 3/5.5 | 6 |

| Technology | 0.18 µm CMOS | 0.32 μm BCD | 0.5 μm GaN on Si | n.a. | n.a. | 0.5 μm GaN on Si |

| No. of dice | 2 | 2 | 2 | 2 | 3 | 2 |

| Area [mm2] | n.a. | 11.6 | 5.8 | n.a. | n.a. | 8.7 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Samperi, K.; Spina, N.; Castorina, A.; Palmisano, G. Three-Channel Fully Integrated Galvanic Isolation Interface in GaN Technology. Electronics 2025, 14, 1403. https://doi.org/10.3390/electronics14071403

Samperi K, Spina N, Castorina A, Palmisano G. Three-Channel Fully Integrated Galvanic Isolation Interface in GaN Technology. Electronics. 2025; 14(7):1403. https://doi.org/10.3390/electronics14071403

Chicago/Turabian StyleSamperi, Katia, Nunzio Spina, Alessandro Castorina, and Giuseppe Palmisano. 2025. "Three-Channel Fully Integrated Galvanic Isolation Interface in GaN Technology" Electronics 14, no. 7: 1403. https://doi.org/10.3390/electronics14071403

APA StyleSamperi, K., Spina, N., Castorina, A., & Palmisano, G. (2025). Three-Channel Fully Integrated Galvanic Isolation Interface in GaN Technology. Electronics, 14(7), 1403. https://doi.org/10.3390/electronics14071403