Investigation of the Effect of Gate Oxide Screening with Adjustment Pulse on Commercial SiC Power MOSFETs

Abstract

1. Introduction

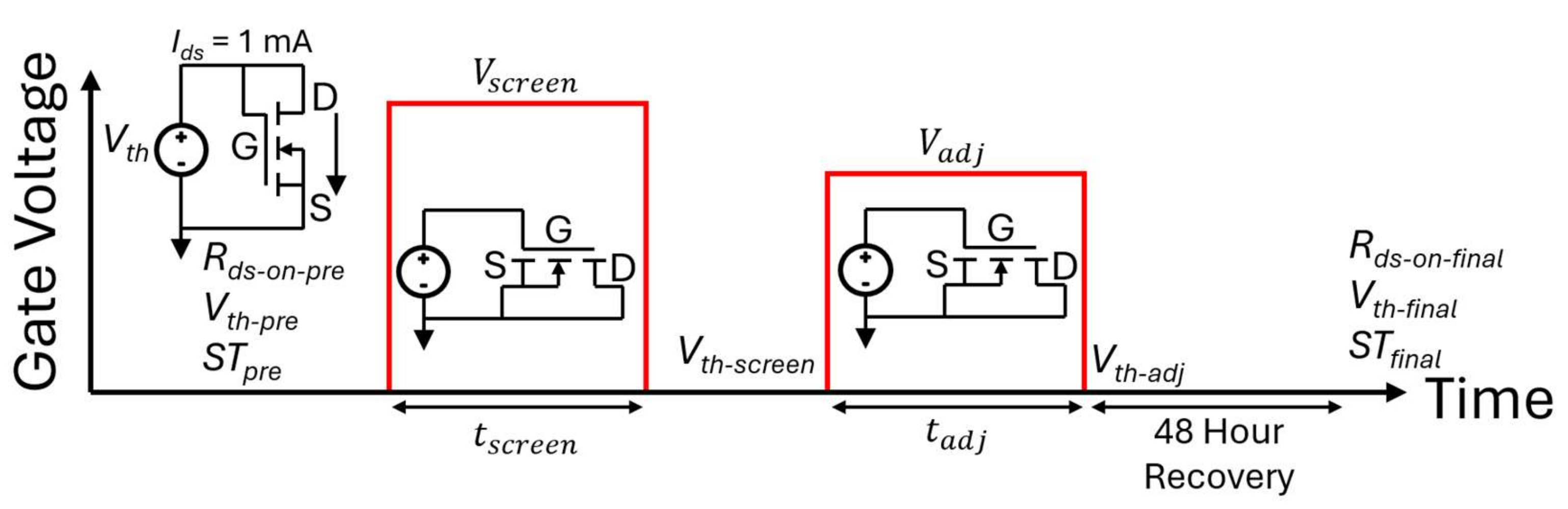

2. Materials and Methods

3. Results

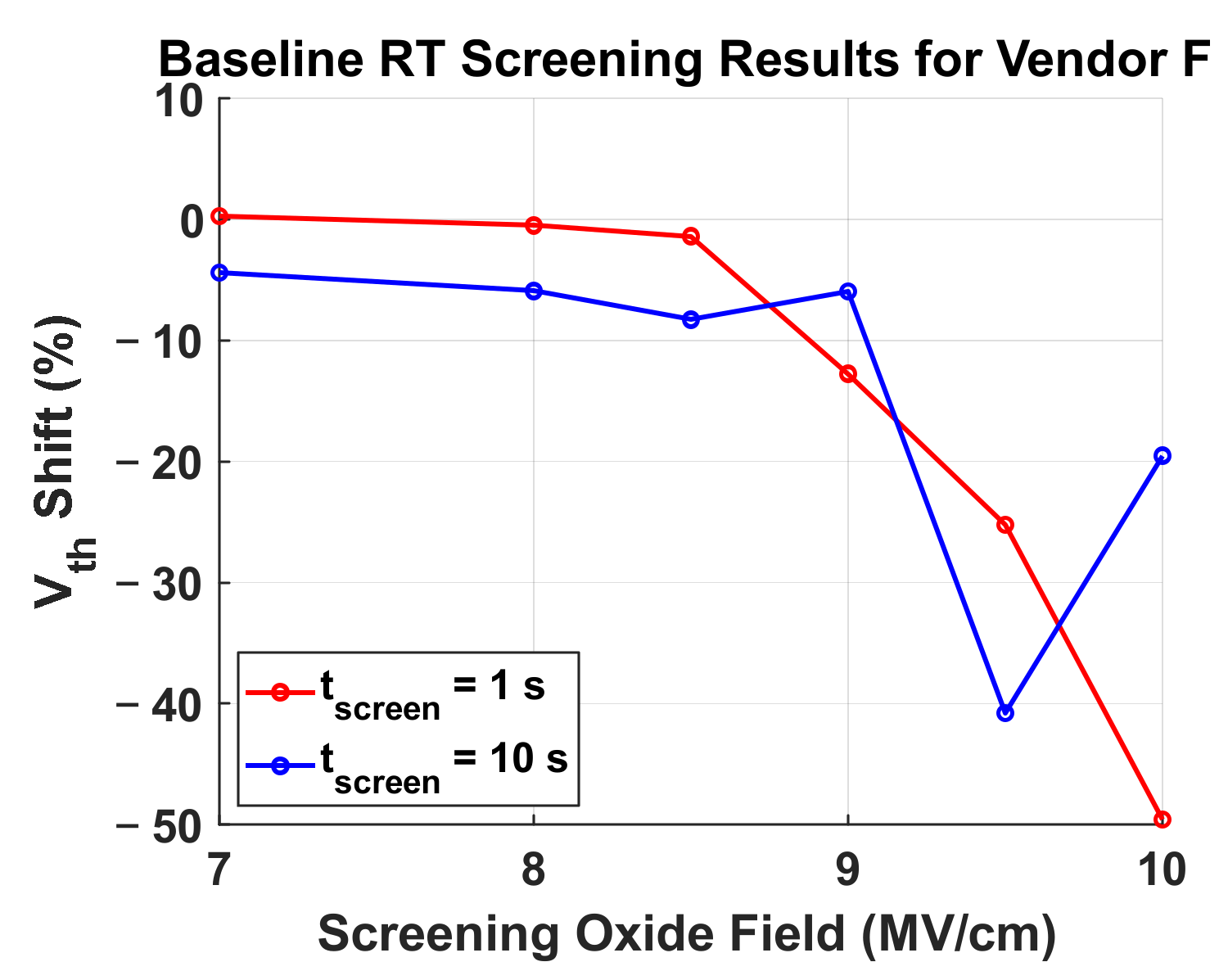

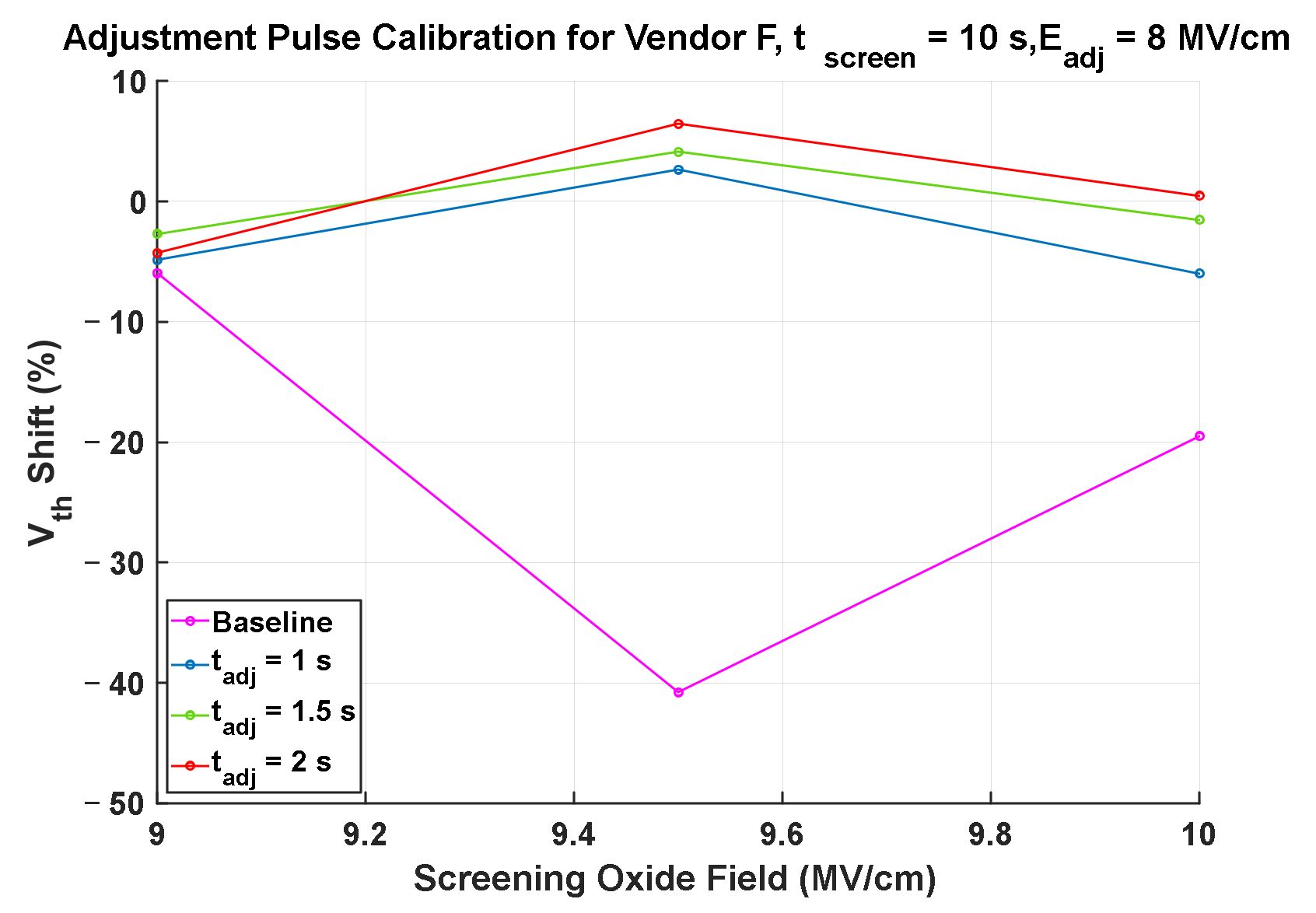

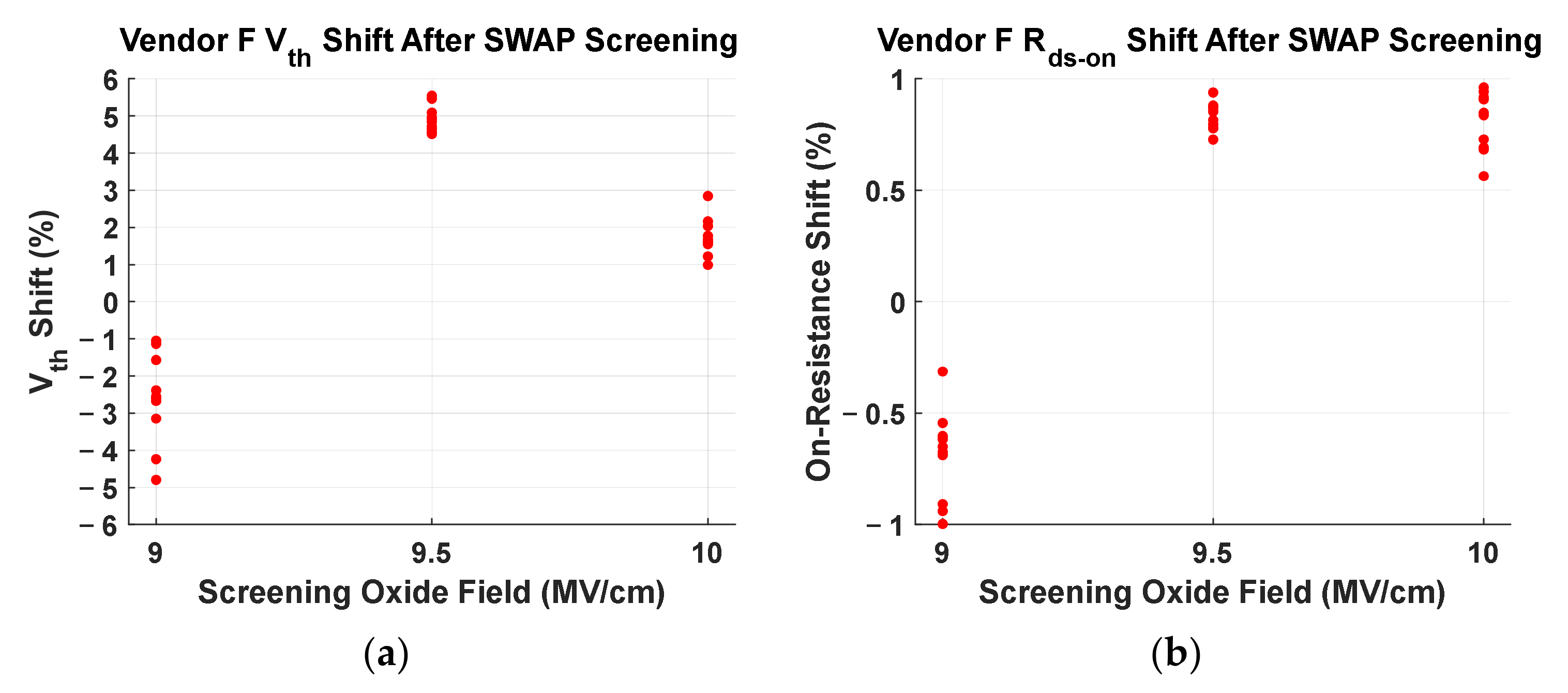

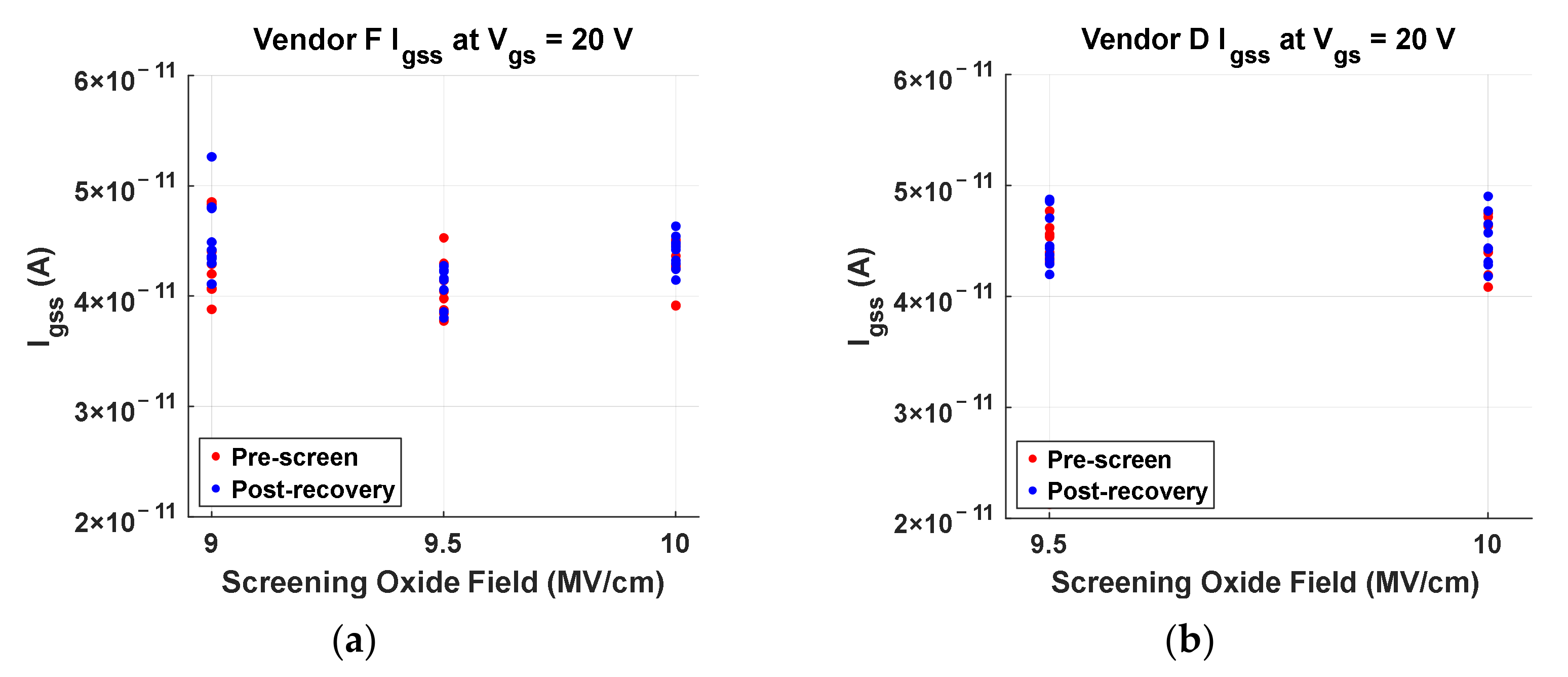

3.1. Calibration and Results for Vendor F1

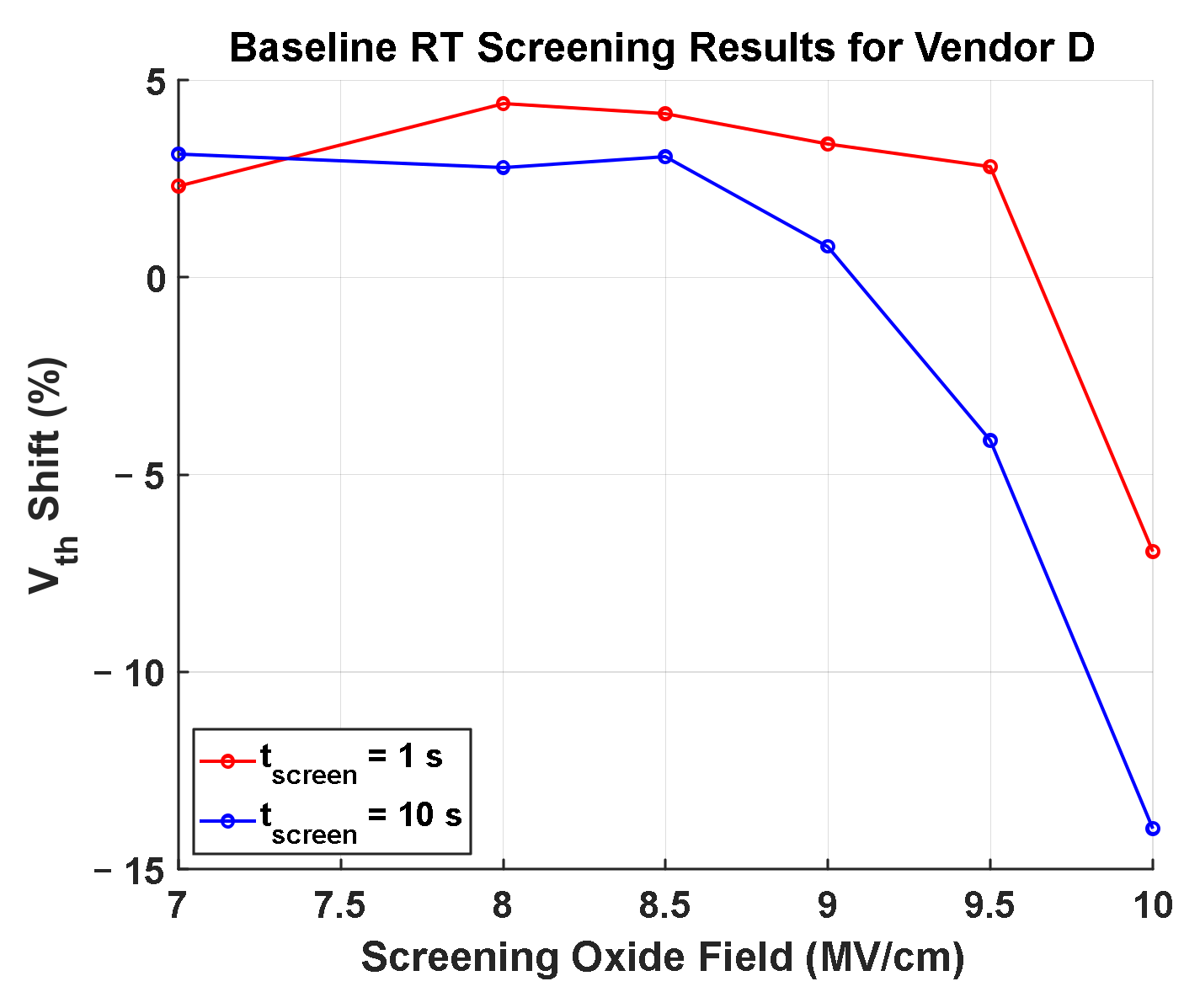

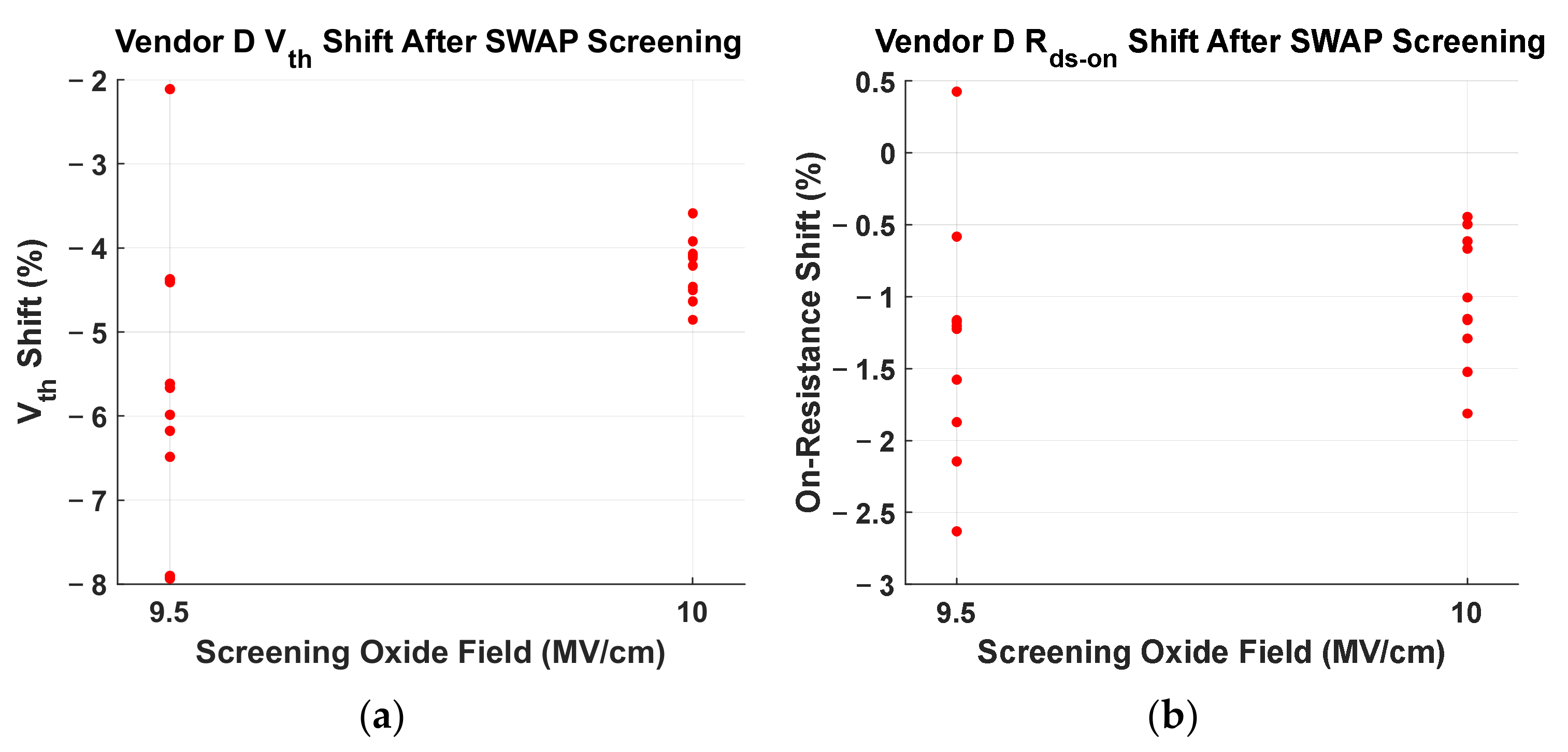

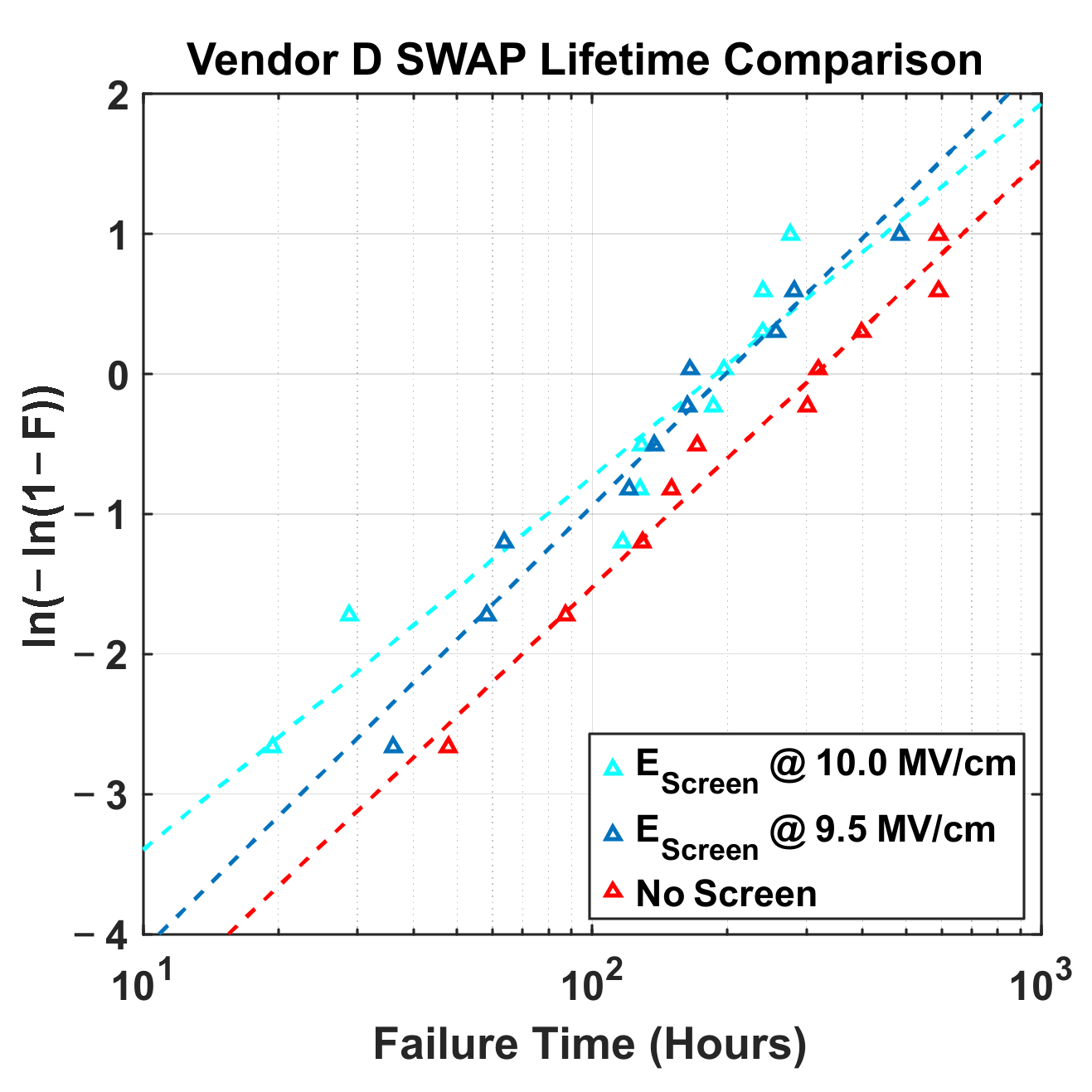

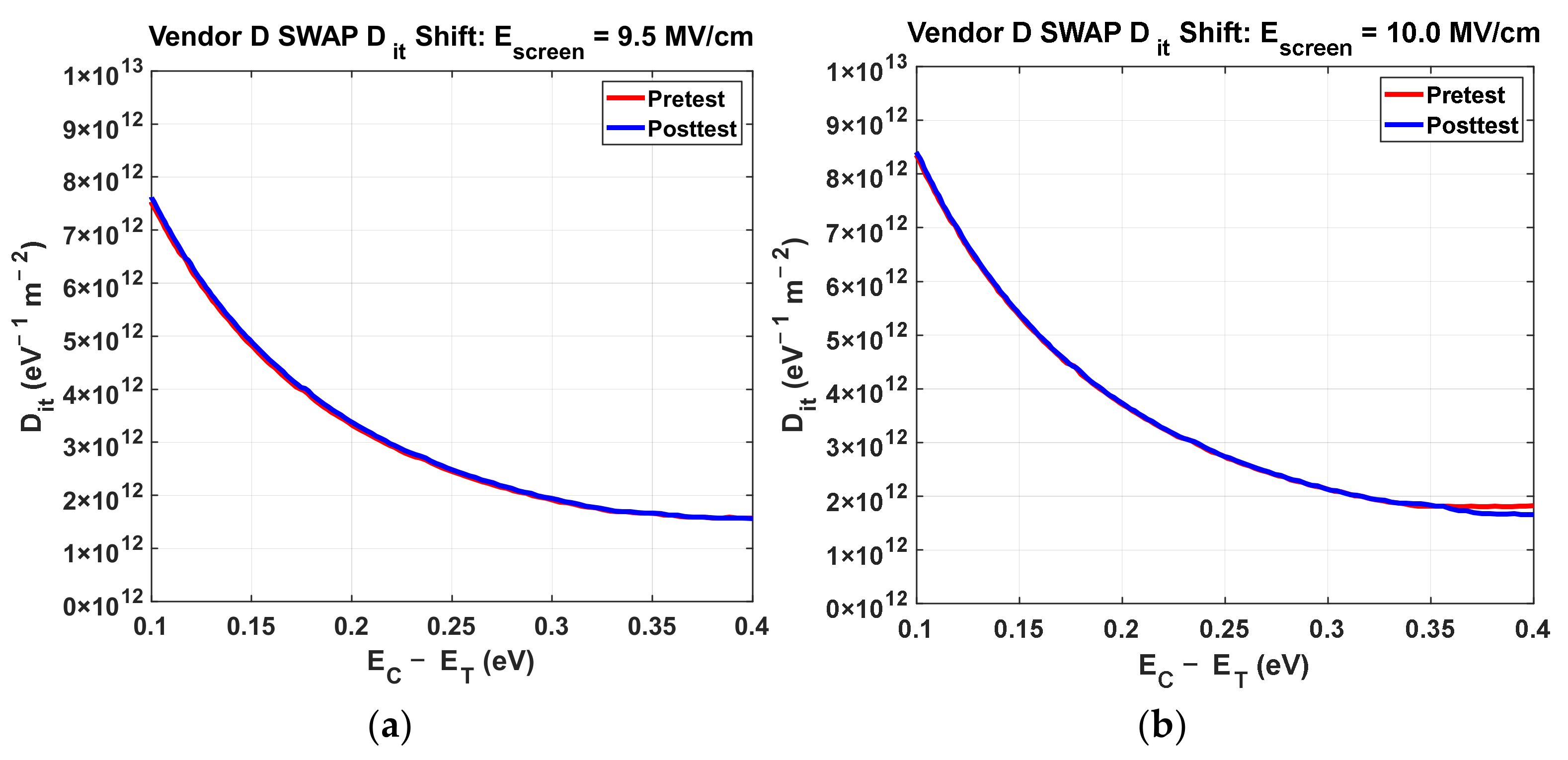

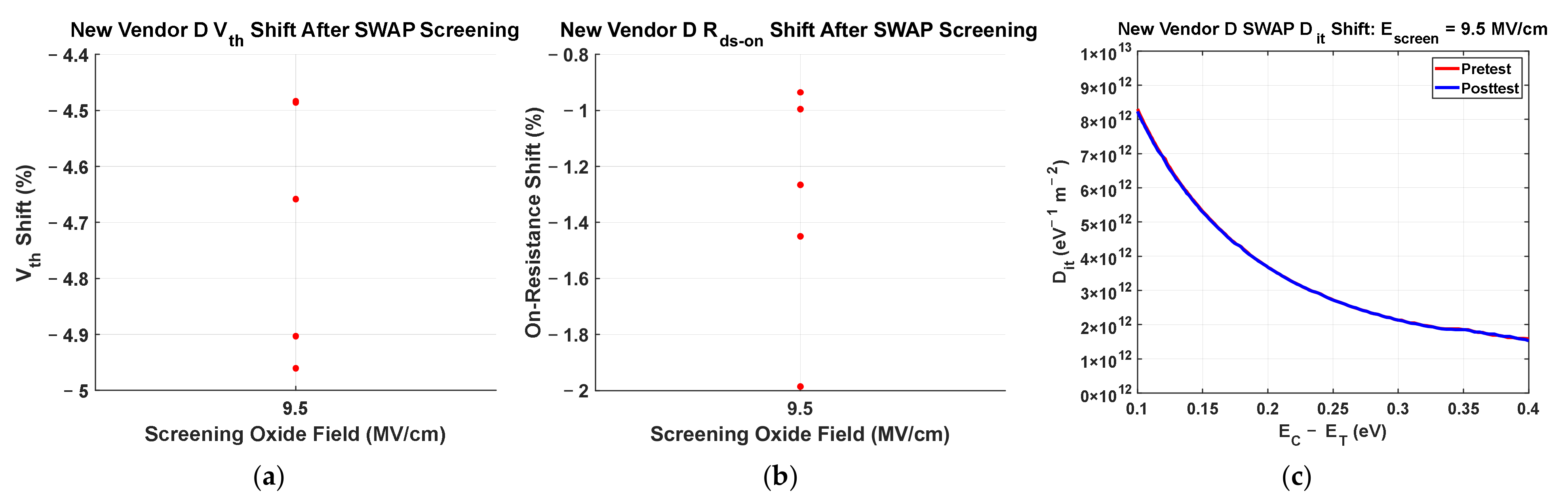

3.2. Results for Vendor D

3.3. Results for Vendor B

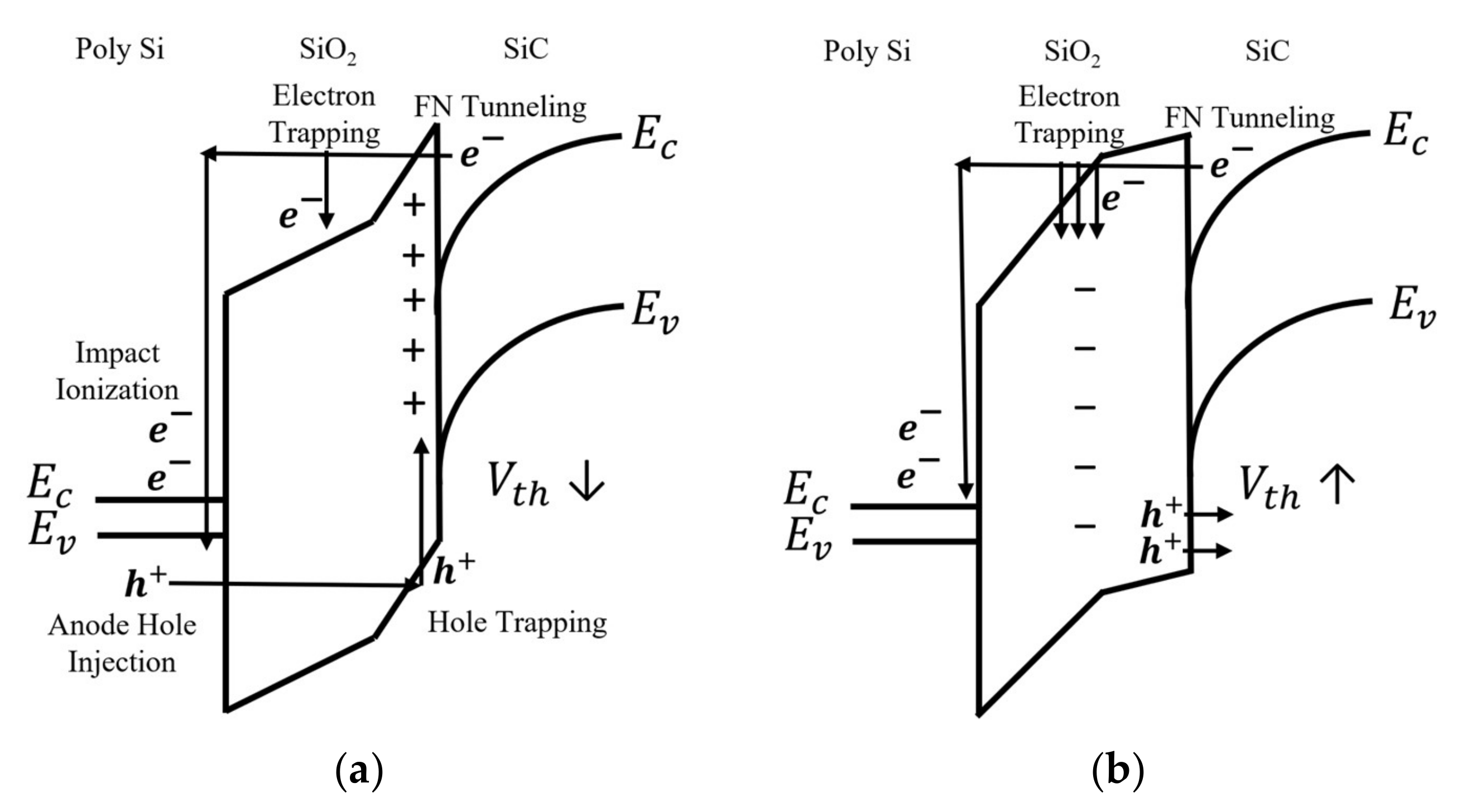

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

Abbreviations

| SWAP | Screening With Adjustment Pulse |

| TDDB | Time Dependent Dielectric Breakdown |

| MOSFET | Metal-Oxide-Semiconductor Field Effect Transistor |

| SiC | Silicon Carbide |

| DUT | Device Under Test |

References

- Tsunenobu, K.; James, A.C. Physical Properties of Silicon Carbide. In Fundamentals of Silicon Carbide Technology: Growth, Characterization, Devices and Applications; Wiley-IEEE: Piscataway, NJ, USA, 2014; pp. 11–38. [Google Scholar]

- Hamada, K.; Nagao, M.; Ajioka, M.; Kawai, F. SiC—Emerging Power Device Technology for Next-Generation Electrically Powered Environmentally Friendly Vehicles. IEEE Trans. Electron Devices 2015, 62, 278–285. [Google Scholar] [CrossRef]

- Tan, C.; Stecca, M.; Soeiro, T.B.; Dong, J.; Bauer, P. Performance Evaluation of an Electric Vehicle Traction Drive Using Si/SiC Hybrid Switches. In Proceedings of the 2021 IEEE 19th International Power Electronics and Motion Control Conference (PEMC), Gliwice, Poland, 25–29 April 2021; pp. 278–283. [Google Scholar]

- Wang, J.; Jiang, X. Review and analysis of SiC MOSFETs’ ruggedness and reliability. IET Power Electron. 2020, 13, 445–455. [Google Scholar] [CrossRef]

- Liu, T.; Zhu, S.; White, M.H.; Salemi, A.; Sheridan, D.; Agarwal, A.K. Time-Dependent Dielectric Breakdown of Commercial 1.2 kV 4H-SiC Power MOSFETs. IEEE J. Electron Devices Soc. 2021, 9, 633–639. [Google Scholar] [CrossRef]

- Aichinger, T.; Schmidt, M. Gate-oxide reliability and failure-rate reduction of industrial SiC MOSFETs. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; pp. 1–6. [Google Scholar]

- Cheung, K.P. SiC power MOSFET gate oxide breakdown reliability—Current status. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. 2B.3-1–2B.3-5. [Google Scholar]

- Zheng, Y.; Potera, R.; Witt, T. Characterization of Early Breakdown of SiC MOSFET Gate Oxide by Voltage Ramp Tests. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021; pp. 1–5. [Google Scholar]

- Beier-Moebius, M.; Lutz, J. Breakdown of gate oxide of 1.2 kV SiC-MOSFETs under high temperature and high gate voltage. In Proceedings of the PCIM Europe 2016, International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, Nuremberg, Germany, 10–12 May 2016; pp. 1–8. [Google Scholar]

- Lee, J.C.; Chen, I.-C.; Hu, C. Modeling and characterization of gate oxide reliability. IEEE Trans. Electron Devices 1988, 35, 2268–2278. [Google Scholar] [CrossRef]

- Jin, M.; Bhattacharya, M.; Shi, L.; Qian, J.; Houshmand, S.; Yu, H.; White, M.H.; Agarwal, A.K.; Liu, T.; Zhu, S.; et al. Threshold Voltage Adjustment of Commercial SiC MOSFETs During Gate Oxide Screening by Low Field Pulse. In Proceedings of the 2024 IEEE 11th Workshop on Wide Bandgap Power Devices & Applications (WiPDA), Dayton, OH, USA, 4–6 November 2024; pp. 1–5. [Google Scholar]

- Berens, J.; Aichinger, T. A Straightforward Electrical Method to Determine Screening Capability of GOX Extrinsics in Arbitrary, Commercially Available SiC MOSFETs. In Proceedings of the 2021 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 21–25 March 2021; pp. 1–5. [Google Scholar]

- Miki, H.; Sagawa, M.; Mori, Y.; Murata, T.; Kinoshita, K.; Asaka, K.; Oda, T. Accurate Screening of Defective Oxide on SiC Using Consecutive Multiple Threshold—Voltage Measurements. In Proceedings of the 2022 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 27–31 March 2022; pp. 8B.2-1–8B.2-7. [Google Scholar]

- Shi, L.; Zhu, S.; Qian, J.; Jin, M.; Bhattacharya, M.; White, M.H.; Agarwal, A.K.; Shimbori, A.; Liu, T. Investigation of different Screening Methods on Threshold Voltage and Gate Oxide Lifetime of SiC Power MOSFETs. In Proceedings of the 2023 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 26–30 March 2023; pp. 1–7. [Google Scholar]

- Maaß, S.; Reisinger, H.; Aichinger, T.; Rescher, G. Influence of High-Voltage Gate-Oxide Pulses on the BTI Behavior of SiC MOSFETs. In Proceedings of the 2020 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 28 April–30 May 2020; pp. 1–6. [Google Scholar]

- Noguchi, M.; Koyama, A.; Iwamatsu, T.; Amishiro, H.; Watanabe, H.; Miura, N. Gate Oxide Instability and Lifetime in SiC MOSFETs under a Wide Range of Positive Electric Field Stress. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–18 December 2020; pp. 23.24.21–23.24.24. [Google Scholar]

- Yu, S.; White, M.H.; Agarwal, A.K. Experimental Determination of Interface Trap Density and Fixed Positive Oxide Charge in Commercial 4H-SiC Power MOSFETs. IEEE Access 2021, 9, 149118–149124. [Google Scholar] [CrossRef]

- Asllani, B.; Castellazzi, A.; Salvado, O.A.; Fayyaz, A.; Morel, H.; Planson, D. VTH-Hysteresis and Interface States Characterisation in SiC Power MOSFETs with Planar and Trench Gate. In Proceedings of the 2019 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 31 March–4 April 2019; pp. 1–6. [Google Scholar]

- Berens, J.; Rasinger, F.; Aichinger, T.; Heuken, M.; Krieger, M.; Pobegen, G. Detection and Cryogenic Characterization of Defects at the SiO2/4H-SiC Interface in Trench MOSFET. IEEE Trans. Electron Devices 2019, 66, 1213–1217. [Google Scholar] [CrossRef]

- Tian, K.; Hallén, A.; Qi, J.; Nawaz, M.; Ma, S.; Wang, M.; Guo, S.; Elgammal, K.; Li, A.; Liu, W. Comprehensive Characterization of the 4H-SiC Planar and Trench Gate MOSFETs From Cryogenic to High Temperature. IEEE Trans. Electron Devices 2019, 66, 4279–4286. [Google Scholar] [CrossRef]

- Lelis, A.J.; Green, R.; Habersat, D.B. SiC MOSFET reliability and implications for qualification testing. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; pp. 2A-4.1–2A-4.4. [Google Scholar]

- Rescher, G.; Pobegen, G.; Grasser, T. Threshold Voltage Instabilities of Present SiC-Power MOSFETs under Positive Bias Temperature Stress. Mater. Sci. Forum 2016, 858, 481–484. [Google Scholar] [CrossRef]

- Ouaida, R.; Berthou, M.; León, J.; Perpiñà, X.; Oge, S.; Brosselard, P.; Joubert, C. Gate Oxide Degradation of SiC MOSFET in Switching Conditions. IEEE Electron Device Lett. 2014, 35, 1284–1286. [Google Scholar] [CrossRef]

- Chbili, Z.; Matsuda, A.; Chbili, J.; Ryan, J.T.; Campbell, J.P.; Lahbabi, M.; Ioannou, D.E.; Cheung, K.P. Modeling Early Breakdown Failures of Gate Oxide in SiC Power MOSFETs. IEEE Trans. Electron Devices 2016, 63, 3605–3613. [Google Scholar] [CrossRef]

| Vendor | Vendor F | Vendor D | Vendor B |

|---|---|---|---|

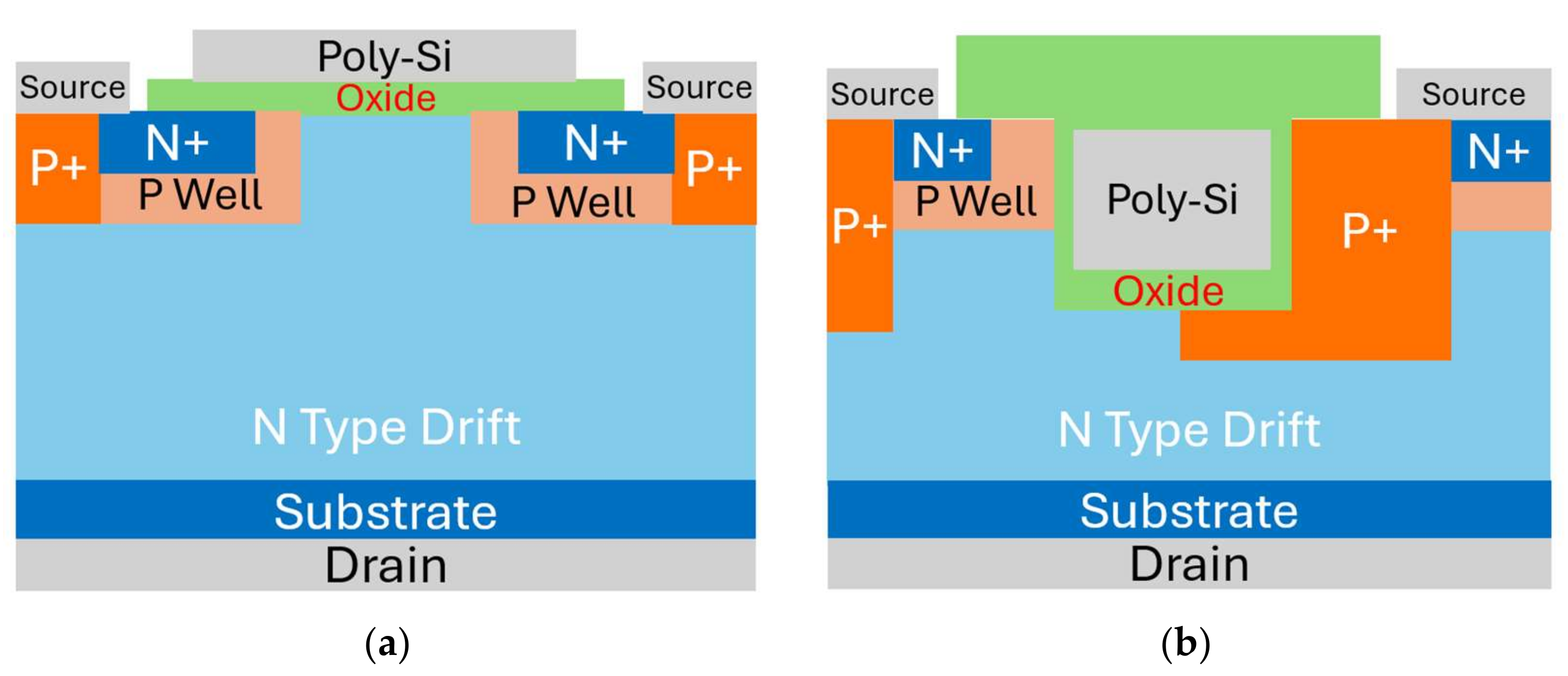

| Structure | Planar | Planar | Asymmetric Trench |

| Voltage Rating | 1200 V | 1200 V | 1200 V |

| Current Rating | 7.6 A | 20 A | 4.7 A |

| Average Oxide Vbr @ 150 °C | 42 V | 54.3 V | 62.8 V |

| Estimated tox | 38.2 nm | 49.4 nm | 57.1 nm |

| Escreen (MV/cm) | tscreen (s) | Eadj (MV/cm) | tadj (s) |

|---|---|---|---|

| 9 | 10 | 8 | 2 |

| 9.5 | 10 | 8 | 2 |

| 10 | 10 | 8 | 2 |

| Escreen (MV/cm) | tscreen (s) | Eadj (MV/cm) | tadj (s) |

|---|---|---|---|

| 9.5 | 10 | 8 | 5 |

| 10 | 10 | 8.5 | 200 |

| Escreen (MV/cm) | tscreen (s) | Eadj (MV/cm) | tadj (s) |

|---|---|---|---|

| 9.5 | 5 | 8 | 2 |

| Escreen (MV/cm) | tscreen (s) | Eadj (MV/cm) | tadj (s) | ΔVth (%) |

|---|---|---|---|---|

| 8.5 | 10 | 8 | 2 | −7.7 |

| 8.5 | 10 | 8 | 4 | −8.4 |

| 9 | 10 | 8 | 2 | −44 |

| 9 | 10 | 8 | 10 | −37 |

| 9 | 5 | 8 | 10 | −27 |

| 9 | 5 | 7.5 | 10 | −30 |

| 9.5 | 10 | 8 | 2 | −32 |

| 9.5 | 1 | 8 | 10 | −42 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jin, M.; Bhattacharya, M.; Yu, H.; Qian, J.; Houshmand, S.; Shimbori, A.; White, M.H.; Agarwal, A.K. Investigation of the Effect of Gate Oxide Screening with Adjustment Pulse on Commercial SiC Power MOSFETs. Electronics 2025, 14, 1366. https://doi.org/10.3390/electronics14071366

Jin M, Bhattacharya M, Yu H, Qian J, Houshmand S, Shimbori A, White MH, Agarwal AK. Investigation of the Effect of Gate Oxide Screening with Adjustment Pulse on Commercial SiC Power MOSFETs. Electronics. 2025; 14(7):1366. https://doi.org/10.3390/electronics14071366

Chicago/Turabian StyleJin, Michael, Monikuntala Bhattacharya, Hengyu Yu, Jiashu Qian, Shiva Houshmand, Atsushi Shimbori, Marvin H. White, and Anant K. Agarwal. 2025. "Investigation of the Effect of Gate Oxide Screening with Adjustment Pulse on Commercial SiC Power MOSFETs" Electronics 14, no. 7: 1366. https://doi.org/10.3390/electronics14071366

APA StyleJin, M., Bhattacharya, M., Yu, H., Qian, J., Houshmand, S., Shimbori, A., White, M. H., & Agarwal, A. K. (2025). Investigation of the Effect of Gate Oxide Screening with Adjustment Pulse on Commercial SiC Power MOSFETs. Electronics, 14(7), 1366. https://doi.org/10.3390/electronics14071366