A Temperature-Independent Gate-Oxide Degradation Monitoring Method for Silicon Carbide Metal Oxide–Semiconductor Field-Effect Transistors Based on Turn-Off Ringing

Abstract

1. Introduction

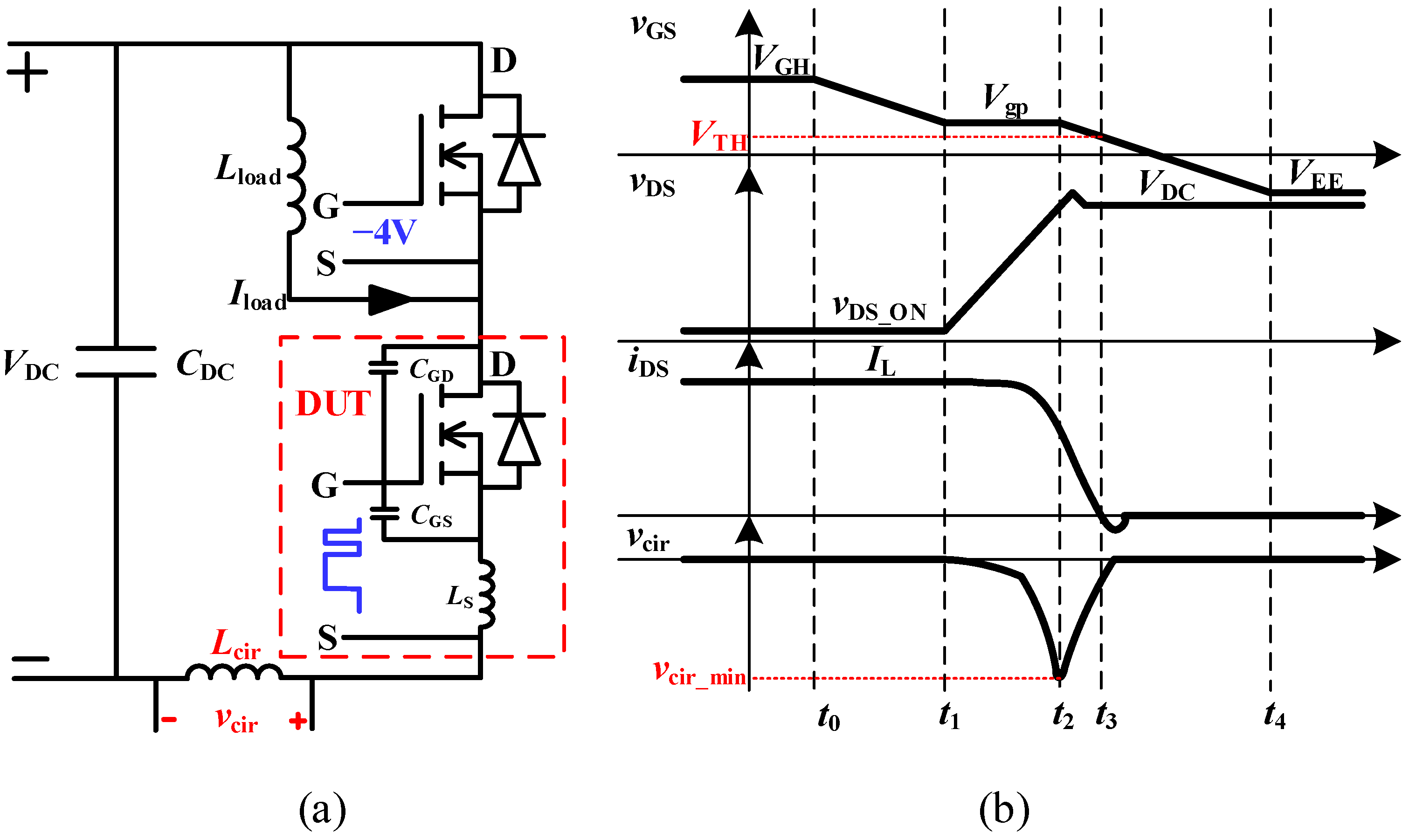

2. Theoretical Basis of the Proposed Gate-Oxide Degradation Monitoring Method

2.1. The vcir_min of SiC MOSFET at Turn-Off

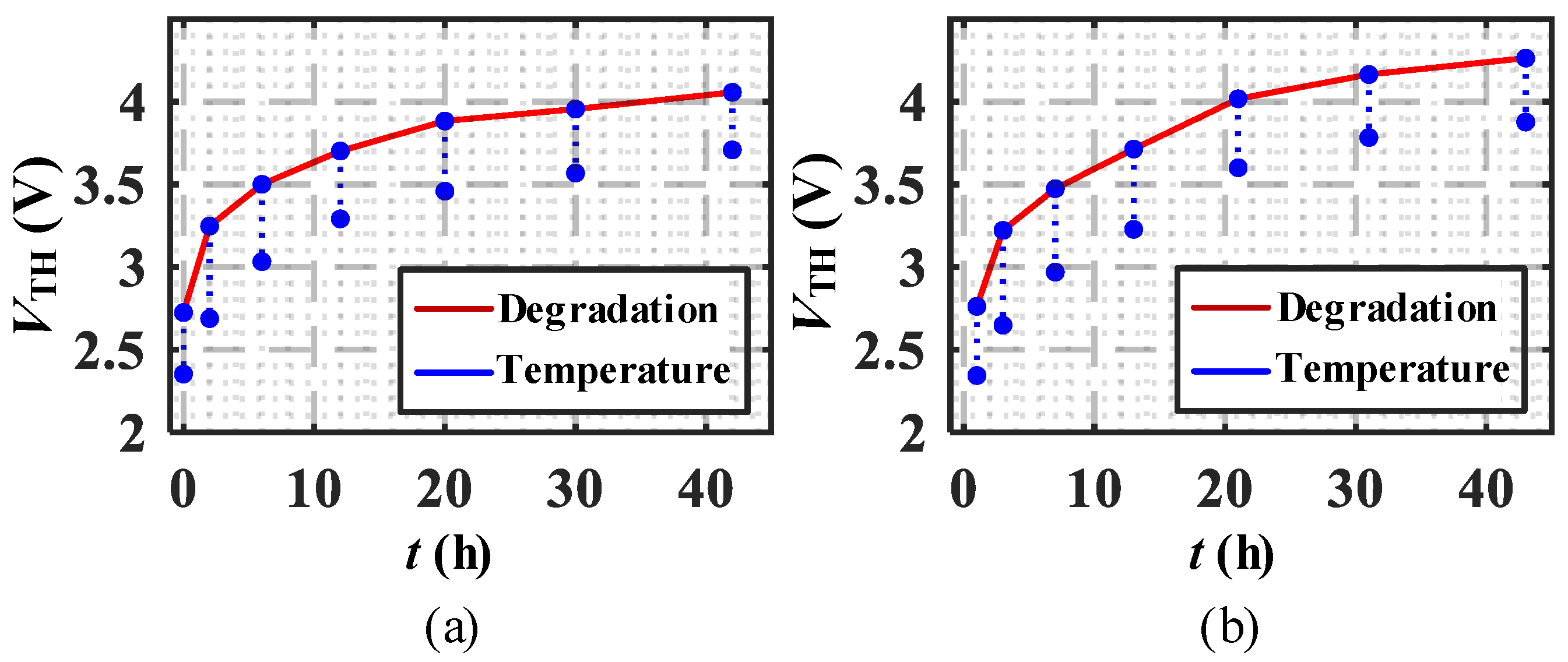

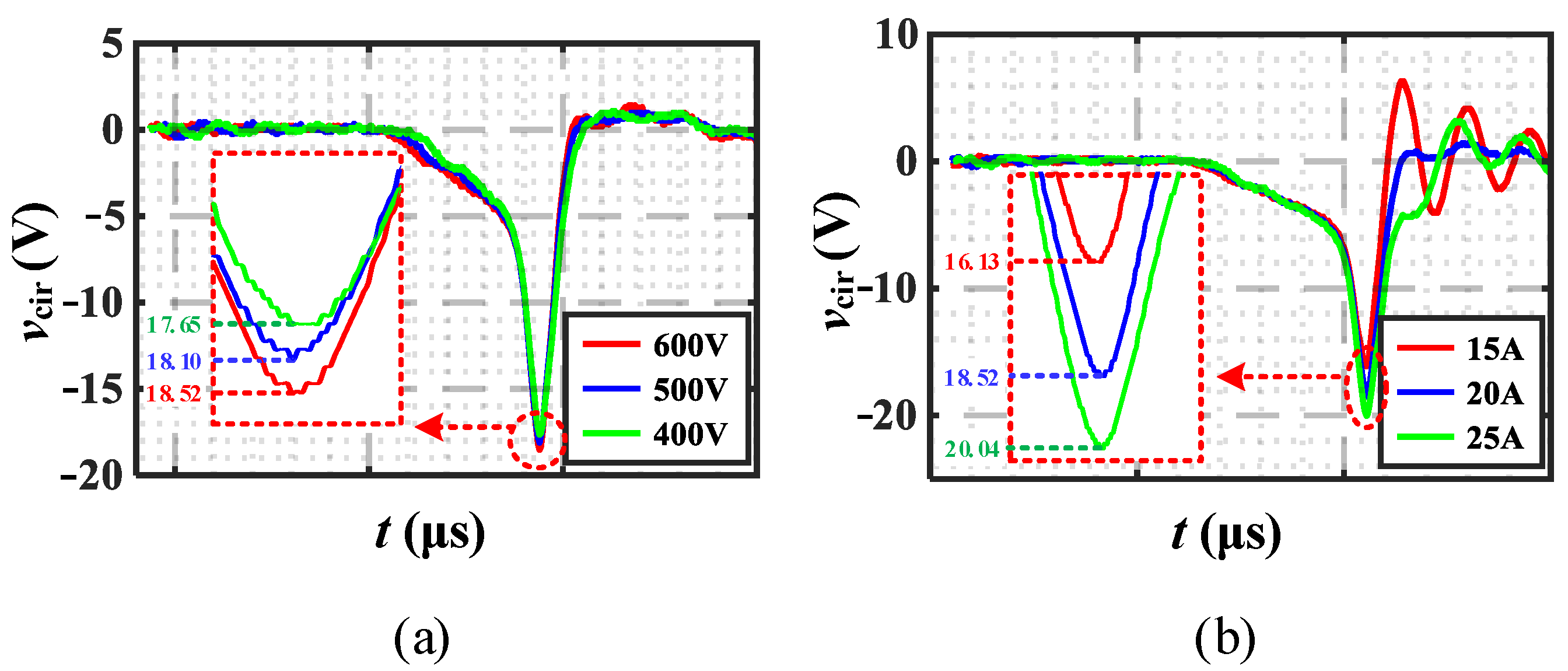

2.2. Effects of Gate-Oxide Degradation and Temperature on vcir_min

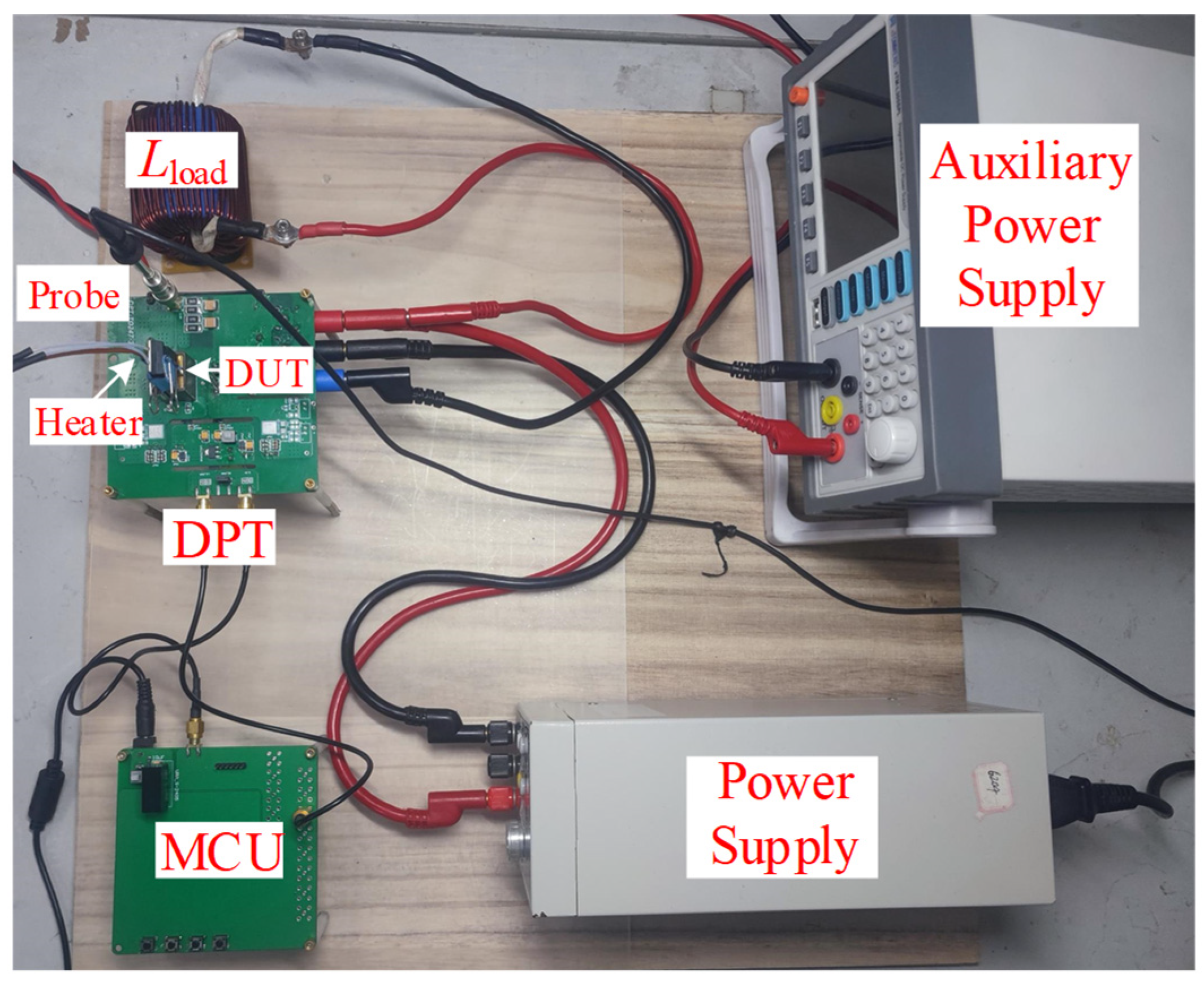

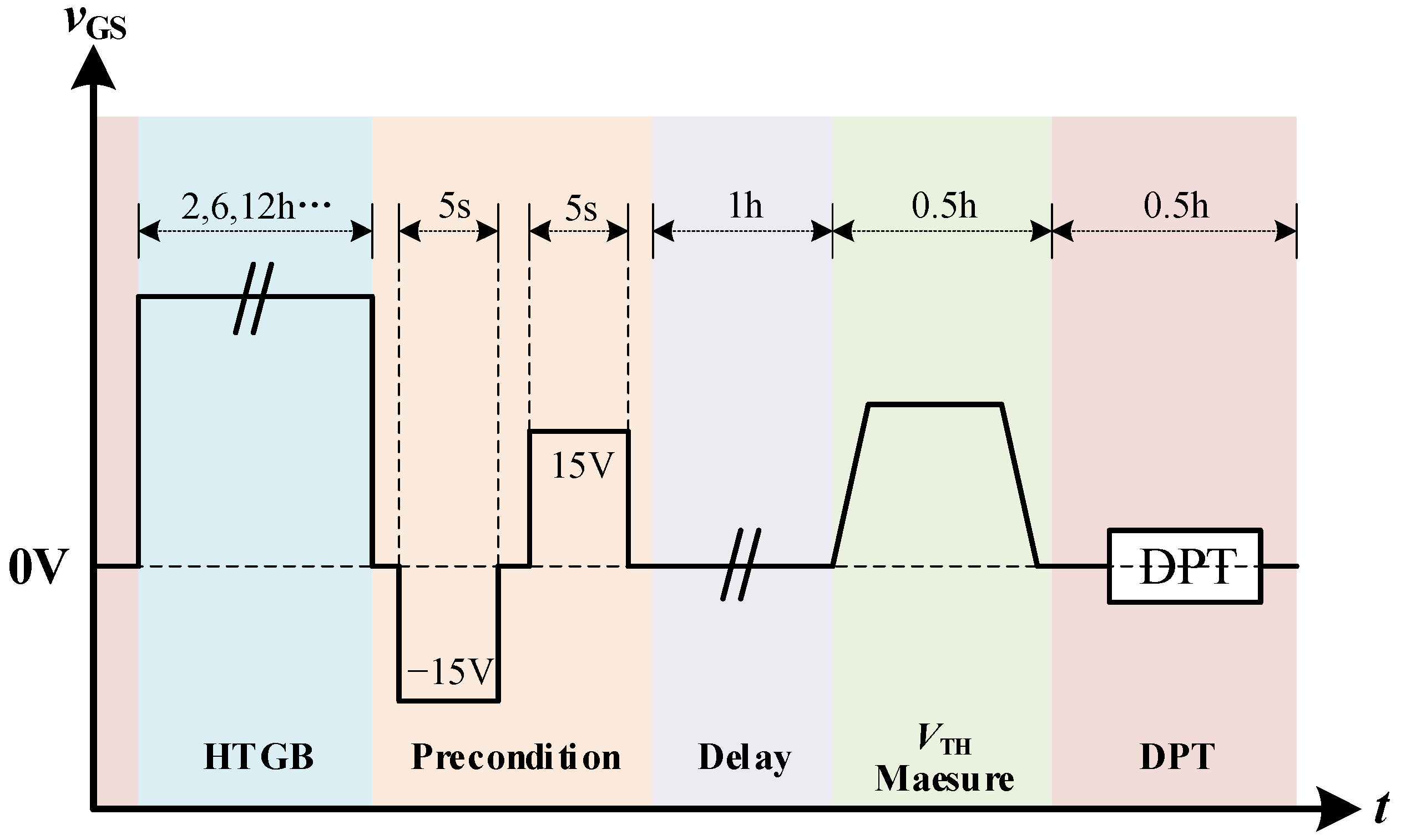

3. Experimental Validation and Analysis

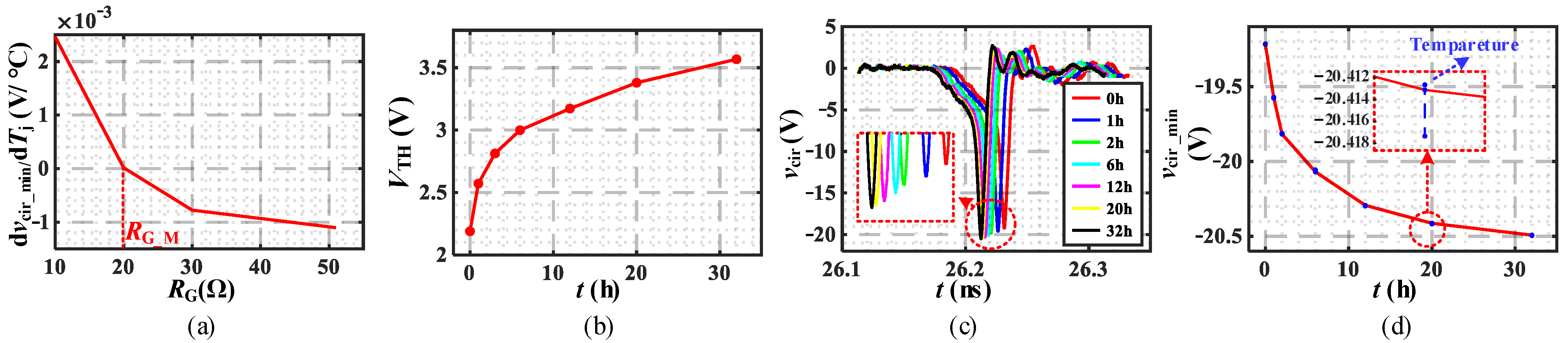

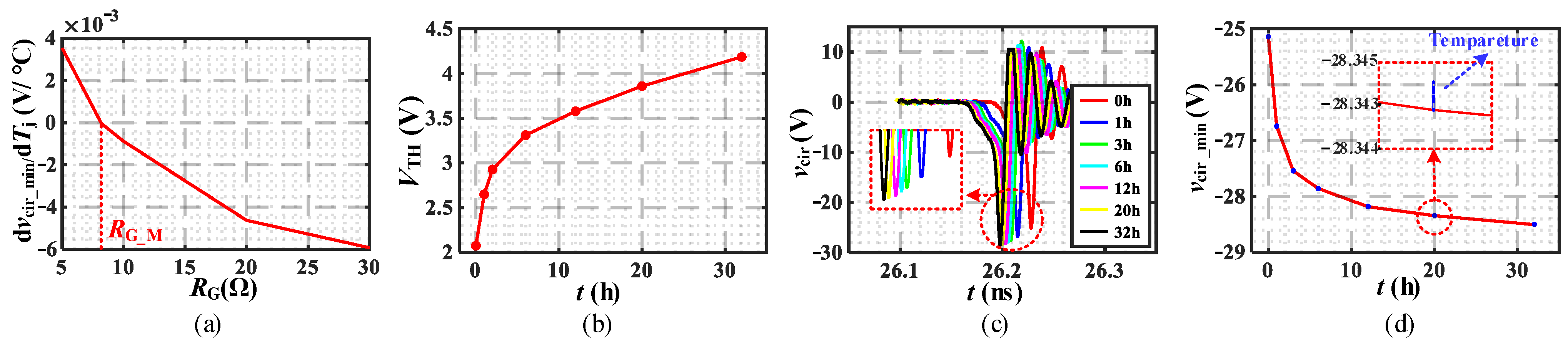

3.1. The Selection of VEE_M and RG_M

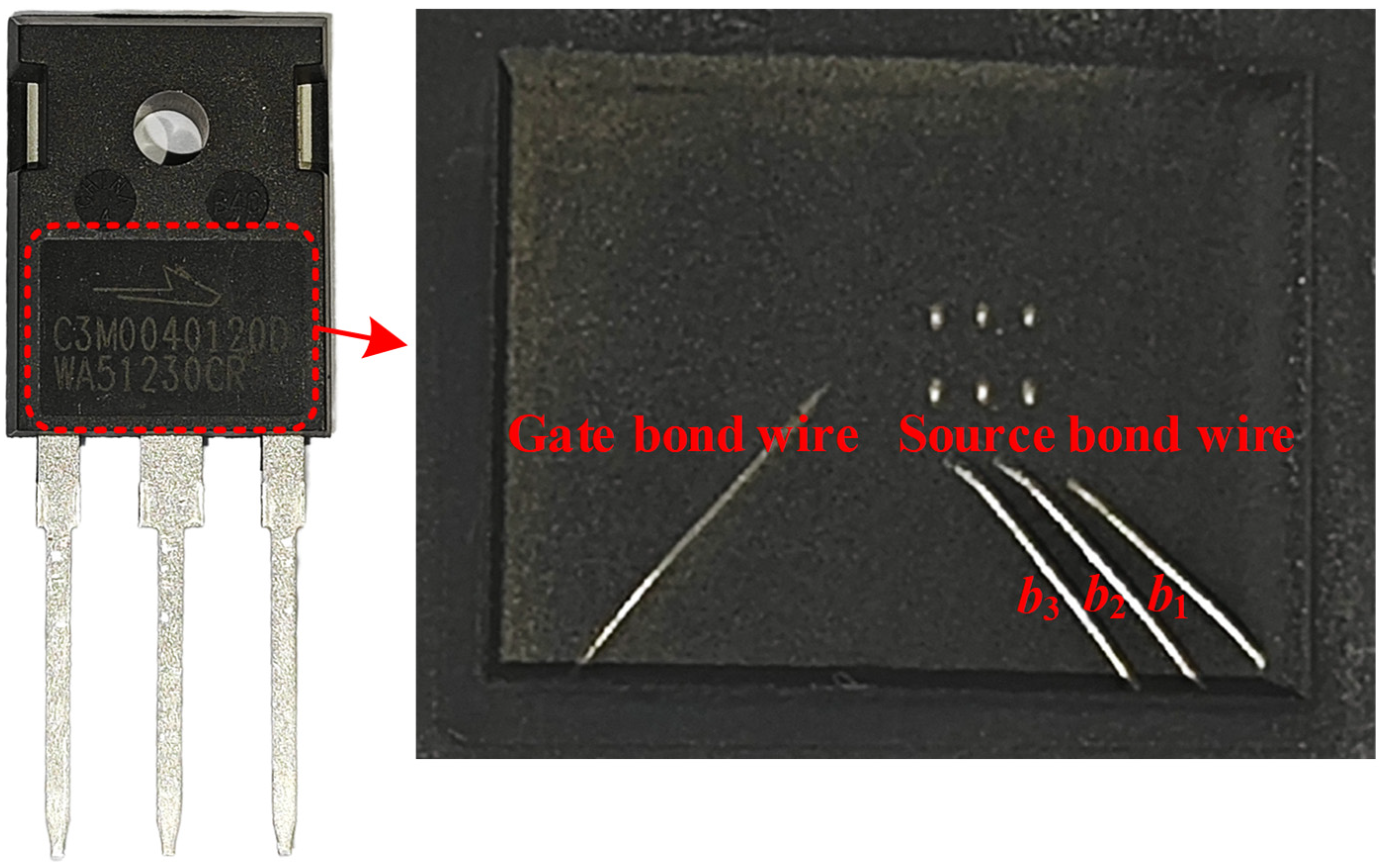

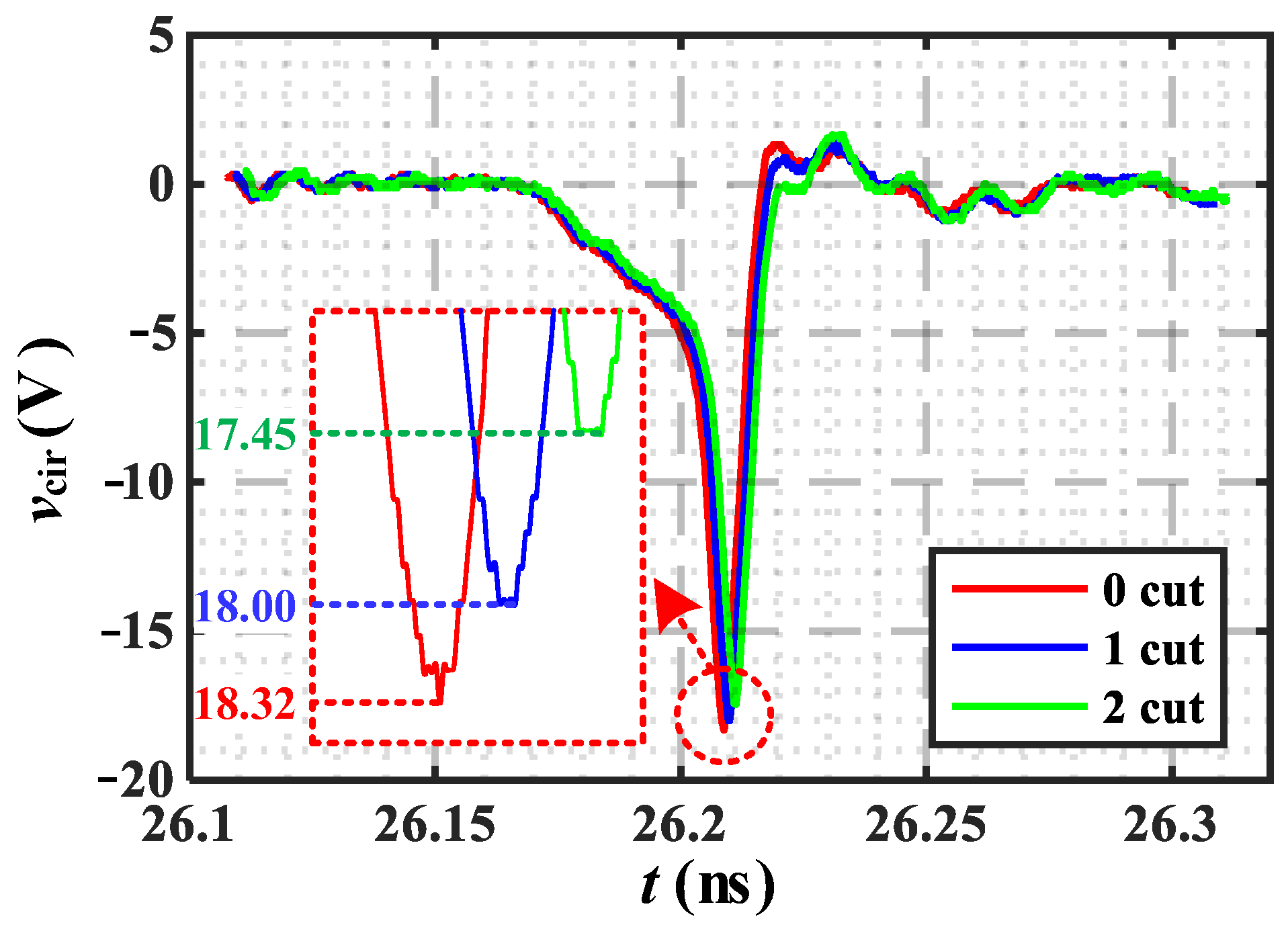

3.2. Validation of the Proposed Method

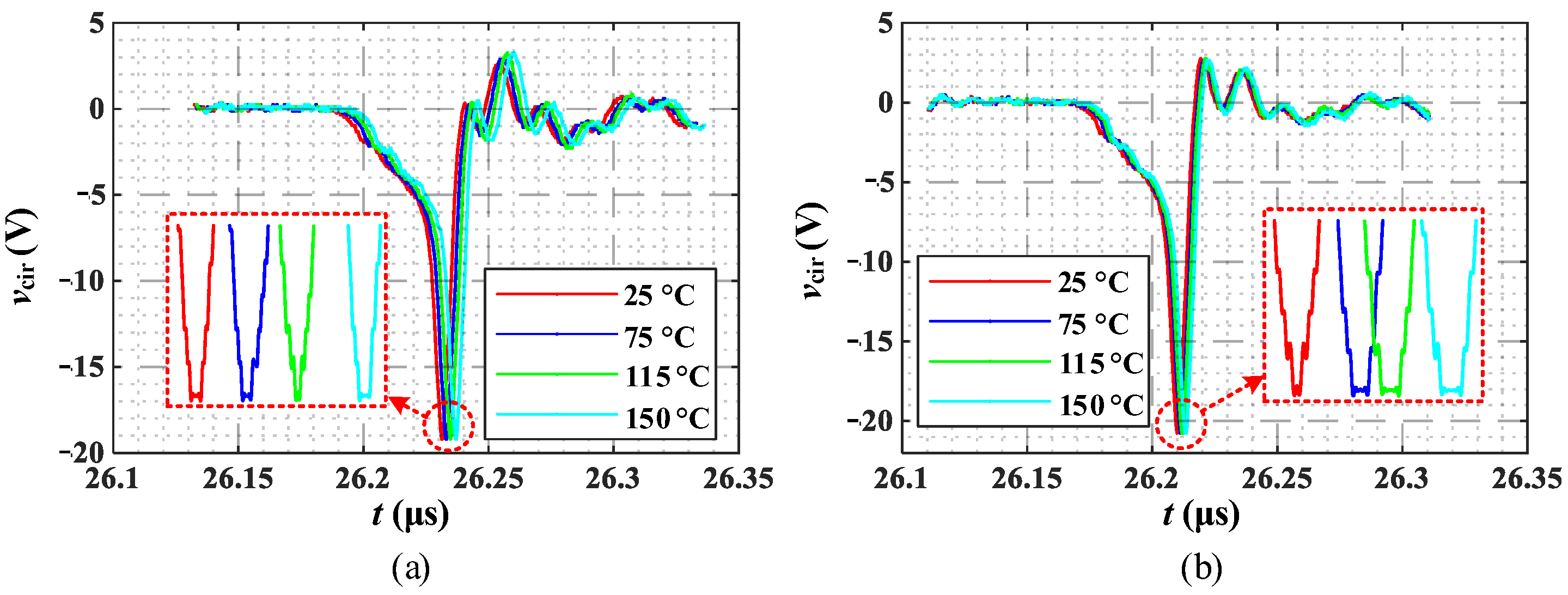

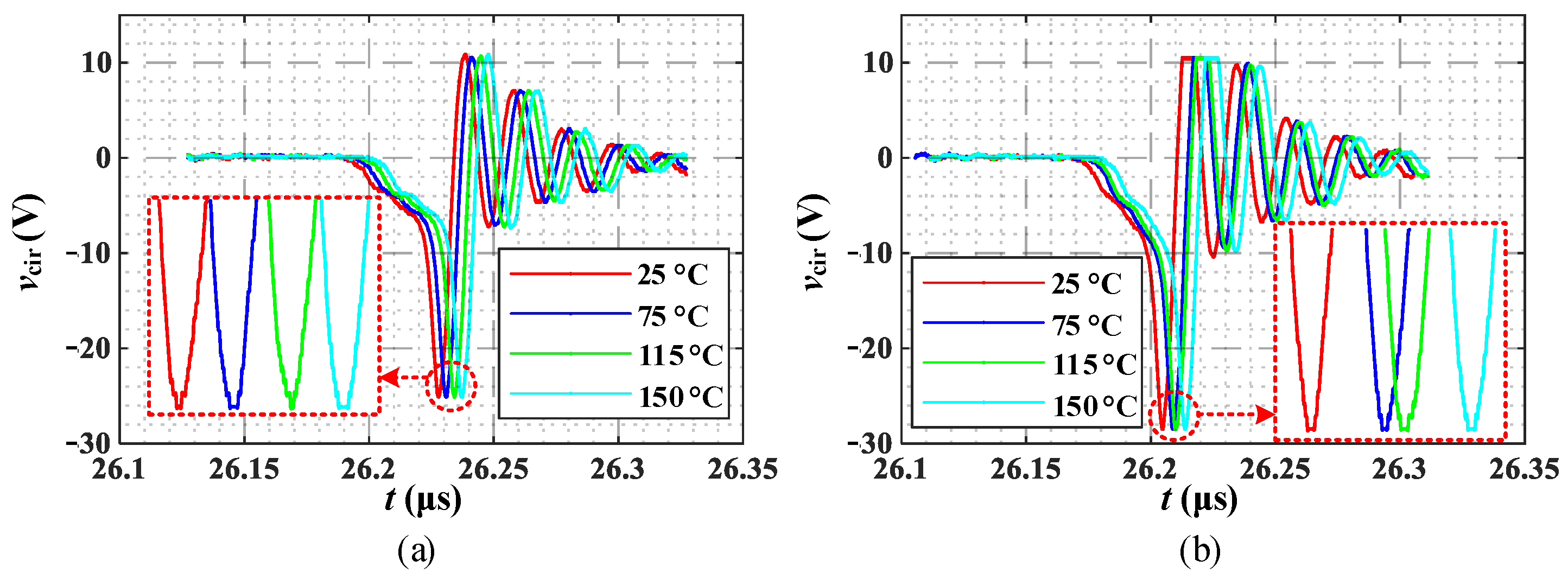

3.3. Affecting Factors of vcir_min

4. Discussion

4.1. Universality Analysis

4.2. Comparison with Other Precursors

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Millán, J.; Godignon, P.; Perpiñà, X.; Pérez-Tomás, A.; Rebollo, J. A Survey of Wide Bandgap Power Semiconductor Devices. IEEE Trans. Power Electron. 2014, 29, 2155–2163. [Google Scholar]

- Li, K.; Sun, P.; He, Z.; Huang, X.; Li, Q.; Chen, L.; Luo, Q.; Du, X. Recovery of Quasi-Permanent Bias Temperature Instability in SiC MOSFETs and Its Physical Mechanism. IEEE J. Emerg. Sel. Top. Power Electron. 2024, 12, 5852–5863. [Google Scholar] [CrossRef]

- Li, K.; Sun, P.; Zhou, X.; Chen, L.; Liu, Q. Comprehensive Investigations on Recovery Characteristics of Bias Temperature Instability in Planar and Trench SiC MOSFETs. IEEE J. Emerg. Sel. Top. Power Electron. 2024; early access. [Google Scholar] [CrossRef]

- Miki, H.; Sagawa, M.; Mori, Y.; Murata, T.; Kinoshita, K.; Asaka, K.; Oda, T. Accurate screening of defective oxide on SiC using consecutive multiple threshold-voltage measurements. In Proceedings of the 2022 IEEE International Reliability Physics Symposium (IRPS), Dallas, TX, USA, 27–31 March 2022; pp. 8B.2-1–8B.2-7. [Google Scholar]

- Barón, K.M.; Sharma, K.; Nitzsche, M.; Kallfass, I. Online Monitoring of Degradation Sensitive Electrical Parameters in Inverter Operation for SiC-MOSFETs. In Proceedings of the 2021 IEEE Applied Power Electronics Conference and Exposition (APEC), Phoenix, AZ, USA, 14–17 June 2021; pp. 1235–1241. [Google Scholar]

- Zhang, Q.; Li, W.; Zhang, P. A Decoupled Junction Temperature and Aging Level Evaluating Method for SiC MOSFETs. IEEE J. Emerg. Sel. Top. Power Electron. 2024, 12, 2558–2568. [Google Scholar] [CrossRef]

- Jiang, X.; Wang, J.; Yu, H.; Chen, J.; Zeng, Z.; Yang, X.; Shen, Z.J. Online Junction Temperature Measurement for SiC MOSFET Based on Dynamic Threshold Voltage Extraction. IEEE Trans. Power Electron. 2021, 36, 3757–3768. [Google Scholar] [CrossRef]

- Farhadi, M.; Vankayalapati, B.T.; Sajadi, R.; Akin, B. AC Power Cycling Test Setup and Condition Monitoring Tools for SiC-Based Traction Inverters. IEEE Trans. Veh. Technol. 2023, 72, 12728–12743. [Google Scholar] [CrossRef]

- Pu, S.; Yang, F.; Vankayalapati, B.T.; Ugur, E.; Xu, C.; Akin, B. A Practical On-Board SiC MOSFET Condition Monitoring Technique for Aging Detection. IEEE Trans. Ind. Appl. 2020, 56, 2828–2839. [Google Scholar] [CrossRef]

- Ugur, E.; Xu, C.; Yang, F.; Pu, S.; Akin, B. A New Complete Condition Monitoring Method for SiC Power MOSFETs. IEEE Trans. Ind. Electron. 2021, 68, 1654–1664. [Google Scholar] [CrossRef]

- Ye, X.; Chen, C.; Wang, Y.; Zhai, G.; Vachtsevanos, G.J. Online Condition Monitoring of Power MOSFET Gate Oxide Degradation Based on Miller Platform Voltage. IEEE Trans. Power Electron. 2017, 32, 4776–4784. [Google Scholar] [CrossRef]

- Karki, U.; González-Santini, N.S.; Peng, F.Z. Effect of Gate-Oxide Degradation on Electrical Parameters of Silicon Carbide MOSFETs. IEEE Trans. Electron Devices 2020, 67, 2544–2552. [Google Scholar] [CrossRef]

- Ouaida, R.; Berthou, M.; León, J.; Perpina, X.; Oge, S.; Brosselard, P.; Joubert, C. Gate Oxide Degradation of SiC MOSFET in Switching Conditions. IEEE Electron Device Lett. 2014, 35, 1284–1286. [Google Scholar] [CrossRef]

- Erturk, F.; Ugur, E.; Olson, J.; Akin, B. Real-Time Aging Detection of SiC MOSFETs. IEEE Trans. Ind. Appl. 2019, 55, 600–609. [Google Scholar] [CrossRef]

- Farhadi, M.; Yang, F.; Pu, S.; Vankayalapati, B.T.; Akin, B. Temperature-Independent Gate-Oxide Degradation Monitoring of SiC MOSFETs Based on Junction Capacitances. IEEE Trans. Power Electron. 2021, 36, 8308–8324. [Google Scholar] [CrossRef]

- Xie, M.; Sun, P.; Wang, K.; Luo, Q.; Du, X. Online Gate-Oxide Degradation Monitoring of Planar SiC MOSFETs Based on Gate Charge Time. IEEE Trans. Power Electron. 2022, 37, 7333–7343. [Google Scholar] [CrossRef]

- Zhang, W.; Qi, L.; Tan, K.; Ji, B.; Zhang, X.; Chai, W.; Cui, X. IGBT Junction Temperature Estimation Using a Dynamic TSEP Independent of Wire Bond Faults. IEEE Trans. Power Electron. 2023, 38, 5323–5334. [Google Scholar] [CrossRef]

- Fang, X.; Sun, P.; Wang, B.; Luo, Q.; Du, X. Online Bridge-Level Junction Temperature Evaluation of IGBTs via Emitter Parasitic Inductance Voltage Undershoot. IEEE Trans. Ind. Electron. 2024, 71, 16728–16738. [Google Scholar] [CrossRef]

- Yang, Y.; Zhang, P. In Situ Insulated Gate Bipolar Transistor Junction Temperature Estimation Method via a Bond Wire Degradation Independent Parameter Turn-OFF Vce Overshoot. IEEE Trans. Ind. Electron. 2021, 68, 10118–10129. [Google Scholar] [CrossRef]

- Yang, Y.; Wu, Y.; Ding, X.; Zhang, P. Online Junction Temperature Estimation Method for SiC MOSFETs Based on the DC Bus Voltage Undershoot. IEEE Trans. Power Electron. 2023, 38, 5422–5431. [Google Scholar] [CrossRef]

- Fang, X.; Sun, P.; He, C.; Wang, B. Online Converter-level Temperature Estimation for IGBTs Using Proportional Calibration Method. IEEE Trans. Power Electron. 2024, 40, 157–161. [Google Scholar] [CrossRef]

- Xie, M.; Sun, P.; Ouyang, W.; Luo, Q.; Du, X. Online Monitoring Bond Wires Fault of SiC MOSFETs With Kelvin Package Based on Turn-on Source Voltage Ringing. IEEE Trans. Ind. Electron. 2024, 71, 9767–9776. [Google Scholar] [CrossRef]

- Kang, J.; Zhu, A.; Chen, Y.; Luo, H.; Yao, L.; Xin, Z. An Online Gate Oxide Degradation Monitoring Method for SiC MOSFETs With Contactless PCB Rogowski Coil Approach. IEEE Trans. Power Electron. 2023, 38, 9673–9684. [Google Scholar] [CrossRef]

- Jahdi, S.; Alatise, O.; Alexakis, P.; Ran, L.; Mawby, P. The Impact of Temperature and Switching Rate on the Dynamic Characteristics of Silicon Carbide Schottky Barrier Diodes and MOSFETs. IEEE Trans. Ind. Electron. 2015, 62, 163–171. [Google Scholar] [CrossRef]

- Pérez-Tomás, A.; Brosselard, P.; Godignon, P.; Millán, J.; Mestres, N.; Jennings, M.R.; Covington, J.A.; Mawby, P.A. Field-effect mobility temperature modeling of 4H-SiC metal-oxide-semiconductor transistors. J. Appl. Phys. 2006, 100, 114508. [Google Scholar] [CrossRef]

- Yang, L.; Bai, Y.; Li, C.; Chen, H.; Han, Z.; Tang, Y.; Hao, J.; Yang, C.; Tian, X.; Lu, J.; et al. Analysis of Mobility for 4H-SiC N/P-Channel MOSFETs Up To 300 °C. IEEE Trans. Electron Devices 2021, 68, 3936–3941. [Google Scholar] [CrossRef]

- Sun, P.; Guo, Y.; Wu, T.; Zhao, Z.; Lai, P.; Chen, Z.; Qi, L.; Cui, X. An Online Junction Temperature Monitoring Correction Method for SiC MOSFETs at Different Parasitic Parameters. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 5007–5018. [Google Scholar] [CrossRef]

- González, J.A.O.; Alatise, O. A Novel Non-Intrusive Technique for BTI Characterization in SiC mosfets. IEEE Trans. Power Electron. 2019, 34, 5737–5747. [Google Scholar] [CrossRef]

- Wang, M.; Zhang, J.; Ng, W.T.; Nishio, H.; Iwamoto, M.; Sumida, H. Application of a Smart Gate Driver to Detect Aging in SiC Power MOSFETs. In Proceedings of the 2023 35th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Hong Kong, China, 28 May–1 June 2023; pp. 187–190. [Google Scholar]

- Zhong, X.; Jiang, H.; Qiu, G.; Tang, L.; Mao, H.; Xu, C.; Jiang, X.; Hu, J.; Qi, X.; Ran, L. Bias Temperature Instability of Silicon Carbide Power MOSFET Under AC Gate Stresses. IEEE Trans. Power Electron. 2022, 37, 1998–2008. [Google Scholar] [CrossRef]

- Zhang, J.; Shen, H.; Du, X.; Chen, R. Condition Monitoring the Inhomogeneous Thermal Fatigue of Multichip IGBT Module Based on the Thermal Attenuation Coefficient. IEEE Trans. Power Electron. 2025, 40, 2114–2125. [Google Scholar] [CrossRef]

- Zhao, S.; Yang, X.; Wu, X.; Liu, G. Investigation on Creep-Fatigue Interaction Failure of Die-Attach Solder layers in IGBTs Under Power Cycling. IEEE Trans. Power Electron. 2025; early access. [Google Scholar] [CrossRef]

- Xu, M.; Yang, X.; Li, J. C-RC Snubber Optimization Design for Improving Switching Characteristics of SiC MOSFET. IEEE Trans. Power Electron. 2022, 37, 12005–12016. [Google Scholar] [CrossRef]

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| VDC | 600 V | VGH | 15 V |

| Iload | 20 A | Lload | 700 μH |

| Rated voltage | 1200 V | Rated current | 66 A |

| Max VGH/VEE | 19/−8 V | Ref VGH/VEE | 15/−4 V |

| Parameter | Value | Parameter | Value |

|---|---|---|---|

| VEE_M (V) | 8 | VEE_M (V) | 8 |

| RG_M (Ω) | 20 | RG_M (Ω) | 8.2 |

| ΔVTH/VTH_healthy | 63.01% | ΔVTH/VTH_healthy | 91.27% |

| Δvcir_min/vcir_min_healthy | 6.64% | Δvcir_min/vcir_min_healthy | 13.38% |

| Δvcir_min/vcir_min_25 °C | 0.114% | Δvcir_min/vcir_min_25 °C | 0.089% |

| Test Condition | Monitoring Precursors | Degradation Value | Temperature Value | Degradation Sensitivity | ζ | VDC | Iload | Bond Wires Failure | Test Interface |

|---|---|---|---|---|---|---|---|---|---|

| vcir_min | 1.302 V | 0.019 V | 7.09% | 68.8 | yes | yes | yes for non-Kelvin no for Kelvin | BUS | |

| VTH (5 mA) | 1.501 V | 0.251 V | 54.38% | 5.99 | no | no | no | G, S | |

| RON (20 A, 15 V) | 7.4 mΩ | 19.5 mΩ | 13.8% | 0.39 | no | yes | yes | D, S | |

| VSD (20 A, −4 V) | 0.198 V | 0.450 V | 4.22% | 0.44 | no | yes | yes | D, S | |

| Igss (15 V) | 200 pA | <40 pA | <500 pA | × | no | no | no | G |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhou, X.; Sun, P.; Li, K.; Liu, Q.; Chen, L.; Wang, B. A Temperature-Independent Gate-Oxide Degradation Monitoring Method for Silicon Carbide Metal Oxide–Semiconductor Field-Effect Transistors Based on Turn-Off Ringing. Electronics 2025, 14, 771. https://doi.org/10.3390/electronics14040771

Zhou X, Sun P, Li K, Liu Q, Chen L, Wang B. A Temperature-Independent Gate-Oxide Degradation Monitoring Method for Silicon Carbide Metal Oxide–Semiconductor Field-Effect Transistors Based on Turn-Off Ringing. Electronics. 2025; 14(4):771. https://doi.org/10.3390/electronics14040771

Chicago/Turabian StyleZhou, Xinghao, Pengju Sun, Kaiwei Li, Qingsong Liu, Lan Chen, and Bo Wang. 2025. "A Temperature-Independent Gate-Oxide Degradation Monitoring Method for Silicon Carbide Metal Oxide–Semiconductor Field-Effect Transistors Based on Turn-Off Ringing" Electronics 14, no. 4: 771. https://doi.org/10.3390/electronics14040771

APA StyleZhou, X., Sun, P., Li, K., Liu, Q., Chen, L., & Wang, B. (2025). A Temperature-Independent Gate-Oxide Degradation Monitoring Method for Silicon Carbide Metal Oxide–Semiconductor Field-Effect Transistors Based on Turn-Off Ringing. Electronics, 14(4), 771. https://doi.org/10.3390/electronics14040771