A Design of High-Precision and Low-Noise High-Current Power Amplifier

Abstract

1. Introduction

2. Circuit Design and Implementation

2.1. Overall Circuit Structure

2.2. Core Amplifier Circuit

2.2.1. Circuit Structure Design

2.2.2. Small-Signal Analysis

2.3. Protection Circuit

2.3.1. Design of Over-Temperature Protection Circuit

2.3.2. Design of Current Limiting Protection Circuit

3. Circuit Simulation and Layout Design

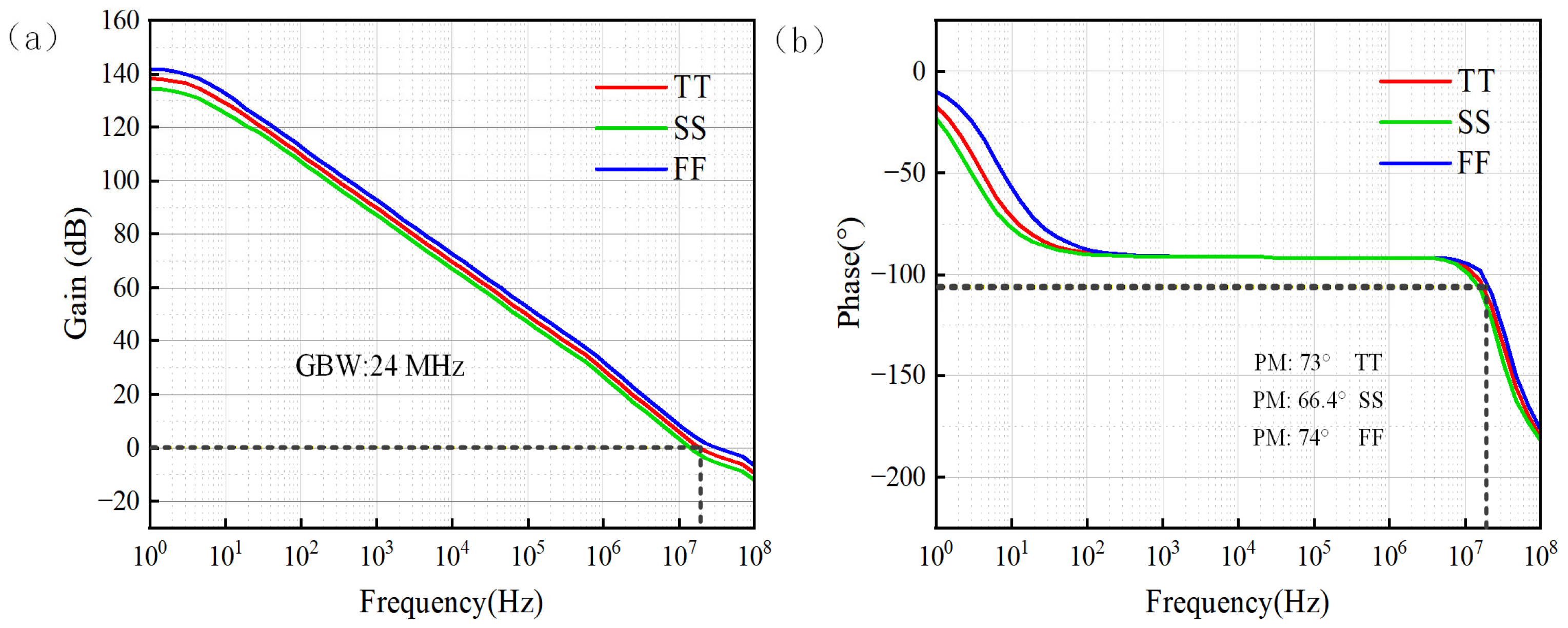

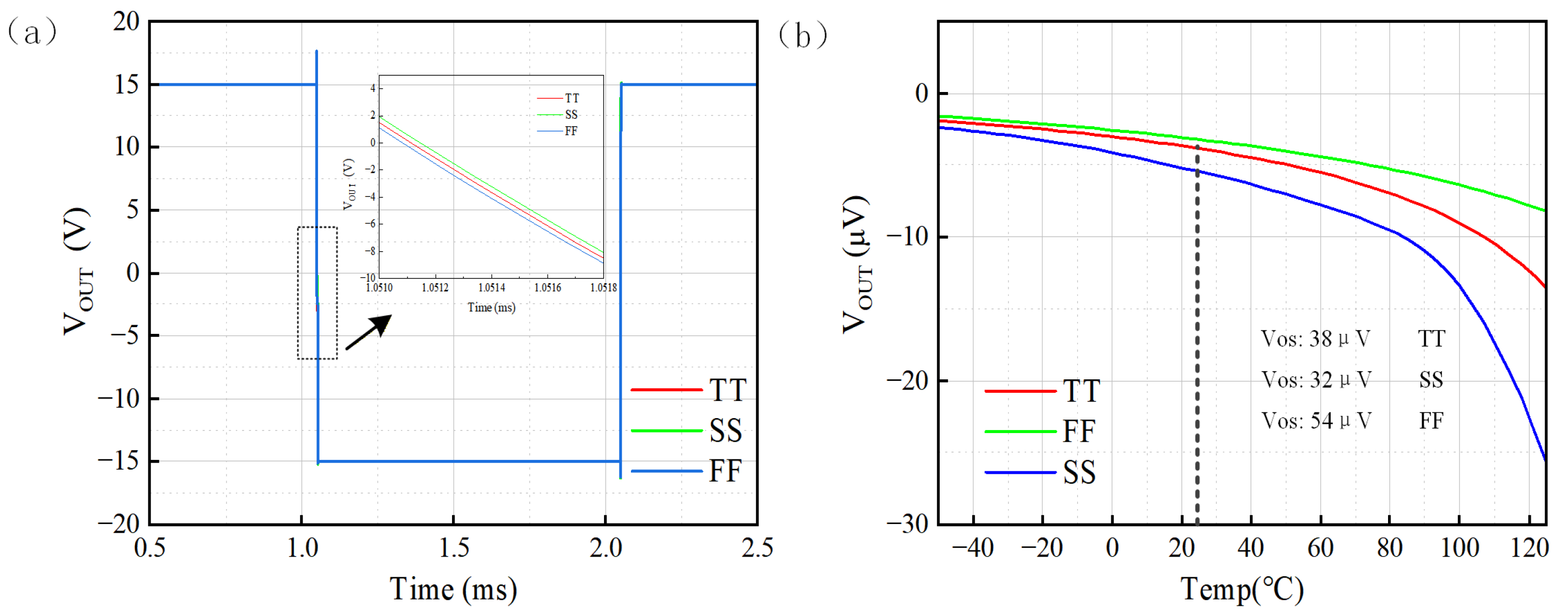

3.1. Circuit Simulation Results

3.2. Layout Design

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Singh, P.; Hariharan, K.; Kapat, S. High-Frequency Digital Current Mode Control Architectures for Class-D Audio Amplifiers. In Proceedings of the 2022 IEEE Applied Power Electronics Conference and Exposition (APEC), Houston, TX, USA, 20–24 March 2022; pp. 1846–1852. [Google Scholar]

- Kazimierczuk, M.K. Class AB, B, and C RF Power Amplifiers. In Rf Power Amplifiers; Wiley: Hoboken, NJ, USA, 2015; pp. 117–163. [Google Scholar]

- Morgos, J.; Hanko, B.; Frivaldsky, M. Design proposal of low noise automotive power supply for high-end audio systems. In Proceedings of the 2020 ELEKTRO, Taormina, Italy, 25–28 May 2020; pp. 1–5. [Google Scholar]

- Liao, H.; Wang, Y.; Jin, X. Low-power audio power amplifier with over-temperature protection function. Sens. Microsyst. 2020, 39, 100–102+106. [Google Scholar]

- Chen, X.; Shi, J.; Hu, R.; Han, Q. A High-voltage and High-Power Integrated Operational Amplifier. Appl. Integr. Circuits 2018, 35, 18–22. [Google Scholar]

- Wang, Z.; Chen, L.; Pang, Y.; Guo, L.; Ma, C. A Design of High-Voltage Operational Amplifier. Microelectronics 2018, 48, 316–320. [Google Scholar]

- Shi, J.; Yang, F.; Shi, C.; Hu, R.; Ma, Q. A low-offset high-voltage high-current Integrated operational amplifier. Semicond. Technol. 2019, 44, 8–14. [Google Scholar]

- Feng, S.; Yu, D.; Ma, K.; Yang, F. A high-speed power operational amplifier with over-temperature indication function. Semicond. Technol. 2020, 50, 273–281+312. [Google Scholar]

- Tao, J.; Shen, R.; Chen, H. Design of Low Offset High Swing rail-to-rail Operational Amplifier. Chin. J. Electron. Meas. Instrum. 2025, 39, 264–273. [Google Scholar]

- Su, G.; Xu, W.; Li, G.; Tang, H.; Wei, B.; Wei, X. A very Low power rail-to-rail high-gain low-offset operational amplifier. Pop. Sci. Technol. 2024, 26, 113–117. [Google Scholar]

- Chen, Q. Design of High-Precision, Low-Power, High-Bandwidth Rail-to-Rail Operational Amplifier. Master’s Thesis, Hunan University, Changsha, China, 2022. [Google Scholar]

- Liu, M.; Tian, Z.; Shao, G. Design and Implementation of High-Gain rail-to-rail Operational Amplifier. Comput. Technol. Dev. 2013, 23, 152–156. [Google Scholar]

- Shruthi, T.; Panchal, S.; Uniyal, S.; Tantry, S. A High Gain, Low Power Operational Amplifier utilizing BiCMOS Class AB Output Stage. In Proceedings of the 2021 2nd Global Conference for Advancement in Technology (GCAT), Bangalore, India, 1–3 October 2021; pp. 1–3. [Google Scholar]

- Kumar, A.J.; Krishna, K.L.; Viswateja, K.A.; Gopi, K.; Rao, S.M.; Mamatha, B. A High Gain Low Power Operational Amplifier using Class AB Output Stage. In Proceedings of the 2019 3rd International Conference on Computing Methodologies and Communication (ICCMC), Erode, India, 27–29 March 2019; pp. 409–413. [Google Scholar]

- Safari, L.; Azhari, S.J. A novel low voltage very low power CMOS class AB current output stage with ultra high output current drive capability. Microelectron. J. 2012, 43, 34–42. [Google Scholar] [CrossRef]

- Chen, X.; Chen, T.; Yang, J. Design of a Reference Current Source with Base Current Compensation and Over-temperature Protection Circuit. Appl. Integr. Circuits 2024, 41, 30–32. [Google Scholar]

- He, S.; Ma, K.; Yang, F. Design of High-Precision Bandgap Reference Source with Over-temperature Protection Function. Intell. Comput. Appl. 2023, 13, 107–113. [Google Scholar]

- Zhang, J.; Zhang, C.; Yang, F.; Li, C.; Li, D.; Li, T. A 40V High-Voltage Output Auto-Zero Operational Amplifier Based on 0.6μm BCD Process. Microelectronics 2023, 53, 786–793. [Google Scholar]

- Han, Q.; Zang, K.; Kong, X.; Li, K. A bipolar rail-to-rail power operational amplifier. Semicond. Technol. 2020, 45, 924–930. [Google Scholar]

- Fan, J. OPA541 monolithic power operational amplifier and its typical applications. Foreign Electron. Compon. 1998, 2–4. Available online: https://kns.cnki.net/kcms2/article/abstract?v=VqE8_zhXCqVDTv_3TPMOAL33y_rNkN1rJIU8rmiB_Lhhou7fXwAkBeIkGNIXIJI8QoS3oETZQecE0qkC8NtSedNzLsWsrtLUamYkfuSTPs_FrlqX1yIBlWyDg_CgsC5M6Tj5rwrvxVxuJeipQHHcXqvWqB01x9NdqDkCBTN8OI3gW6vMfVO8pA==&uniplatform=NZKPT&language=CHS (accessed on 15 December 2025).

- Ivanov, V.; Baum, D. A 3 A 20 MHz BiCMOS/DMOS power operational amplifier: A structural design approach. In Proceedings of the 2003 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 13 February 2003; Digest of Technical Papers. ISSCC: San Francisco, CA, USA, 2003; Volume 1, pp. 138–483. [Google Scholar]

- Gagliardi, F.; Catania, A.; Piotto, M.; Bruschi, P.; Dei, M. Parallel Slew-Rate Enhancer with Current-Recycling Core for Switched-Capacitors Circuits. IEEE Trans. Circuits Syst. II Express Briefs 2024, 71, 4814–4818. [Google Scholar] [CrossRef]

- Roh, J. High-gain class-AB OTA with low quiescent current. Analog. Integr. Circuits Signal Process. 2006, 47, 225–228. [Google Scholar] [CrossRef]

| Tube | W/L | Tube | W/L |

|---|---|---|---|

| M1/M2 | 16 × 103 | M3/M4 | 9.6 × 103 |

| M27 | 720 | M25 | 700 |

| M21 | 320 | M23 | 230 |

| Parameter | Open Loop Gain (dB) | Band- Width (MHz) | Output Current (mA) | Offset Voltage (μV) | Noise ) | Slew Rate (V/μs) | Power |

|---|---|---|---|---|---|---|---|

| Pre-simulation | 140 | 26 | 576 | 36.72 | 4.6 | 15.1 | 0.8 |

| Post-simulation | 138.9 | 24 | 560 | 38 | 4.8 | 14.2 | 0.9 |

| Parameter | This Paper | [6] | [7] | [8] | [18] | [19] | [20] | [21] |

|---|---|---|---|---|---|---|---|---|

| Open-Loop Gain (dB) | 138 | 97.9 | 95 | 138.6 | 142.7 | 125.6 | 97 | 100 |

| Bandwidth (MHz) | 24 | 3 | 9.6 | 3.089 | 1.9 | 4.98 | 1.6 | 20 |

| Output Current (mA) | 560 | 75 | 900 | 369 | - | 114.8 | 104 | 3000 |

| Noise (nV/) | 4.8 | - | - | 9.07 | 31.8 | 1.8 × 103 | - | - |

| Offset Voltage (μV) | 38 | - | 225 | 29.9 | 0.78 | 105 | 2000 | 104 |

| Slew Rate (V/μs) | 14.2 | 57 | 20 | 16.58 | 1.3 | 1.68 | 10 | 50 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, M.; He, Z.; Cao, Y.; He, B.; Liu, B.; Ren, J. A Design of High-Precision and Low-Noise High-Current Power Amplifier. Electronics 2025, 14, 4956. https://doi.org/10.3390/electronics14244956

Li M, He Z, Cao Y, He B, Liu B, Ren J. A Design of High-Precision and Low-Noise High-Current Power Amplifier. Electronics. 2025; 14(24):4956. https://doi.org/10.3390/electronics14244956

Chicago/Turabian StyleLi, Meng, Zishu He, Yu Cao, Binghui He, Bin Liu, and Jian Ren. 2025. "A Design of High-Precision and Low-Noise High-Current Power Amplifier" Electronics 14, no. 24: 4956. https://doi.org/10.3390/electronics14244956

APA StyleLi, M., He, Z., Cao, Y., He, B., Liu, B., & Ren, J. (2025). A Design of High-Precision and Low-Noise High-Current Power Amplifier. Electronics, 14(24), 4956. https://doi.org/10.3390/electronics14244956