Optimized Submodule Capacitor Ripple Voltage Suppression of an MMC-Based Power Electronic Transformer

Abstract

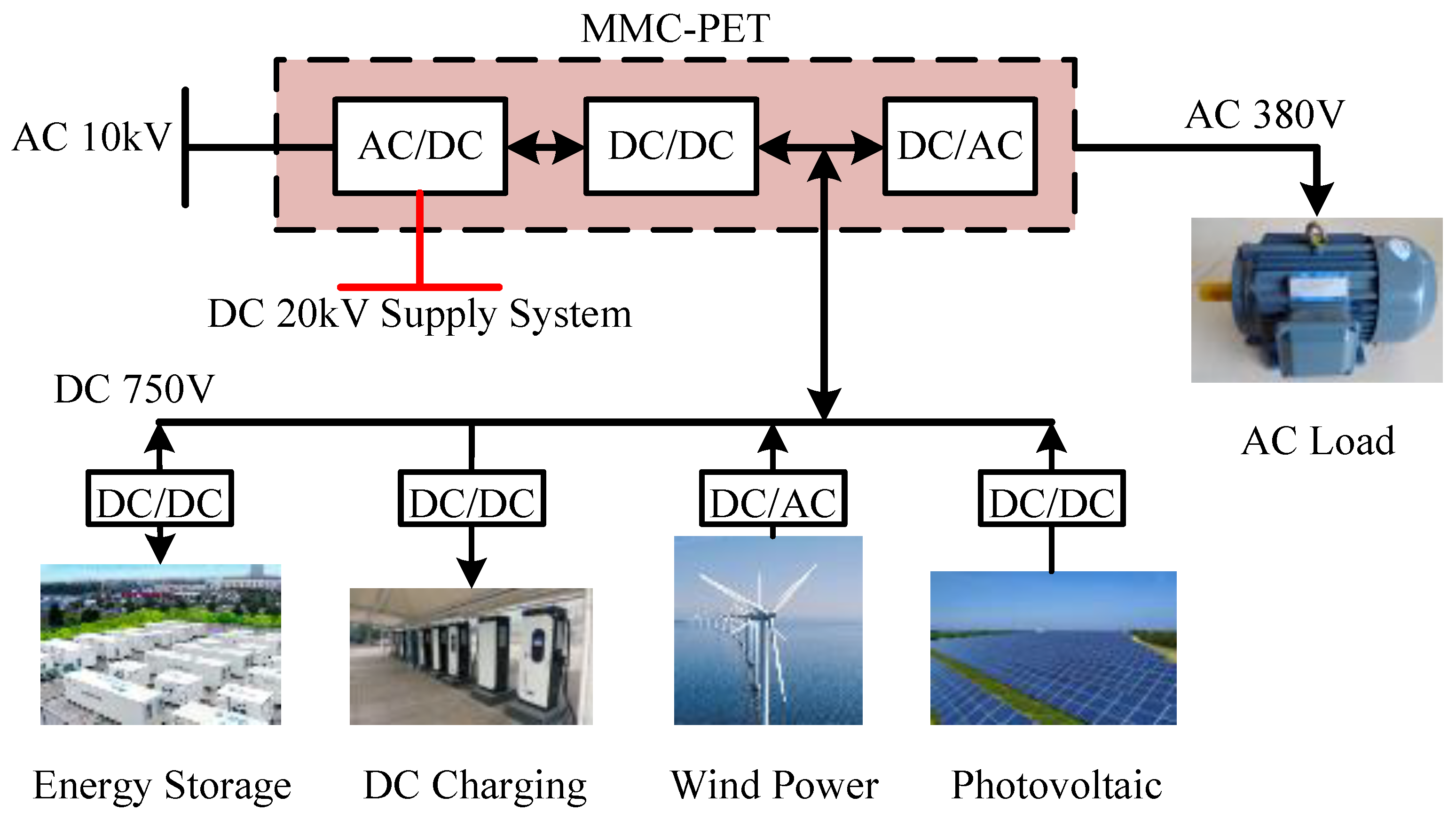

1. Introduction

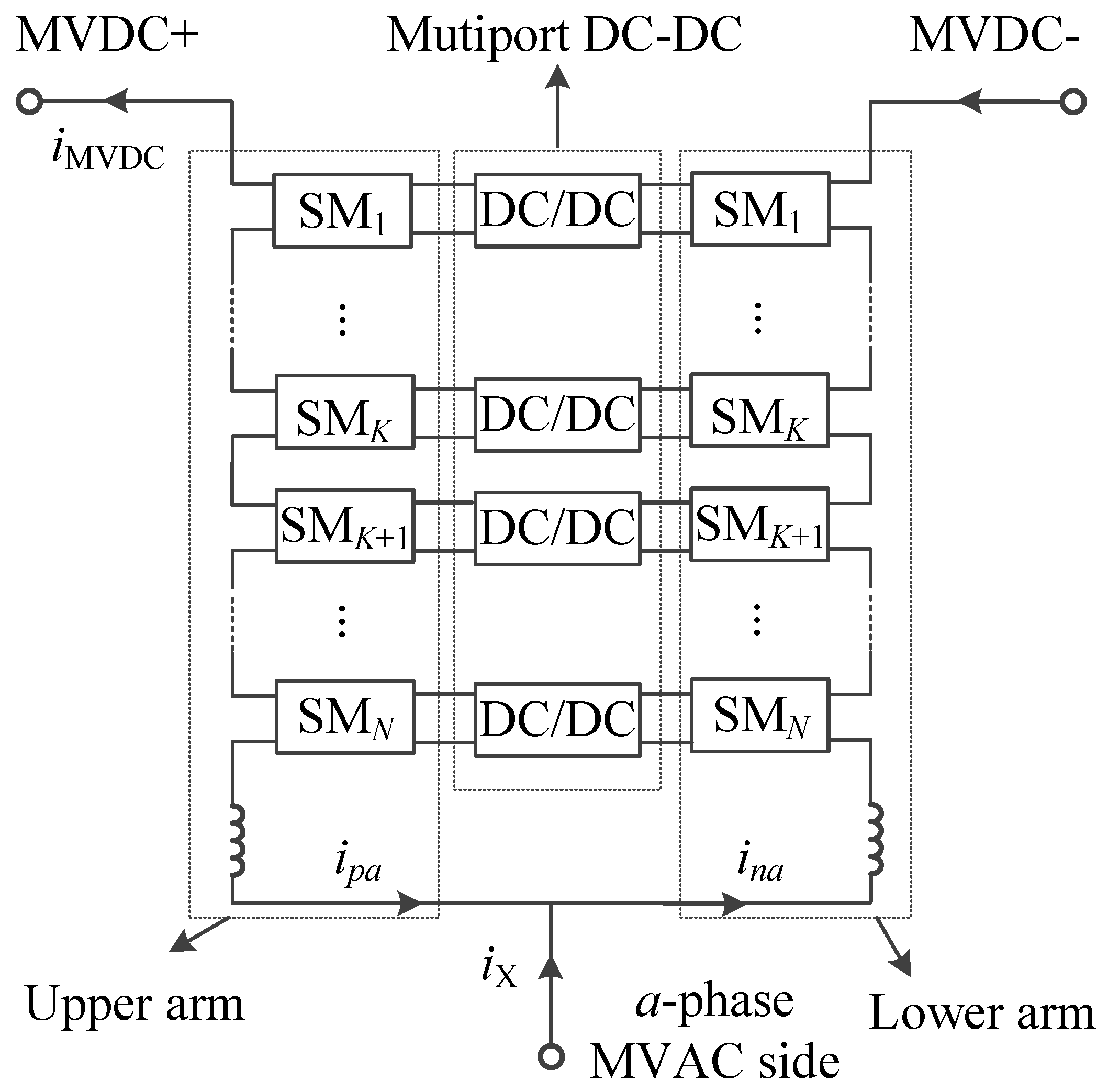

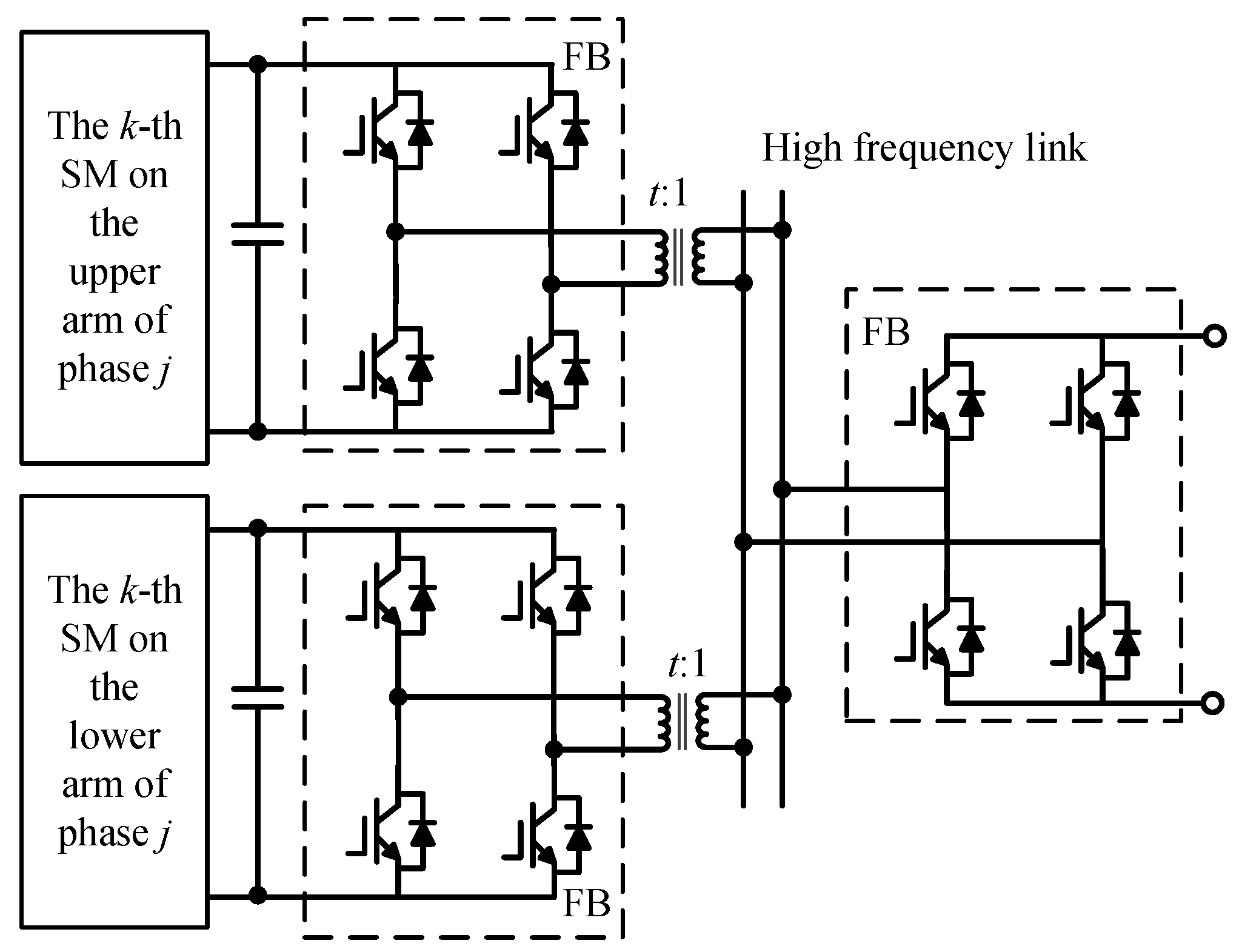

- This article proposes an MMC-type PET topology with high-frequency coupling of upper and lower arms in the isolation stage, which reduces the number of full-bridge modules and makes the structure more compact.

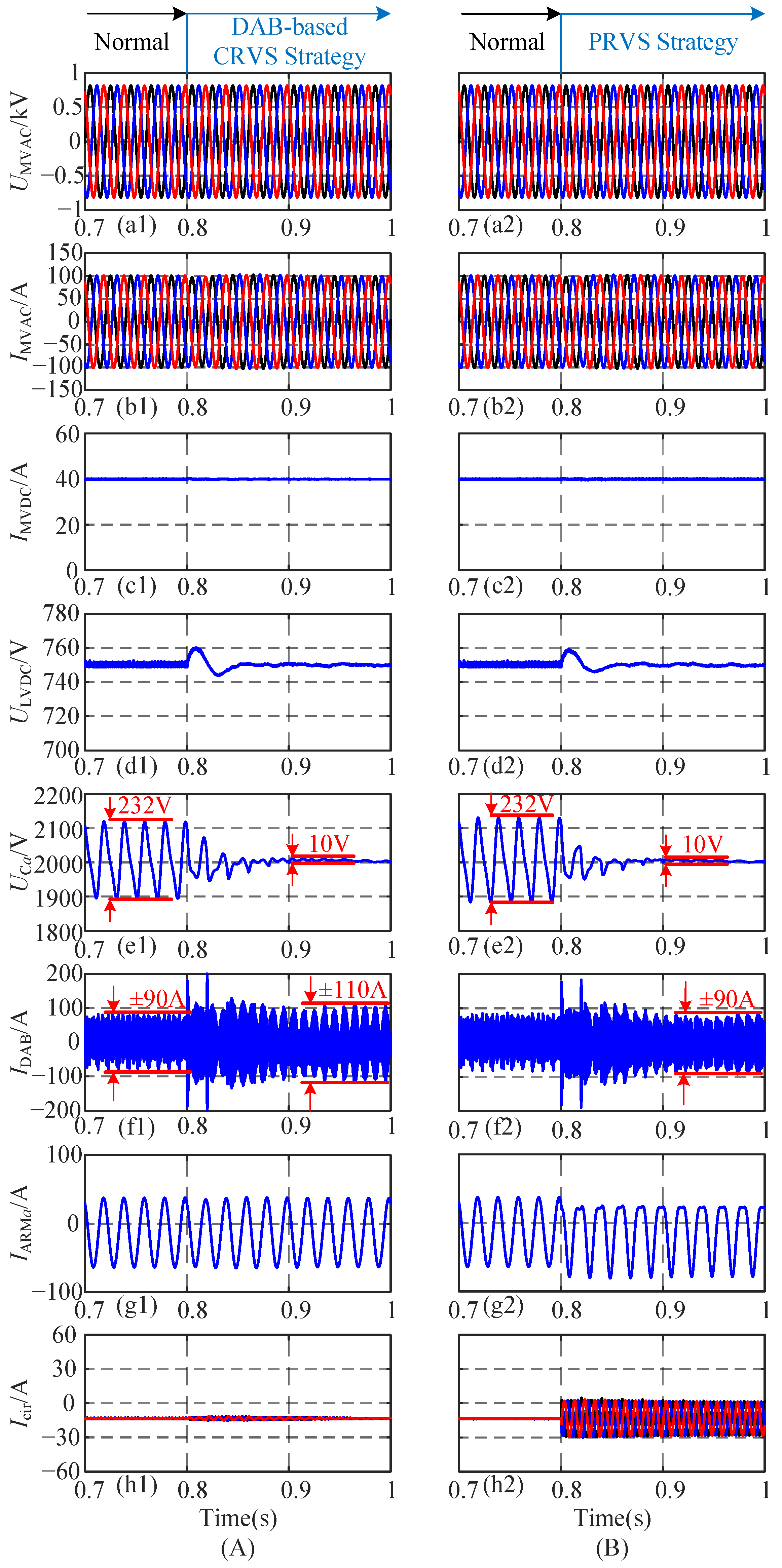

- The submodule capacitor ripple voltage coupling characteristics of the modified MMC-PET were analyzed considering symmetry and asymmetry grid voltage conditions. It is found that, under the asymmetry grid voltage condition, an unbalanced second-order ripple current can flow into the LVDC with the fully ripple voltage suppression in the DAB stage, causing a certain ripple in the LVDC side voltage.

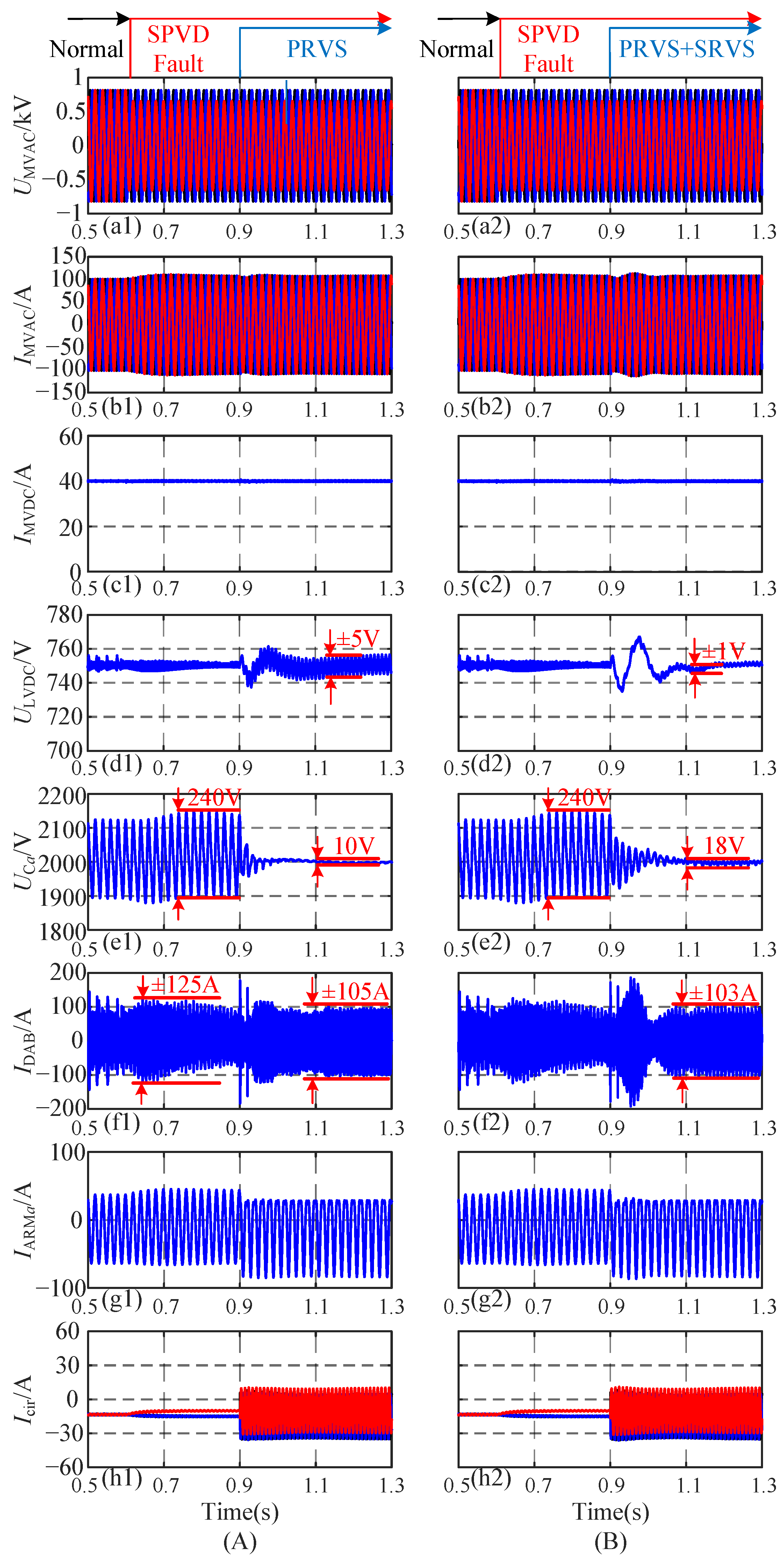

- A coordinated ripple suppression strategy combining PRVS in the MMC stage and SRVS in the DAB stage was designed to eliminate both the submodule capacitor voltage ripple and the LVDC bus voltage ripple considering asymmetric grid voltage operation conditions. The proposed PRVS + SRVS strategy can effectively suppress both the fundamental and second-order harmonic components of the submodule capacitor ripple voltage without increasing the current stress on the isolation-stage DAB switches. The simulation results showed that the peak-to-peak submodule capacitor ripple voltage was reduced from 232 V to 10 V, while the peak current of the isolation stage secondary side (ISSS) switch was limited to ±90 A. The second harmonic ripple voltage on the LVDC bus can be decreased from ±5 V to ±1 V with the proposed SRVS method under the asymmetric grid voltage condition.

- The improved phase shift modulation strategy of PRVS for the DAB stage was designed based on a proportional repetitive controller, which enables real-time multi-frequency ripple suppression and successfully transfers ripple power to the LVDC bus, significantly improving voltage quality. Under both normal and asymmetric grid conditions, the method ensured stable operation of the LVDC side with minimal ripple.

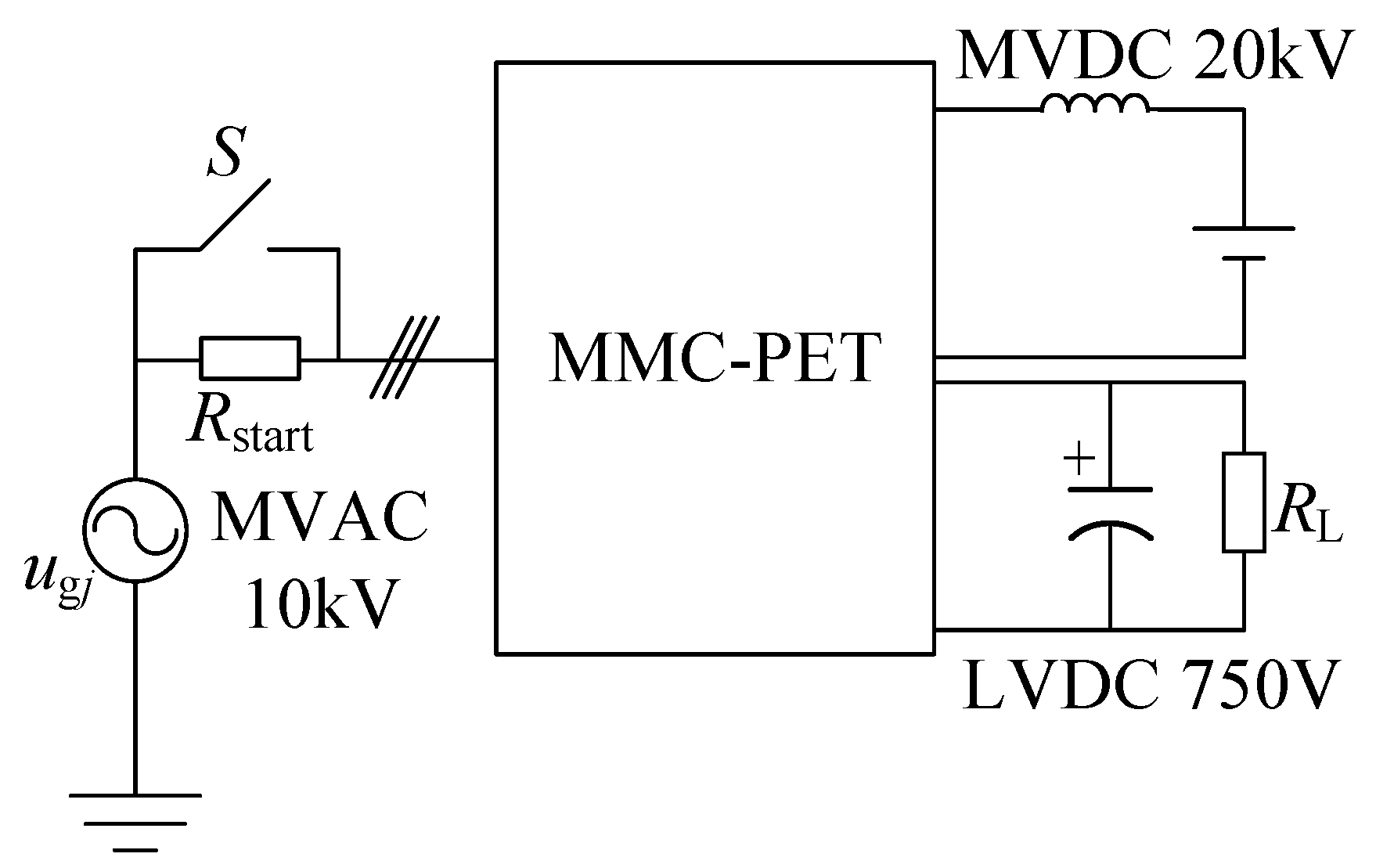

2. Topology and Coupling Characteristic Analysis of the MMC-Type PETs with Upper and Lower Arm Coupling

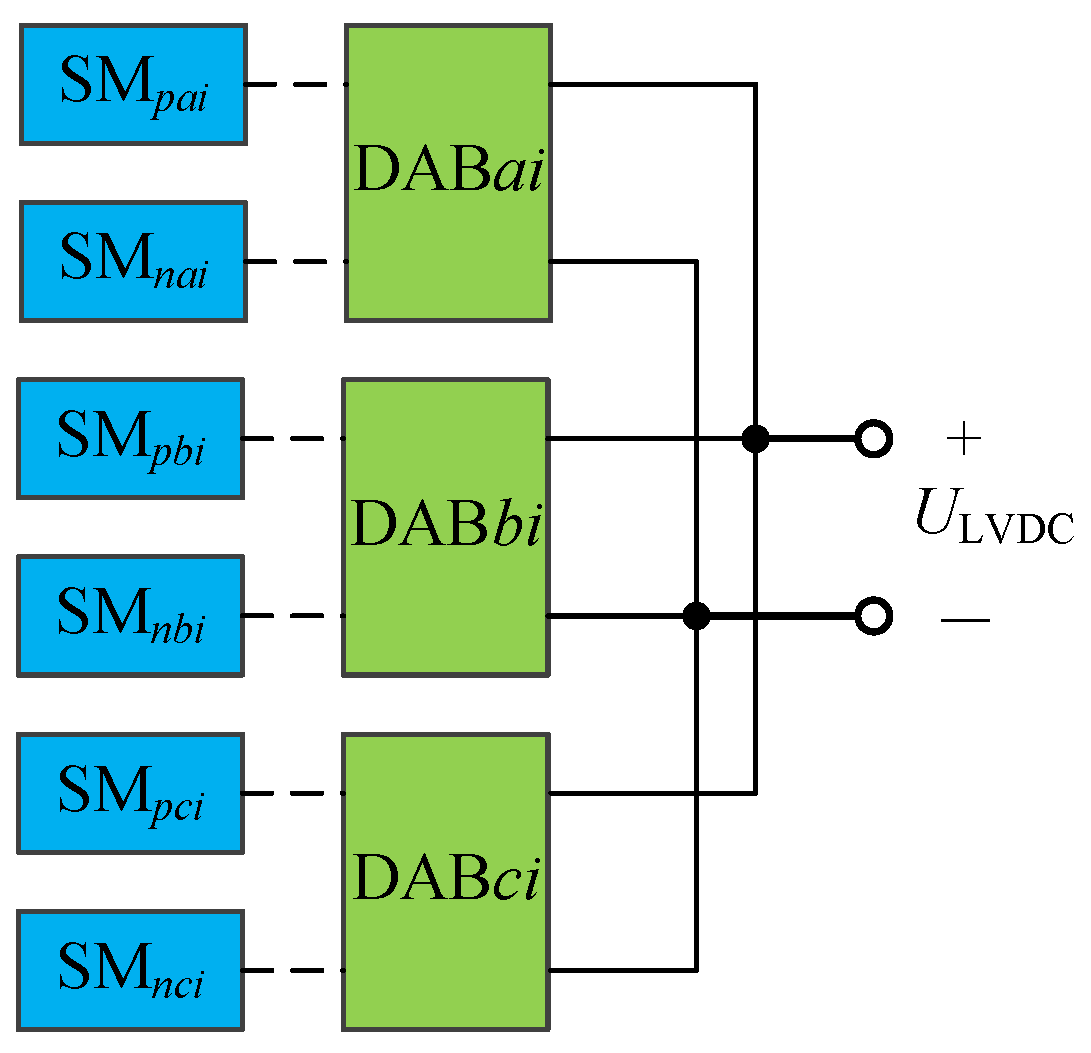

2.1. MMC–PET Topology

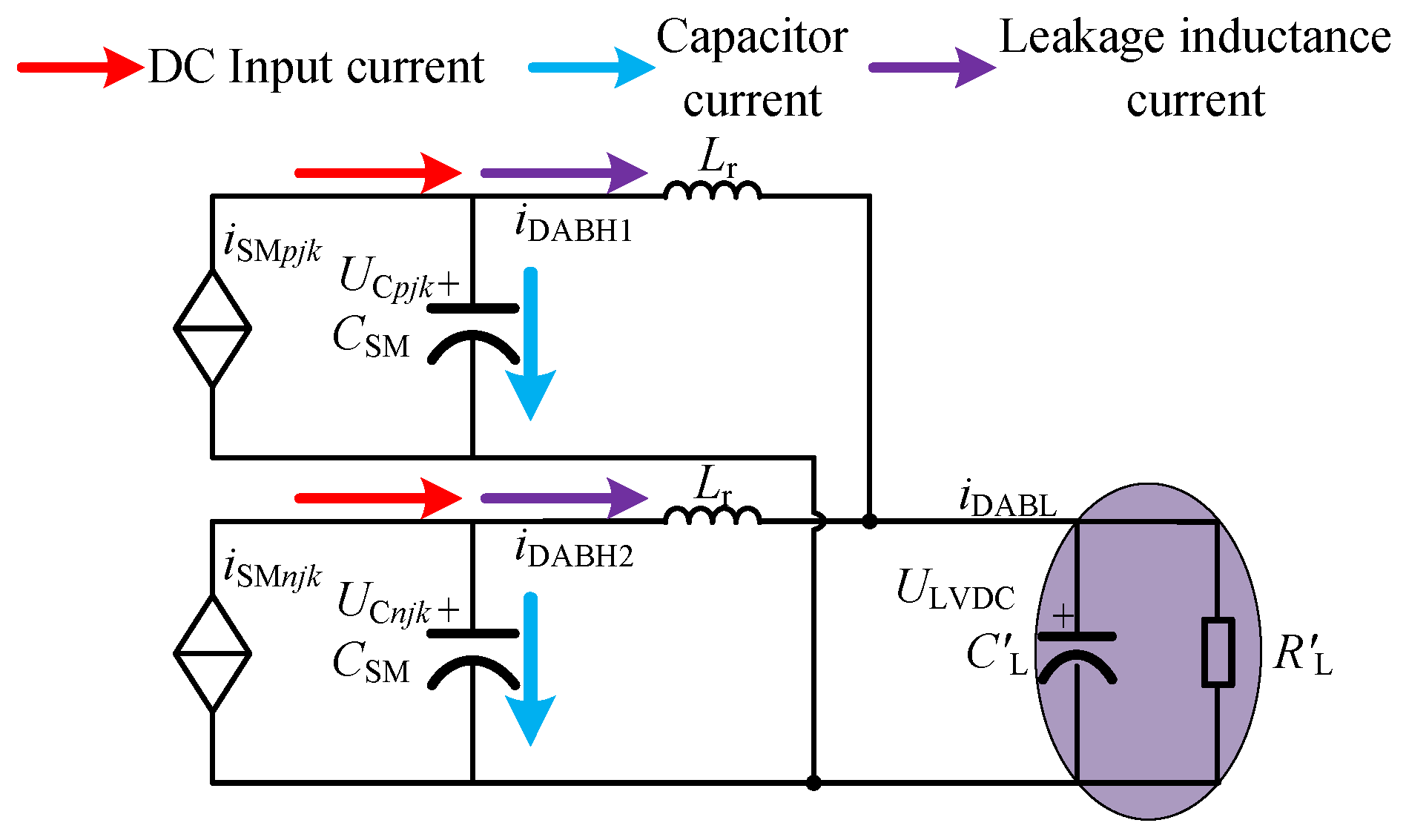

2.2. Analysis of Ripple Voltage Coupling Characteristics Under Symmetry and Asymmetry Grid Voltage Conditions

- (1)

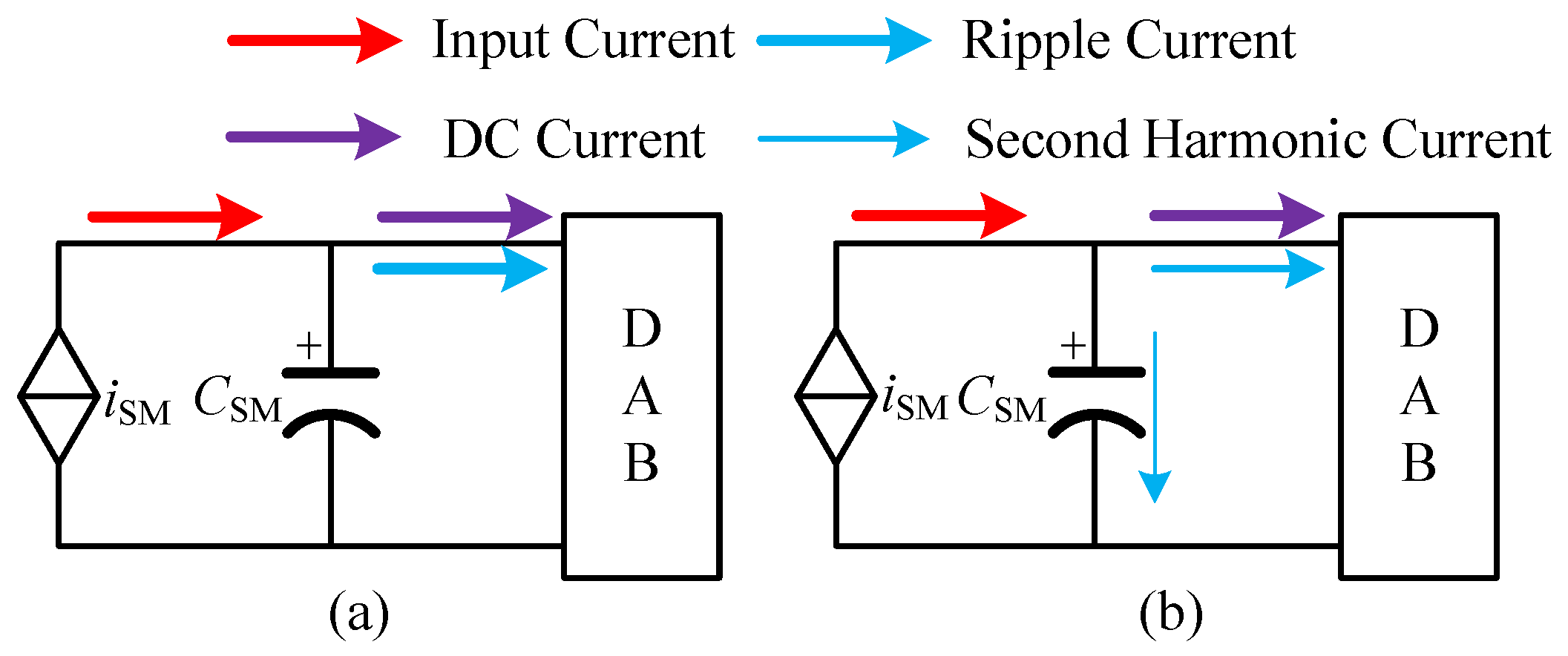

- Under the balanced operation condition of the grid side voltage, there is

- (2)

- Under the unbalanced operation condition of the grid side voltage, the second harmonic current flowing through the LVDC side capacitor will cause a certain ripple in the LVDC side voltage, and this ripple is proportional to the degree of voltage drop. To solve this problem, it can be considered to only transmit the line-frequency ripple voltage of the submodule capacitor without the second harmonic ripple. Then, the LVDC side voltage will not contain the second-order harmonic ripple under asymmetric operating conditions of the grid voltage.

3. Optimized Suppression Method for Capacitor Ripple Voltage in an MMC–PET Submodule Considering Grid Fault Conditions

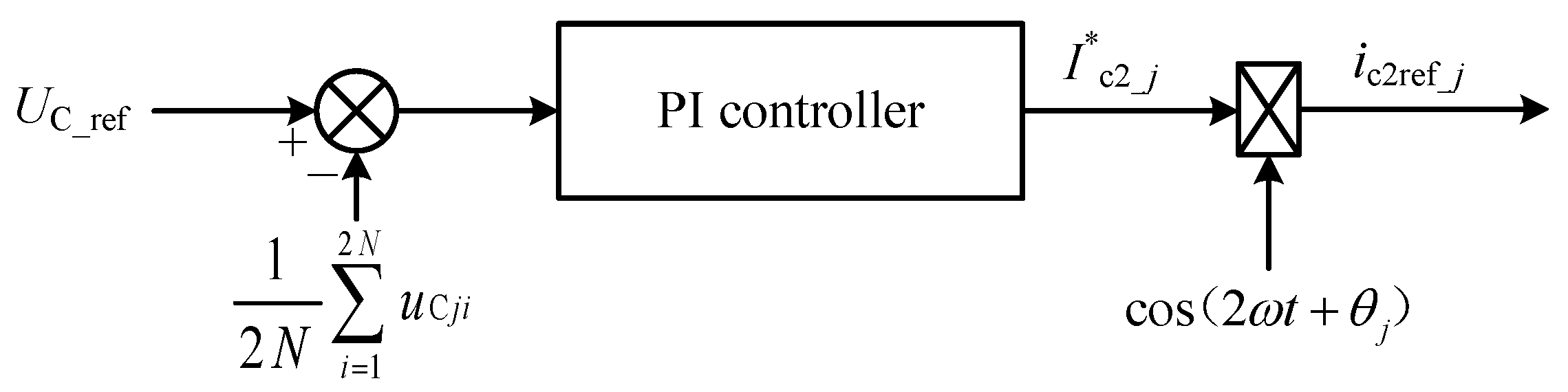

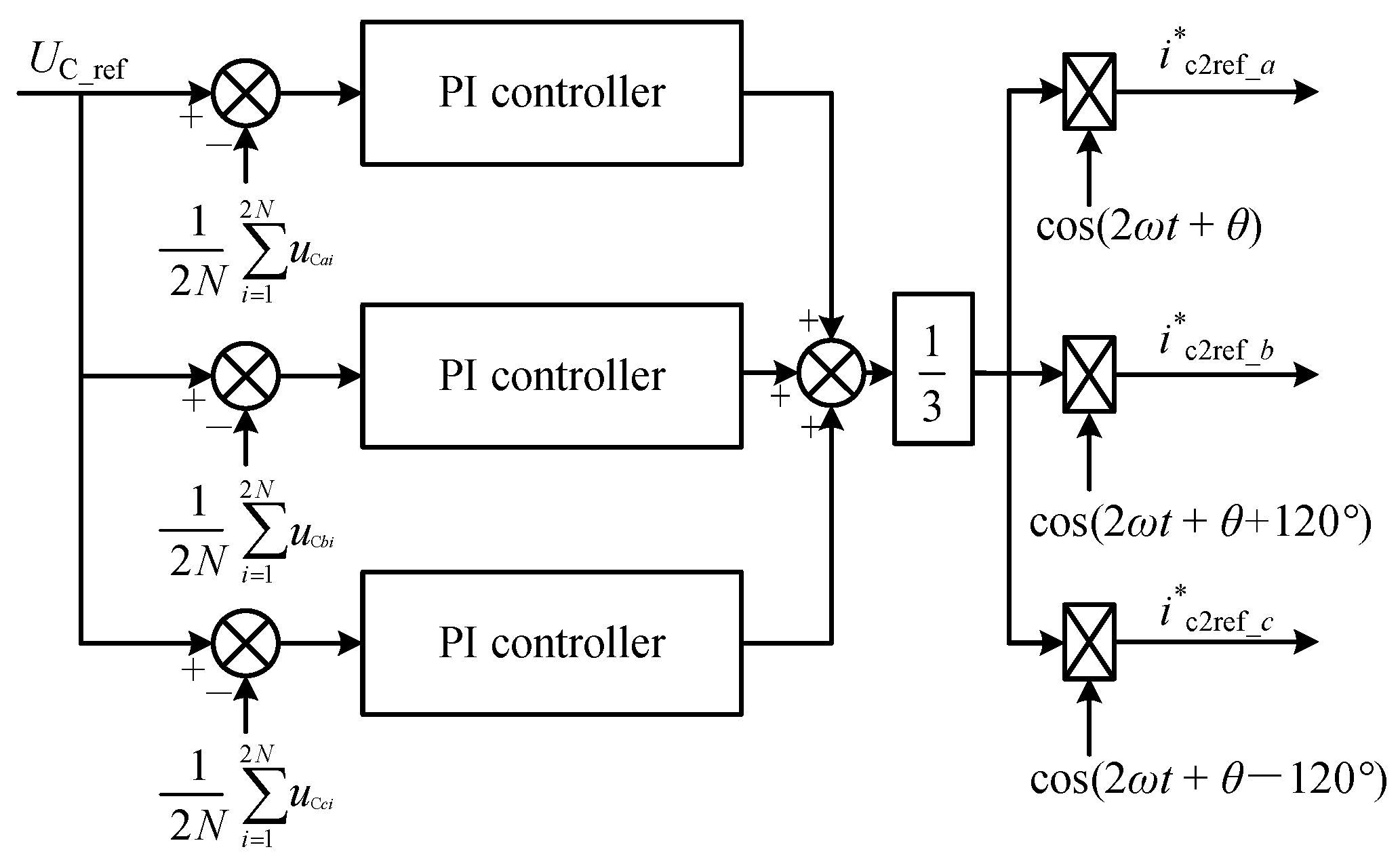

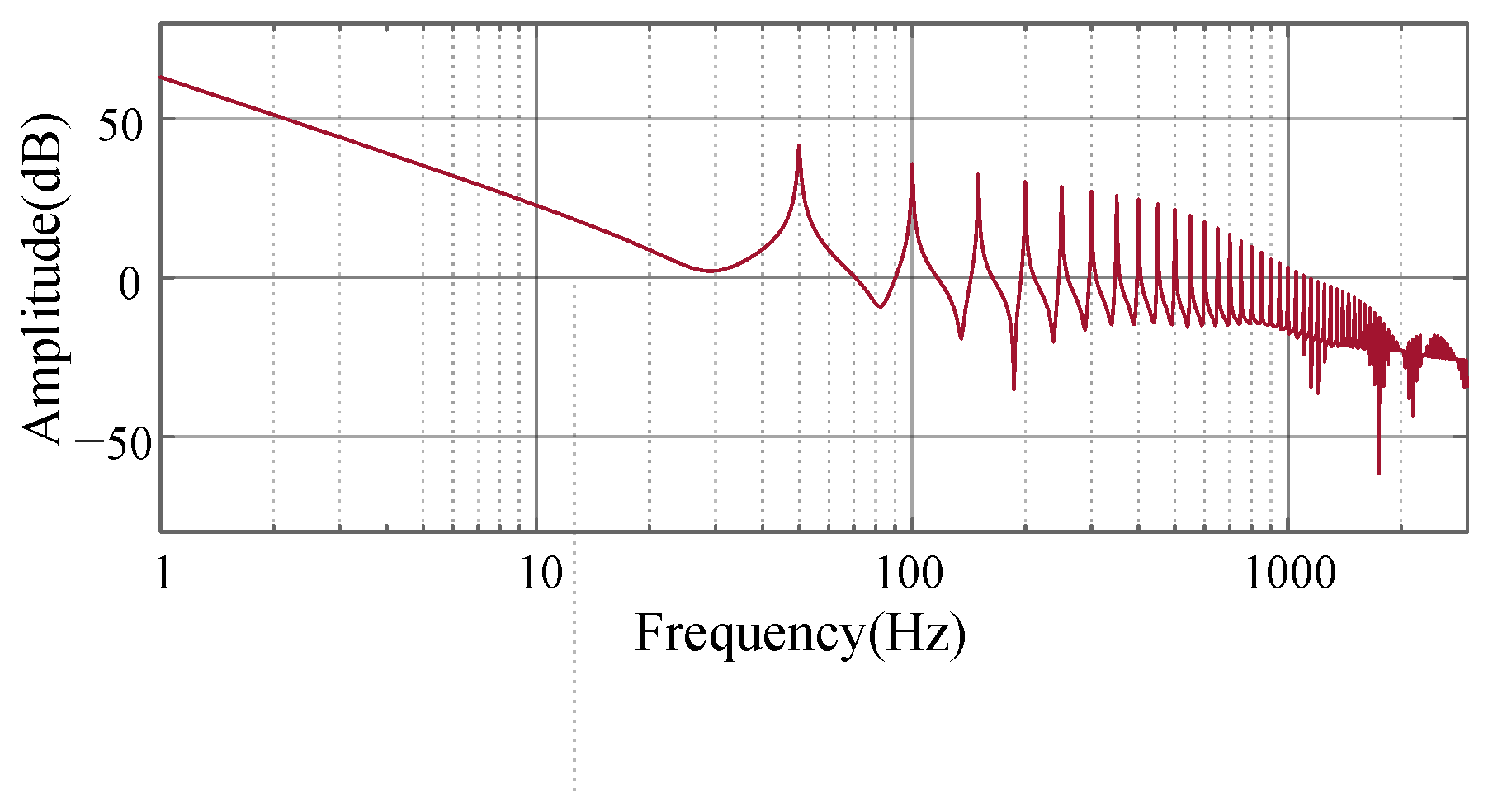

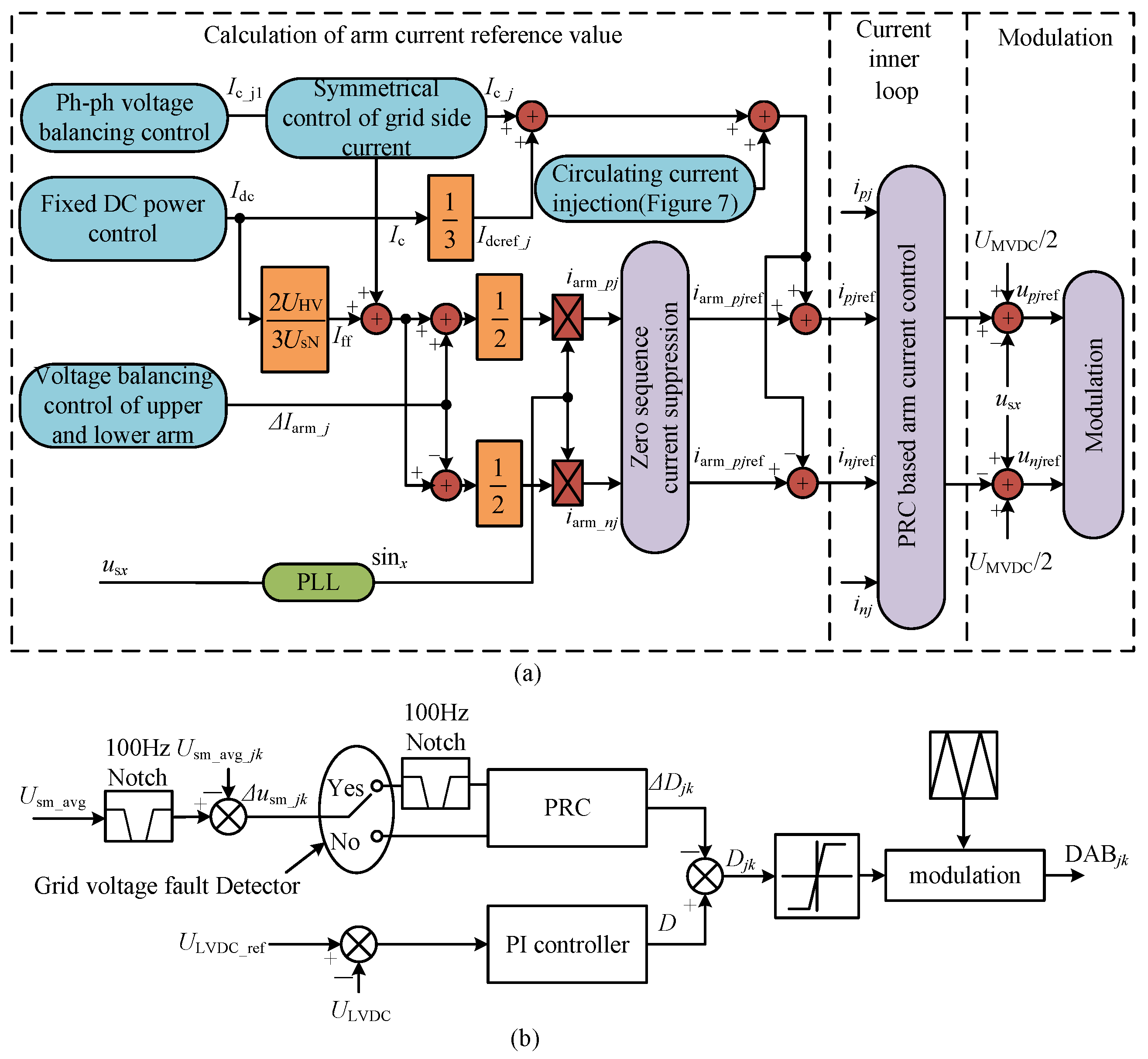

3.1. MMC-Based PRVS Strategy

- (1)

- Balance operation condition of the grid side voltage.

- (2)

- Unbalanced operation condition of the grid voltage

3.2. DAB-Based SRVS Strategy

3.3. Overall Control Strategy

4. Simulation Verification and Analysis

4.1. Balance Operation Condition of the Grid Side Voltage

4.2. Unbalanced Condition of the Grid Side Voltage

5. Conclusions

- This study proposed a modified MMC–PET topology with the ISHFC of upper and lower arms, which reduced the number of full-bridge modules and made the structure more compact.

- The MMC-based PRVS method coordinated with the DAB-based SRVS strategy based on PRC can provide real-time feedback correction for multiple frequency capacitor ripple voltages, and then the ripple power is transmitted to the LVDC bus by the DAB, significantly improving the suppression effect of voltage ripple in the submodule capacitor and second-order voltage ripple in the LVDC bus under normal and grid fault conditions. The second harmonic ripple voltage on the LVDC bus can be decreased from ±5 V to ±1 V with the proposed SRVS method under the asymmetric grid voltage condition.

- The proposed method can effectively eliminate the fundamental and second harmonic components of the submodule capacitor ripple voltage without increasing the current stress of the ISSS switch, thereby reducing the volume and cost of the device; simulation results showed that the peak-to-peak submodule capacitor ripple voltage was reduced from 232 V to 10 V, while the peak current of the isolation-stage secondary side (ISSS) switch was limited to 90 A.

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Núñez, R.A.; Posada, J.; Unsihuay-Vila, C.; Pinzón-Ardila, O. Review of Smart Transformer-Based Meshed Hybrid Microgrids: Shaping, Topology and Energy Management Systems. IEEE Access 2023, 11, 130165–130185. [Google Scholar]

- Deng, J.; Wang, X.; Tao, C.; Meng, F. An Energy Router Based on Multi-Hybrid Energy Storage System with Energy Coordinated Management Strategy in Island Operation Mode. Renew. Energy 2023, 212, 274–284. [Google Scholar] [CrossRef]

- Ma, D.; Chen, W.; Shu, L.; Qu, X.; Hou, K. A MMC-Based Multiport Power Electronic Transformer With Shared Medium-Frequency Transformer. IEEE Trans. Circuits Syst. II 2021, 68, 727–731. [Google Scholar] [CrossRef]

- Lu, S.; Deng, J.; Li, S.; Shao, Y.; Li, K. A Multiport Power Electronic Transformer Based on Three-Phase Four-Arm Full-Bridge Modular Multilevel Converter. IEEE Trans. Power Electron. 2024, 39, 16174–16186. [Google Scholar] [CrossRef]

- Li, Z.; Pei, Y.; Lu, C.; Wang, L.; Cao, W.; Leng, Z. An Analytical Closed-Loop Steady-State Model for Modular Multilevel Converters. IEEE Trans. Ind. Electron. 2025, 1–11. [Google Scholar] [CrossRef]

- Fawzi, M.; Abdelsalam, I.; Ahmed, A.A.; Maksoud, S.A.A. A Modified Phase Shift Control of the Dual Active Bridge-Based Modular Power Electronic Transformer to Minimize the LVdc Side Voltage Ripples Under Unbalanced Load Conditions. IEEE Access 2022, 10, 81309–81322. [Google Scholar] [CrossRef]

- Zhu, X.; Hou, J.; Zhang, B. A Multiport Power Electronic Transformer With MVDC Integration Interface for Multiple DC Units. IEEE Trans. Ind. Electron. 2024, 71, 10704–10715. [Google Scholar] [CrossRef]

- Zhou, J.; Zhang, J.; Wang, J.; Zang, J.; Shi, G.; Feng, X. Design and Control of Power Fluctuation Delivery for Cell Capacitance Optimization in Multiport Modular Solid-State Transformers. IEEE Trans. Power Electron. 2021, 36, 1412–1427. [Google Scholar] [CrossRef]

- Li, Z.; Pei, Y.; Wang, L.; Zhao, L.; Pei, L.; Cao, W. A Comprehensive Closed-Loop Voltage Ripple Control Scheme for Modular Multilevel Converter-Based Power Electronic Transformers. IEEE Trans. Power Electron. 2023, 38, 15225–15241. [Google Scholar] [CrossRef]

- Goudarzitaemeh, S.; Pahlevani, M. Extended Phase Shift Control of a Novel Bidirectional DC–DC Converter With Direct Power Transfer. IEEE J. Emerg. Sel. Top. Power Electron. 2024, 12, 4521–4537. [Google Scholar] [CrossRef]

- Liu, B.; Yu, T.; Ge, L.; Niu, J. Feedforward Compensation for Phase-Shifted Full-Bridge DC–DC Converter Under Peak Current Mode Control. IEEE Trans. Power Electron. 2024, 39, 6840–6851. [Google Scholar] [CrossRef]

- Akbar, S.M.; Hasan, A.; Watson, A.J.; Wheeler, P. Based Transformer Loss Analysis for Dual Active Bridge DC–DC Converter Using Triple Phase Shift Modulation. IEEE J. Emerg. Sel. Top. Power Electron. 2022, 10, 4347–4360. [Google Scholar] [CrossRef]

- Hu, Y.; Li, Z.; Zhang, H.; Zhao, C.; Gao, F.; Luo, L. High-Frequency-Link Current Stress Optimization of Cascaded H-Bridge-Based Solid-State Transformer With Third-Order Harmonic Voltage Injection. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 1027–1038. [Google Scholar] [CrossRef]

- Bandaru, T.; Samajdar, D.; Varma, P.B.S.; Bhattacharya, T.; Chatterjee, D. Optimum Injection of Second Harmonic Circulating Currents for Balancing Capacitor Voltages in Hybrid MMC during Reduced DC Voltage Conditions. IEEE Trans. Ind. Appl. 2020, 56, 1649–1660. [Google Scholar] [CrossRef]

- Xu, J.; Deng, W.; Gao, C.; Lu, F.; Liang, J.; Zhao, C. Dual Harmonic Injection for Reducing the Submodule Capacitor Voltage Ripples of Hybrid MMC. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 3622–3633. [Google Scholar] [CrossRef]

- Ou, Z.; Wang, G.; Zhang, L. Modular Multilevel Converter Control Strategy Based on Arm Current Control Under Unbalanced Grid Condition. IEEE Trans. Power Electron. 2018, 33, 3826–3836. [Google Scholar] [CrossRef]

- Liu, D.; Wang, G.; Ou, Z.; Liu, J. A Control Strategy of MMC Battery Energy Storage System Based on Arm Current Control. In Proceedings of the 2018 International Power Electronics Conference (IPEC-Niigata 2018 -ECCE Asia), Niigata, Japan, 20–24 May 2018; pp. 1376–1380. [Google Scholar]

- Song, Q.; Liu, W.; Li, X.; Rao, H.; Xu, S.; Li, L. A Steady-State Analysis Method for a Modular Multilevel Converter. IEEE Trans. Power Electron. 2013, 28, 3702–3713. [Google Scholar] [CrossRef]

- Vasiladiotis, M.; Cherix, N.; Rufer, A. Accurate Capacitor Voltage Ripple Estimation and Current Control Considerations for Grid-Connected Modular Multilevel Converters. IEEE Trans. Power Electron. 2014, 29, 4568–4579. [Google Scholar] [CrossRef]

| Parameters | Value in Improved DAB Phase Shift Modulation Strategy | Value in Arm Current Control |

|---|---|---|

| 200 | 200 | |

| 0.97 | 0.97 | |

| 11 | 3 | |

| 0.1 | 1.5 |

| Parameters | Value |

|---|---|

| Rated power /MW | 1.5 |

| Medium voltage AC line voltage/kV | 10 |

| Medium voltage DC voltage/kV | 20 |

| Number of arm submodules | 10 |

| Submodule DC voltage/V | 2000 |

| Submodule capacitance/μF | 600 |

| Arm inductance/mH | 10 |

| Grid side inductance/mH | 10 |

| Grid side resistance/ | 0.001 |

| Arm inductance/mH | 40 |

| Arm resistance/ | 0.05 |

| MMC submodule switching frequency/kHz | 1 |

| MMC modulation method | SPWM |

| Transformer isolation stage parameters | |

| Low voltage DC voltage/V | 750 |

| DAB switching frequency/kHz | 5 |

| DAB leakage inductance/mH | 0.5 |

| HFT conversion ratio | 2.67:1 |

| Low voltage DC-side capacitance/mF | 30 |

| Load resistance/ | 1.8 |

| Control parameters | |

| PI of Ph-ph voltage balancing control | 1, 40 |

| PI of Circulating current injection | 1.33, 41.6 |

| PI of Fixed DC power control | 0.003, 1000 |

| PI of voltage balancing control of upper and lower arm | 1.33, 41.6 |

| PI of LVDC voltage control | 0.03, 10 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lai, J.; Wu, Z.; Jia, X.; Wang, Y.; Liu, Y.; Zhu, X. Optimized Submodule Capacitor Ripple Voltage Suppression of an MMC-Based Power Electronic Transformer. Electronics 2025, 14, 2385. https://doi.org/10.3390/electronics14122385

Lai J, Wu Z, Jia X, Wang Y, Liu Y, Zhu X. Optimized Submodule Capacitor Ripple Voltage Suppression of an MMC-Based Power Electronic Transformer. Electronics. 2025; 14(12):2385. https://doi.org/10.3390/electronics14122385

Chicago/Turabian StyleLai, Jinmu, Zijian Wu, Xianyi Jia, Yaoqiang Wang, Yongxiang Liu, and Xinbing Zhu. 2025. "Optimized Submodule Capacitor Ripple Voltage Suppression of an MMC-Based Power Electronic Transformer" Electronics 14, no. 12: 2385. https://doi.org/10.3390/electronics14122385

APA StyleLai, J., Wu, Z., Jia, X., Wang, Y., Liu, Y., & Zhu, X. (2025). Optimized Submodule Capacitor Ripple Voltage Suppression of an MMC-Based Power Electronic Transformer. Electronics, 14(12), 2385. https://doi.org/10.3390/electronics14122385