A Low-Power Differential Temperature Sensor with Chopped Cascode Transistors and Switched-Capacitor Integration

Abstract

1. Introduction

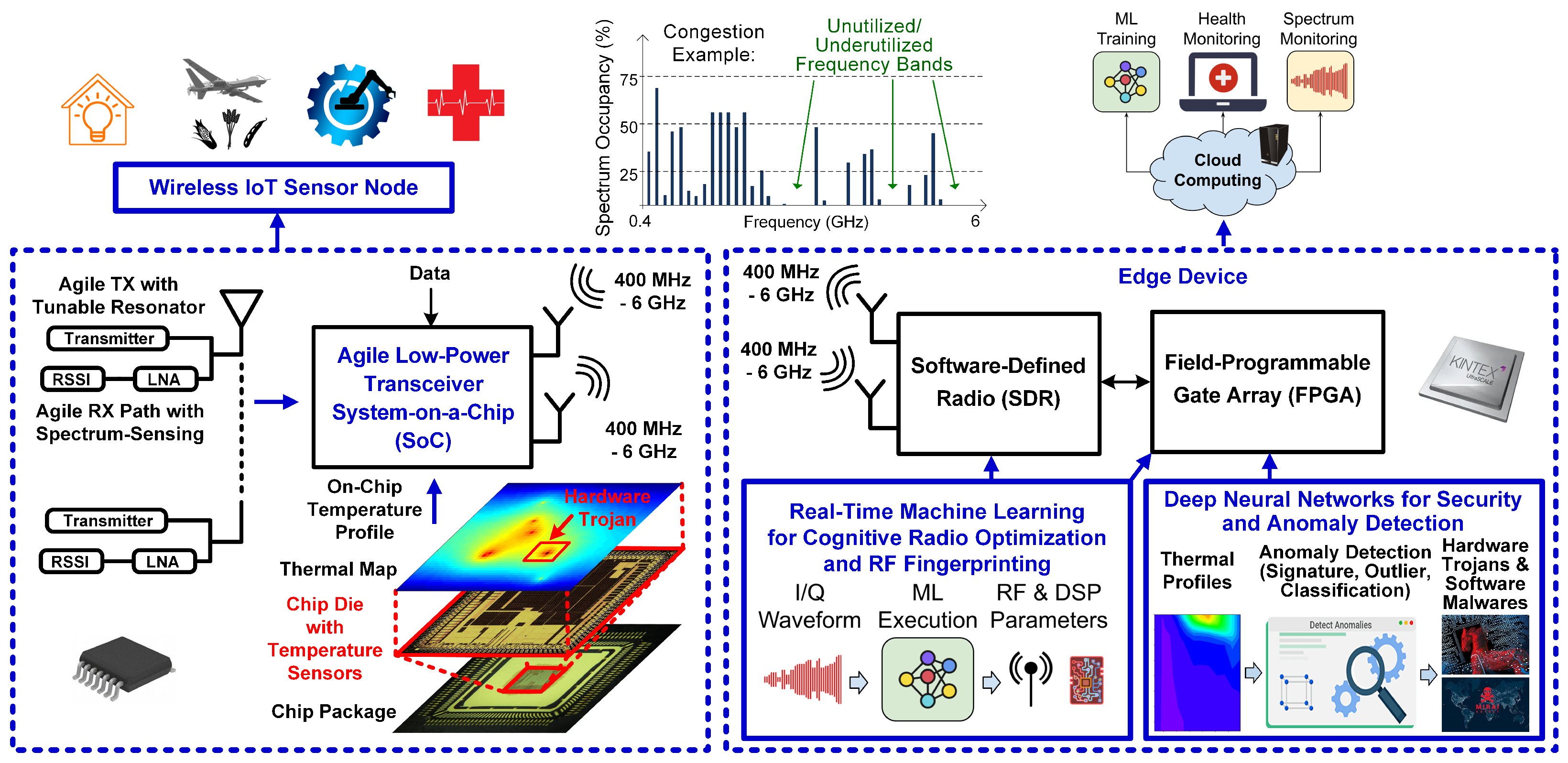

2. Target Application

3. Differential Temperature Sensor Design

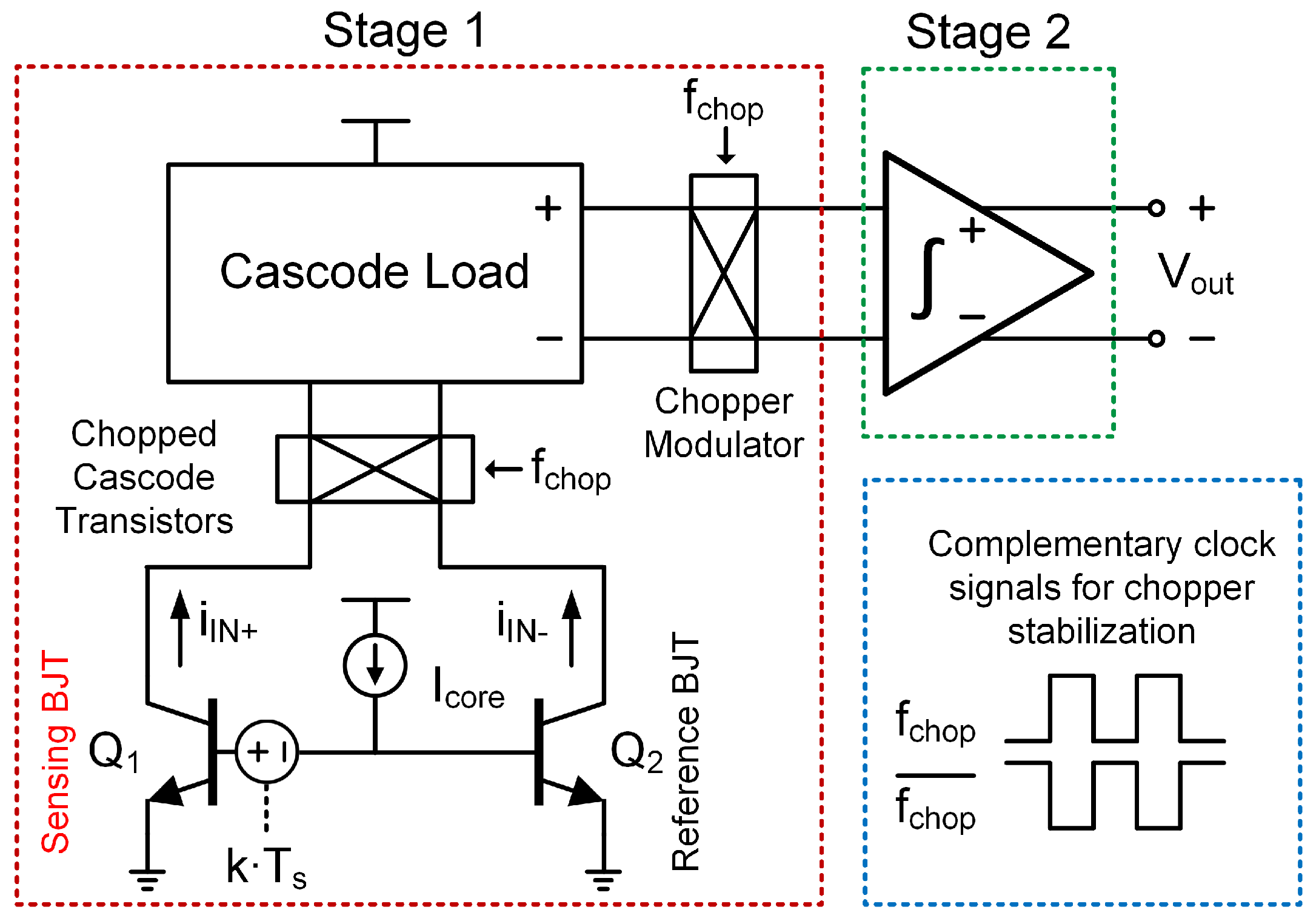

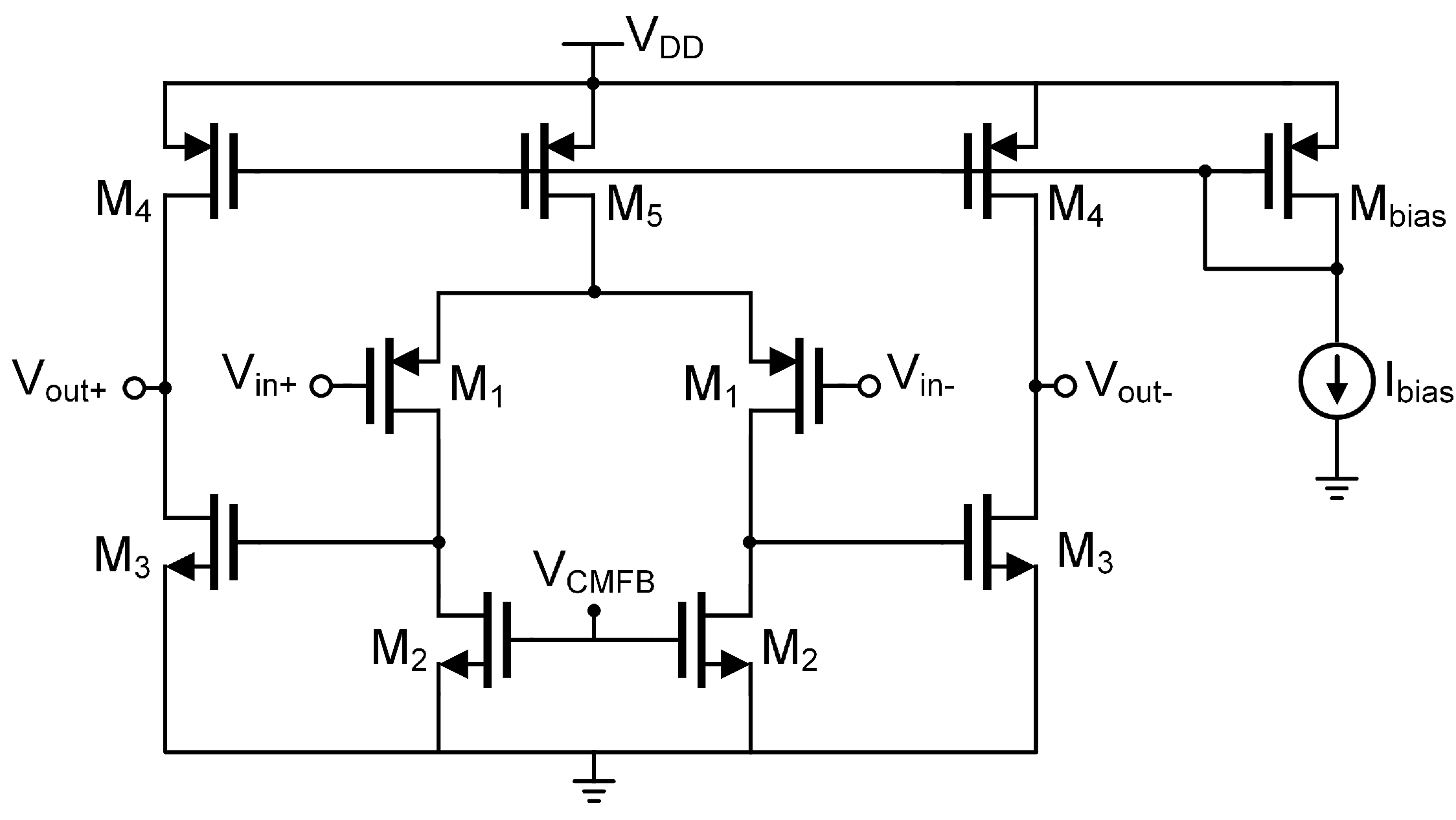

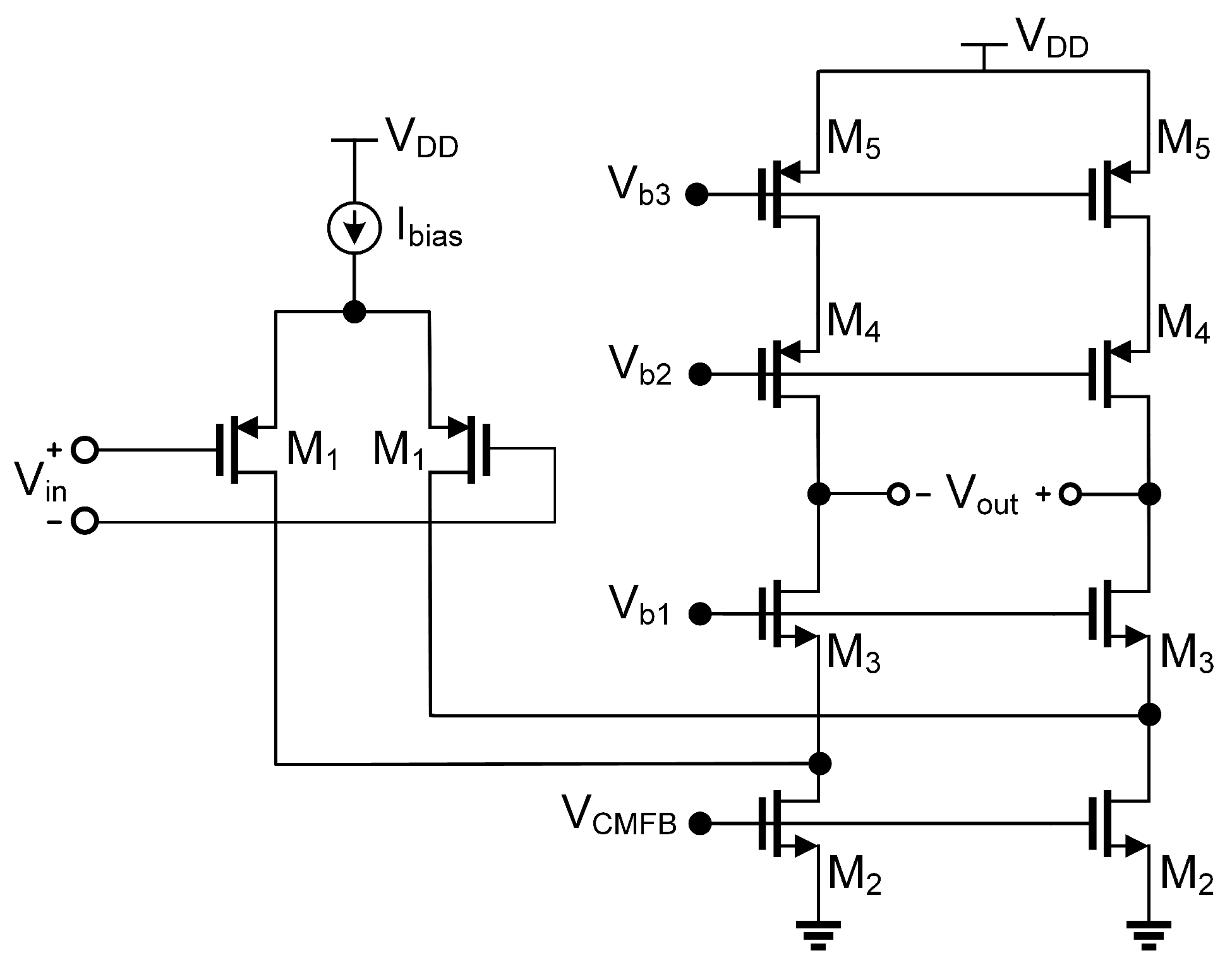

3.1. BJT-Based Cascode Differential Amplifier

3.2. Noise Analysis of the BJT-Based Cascode Differential Amplifier

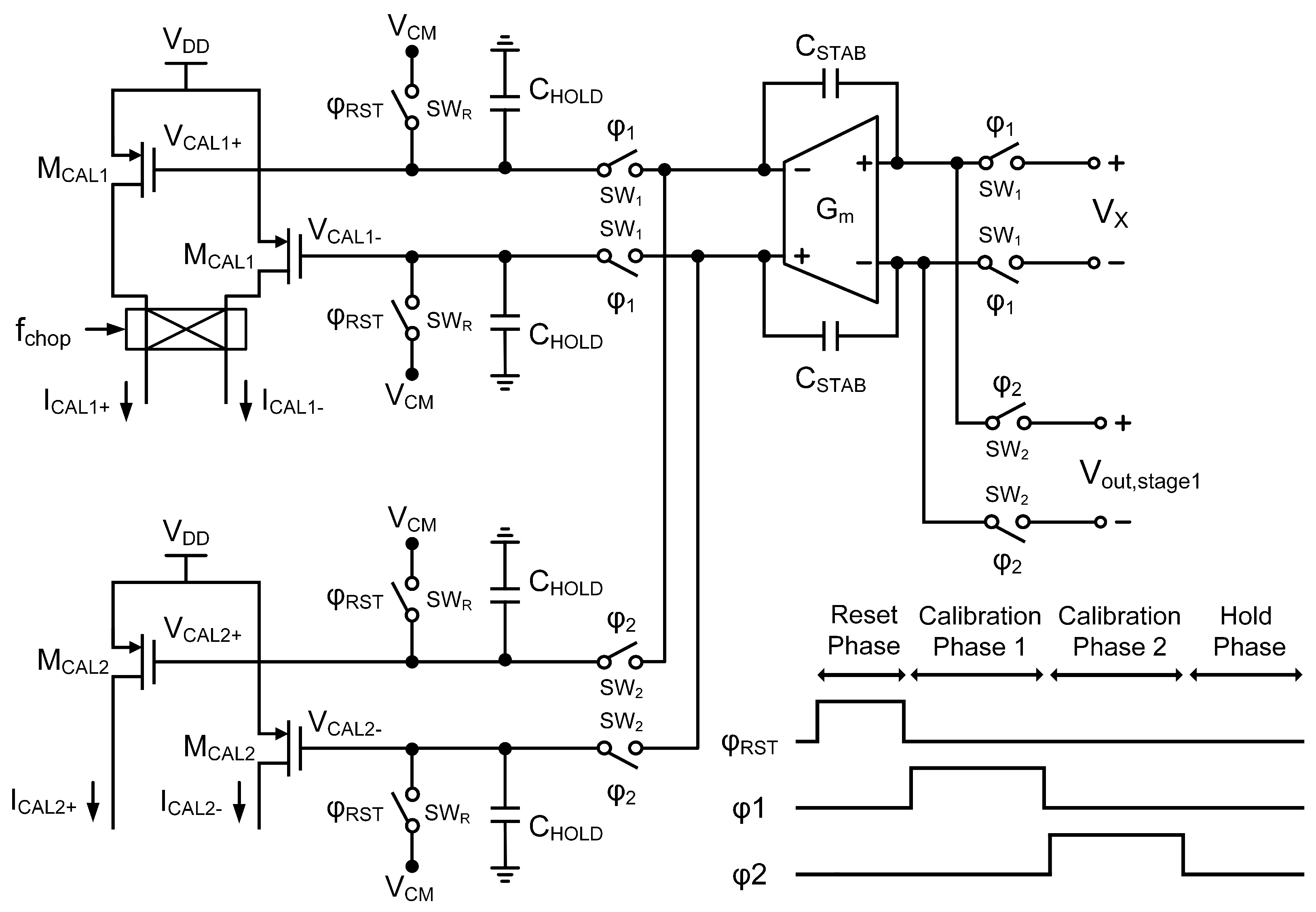

3.3. On-Chip Calibration Circuit

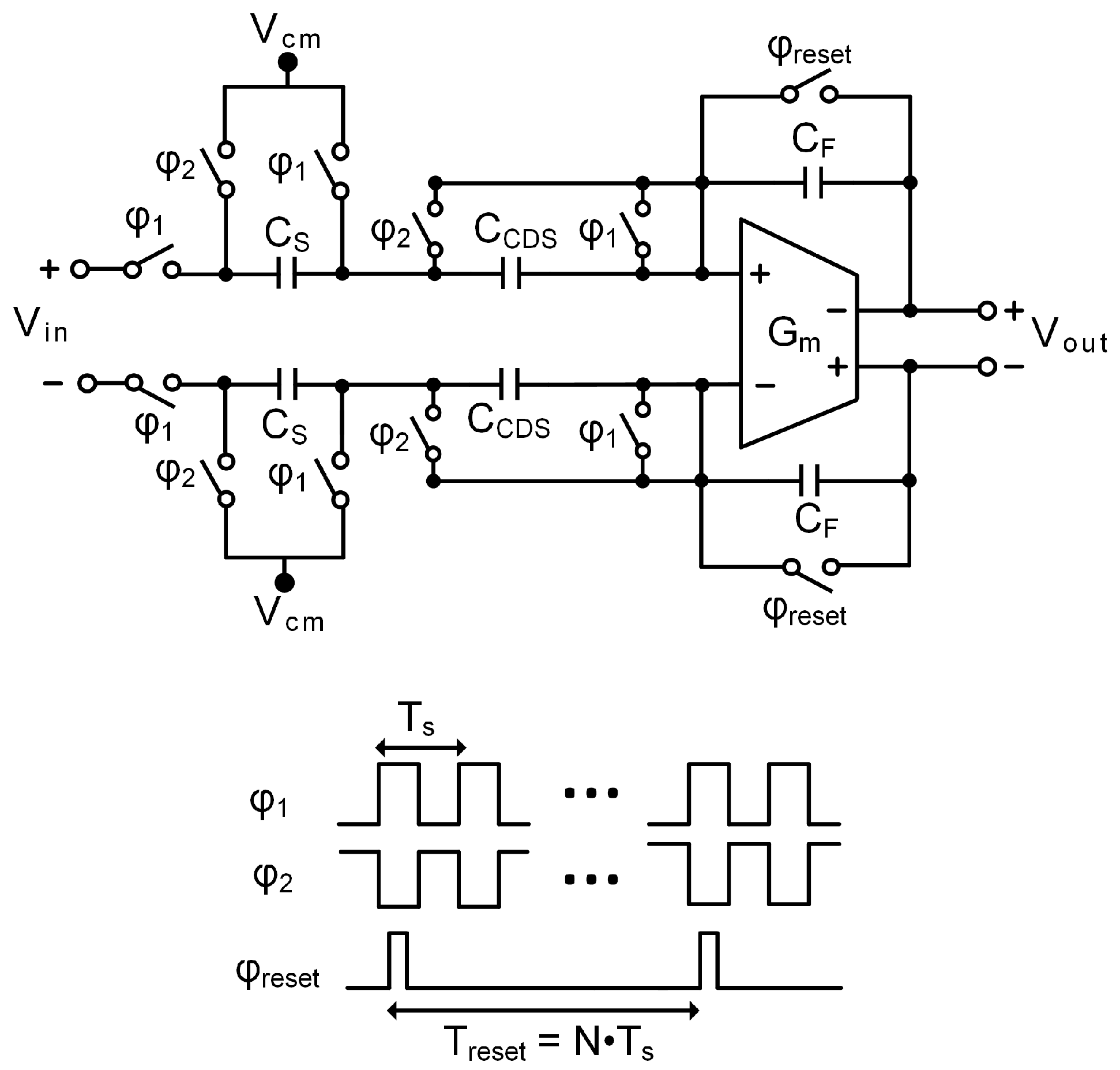

3.4. Switched-Capacitor Integrator with Reset

4. Simulation Results

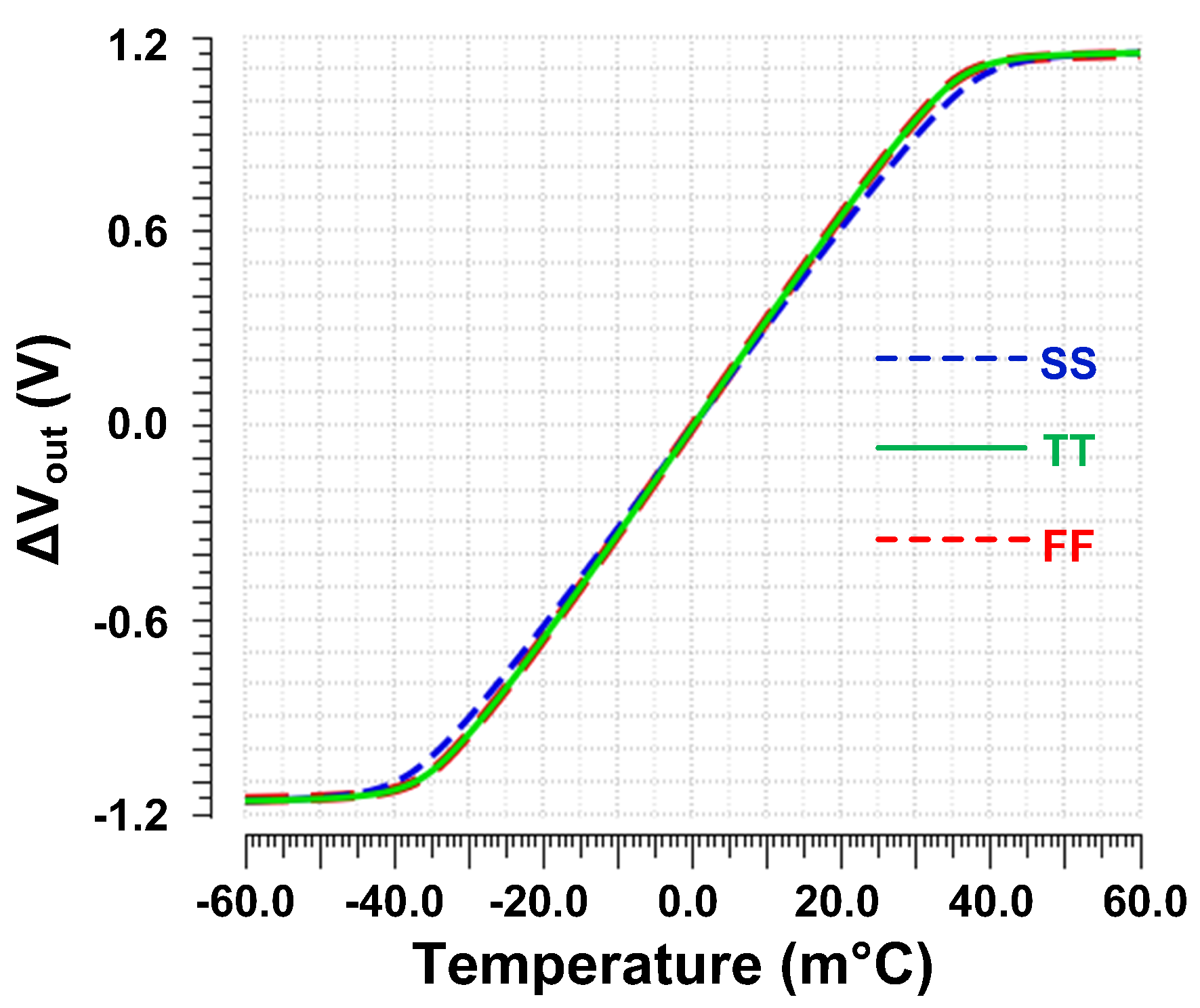

4.1. Evaluation of Stage 1

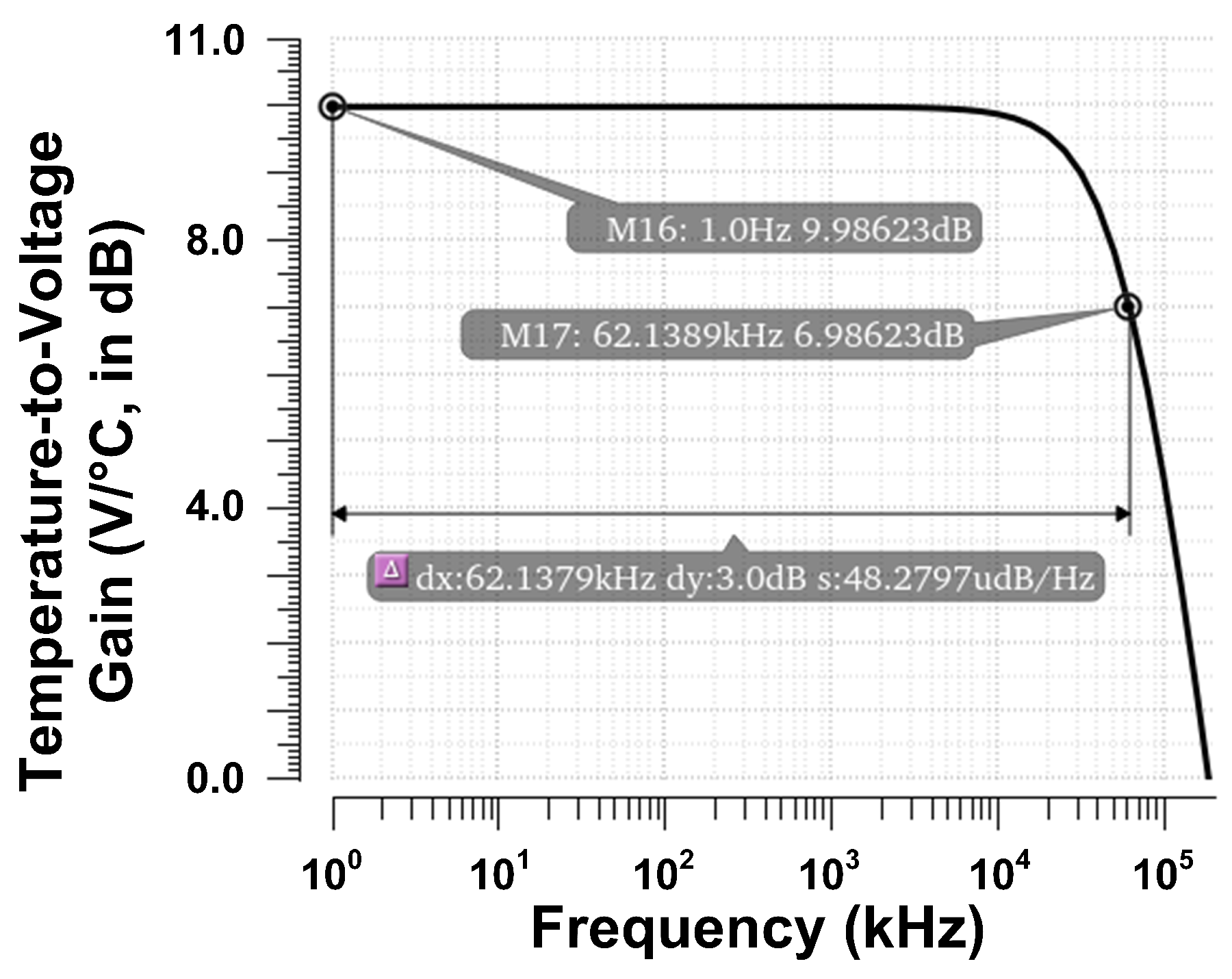

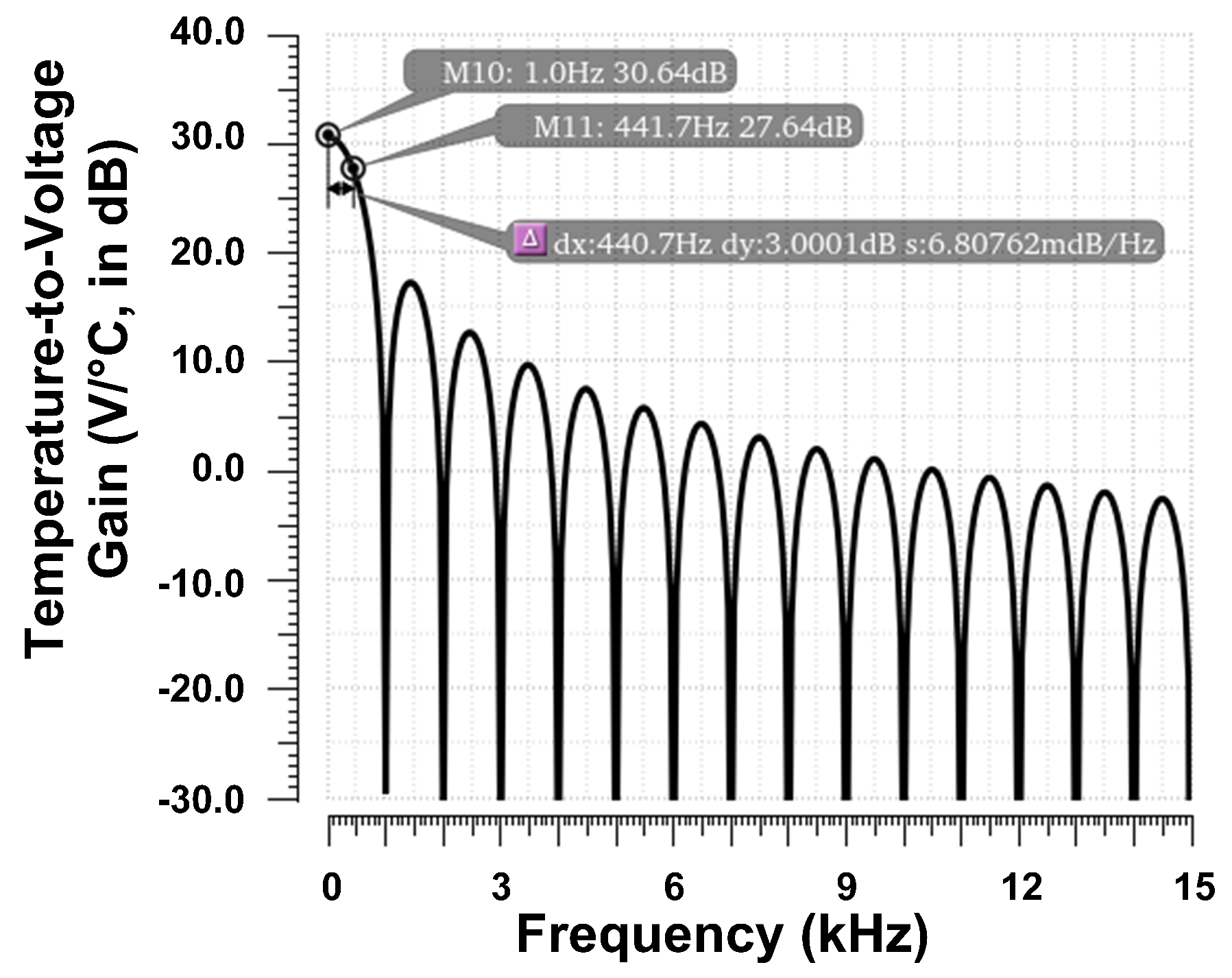

4.2. Frequency Response of the Differential Temperature Sensor

4.3. Noise Assessment

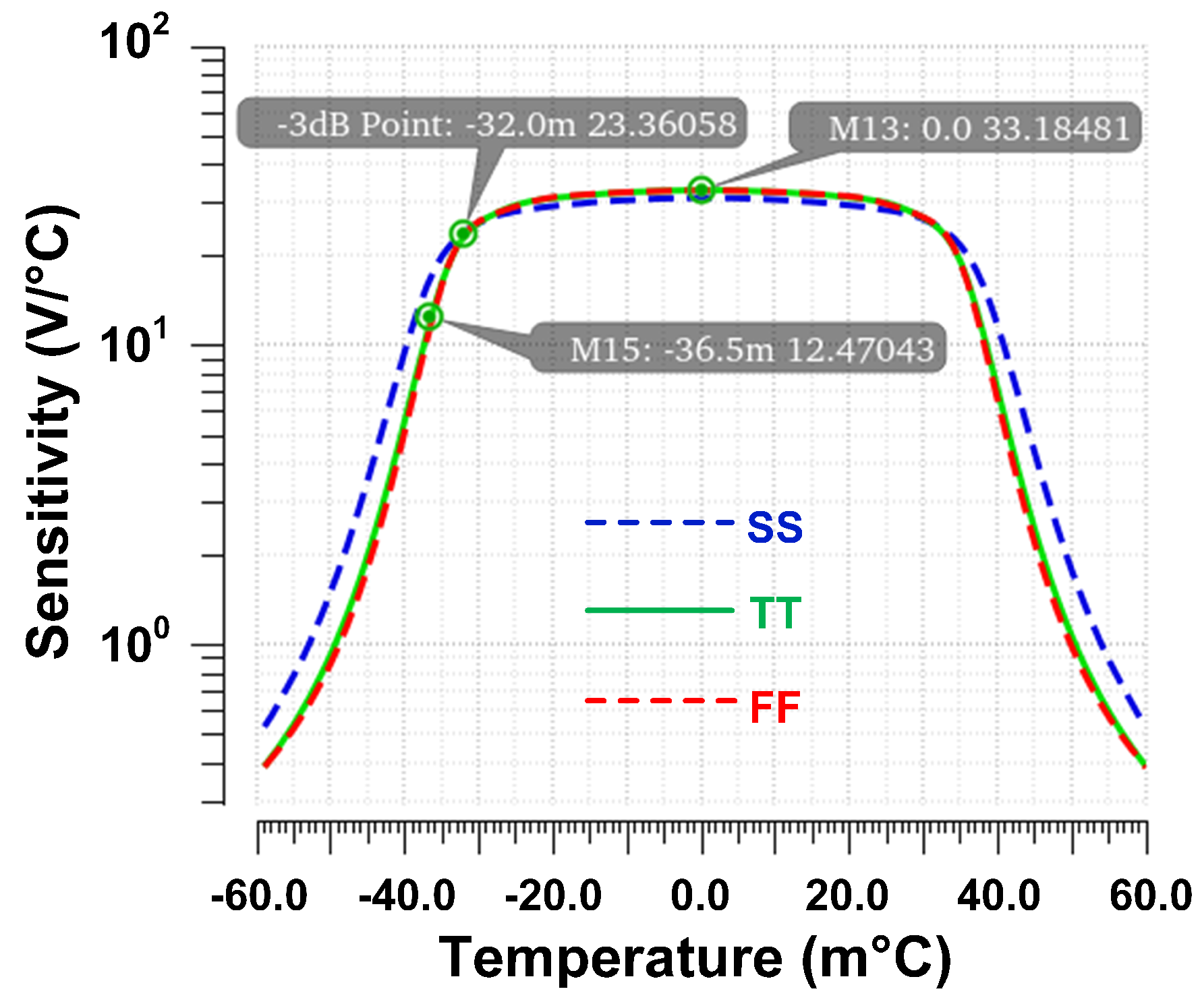

4.4. Sensitivity and Linear Range of the Proposed Differential Temperature Sensor

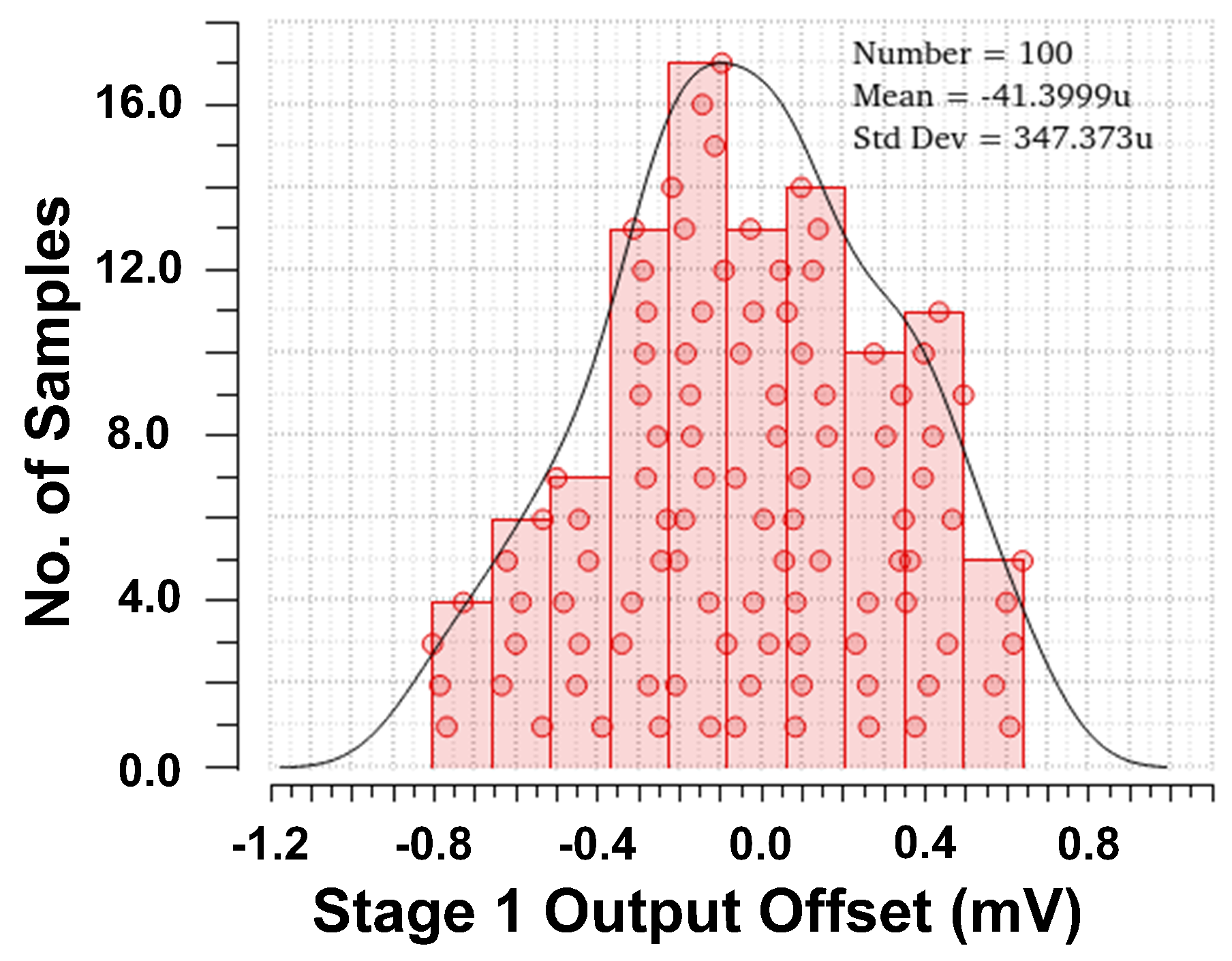

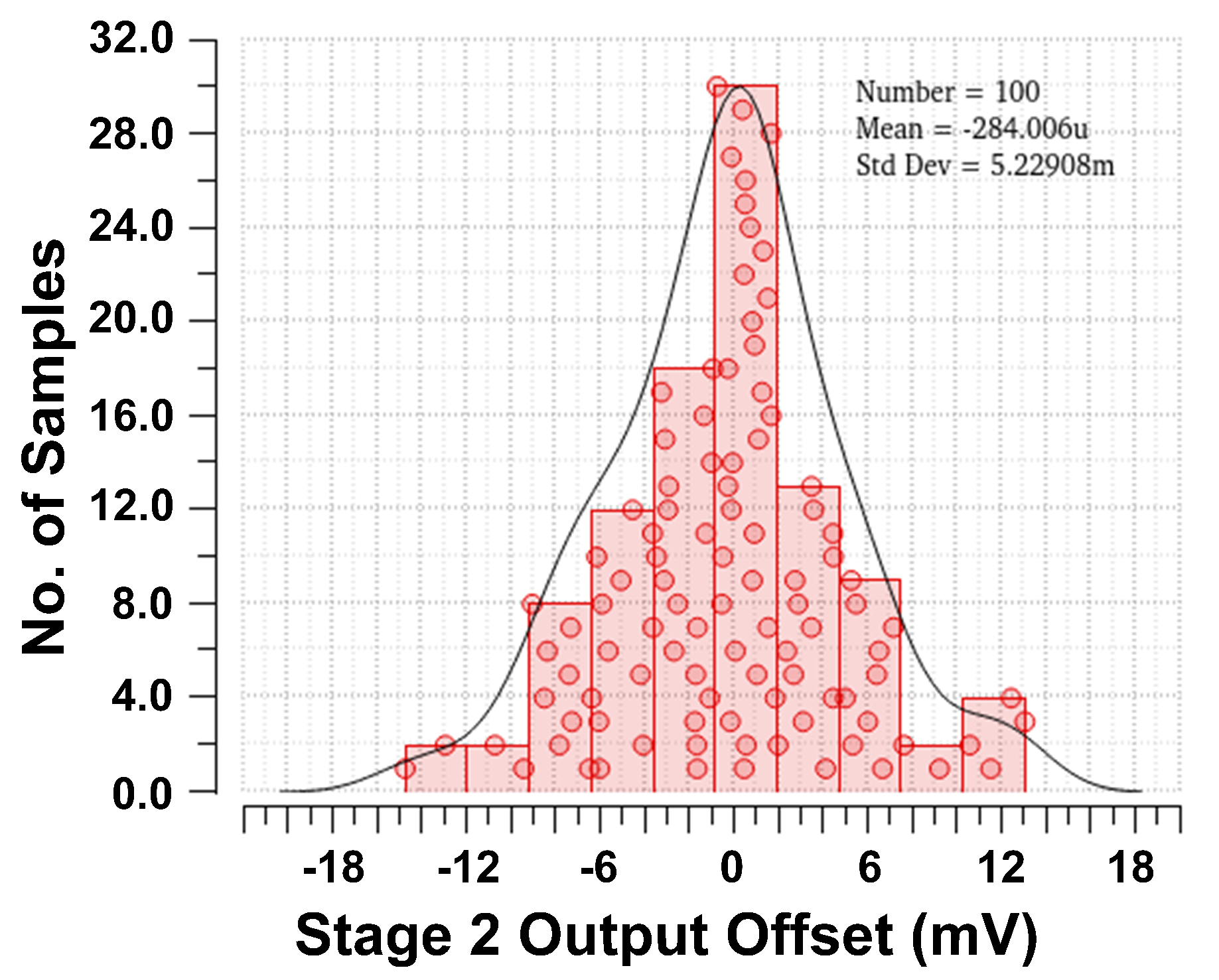

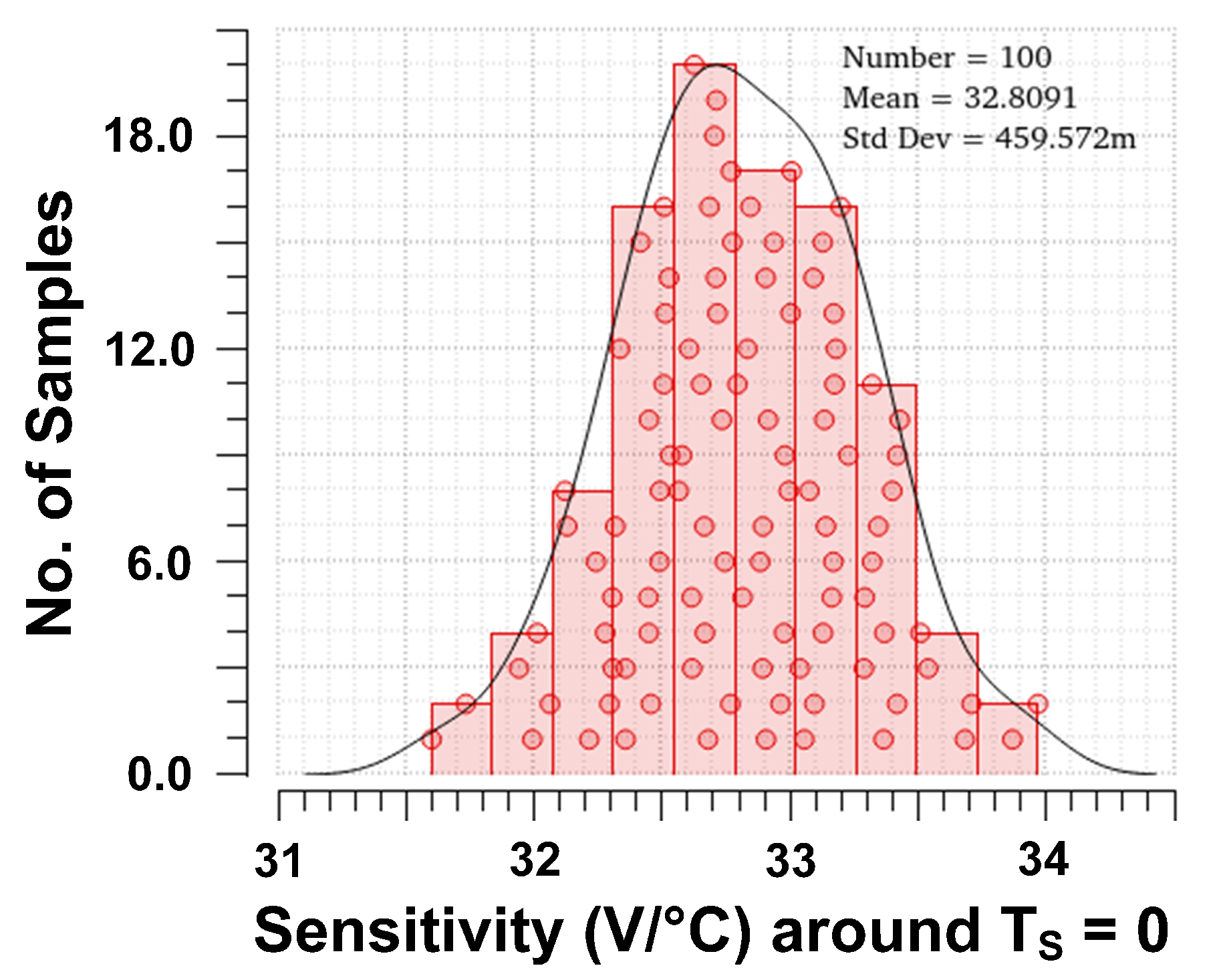

4.5. Monte Carlo Simulations

4.6. Discussion and Comparison with Other Works

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Altet, J.; Rubio, A.; Schaub, E.; Dilhaire, S.; Claeys, W. Thermal coupling in integrated circuits: Application to thermal testing. IEEE J. Solid-State Circuits 2001, 36, 81–91. [Google Scholar] [CrossRef]

- Altet, J.; Claeys, W.; Dilhaire, S.; Rubio, A. Dynamic surface temperature measurements in ICs. Proc. IEEE 2006, 94, 1519–1533. [Google Scholar] [CrossRef]

- Nenadovic, N.; Mijalkovic, S.; Nanver, L.K.; Vandamme, L.K.; d’Alessandro, V.; Schellevis, H.; Slotboom, J.W. Extraction and modeling of self-heating and mutual thermal coupling impedance of bipolar transistors. IEEE J. Solid-State Circuits 2004, 39, 1764–1772. [Google Scholar] [CrossRef]

- Mattisson, S.; Hagberg, H.; Andreani, P. Sensitivity degradation in a tri-band GSM BiCMOS direct-conversion receiver caused by transient substrate heating. IEEE J. Solid-State Circuits 2008, 43, 486–496. [Google Scholar] [CrossRef]

- Lee, S.S.; Allstot, D.J. Electrothermal simulation of integrated circuits. IEEE J. Solid-State Circuits 1993, 28, 1283–1293. [Google Scholar] [CrossRef]

- Mateo, D.; Aragones, X.; Barajas, E.; Martínez, S.; Gisbert, X.; Altet, J. High Sensitivity Temperature Measurements to Track and Compensate Aging Effects on CMOS Amplifiers. IEEE Trans. Device Mater. Reliab. 2024, 25, 11–16. [Google Scholar] [CrossRef]

- Abdallah, L.; Stratigopoulos, H.G.; Mir, S.; Altet, J. Defect-oriented non-intrusive RF test using on-chip temperature sensors. In Proceedings of the IEEE 31st VLSI Test Symposium (VTS), Berkeley, CA, USA, 29 April–2 May 2013. [Google Scholar] [CrossRef]

- Aragones, X.; Mateo, D.; González, J.; Vidal, E.; Gómez, D.; Martineau, B.; Altet, J. DC temperature measurements to characterize the central frequency and 3 dB bandwidth in mmW power amplifiers. IEEE Microw. Wirel. Components Lett. 2015, 25, 745–747. [Google Scholar] [CrossRef]

- Altet, J.; Mateo, D.; Gómez, D.; González Jiménez, J.L.; Martineau, B.; Siligaris, A.; Aragones, X. Temperature Sensors to Measure the Central Frequency and 3 dB Bandwidth in mmW Power Amplifiers. IEEE Microw. Wirel. Components Lett. 2014, 24, 272–274. [Google Scholar] [CrossRef]

- Onabajo, M.; Altet, J.; Aldrete-Vidrio, E.; Mateo, D.; Silva-Martinez, J. Electrothermal Design Procedure to Observe RF Circuit Power and Linearity Characteristics With a Homodyne Differential Temperature Sensor. IEEE Trans. Circuits Syst. I Reg. Pap. 2011, 58, 458–469. [Google Scholar] [CrossRef]

- Wei, H.; Yan, M.; Onabajo, M. Noise reduction via chopper stabilization of fully differential temperature sensors for hardware security applications. In Proceedings of the IEEE 14th Dallas Circuits and Systems Conference (DCAS), Dallas, TX, USA, 15–16 November 2020. [Google Scholar] [CrossRef]

- Yan, M.; Wei, H.; Onabajo, M. On-Chip Thermal Profiling to Detect Malicious Activity: System-Level Concepts and Design of Key Building Blocks. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2021, 29, 530–543. [Google Scholar] [CrossRef]

- Yan, M.; Gourousis, T.; Onabajo, M. On-Chip Power Monitoring: Leveraging High-Sensitivity Differential Temperature Sensors with Chopper Stabilization and Offset Calibration. IEEE Trans. Instrum. Meas. 2024, 73, 2002404. [Google Scholar] [CrossRef]

- Aprile, A.; Moisello, E.; Bonizzoni, E.; Malcovati, P. Performance comparison of BJT and MOS devices as temperature sensing elements. In Proceedings of the IEEE 29th International Conference on Electronics, Circuits and Systems (ICECS), Glasgow, UK, 24–26 October 2022. [Google Scholar] [CrossRef]

- Altet, J.; Barajas, E.; Mateo, D.; Billong, A.; Aragones, X.; Perpiñà, X.; Reverter, F. BPF-based thermal sensor circuit for on-chip testing of RF circuits. Sensors 2021, 21, 805. [Google Scholar] [CrossRef] [PubMed]

- Reverter, F.; Altet, J. On-chip thermal testing using MOSFETs in weak inversion. IEEE Trans. Instrum. Meas. 2014, 64, 524–532. [Google Scholar] [CrossRef]

- Sengupta, K.; Dasgupta, K.; Bowers, S.M.; Hajimiri, A. On-chip sensing and actuation methods for integrated self-healing mm-wave CMOS power amplifier. In Proceedings of the IEEE/MTT-S International Microwave Symposium Digest, Montreal, QC, Canada, 17–22 June 2012. [Google Scholar] [CrossRef]

- Nowroz, A.N.; Hu, K.; Koushanfar, F.; Reda, S. Novel techniques for high-sensitivity hardware Trojan detection using thermal and power maps. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2014, 33, 1792–1805. [Google Scholar] [CrossRef]

- Cao, Y.; Chang, C.H.; Chen, S. A cluster-based distributed active current sensing circuit for hardware Trojan detection. IEEE Trans. Inf. Forensics Secur. 2014, 9, 2220–2231. [Google Scholar] [CrossRef]

- Gourousis, T.; Zhang, Z.; Yan, M.; Zhang, M.; Mittal, A.; Shrivastava, A.; Restuccia, F.; Fei, Y.; Onabajo, M. Identification of Stealthy Hardware Trojans through On-Chip Temperature Sensing and an Autoencoder-Based Machine Learning Algorithm. In Proceedings of the IEEE 66st International Midwest Symposium on Circuits and Systems (MWSCAS), Tempe, AZ, USA, 6–9 August 2023. [Google Scholar] [CrossRef]

- Mittal, A.; Zhang, M.; Gourousis, T.; Zhang, Z.; Fei, Y.; Onabajo, M.; Restuccia, F.; Shrivastava, A. Sub-6 GHz energy detection-based fast on-chip analog spectrum sensing with learning-driven signal classification. IEEE Internet Things J. 2024, 11, 2503–25046. [Google Scholar] [CrossRef]

- Ba, A.; Liu, Y.H.; van den Heuvel, J.; Mateman, P.; Büsze, B.; Dijkhuis, J.; Bachmann, C.; Dolmans, G.; Philips, K.; De Groot, H. A 1.3 nJ/b IEEE 802.11ah fully-digital polar transmitter for IoT applications. IEEE J. Solid-State Circuits 2016, 51, 3103–3113. [Google Scholar] [CrossRef]

- Liu, D.; Ni, X.; Zhou, R.; Rhee, W.; Wang, Z. A 0.42-mW 1-Mb/s 3-to-4-GHz transceiver in 0.18-μm CMOS with flexible efficiency, bandwidth, and distance control for IoT applications. IEEE J. Solid-State Circuits 2017, 52, 1479–1494. [Google Scholar] [CrossRef]

- Tang, K.; Yang, C.; Guo, Y.; Wang, N.; Zhu, Y.; Zhang, Y.; Ng, E.J.; Lee, J.E.Y.; Fang, Z.; Wang, W.; et al. A 107 pJ/b TX 260 pJ/b RX ultralow-power MEMS-based transceiver with wake-up in ISM-bands for IoT applications. IEEE J. Solid-State Circuits 2022, 58, 1337–1349. [Google Scholar] [CrossRef]

- Yi, H.; Yu, W.H.; Mak, P.I.; Yin, J.; Martins, R.P. A 0.18-V 382-μW Bluetooth Low-Energy receiver front-end with 1.33-nW sleep power for energy-harvesting applications in 28-nm CMOS. IEEE J. Solid-State Circuits 2018, 53, 1618–1627. [Google Scholar] [CrossRef]

- Yan, M.; Wei, H.; Onabajo, M. Modeling of thermal coupling and temperature sensor circuit design considerations for hardware Trojan detection. In Proceedings of the IEEE 61st International Midwest Symposium on Circuits and Systems (MWSCAS), Windsor, ON, Canada, 5–8 August 2018. [Google Scholar] [CrossRef]

- Osipov, D.; Paul, S. Temperature-Compensated β -Multiplier Current Reference Circuit. IEEE Trans. Circuits Syst. II Express Briefs 2017, 64, 1162–1166. [Google Scholar] [CrossRef]

- Ivanov, V.; Brederlow, R.; Gerber, J. An ultra low power bandgap operational at supply from 0.75 V. IEEE J. Solid-State Circuits 2012, 47, 1515–1523. [Google Scholar] [CrossRef]

- Ji, Y.; Lee, J.; Kim, B.; Park, H.J.; Sim, J.Y. A 192-pW Voltage Reference Generating Bandgap—Vth With Process and Temperature Dependence Compensation. IEEE J. Solid-State Circuits 2019, 54, 3281–3291. [Google Scholar] [CrossRef]

- Vita, G.D. A Sub 1-V, 10 ppm/℃, Nanopower Voltage Reference Generator. IEEE J. Solid-State Circuits 2007, 42, 1536–1542. [Google Scholar] [CrossRef]

- Fiori, F.; Crovetti, P.S. A new compact temperature-compensated CMOS current reference. IEEE Trans. Circuits Syst. II Express Briefs 2005, 52, 724–728. [Google Scholar] [CrossRef]

- Lee, J.; Cho, S. A 1.4-μW 24.9-ppm/°C current reference with process-insensitive temperature compensation in 0.18-μm CMOS. IEEE J. Solid-State Circuits 2012, 47, 2527–2533. [Google Scholar] [CrossRef]

- Razavi, B. Design of Analog CMOS Integrated Circuits, 2nd ed.; McGraw-Hill Education: New York, NY, USA, 2016; 254p. [Google Scholar]

- Gray, P.R.; Hurst, P.J.; Lewis, S.H.; Meyer, R.G. Analysis and Design of Analog Integrated Circuits, 5th ed.; John Wiley & Sons: Hoboken, NJ, USA, 2009; 745p. [Google Scholar]

- Enz, C.; Temes, G. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. Proc. IEEE 1996, 84, 1584–1614. [Google Scholar] [CrossRef]

- Oh, W.; Bakkaloglu, B.; Wang, C.; Hoon, S.K. A CMOS low noise, chopper stabilized low-dropout regulator with current-mode feedback error amplifier. IEEE Trans. Circuits Syst. I Regul. Pap. 2008, 55, 3006–3015. [Google Scholar] [CrossRef]

- Wu, J.; Law, M.K.; Mak, P.I.; Martins, R.P. A 2-μW, 45-nV/Hz Readout Front End With Multiple-Chopping Active-High-Pass Ripple Reduction Loop and Pseudofeedback DC Servo Loop. IEEE Trans. Circuits Syst. II Express Briefs 2015, 63, 351–355. [Google Scholar] [CrossRef]

- Yang, T.; Lu, J.; Poore, N.; Holleman, J. A current-reuse complementary-input chopper-stabilized amplifier for neural recording. In Proceedings of the IEEE 12th International New Circuits and Systems Conference (NEWCAS), Trois-Rivieres, QC, Canada, 22–25 June 2014. [Google Scholar] [CrossRef]

- Enz, C.C.; Vittoz, E.A.; Krummenacher, F. A CMOS chopper amplifier. IEEE J. Solid-State Circuits 1987, 22, 335–342. [Google Scholar] [CrossRef]

- Carusone, T.C.; Johns, D.A.; Martin, K.W. Analog Integrated Circuit Design; John Wiley & Sons: Hoboken, NJ, USA, 2011. [Google Scholar]

- Xu, G.; Yuan, J. Performance analysis of general charge sampling. IEEE Trans. Circuits Syst. II Express Briefs 2005, 52, 107–111. [Google Scholar] [CrossRef]

- Jiang, W.; Zhu, Y.; Chan, C.H.; Murmann, B.; Martins, R.P. A 7-bit 2 GS/s time-interleaved SAR ADC with timing skew calibration based on current integrating sampler. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 68, 557–568. [Google Scholar] [CrossRef]

- Gregorian, R.; Martin, K.W.; Temes, G.C. Switched-capacitor circuit design. Proc. IEEE 1983, 71, 941–966. [Google Scholar] [CrossRef]

- Liu, J.; Allstot, D.J. A Chopper-Stabilized Switched-Capacitor Front-End for Peripheral Nervous System Recording. IEEE Trans. Circuits Syst. I Regul. Pap. 2023, 70, 3065–3074. [Google Scholar] [CrossRef]

- Liu, J.; Walker, R.M. A compact, low-noise, chopped front-end for peripheral nerve recording in 180 nm CMOS. In Proceedings of the 2018 IEEE Biomedical Circuits and Systems Conference (BioCAS), Cleveland, OH, USA, 17–19 October 2018. [Google Scholar] [CrossRef]

- Oliaei, O. Noise analysis of correlated double sampling SC integrators with a hold capacitor. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 2003, 50, 1198–1202. [Google Scholar] [CrossRef]

- Chen, H.L.; Chen, P.S.; Chiang, J.S. A low-offset low-noise sigma-delta modulator with pseudorandom chopper-stabilization technique. IEEE Trans. Circuits Syst. I Regul. Pap. 2009, 56, 2533–2543. [Google Scholar] [CrossRef]

- Belloni, M.; Bonizzoni, E.; Fornasari, A.; Maloberti, F. A micropower chopper—CDS operational amplifier. IEEE J. Solid-State Circuits 2010, 45, 2521–2529. [Google Scholar] [CrossRef]

- Mallya, S.; Nevin, J.H. Design procedures for a fully differential folded-cascode CMOS operational amplifier. IEEE J. Solid-State Circuits 2002, 24, 1737–1740. [Google Scholar] [CrossRef]

| Parameter | This Work | [9] | [11] | [12] |

|---|---|---|---|---|

| Technology (nm) | 65 | 65 | 130 | 130 |

| Sensitivity () | 33.18 | 0.6 | 2.09 | 840 |

| Linear Range () | ±36.5 | ±600 | ±210 | ±1 |

| Integrated Output Noise [1– Hz] () | 0.862 | n/a | 0.38 | 60 |

| Power Consumption (mW) | 0.187 | 0.1368 | 1.08 | 1.452 |

| (1/mW) | 7513 | n/a | 1069 | 9.64 |

| (V/mW) | 6.476 | 2.632 | 0.406 | 0.579 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Yang, J.; Gourousis, T.; Yan, M.; Ding, R.; Mittal, A.; Zhang, M.; Restuccia, F.; Shrivastava, A.; Fei, Y.; Onabajo, M. A Low-Power Differential Temperature Sensor with Chopped Cascode Transistors and Switched-Capacitor Integration. Electronics 2025, 14, 2381. https://doi.org/10.3390/electronics14122381

Yang J, Gourousis T, Yan M, Ding R, Mittal A, Zhang M, Restuccia F, Shrivastava A, Fei Y, Onabajo M. A Low-Power Differential Temperature Sensor with Chopped Cascode Transistors and Switched-Capacitor Integration. Electronics. 2025; 14(12):2381. https://doi.org/10.3390/electronics14122381

Chicago/Turabian StyleYang, Junyi, Thomas Gourousis, Mengting Yan, Ruyi Ding, Ankit Mittal, Milin Zhang, Francesco Restuccia, Aatmesh Shrivastava, Yunsi Fei, and Marvin Onabajo. 2025. "A Low-Power Differential Temperature Sensor with Chopped Cascode Transistors and Switched-Capacitor Integration" Electronics 14, no. 12: 2381. https://doi.org/10.3390/electronics14122381

APA StyleYang, J., Gourousis, T., Yan, M., Ding, R., Mittal, A., Zhang, M., Restuccia, F., Shrivastava, A., Fei, Y., & Onabajo, M. (2025). A Low-Power Differential Temperature Sensor with Chopped Cascode Transistors and Switched-Capacitor Integration. Electronics, 14(12), 2381. https://doi.org/10.3390/electronics14122381