A Novel Enhancement-Mode Gallium Nitride p-Channel Metal Insulator Semiconductor Field-Effect Transistor with a Buried Back Gate for Gallium Nitride Single-Chip Complementary Logic Circuits

Abstract

1. Introduction

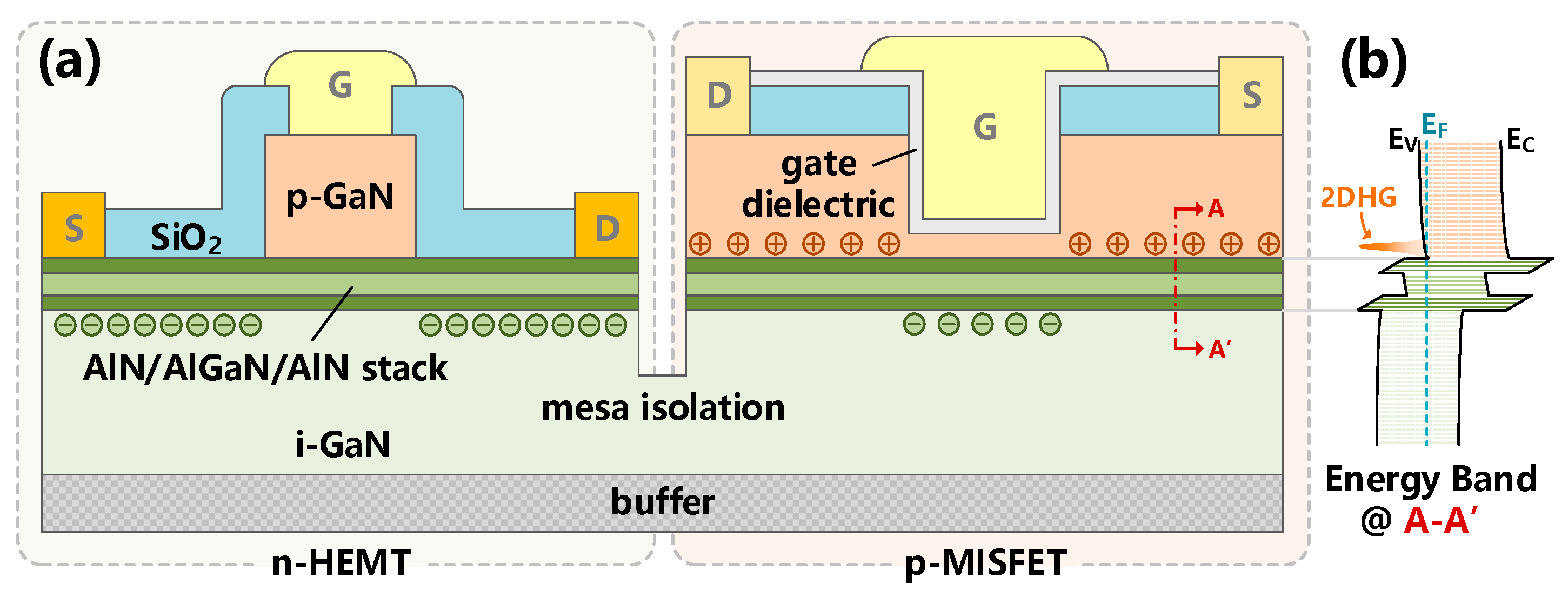

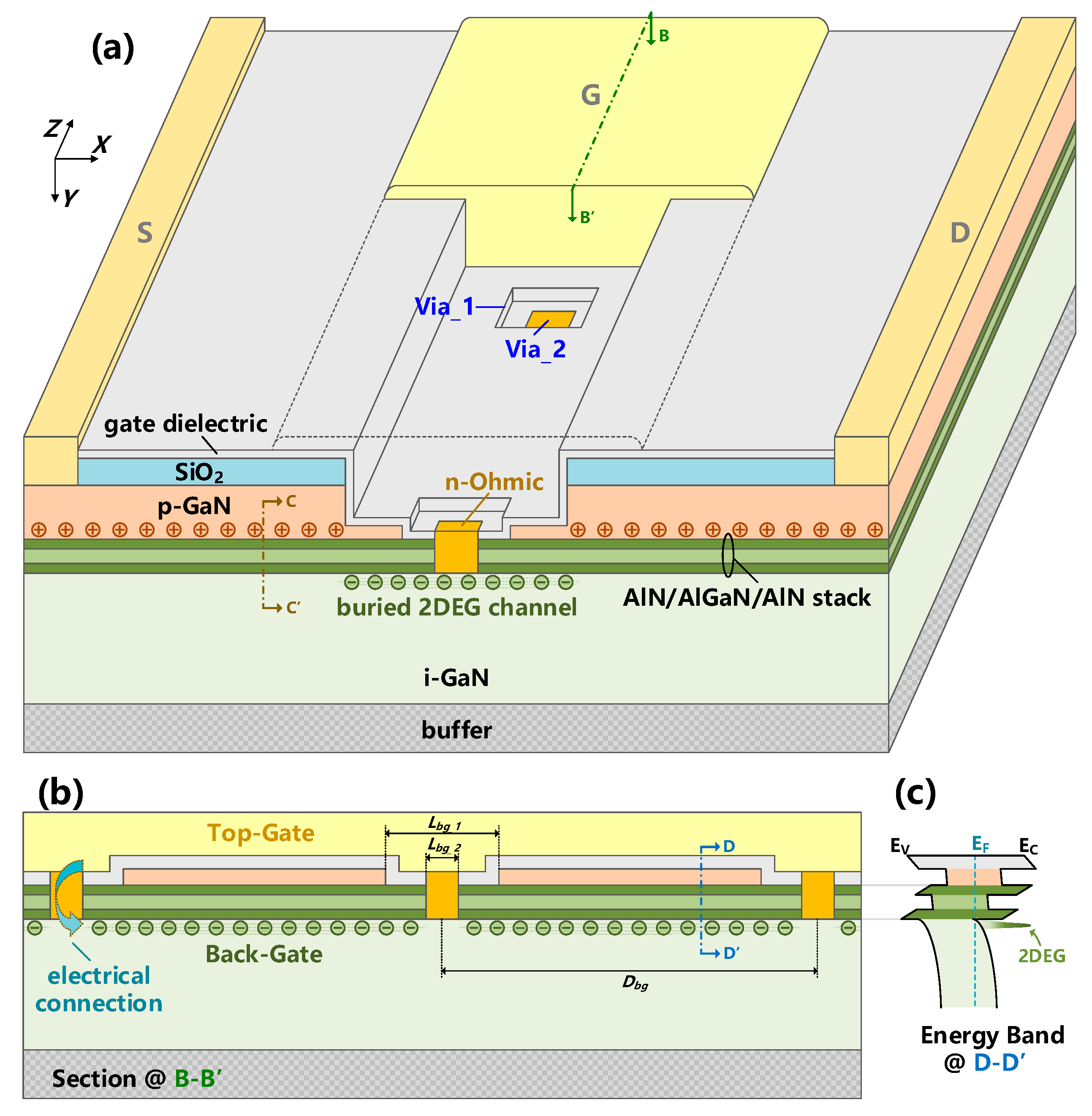

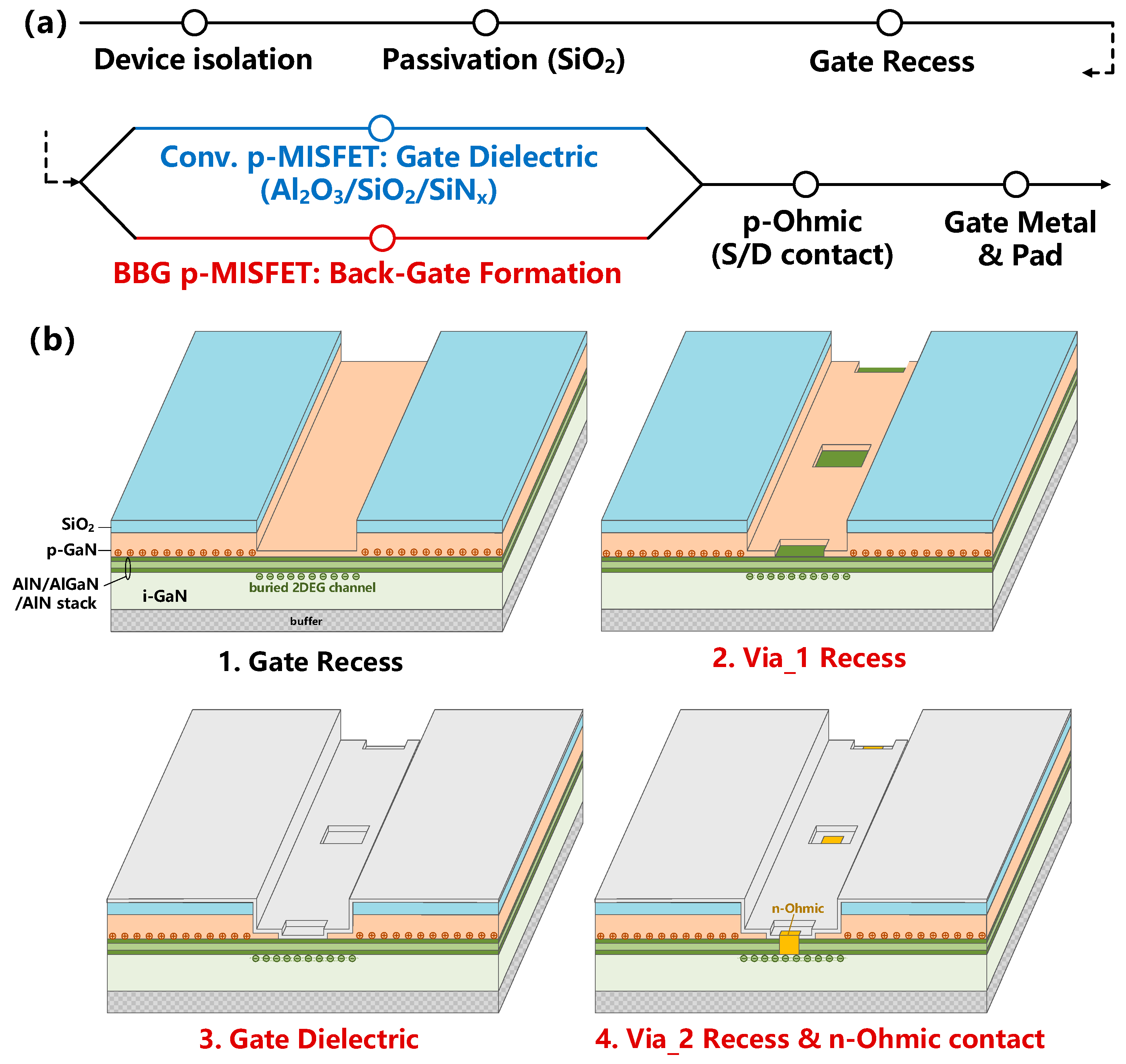

2. Double-Heterojunction Design and GaN p-MOSFET Device Structure

3. Simulation Results and Discussion

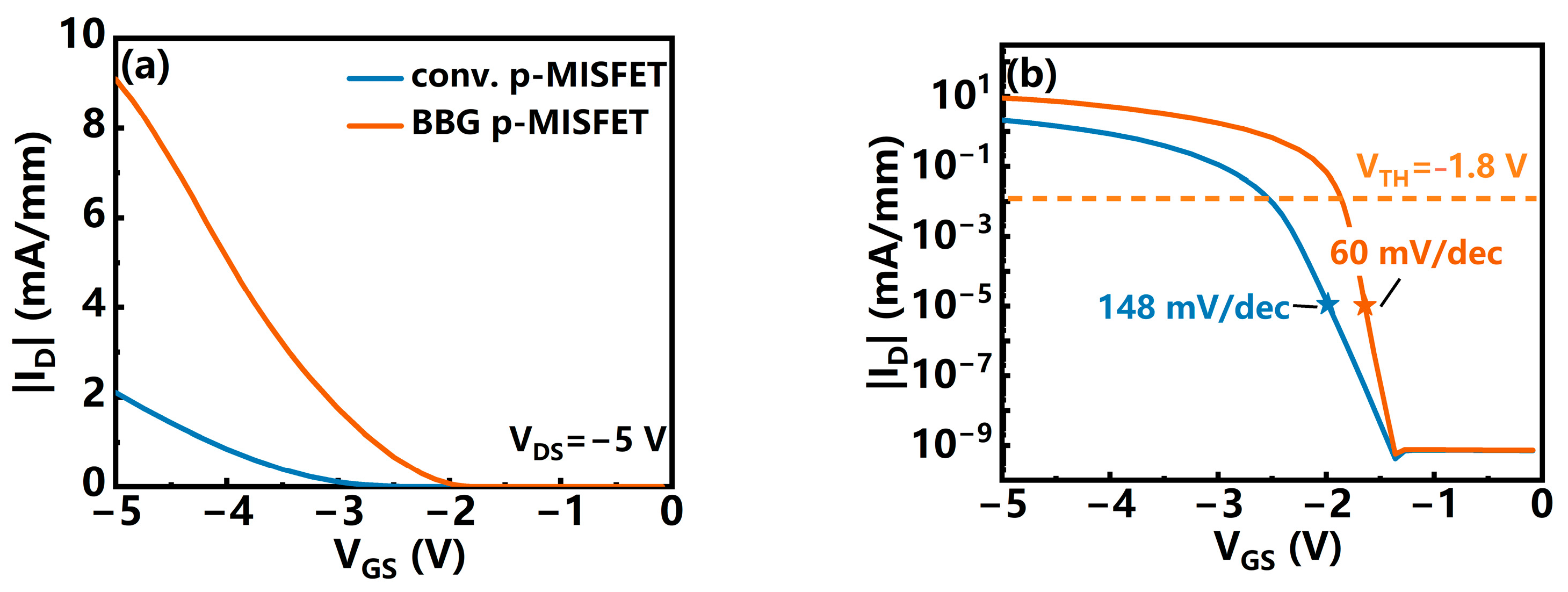

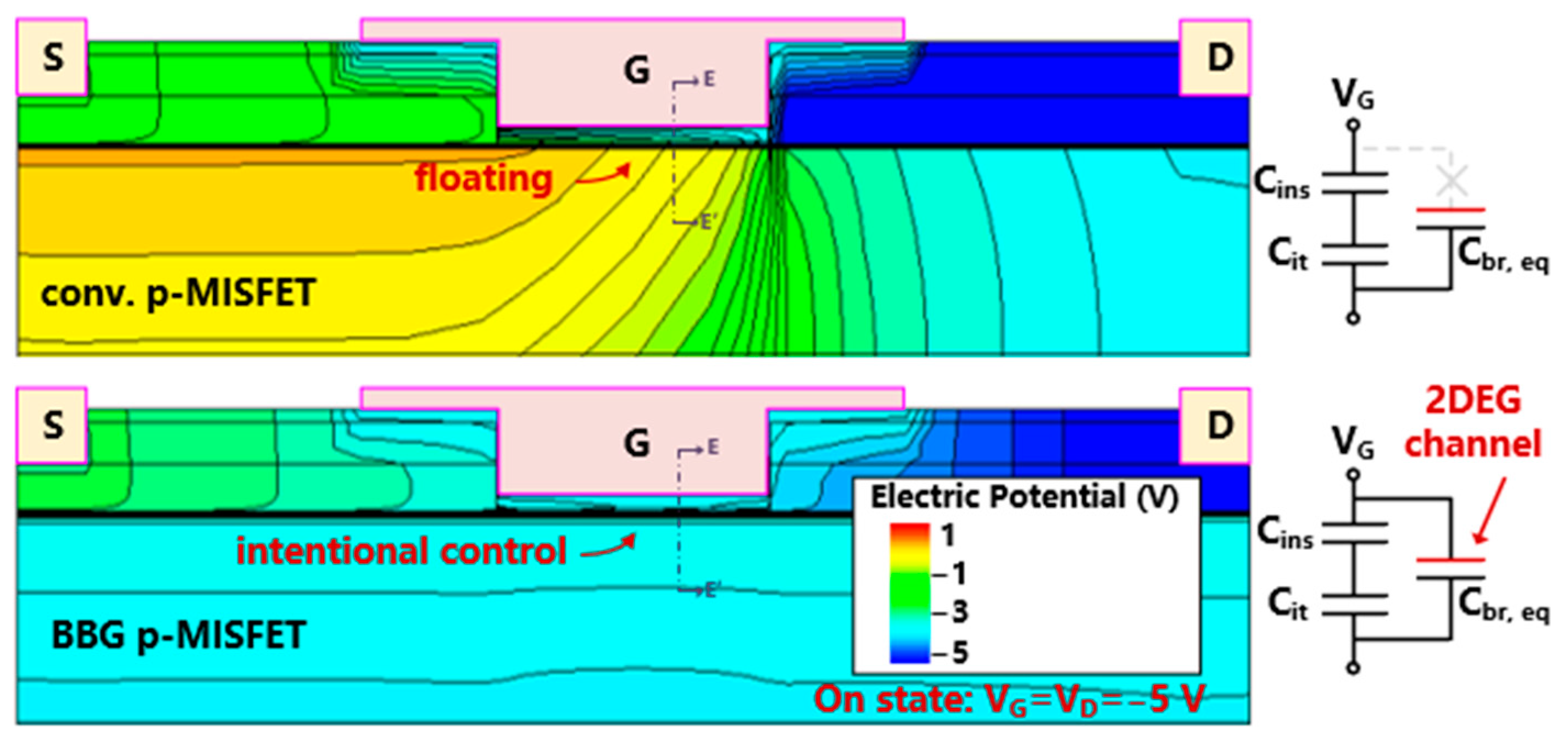

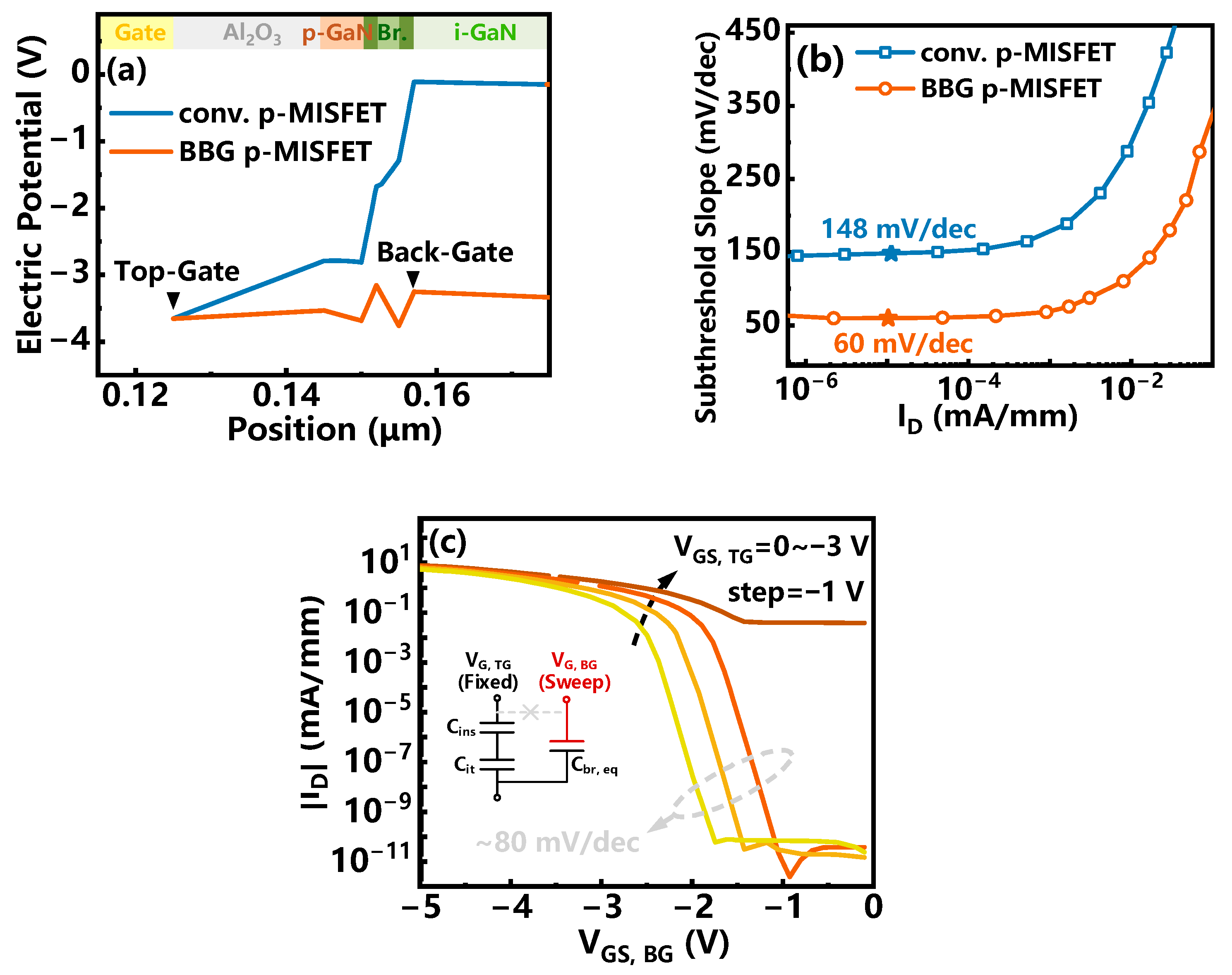

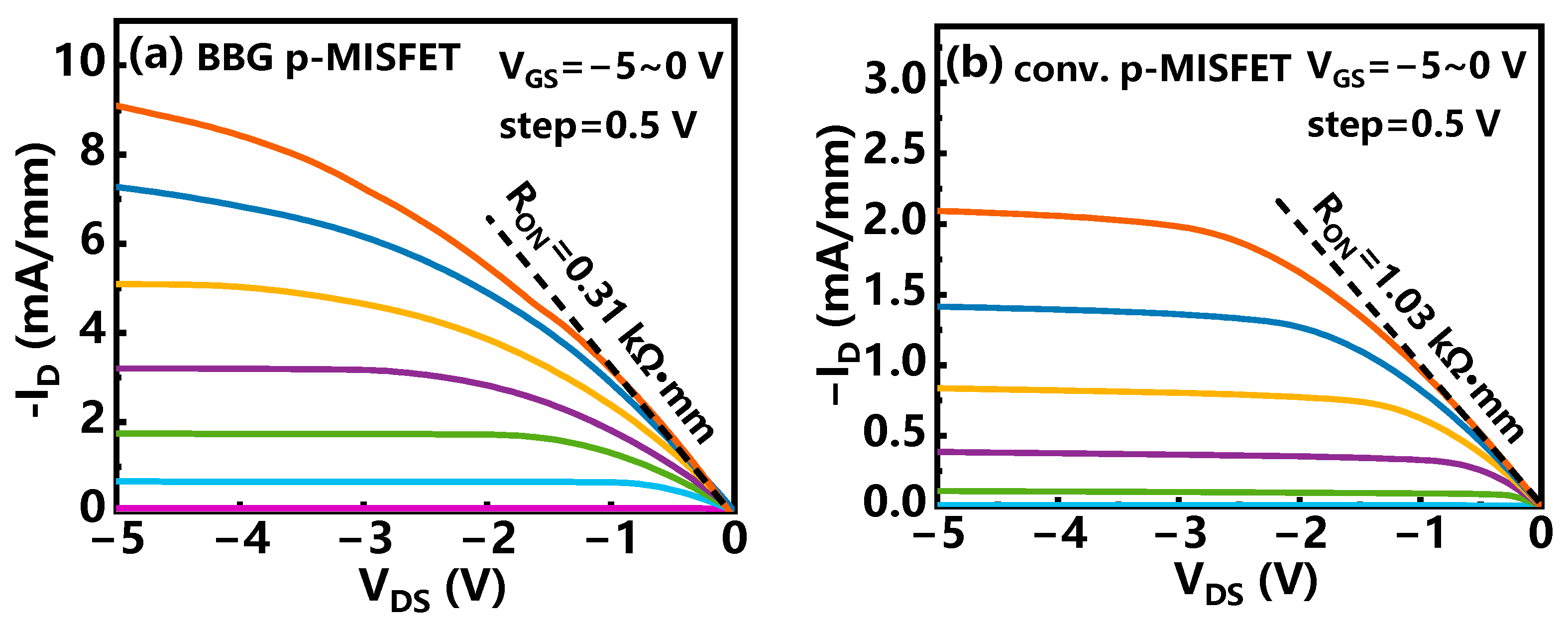

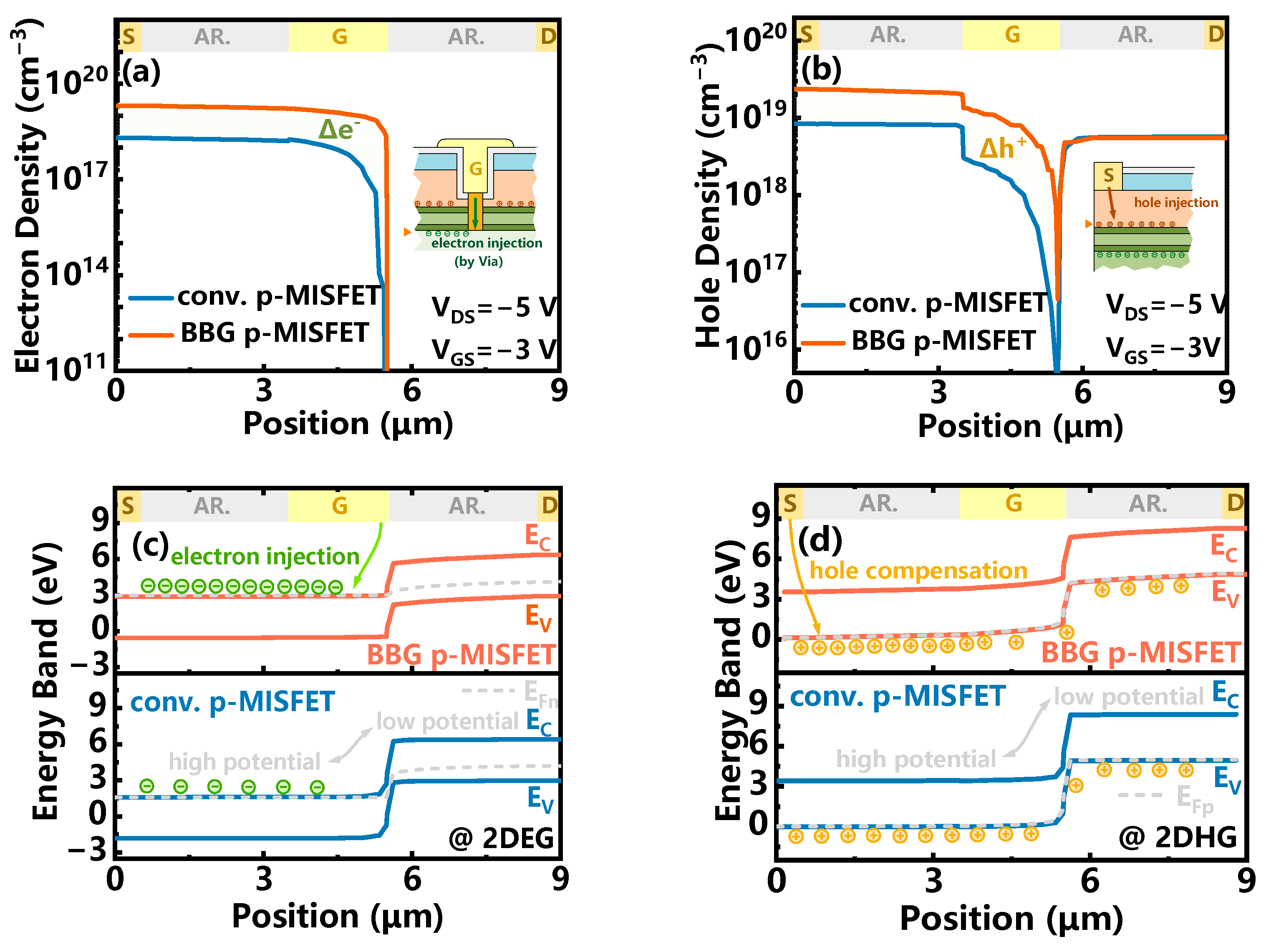

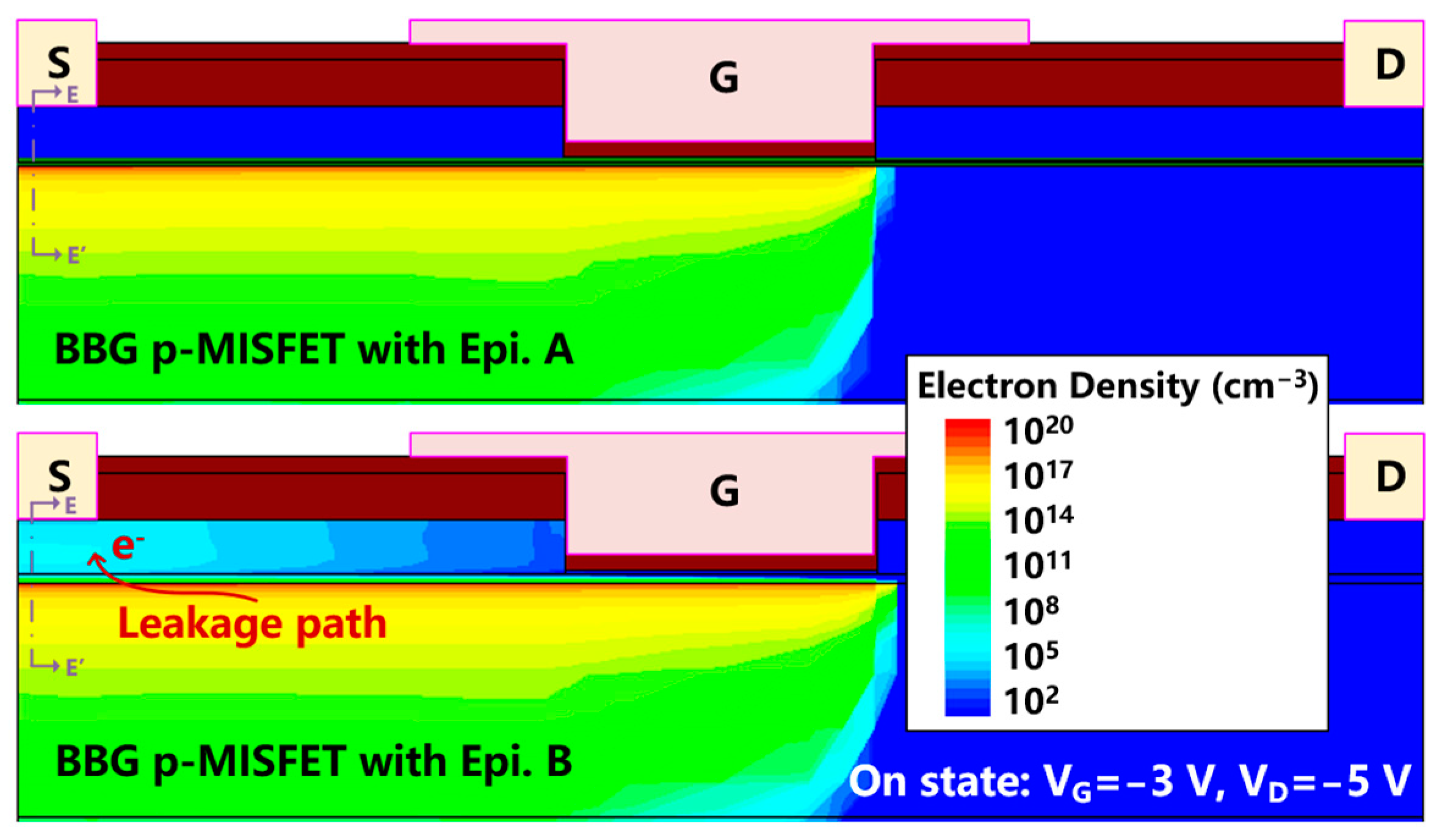

3.1. I-V Characteristics of the BBG p-MISFET

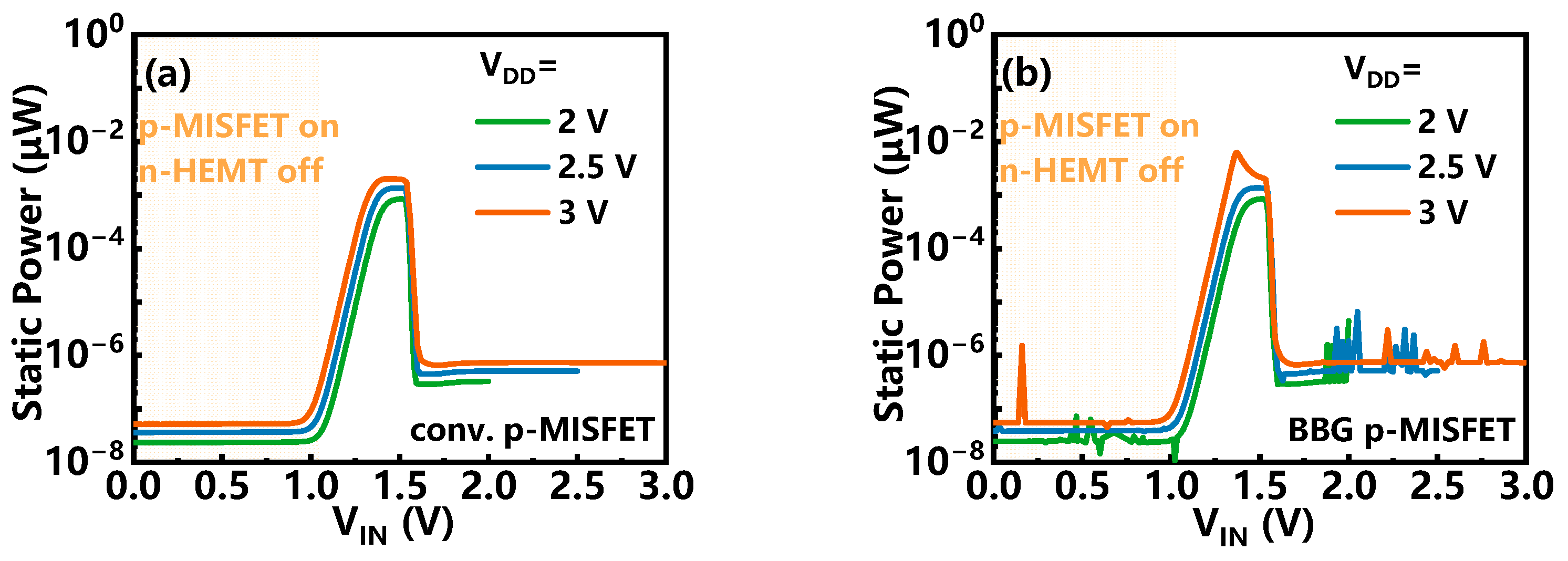

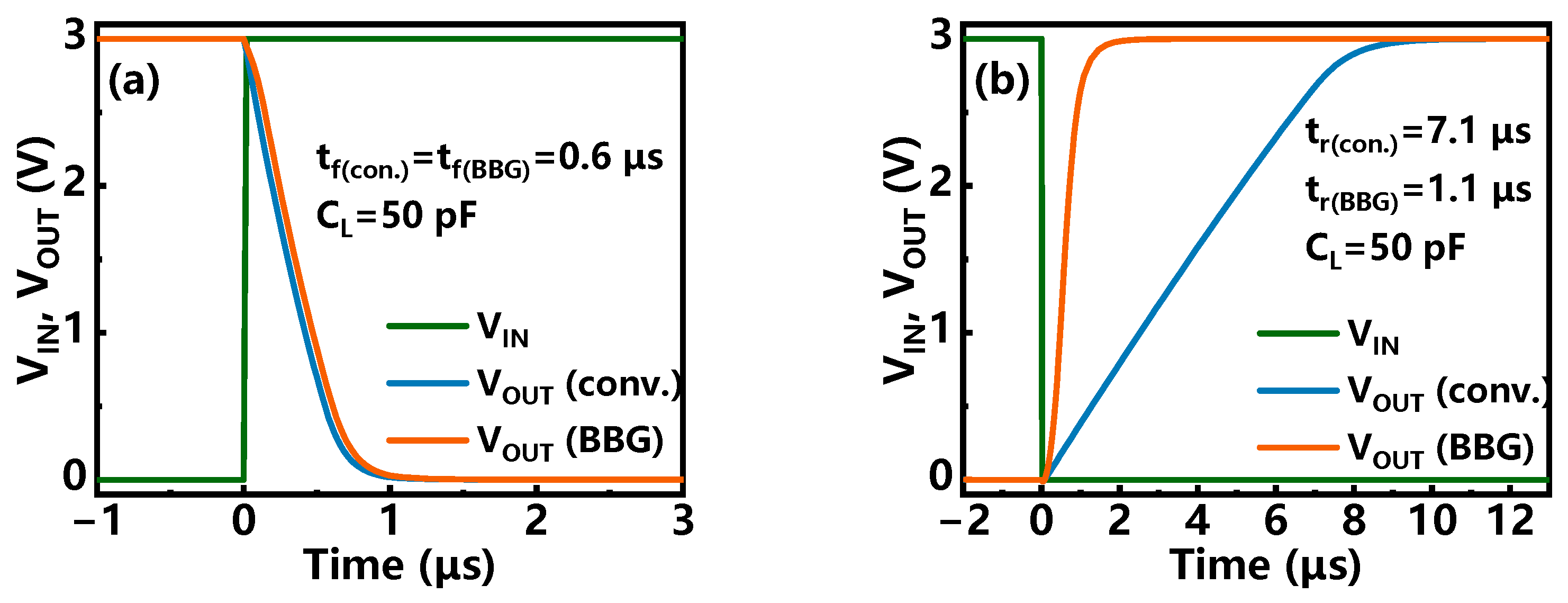

3.2. Switching Characteristics of the Complementary Logic Inverters

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chow, T.P. Progress in High Voltage SiC and GaN Power Switching Devices. Mater. Sci. Forum 2014, 778–780, 1077–1082. [Google Scholar] [CrossRef]

- Chen, K.J.; Häberlen, O.; Lidow, A.; lin Tsai, C.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si Power Technology: Devices and Applications. IEEE Trans. Electron Devices 2017, 63, 779–795. [Google Scholar] [CrossRef]

- Meneghini, M.; De Santi, C.; Abid, I.; Buffolo, M.; Cioni, M.; Khadar, R.A.; Nela, L.; Zagni, N.; Chini, A.; Medjdoub, F.; et al. GaN-based power devices: Physics, reliability, and perspectives. J. Appl. Phys. 2021, 130, 181101. [Google Scholar] [CrossRef]

- Su, M.; Chen, C.; Rajan, S. Prospects for the application of GaN power devices in hybrid electric vehicle drive systems. Semicond. Sci. Technol. 2013, 28, 074012. [Google Scholar] [CrossRef]

- Apparao, D.; Ghaffari, R.; Venkatesh, B.; Wu, B. A survey on energy storage technologies in power systems. In Proceedings of the 2015 IEEE Electrical Power and Energy Conference (EPEC), London, UK, 26–28 October 2015; pp. 105–111. [Google Scholar]

- Krichen, M.; Basheer, Y.; Qaisar, S.M.; Waqar, A. A Survey on Energy Storage: Techniques and Challenges. Energies 2023, 16, 2271. [Google Scholar] [CrossRef]

- Pearton, S.J.; Aitkaliyeva, A.; Xian, M.; Ren, F.; Khachatrian, A.; Ildefonso, A.; Islam, Z.; Rasel, M.A.J.; Haque, A.; Polyakov, A.Y.; et al. Radiation damage in wide and ultra-wide bandgap semiconductors. ECS J. Solid State Sci. Technol. 2021, 10, 055008. [Google Scholar] [CrossRef]

- Wong, K.-Y.; Chen, W.; Chen, K.J. Integrated Voltage Reference Generator for GaN Smart Power Chip Technology. IEEE Trans. Electron Devices 2010, 57, 952–955. [Google Scholar] [CrossRef]

- Kinzer, D. Monolithic GaN Power IC Technology Drives Wide Bandgap Adoption. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–16 December 2020; pp. 27.5.1–27.5.4. [Google Scholar]

- Cui, M.; Sun, R.; Bu, Q.; Liu, W.; Wen, H.; Li, A.; Liang, Y.C.; Zhao, C. Monolithic GaN Half-Bridge Stages With Integrated Gate Drivers for High Temperature DC-DC Buck Converters. IEEE Access 2019, 7, 184375–184384. [Google Scholar] [CrossRef]

- Li, F.; Li, A.; Wang, Y.; Zhu, Y.; Yu, C.; Ding, C.; Wu, S.; Liu, W.; Yu, G.; Gao, X.; et al. Demonstration of the Hydrogen Passivated GaN HEMTs IC Platform. In Proceedings of the 35th International Symposium on Power Semiconductor Devices and ICs (ISPSD), Hong Kong, China, 28 May–1 June 2023; pp. 99–102. [Google Scholar]

- Li, X.; Geens, K.; Amirifar, N.; Zhao, M.; You, S.; Posthuma, N.; Liang, H.; Groeseneken, G.; Decoutere, S. Integration of GaN analog building blocks on p-GaN wafers for GaN ICs. J. Semicond. 2021, 42, 117–120. [Google Scholar] [CrossRef]

- Tang, G.; Kwan, A.M.H.; Wong, R.K.Y.; Lei, J.; Su, R.Y.; Yao, F.W.; Lin, Y.M.; Yu, J.L.; Tsai, T.; Tuan, H.C.; et al. Digital Integrated Circuits on an E-Mode GaN Power HEMT Platform. IEEE Electron Device Lett. 2017, 38, 1282–1285. [Google Scholar] [CrossRef]

- Li, X.; Amirifar, N.; Geens, K.; Zhao, M.; Guo, W.; Liang, H.; You, S.; Posthuma, N.; De Jaeger, B.; Stoffels, S.; et al. GaN-on-SOI: Monolithically integrated all-GaN ICs for power conversion. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), Francisco, CA, USA, 7–11 December 2019. [Google Scholar]

- Zheng, Z.; Zhang, L.; Song, W.; Feng, S.; Xu, H.; Sun, J.; Yang, S.; Chen, T.; Wei, J.; Chen, K.J. Gallium nitride-based complementary logic integrated circuits. Nat. Electron. 2021, 4, 595–603. [Google Scholar] [CrossRef]

- Zheng, Z.; Song, W.; Zhang, L.; Yang, S.; Wei, J.; Chen, K.J. Monolithically Integrated GaN Ring Oscillator Based on High-Performance Complementary Logic Inverters. IEEE Electron Device Lett. 2021, 42, 26–29. [Google Scholar] [CrossRef]

- Poncé, S.; Jena, D.; Giustino, F. Route to High Hole Mobility in GaN via Reversal of Crystal-Field Splitting. Phys. Rev. Lett. 2019, 123, 096602. [Google Scholar] [CrossRef] [PubMed]

- Chowdhury, N.; Lemettinen, J.; Xie, Q.; Zhang, Y.; Rajput, N.S.; Xiang, P.; Cheng, K.; Suihkonen, S.; Then, H.W.; Palacios, T. P-Channel GaN Transistor Based on p-GaN/AlGaN/GaN on Si. IEEE Electron Device Lett. 2019, 40, 1036–1039. [Google Scholar] [CrossRef]

- Zhu, L.Y.; Chen, K.L.; Ma, Y.; Cai, Y.; Zhou, C.H.; Li, Z.J.; Zhang, B.; Zhou, Q. High threshold voltage enhancement-mode GaN p-FET with Si-rich LPCVD SiNx gate insulator for high hole mobility. J. Semicond. 2023, 44, 082801. [Google Scholar] [CrossRef]

- Zheng, Z.; Zhang, L.; Song, W.; Chen, T.; Feng, S.; Ng, Y.H.; Sun, J.; Xu, H.; Yang, S.; Wei, J.; et al. Threshold Voltage Instability of Enhancement-Mode GaN Buried p-Channel MOSFETs. IEEE Electron Device Lett. 2021, 42, 1584–1587. [Google Scholar] [CrossRef]

- Chowdhury, N.; Xie, Q.; Niroula, J.; Rajput, N.S.; Cheng, K.; Then, H.W.; Palacios, T. Field-induced acceptor ionization in enhancement-mode GaN p-MOSFETs. In Proceedings of the 2020 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 12–16 December 2020. [Google Scholar]

- Zhang, Y.; Sun, Z.; Wang, W.; Liang, Y.; Cui, M.; Zhao, Y.; Wen, H.; Liu, W. Low-resistance Ni/Ag contacts on GaN-based p-channel heterojunction field-effect transistor. IEEE Trans. Electron Devices 2022, 70, 31–35. [Google Scholar] [CrossRef]

- Tang, C.-Y.; Lu, H.-H.; Qiao, Z.-P.; Jiang, Y.; Du, F.-Z.; He, J.-Q.; Jiang, Y.-L.; Wang, Q.; Yu, H.-Y. Ohmic contact with a contact resistivity of 12 Ω mm on p-GaN/AlGaN/GaN. IEEE Electron Device Lett. 2022, 43, 1412–1415. [Google Scholar] [CrossRef]

- Bader, S.J.; Chaudhuri, R.; Nomoto, K.; Hickman, A.; Chen, Z.; Then, H.W.; Muller, D.A.; Xing, H.G.; Jena, D. Gate-Recessed E-mode p-Channel HFET With High On-Current Based on GaN/AlN 2D Hole Gas. IEEE Electron Device Lett. 2018, 39, 1848–1851. [Google Scholar] [CrossRef]

- Zhang, Z.; Encomendero, J.; Chaudhuri, R.; Cho, Y.; Protasenko, V.; Nomoto, K.; Lee, K.; Toita, M.; Xing, H.G.; Jena, D. Polarization-induced 2D hole gases in pseudomorphic undoped GaN/AlN heterostructures on single-crystal AlN substrates. Appl. Phys. Lett. 2021, 119, 162104. [Google Scholar] [CrossRef]

- Chowdhury, N.; Xie, Q.; Yuan, M.; Cheng, K.; Then, H.W.; Palacios, T. Regrowth-free GaN-based complementary logic on a Si substrate. IEEE Electron Device Lett. 2020, 41, 820–823. [Google Scholar] [CrossRef]

- Raj, A.; Krishna, A.; Romanczyk, B.; Hatui, N.; Liu, W.; Keller, S.; Mishra, U.K. GaN/AlGaN Superlattice Based E-Mode Hole Channel FinFET With Schottky Gate. IEEE Electron Device Lett. 2022, 44, 9–12. [Google Scholar] [CrossRef]

- Chowdhury, N.; Xie, Q.; Palacios, T. Self-Aligned E-Mode GaN p-Channel FinFET With ION> 100 mA/mm and ION/IOFF> 107. IEEE Electron Device Lett. 2022, 43, 358–361. [Google Scholar] [CrossRef]

- Yang, C.; Fu, H.; Peri, P.; Fu, K.; Yang, T.-H.; Zhou, J.; Montes, J.; Smith, D.J.; Zhao, Y. Enhancement-mode gate-recess-free GaN-based p-channel heterojunction field-effect transistor with ultra-low subthreshold swing. IEEE Electron Device Lett. 2021, 42, 1128–1131. [Google Scholar] [CrossRef]

- Yin, Y.; Lee, K.B. High-Performance Enhancement-Mode p-Channel GaN MISFETs With Steep Subthreshold Swing. IEEE Electron Device Lett. 2022, 43, 533–536. [Google Scholar] [CrossRef]

- Zheng, Z.; Chen, T.; Zhang, L.; Song, W.; Chen, K.J. Unveiling the parasitic electron channel under the gate of enhancement-mode p-channel GaN field-effect transistors on the p-GaN/AlGaN/GaN platform. Appl. Phys. Lett. 2022, 120, 152102. [Google Scholar] [CrossRef]

- Sang, L.; Ren, B.; Nabatame, T.; Sumiya, M.; Liao, M. Insight into traps at Al2O3/p-GaN metal-oxide-semiconductor interface fabricated on free-standing GaN substrate. J. Alloys Compd. 2021, 853, 157356. [Google Scholar] [CrossRef]

- Zheng, Z.; Song, W.; Zhang, L.; Yang, S.; Wei, J.; Chen, K.J. High ION and ION/IOFF Ratio Enhancement-Mode Buried p-Channel GaN MOSFETs on p-GaN Gate Power HEMT Platform. IEEE Trans. Electron Devices 2020, 41, 26–29. [Google Scholar] [CrossRef]

- Lyu, J.-S. A New Method for Extracting Interface Trap Density in Short-Channel MOSFETs from Substrate-Bias-Dependent Subthreshold Slopes. ETRI J. 1993, 15, 10–25. [Google Scholar] [CrossRef]

- Du, H.; Liu, Z.; Hao, L.; Su, H.; Zhang, T.; Zhang, W.; Zhang, J.; Hao, Y. High-performance E-mode p-channel GaN FinFET on silicon substrate with high I ON/I OFF and high threshold voltage. IEEE Electron Device Lett. 2022, 43, 705–708. [Google Scholar] [CrossRef]

- Chen, J.; Liu, Z.; Wang, H.; He, Y.; Zhu, X.; Ning, J.; Zhang, J.; Hao, Y. A GaN complementary FET inverter with excellent noise margins monolithically integrated with power gate-injection HEMTs. IEEE Trans. Electron Devices 2021, 69, 51–56. [Google Scholar] [CrossRef]

- Chu, R.; Cao, Y.; Chen, M.; Li, R.; Zehnder, D. An Experimental Demonstration of GaN CMOS Technology. IEEE Electron Device Lett. 2016, 37, 269–271. [Google Scholar] [CrossRef]

- Jin, H.; Jiang, Q.; Huang, S.; Wang, X.; Wang, Y.; Ji, Z.; Dai, X.; Feng, C.; Fan, J.; Wei, K.; et al. An Enhancement-Mode GaN p-FET With Improved Breakdown Voltage. IEEE Electron Device Lett. 2022, 43, 1191–1194. [Google Scholar] [CrossRef]

| Symbol | Description | Value |

|---|---|---|

| LG | Length of gate | 2.0 |

| LGS | Gate-to-source spacing | 3.0 |

| LGD | Gate-to-drain spacing | 3.0 |

| Lohmic | Ohmic contact spacing | 0.5 |

| Tox | Thickness of gate dielectric | 20 |

| Tpass | Thickness of SiO2 passivation | 60 |

| Tp-GaN | Thickness of p-GaN cap layer | 70 |

| Dtrench | Depth of gate trench | 65 |

| Tch | Thickness of UID-GaN channel | 0.3 |

| Tbuffer | Thickness of GaN buffer | 4.0 |

| TAlN | Thickness of AlN spacer | 2 |

| TAlGaN | Thickness of AlGaN barrier | 3 |

| xAl | Al mole fraction of AlGaN | 0.2 |

| Dbg | Distance between adjacent back gate via | 20.0 |

| Lbg_1 | Length of back gate via_1 | 1.0 |

| Lbg_2 | Length of back gate via_2 | 0.5 |

| Np | Hole concentration of p-GaN | 6 × 1017 cm−3 |

| Symbol | Description | Value |

|---|---|---|

| μe | The maximum of electron mobility of GaN | 1000 cm2/V·s |

| μh | The maximum of hole mobility of GaN | 10 cm2/V·s |

| Rc_p | P-type ohmic contact resistance | 60 Ω·mm |

| Rc_n | N-type ohmic contact resistance | 10−5 Ω·cm2 |

| a | Polarization activation factor at AlN interface | 0.6 |

| εox | Dielectric constant of gate dielectric | 9 |

| Affinity | Platform | Vth a (V) | |Ion| b (mA/mm) | SS (mV/dec) |

|---|---|---|---|---|

| MIT [26] | p-GaN/i-GaN/AlGaN/GaN (Al2O3 MIS gate) | −0.5 (VDS = −0.5 V) | 0.6 | N.A. |

| MIT [21] | p-GaN/i-GaN/AlGaN/GaN (Al2O3 MIS gate, self-aligned) | 0.3 (VDS = −1 V) | ~3 (VDS = −1 V) | ~800 |

| XDU [35] | p-GaN/AlN/AlGaN/AlN (Al2O3 MIS gate, FinFET) | 3.5 | 3.6 | 130 |

| XDU [36] | p-GaN/AlGaN/AlN/UID-GaN (Al2O3 MIS gate) | −2 | ~0.35 | 251 |

| Sheffield [30] | p-GaN/i-GaN/AlGaN/GaN (SiO2 MIS gate) | −0.7 | ~1.5 | ~60 |

| HKUST [33] | p-GaN/AlGaN/GaN (Al2O3 MIS gate) | −1.7 | ~1 | 230 |

| LJTLU [22] | p-GaN/AlGaN/GaN (Al2O3 MIS gate) | −2.7 | ~0.8 | 460 |

| UESTC [19] | p-GaN/AlGaN/GaN (SiNx MIS gate) | −2.3 | ~0.4 | N.A. |

| HRL [37] | p-GaN/i-GaN/AlGaN/GaN (AlN/SiNx MIS gate) | −0.36 (−0.1 V) | ~1.3 | 304 |

| UCSB [27] | GaN/AlGaN Superlattice (Schottky gate, FinFET) | 0.3 (−10 V) | ~10 | 130 |

| IMECAS [38] | p-GaN/AlN/AlGaN/AlN/GaN (Al2O3 MIS gate) | −2.8 | 1.5 | N.A. |

| Conv. (this work) | p-GaN/AlN/AlGaN/AlN/GaN (MIS gate, gate recess) | −2.55 | 2.1 | 148 |

| BBG (this work) | p-GaN/AlN/AlGaN/AlN/GaN (MIS gate, BBG) | −1.8 | 9.1 | ~60 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, H.; Chen, K.; Yang, N.; Zhu, J.; Duan, E.; Huang, S.; Zhao, Y.; Zhang, B.; Zhou, Q. A Novel Enhancement-Mode Gallium Nitride p-Channel Metal Insulator Semiconductor Field-Effect Transistor with a Buried Back Gate for Gallium Nitride Single-Chip Complementary Logic Circuits. Electronics 2024, 13, 729. https://doi.org/10.3390/electronics13040729

Wang H, Chen K, Yang N, Zhu J, Duan E, Huang S, Zhao Y, Zhang B, Zhou Q. A Novel Enhancement-Mode Gallium Nitride p-Channel Metal Insulator Semiconductor Field-Effect Transistor with a Buried Back Gate for Gallium Nitride Single-Chip Complementary Logic Circuits. Electronics. 2024; 13(4):729. https://doi.org/10.3390/electronics13040729

Chicago/Turabian StyleWang, Haochen, Kuangli Chen, Ning Yang, Jianggen Zhu, Enchuan Duan, Shuting Huang, Yishang Zhao, Bo Zhang, and Qi Zhou. 2024. "A Novel Enhancement-Mode Gallium Nitride p-Channel Metal Insulator Semiconductor Field-Effect Transistor with a Buried Back Gate for Gallium Nitride Single-Chip Complementary Logic Circuits" Electronics 13, no. 4: 729. https://doi.org/10.3390/electronics13040729

APA StyleWang, H., Chen, K., Yang, N., Zhu, J., Duan, E., Huang, S., Zhao, Y., Zhang, B., & Zhou, Q. (2024). A Novel Enhancement-Mode Gallium Nitride p-Channel Metal Insulator Semiconductor Field-Effect Transistor with a Buried Back Gate for Gallium Nitride Single-Chip Complementary Logic Circuits. Electronics, 13(4), 729. https://doi.org/10.3390/electronics13040729