A 60 GHz Power Amplifier with Neutralization Capacitors and Compensation Inductors

Abstract

1. Introduction

2. Design Methodology

2.1. Active Device

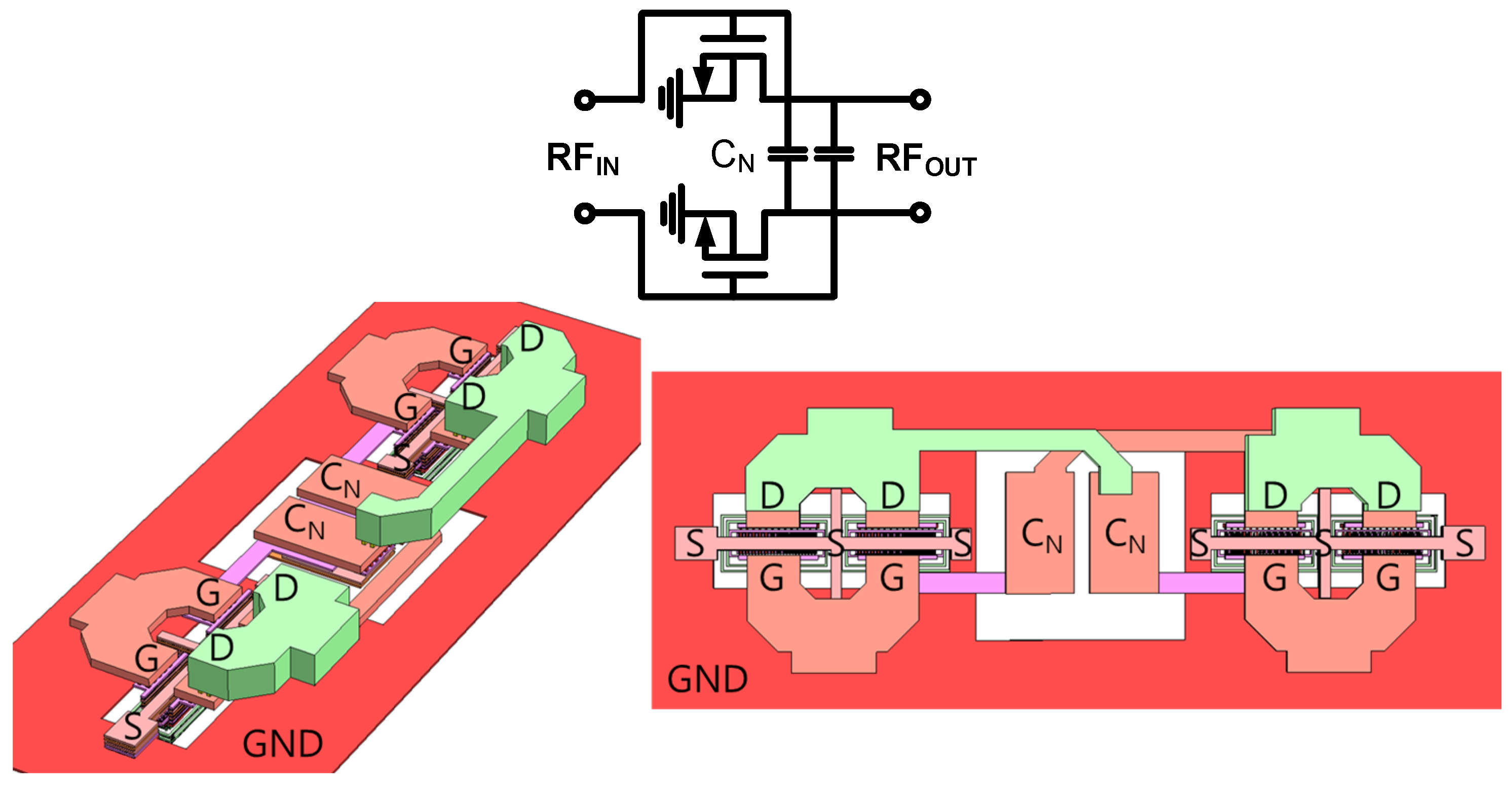

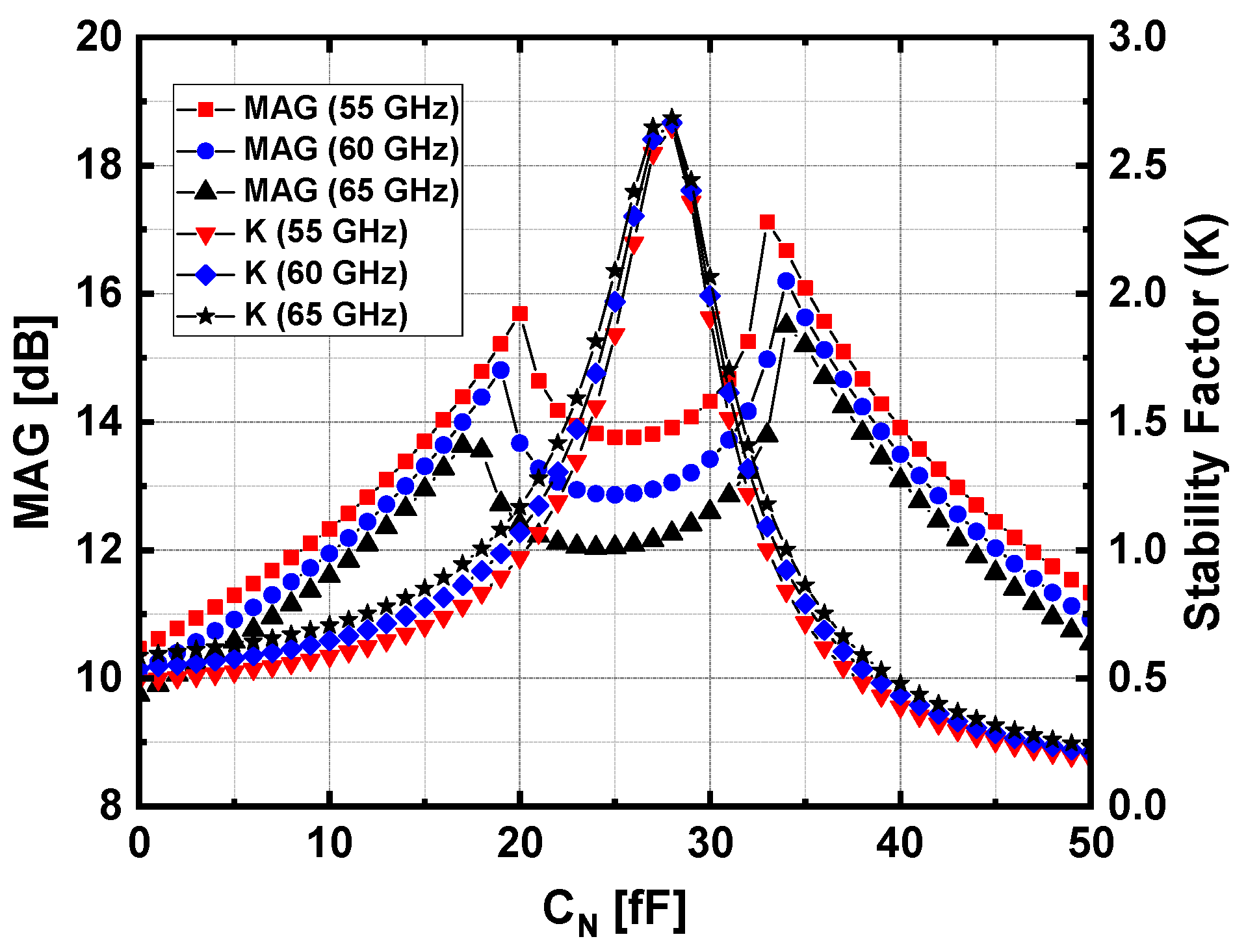

2.2. Neutralization Capacitors

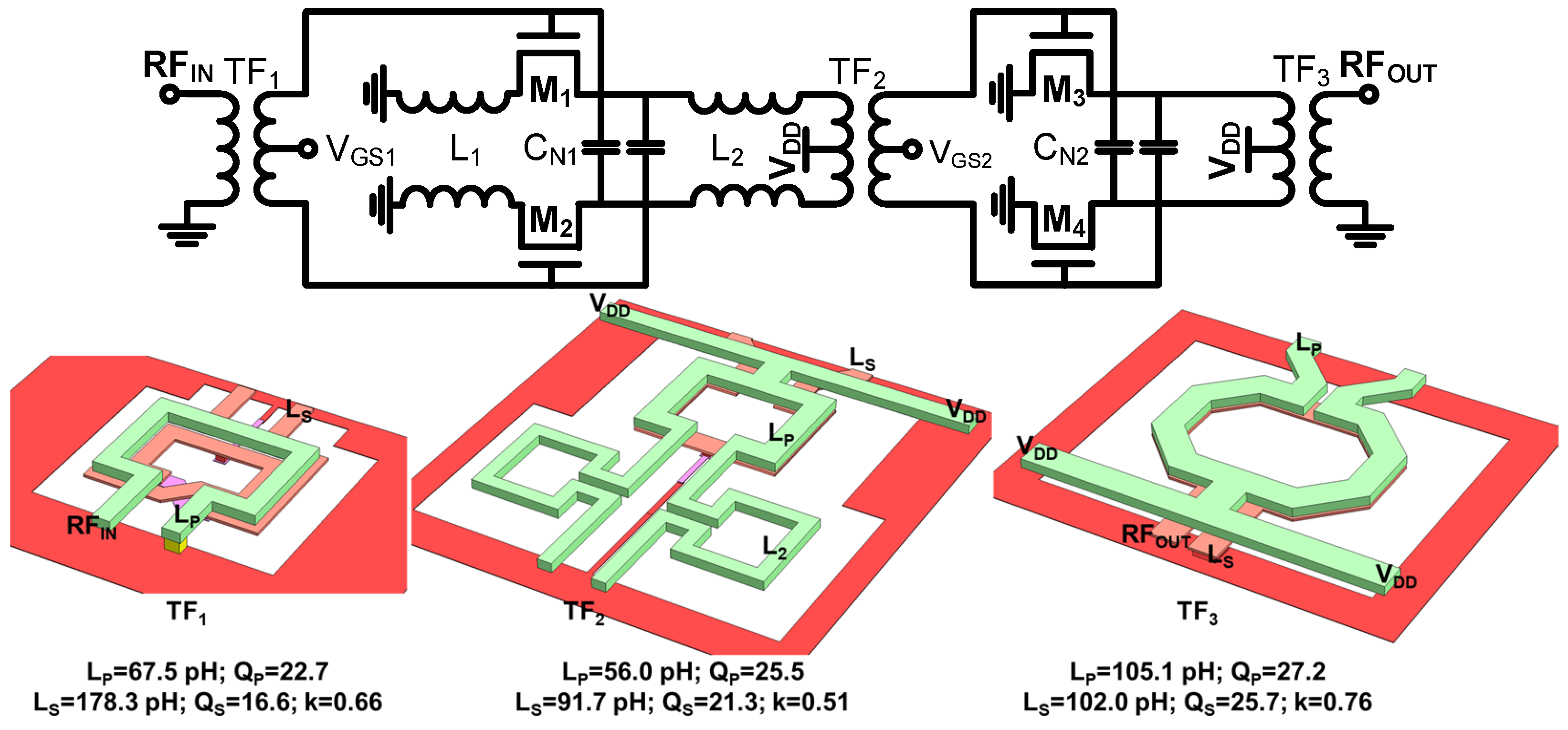

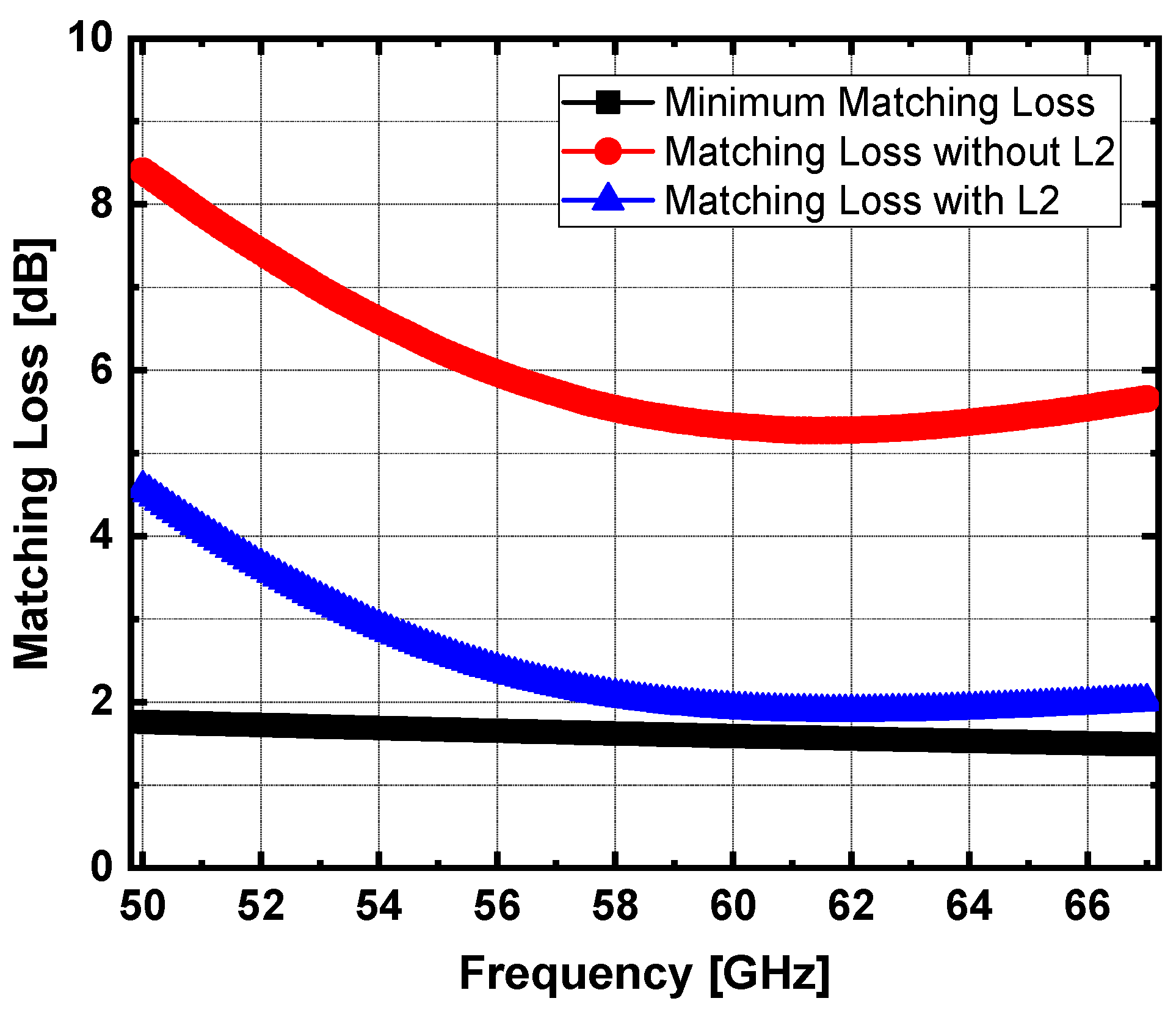

2.3. Proposed PA Design with Transformers and Compensation Inductors

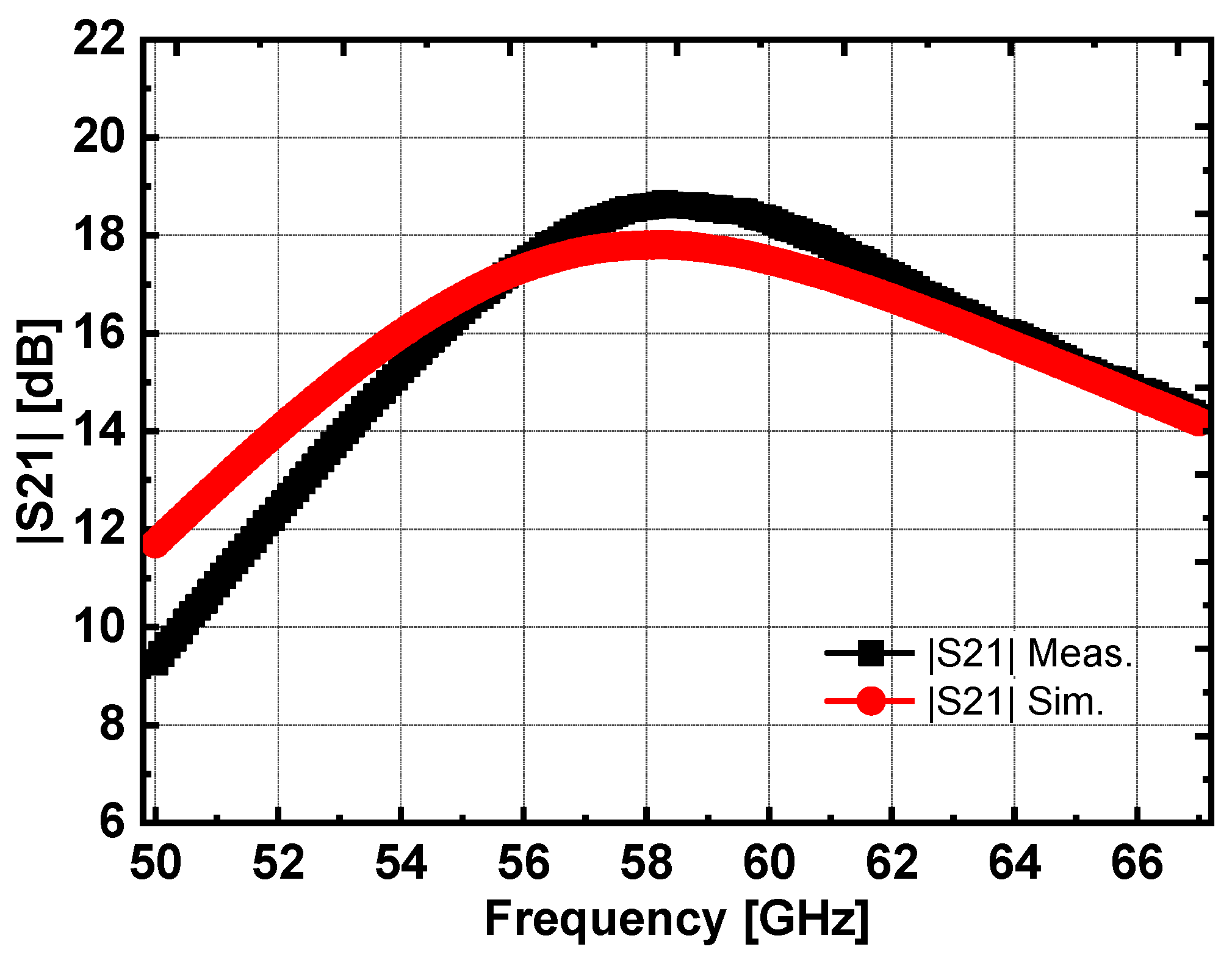

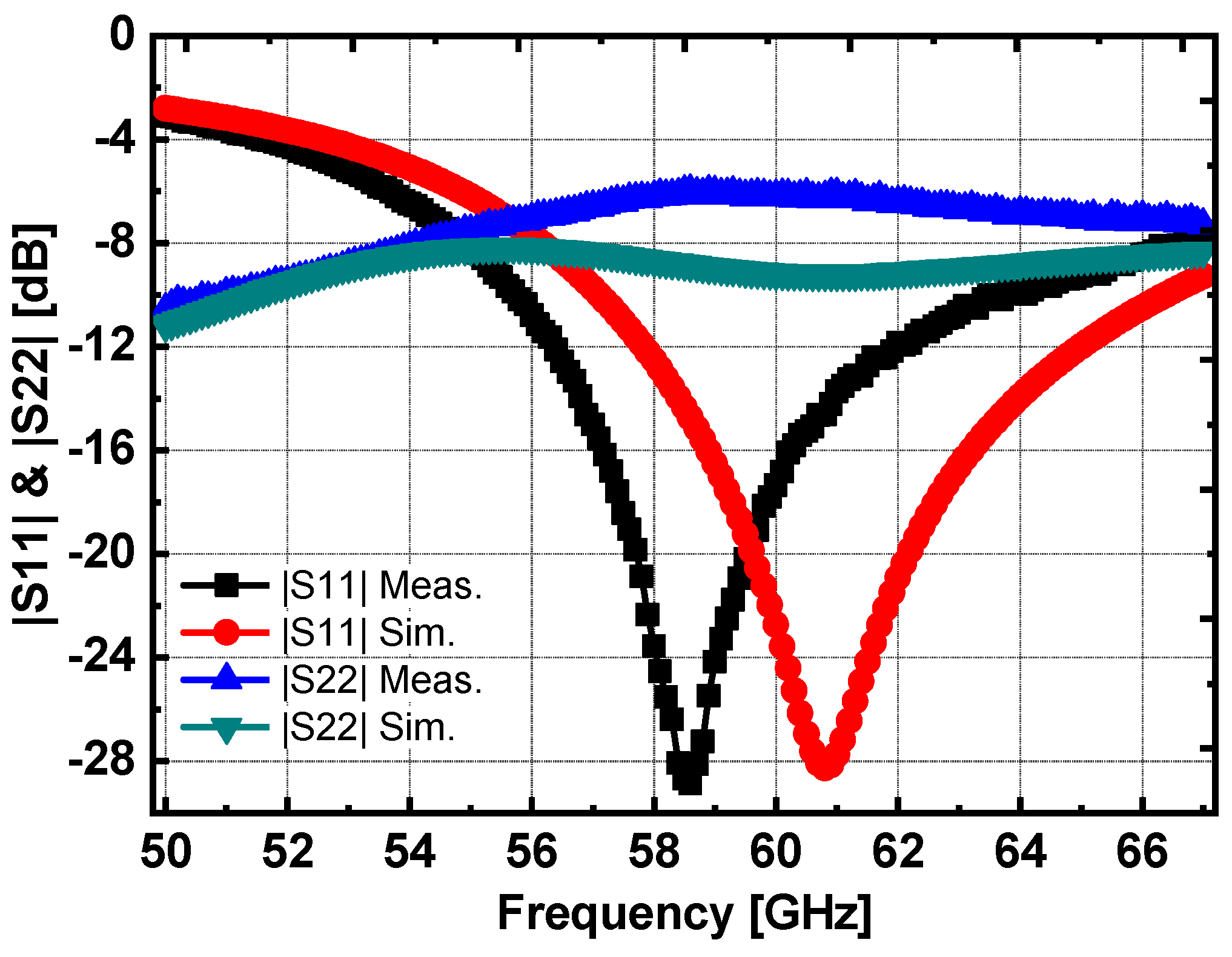

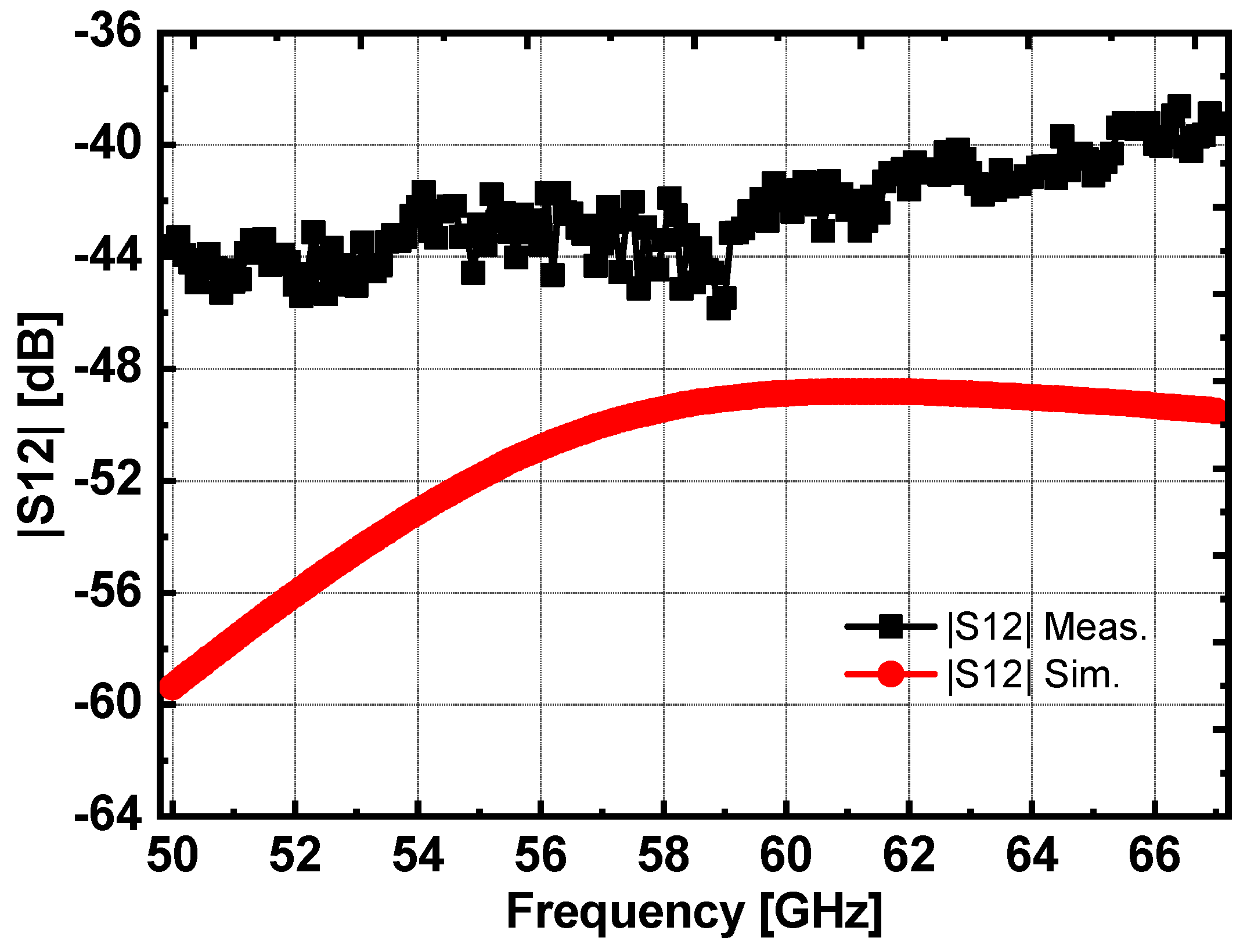

3. Results

4. Discussion

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Wang, Y.; Liu, B.; Wu, R.; Liu, H.; Narayanan, A.T. A 60-GHz 3.0-Gb/s Spectrum Efficient BPOOK Transceiver for Low-Power Short-Range Wireless in 65-nm CMOS. IEEE J. Solid-State Circuits 2019, 54, 1363–1374. [Google Scholar] [CrossRef]

- Byeon, C.W.; Eun, K.C.; Park, C.S. A 2.65-pJ/Bit 12.5-Gb/s 60-GHz OOK CMOS Transmitter and Receiver for Proximity Communications. IEEE Trans. Microw. Theory Tech. 2020, 68, 2902–2910. [Google Scholar] [CrossRef]

- Wang, Y.; Chung, H.; Ma, Q.; Rebeiz, G.M. A 57.5–65.5 GHz Phased-Array Transmit Beamformer in 45 nm CMOS SOI with 5 dBm and 6.1% Linear PAE for 400 MBaud 64-QAM Waveforms. IEEE Trans. Microw. Theory Tech. 2021, 69, 1772–1779. [Google Scholar] [CrossRef]

- Son, H.S.; Jang, T.H.; Kim, S.H.; Jung, K.P.; Kim, J.H.; Park, C.S. Pole-controlled wideband 120 GHz CMOS power amplifier for wireless chip-to-chip communication in 40-nm CMOS process. IEEE Trans. Circuits Syst. II Exp. Briefs 2019, 66, 1351–1355. [Google Scholar] [CrossRef]

- Kim, J. Broadband Millimeter-Wave Power Amplifier Using Modified 2D Distributed Power Combining. Electronics 2020, 9, 899. [Google Scholar] [CrossRef]

- Mayeda, J.; Lie, D.Y.C.; Lopez, J. Broadband Millimeter-Wave 5G Power Amplifier Design in 22 nm CMOS FD-SOI and 40 nm GaN HEMT. Electronics 2022, 11, 683. [Google Scholar] [CrossRef]

- Chan, W.L.; Long, J.R. A 58–65 GHz neutralized CMOS power amplifier with PAE above 10% at 1-V supply. IEEE J. Solid-State Circuits 2010, 45, 554–564. [Google Scholar] [CrossRef]

- Xu, X.; Wagner, J.; Ellinger, F. A 62-GHz High-Efficiency Power Amplifier with Modulation Capability via Back-Gate in 22-nm FD-SOI. IEEE Solid-State Circuits Lett. 2023, 6, 49–52. [Google Scholar] [CrossRef]

- Feng, J.; Lu, L.; Chen, X.; Sun, Y.; Wu, X.; Fan, X.; Li, L. A 60-GHz Variable-Gain Power Amplifier with a Switchable Inductor for TDD Systems. IEEE Microw. Wireless Tech. Lett. 2024, 34, 512–515. [Google Scholar] [CrossRef]

- Feng, J.; Liang, Y.; Niu, X.; Lu, L.; Chen, X.; Cheng, D.; Chen, Q.; Luo, L.; Wu, X.; Fan, X.; et al. A Compact Low-Loss High-Reliability Antenna T/R Switch Embedded in Power Combiner for 60-GHz Fully Differential PA and LNA. IEEE Microw. Wireless Tech. Lett. 2024; to be appeared. [Google Scholar]

- Zhang, L.; Ma, K.; Fu, H. A 60-GHz 32-Way Hybrid Power Combination Power Amplifier in 55-nm Bulk CMOS. IEEE Trans. Microw. Theory Tech. 2023, 71, 613–627. [Google Scholar] [CrossRef]

- Chu, K.-D.; Callender, S.; Wang, Y.; Rudell, J.C.; Pellerano, S.; Hull, C. A dual-mode V-band 2/4-way non-uniform power-combining PA with +17.9-dBm PSAT and 26.5-% PAE in 16-nm FinFET CMOS. In Proceedings of the 2020 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Los Angeles, CA, USA, 4–6 August 2020; pp. 183–186. [Google Scholar]

- Mosalam, H.; Xiao, W.; Gui, X.; Li, D.; Pan, Q. A 54–68 GHz Power Amplifier with Improved Linearity and Efficiency in 40 nm CMOS. IEEE Trans. Circuits Syst. II Exp. Briefs 2022, 69, 40–44. [Google Scholar] [CrossRef]

- Li, X.; Cheng, D.; Jiang, X.; Wang, D.; Li, L. A 57–71-GHz Accurate dB-Linear Variable Gain Power Amplifier with Ultralow Gain Error Using Particle Swarm Optimization Algorithm. In Proceedings of the 2024 IEEE/MTT-S International Microwave Symposium, Washington, DC, USA, 16–21 June 2024; pp. 454–457. [Google Scholar]

- Byeon, C.W.; Park, C.S. A low-loss compact 60-GHz phase shifter in 65-nm CMOS. IEEE Microw. Wireless Compon. Lett. 2017, 27, 663–665. [Google Scholar] [CrossRef]

- Aoki, I.; Kee, S.D.; Rutledge, D.B.; Hajimiri, A. Distributed active transformer—A new power-combining and impedance-transformation technique. IEEE Trans. Microw. Theory Tech. 2002, 50, 316–331. [Google Scholar] [CrossRef]

| Topology | 4 μm × 25 Fingers | 2 × 2 μm × 25 Fingers | 4 × 1 μm × 25 Fingers |

|---|---|---|---|

| PSAT (dBm) | 15.2 | 15.9 | 15.5 |

| PAEpeak (%) | 33.8 | 37.5 | 36.5 |

| Power Gain (dB) | 11.1 | 12.0 | 12.2 |

| Zopt (Ω) | 21.1 + j15.3 | 16.3 + j16.5 | 17.4 + 21.0 |

| This Work | [8] | [9] | [10] | [11] | [12] | [13] | [14] | |

|---|---|---|---|---|---|---|---|---|

| Process | 65 nm CMOS | 22 nm CMOS | 65 nm CMOS | 65 nm CMOS | 65 nm CMOS | 16 nm CMOS | 40 nm CMOS | 55 nm CMOS |

| Topology | 1-way 2-stage CS | 1-way 2-stage cascode | 1-way 4-stage CS cascode | 2-way 4-stage CS | 32-way 4-stage CS | 4-way 2-stage CS | 1-way 4-stage CS | 1-way 4-stage CS |

| Frequency (GHz) | 60 | 62 | 60 | 60 | 60 | 65 | 60 | 60 |

| VDD (V) | 1.0 | 2 | 1.2 | 1.2 | 1.2 | 0.95 | 2 | 1.2 |

| Gain (dB) | 18.3 | 23.3 | 25.4 | 25 | 21.9 | 18 * | 14 | 22.5 |

| Gain/stage (dB) | 9.2 | 11.7 | 6.4 | 6.3 | 5.4 | 9.0 | 7.0 | 5.6 |

| PSAT (dBm) | 13.4 | 13.6 | 12.2 | 16 | 25.1 | 17.9 | 15 | 14.4 |

| P1dB (dBm) | 10.5 | 12.1 | 11.3 | 11.3 | 21.7 | 13.5 | 14 | 13 |

| PAEpeak (%) | 26.7 | 28.3 | 8.9 | 17 | 21 | 26.5 | 26 | 21.5 |

| PAE1dB (%) | 16 | 26 * | 6.5 * | 7 * | 7 * | 15 | 21 * | 17.7 |

| PDC (mW) | 58 | 33 | 186 | 185 | 942 * | - | 110 | 67.2 |

| Area (mm2) | 0.094 | 0.065 | 0.36 | 0.20 | 1.17 | 0.107 | 0.2 | 0.15 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Kim, J.-H.; Byeon, C.-W. A 60 GHz Power Amplifier with Neutralization Capacitors and Compensation Inductors. Electronics 2024, 13, 4276. https://doi.org/10.3390/electronics13214276

Kim J-H, Byeon C-W. A 60 GHz Power Amplifier with Neutralization Capacitors and Compensation Inductors. Electronics. 2024; 13(21):4276. https://doi.org/10.3390/electronics13214276

Chicago/Turabian StyleKim, Joon-Hyung, and Chul-Woo Byeon. 2024. "A 60 GHz Power Amplifier with Neutralization Capacitors and Compensation Inductors" Electronics 13, no. 21: 4276. https://doi.org/10.3390/electronics13214276

APA StyleKim, J.-H., & Byeon, C.-W. (2024). A 60 GHz Power Amplifier with Neutralization Capacitors and Compensation Inductors. Electronics, 13(21), 4276. https://doi.org/10.3390/electronics13214276